# Durham E-Theses

---

## *Gas effects on the interface state spectrum of mis devices*

Martin, P. J.

---

### How to cite:

Martin, P. J. (1980). *Gas effects on the interface state spectrum of mis devices*, Durham e-Theses.

<http://etheses.dur.ac.uk/7619/>

---

### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the [full Durham E-Theses policy](#) for further details.

**GAS EFFECTS ON THE INTERFACE STATE SPECTRUM

OF MIS DEVICES**

By

P. J. MARTIN BSc.

A THESIS SUBMITTED FOR THE

DEGREE OF DOCTOR OF PHILOSOPHY

IN THE UNIVERSITY OF DURHAM

OCTOBER 1980

The copyright of this thesis rests with the author.

No quotation from it should be published without

his prior written consent and information derived

from it should be acknowledged.

### **Abstract**

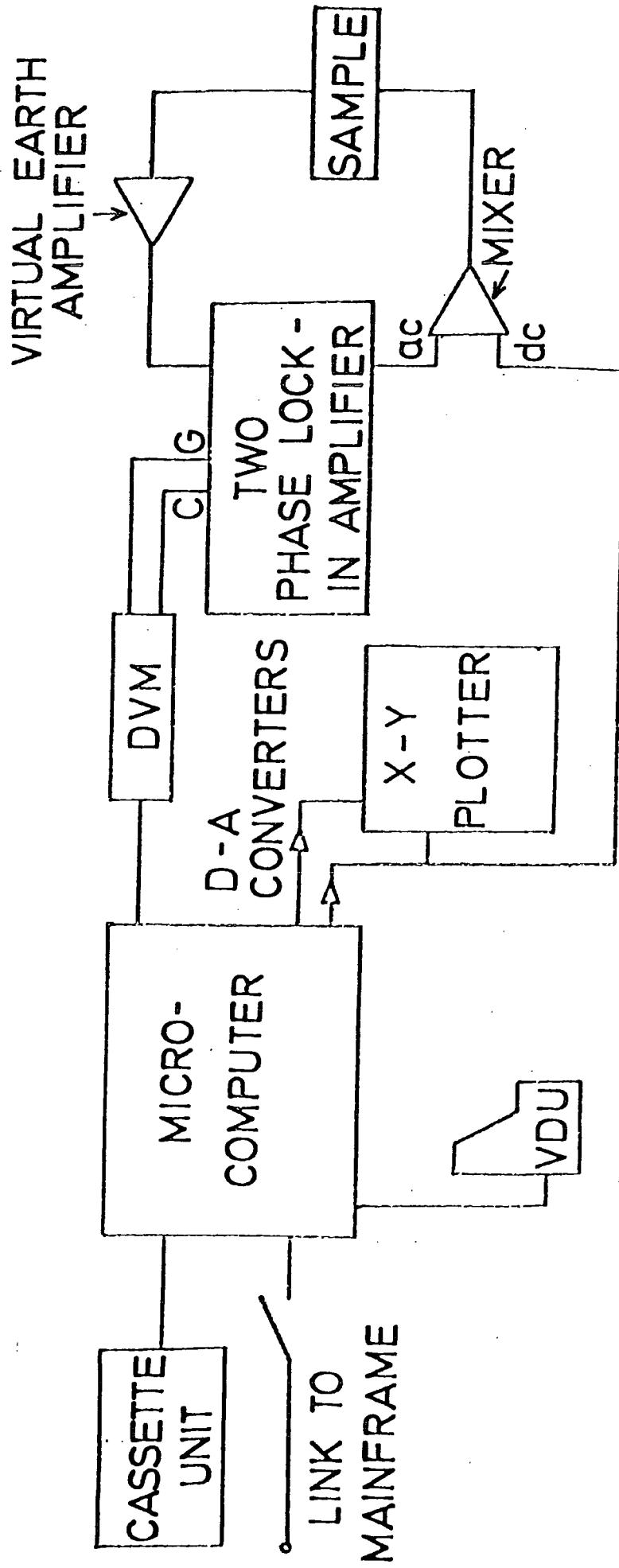

A semiautomatic measurement system has been developed for investigating the electronic structure of the interface between an insulator and a semiconductor. The associated microcomputer possesses advanced software which leads to simple operation particularly when used in the real time mode. An attractive feature of the technique is that admittance data are evaluated in the voltage domain using a modified version of the Simonne method.

The system has been used to investigate the effects of gases on the interface state spectrum of MIS devices; the action of hydrogen upon the palladium-silicon dioxide-silicon system receiving the most attention. An alternative insulator to silicon dioxide has been considered, namely organic Langmuir films. Overall there has been little detectable change in the surface state density, although results with different semiconductors appear to be more encouraging.

## ACKNOWLEDGEMENTS

I gratefully acknowledge the advice, support and guidance given to me throughout the course of this research by the staff and students of the Department of Applied Physics at the University of Durham. In particular, I am indebted to my supervisor, Professor G.G. Roberts, for the time he has devoted to encourage and direct me. I wish to thank Drs B.J. Stanier and C.T. Spracklen for their assistance in setting up the microcomputer; Drs. M.C. Petty and P.G.C. Allman and Messrs R.W. Sykes, K.K. Kan and D.G. Foster for practical assistance and useful discussions; and Mr. D.C. Cowan and Miss J. Morgan for their help in the production of this thesis. The departmental technicians have all helped me along with their friendly advice, especially Messrs. F. Spence, B. Blackburn and P. Friend.

I gratefully acknowledge financial support from ICI Ltd. and the help given by the research group at ICI Runcorn, in particular Dr W.M. Barlow. I would also like to thank Philips, GEC, Plessey Co., and Dr M.J. Morant for the samples used in the research.

Finally I wish to thank my wife, Jo, and my family for their patient support throughout this work.

## CONTENTS

|                                                              | Page     |

|--------------------------------------------------------------|----------|

| <b>CHAPTER 1 Introduction</b>                                | <b>1</b> |

| <b>CHAPTER 2 Theory of the Insulator-Silicon Interface</b>   | <b>3</b> |

| 2.1 Introduction                                             | 3        |

| 2.2 The Atomic Approach                                      | 3        |

| 2.3 The Charge Approach                                      | 9        |

| 2.31 The Fermi Function                                      | 9        |

| 2.32 The Surface Space Charge Region of the<br>Semiconductor | 11       |

| 2.4 The Capacitance Approach                                 | 12       |

| 2.41 Semiconductor Surface Capacitance                       | 12       |

| 2.42 Capacitance of an Ideal MIS Diode                       | 14       |

| 2.43 Insulator Effects                                       | 17       |

| 2.5 The Conductance Approach                                 | 18       |

| 2.51 Admittance of a Single Level State                      | 19       |

| 2.52 Admittance of a Continuum of Surface States             | 22       |

| 2.53 The Surface Potential Fluctuation Model                 | 23       |

| 2.54 The Tunnelling Model                                    | 24       |

| 2.6 More Complex Equivalent Circuits                         | 25       |

| 2.7 Summary                                                  | 26       |

|                                                                                              |           |

|----------------------------------------------------------------------------------------------|-----------|

| <b>CHAPTER 3 Determination of Surface State Parameters<br/>from Measured Electrical Data</b> | <b>28</b> |

| 3.1 Introduction                                                                             | 28        |

| 3.2 The Capacitance Techniques                                                               | 29        |

| 3.21 High Frequency Method                                                                   | 29        |

| 3.22 Low Frequency Method                                                                    | 30        |

| 3.23 Quasi-static Measurement Configuration                                                  | 33        |

| 3.3 Temperature Techniques                                                                   | 33        |

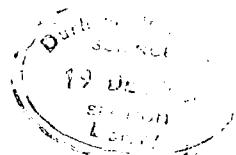

| 3.31 Low Temperature Hysteresis Method                                                       | 34        |

| 3.32 The Transient Capacitance Method                                                        | 35        |

| 3.4 The Conductance Technique                                                                | 36        |

| 3.41 Equivalent Circuits                                                                     | 36        |

| 3.42 Surface State Evaluation                                                                | 38        |

| 3.5 Summary                                                                                  | 40        |

| <b>CHAPTER 4 Experimental Details</b>                                                        | <b>41</b> |

| 4.1 Introduction                                                                             | 41        |

| 4.2 The Quasi-static Technique                                                               | 41        |

| 4.21 Use of Equipment                                                                        | 41        |

| 4.22 Experimental Difficulties                                                               | 43        |

| 4.3 The Admittance Measurement System                                                        | 44        |

| 4.31 Input Circuit                                                                           | 45        |

| 4.32 Input Circuit with VEA                                                                  | 47        |

| 4.33 Bias Injection Circuit                                                                  | 48        |

| 4.4 Calibration                                                                              | 48        |

| 4.5 The Microcomputer                                                                        | 50        |

| 4.51 The Hardware                                                                            | 50        |

| 4.52 The Software                                                                            | 52        |

|                                                       |           |

|-------------------------------------------------------|-----------|

| 4.53 SIXTH in Detail                                  | 54        |

| 4.6 Sample Details                                    | 55        |

| 4.61 Source of Samples                                | 55        |

| 4.62 Sample Characteristics                           | 56        |

| 4.63 Sample Contacting Procedure                      | 57        |

| 4.64 Sample Measurement                               | 57        |

| 4.7 Experimental Results                              | 58        |

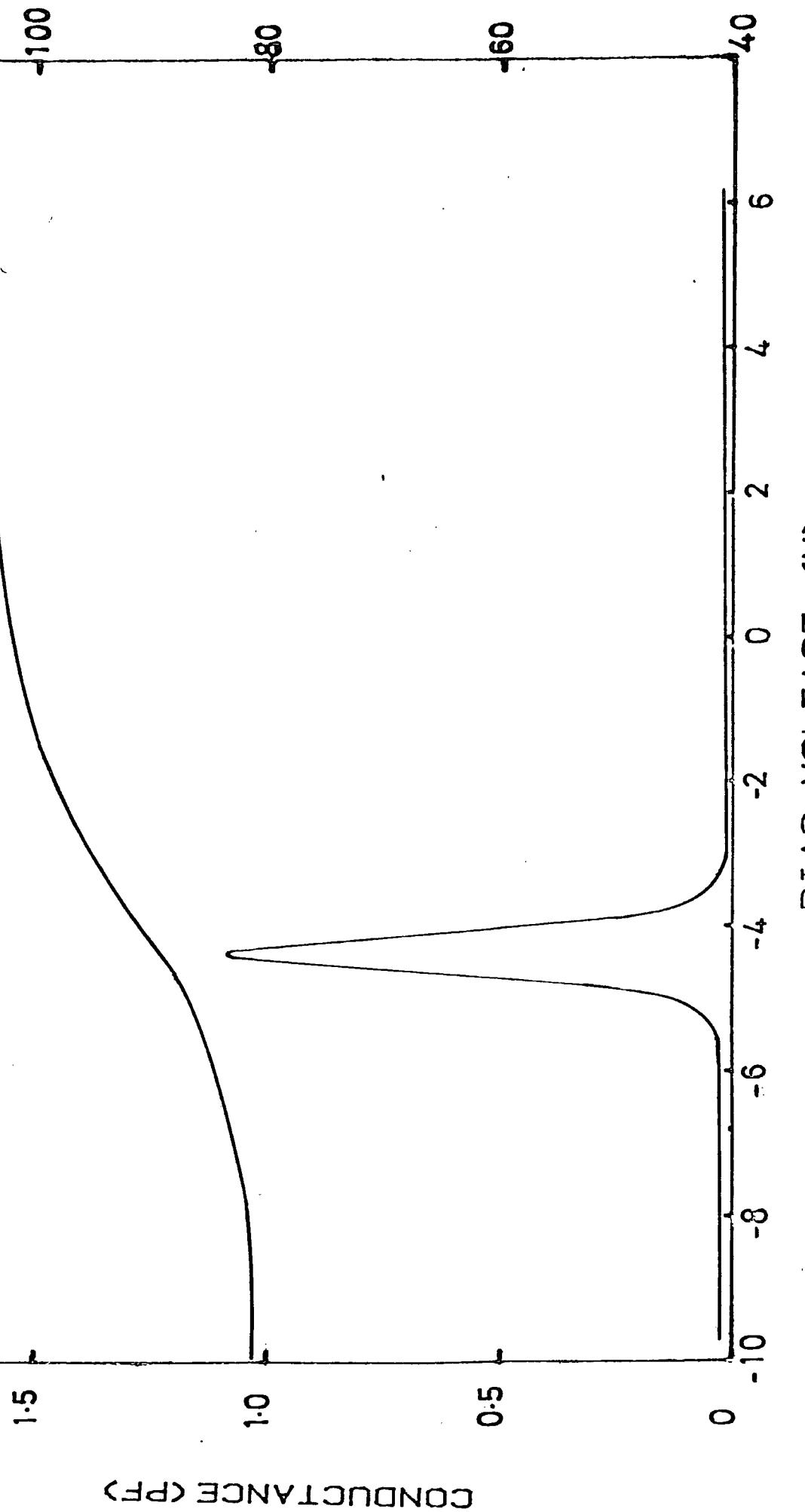

| 4.71 Admittance-Voltage Characteristics               | 58        |

| 4.72 Results obtained with the Microcomputer          | 59        |

| <b>CHAPTER 5 Surface State Density Measurement -</b>  | <b>61</b> |

| <b>A Novel Approach Using a Microcomputer</b>         |           |

| 5.1 Introduction                                      | 61        |

| 5.2 Practical Drawbacks of the Conductance Technique  | 61        |

| 5.3 Real Time Processing                              | 62        |

| 5.4 Parallel Conductance Peaks                        | 63        |

| 5.5 Novel Surface State Density Measurement Procedure | 64        |

| 5.6 Semiconductor Capacitance                         | 65        |

| 5.7 Assisted Peak Location                            | 66        |

| 5.8 Practical Procedure                               | 68        |

| 5.9 Experimental Results                              | 71        |

| 5.10 Summary                                          | 73        |

| <b>CHAPTER 6 Gas Effects on MOS Devices</b>           | <b>75</b> |

| 6.1 Introduction                                      | 75        |

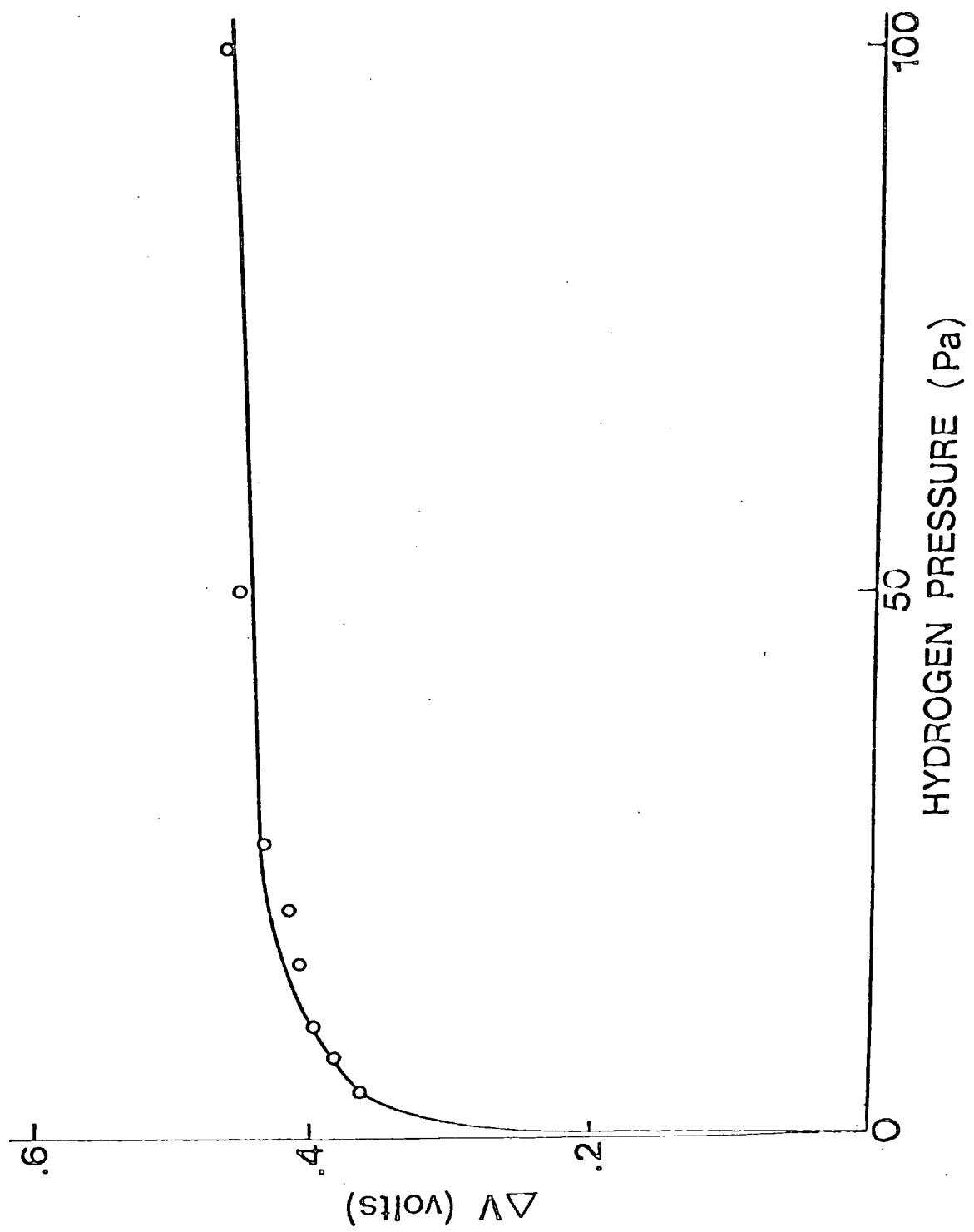

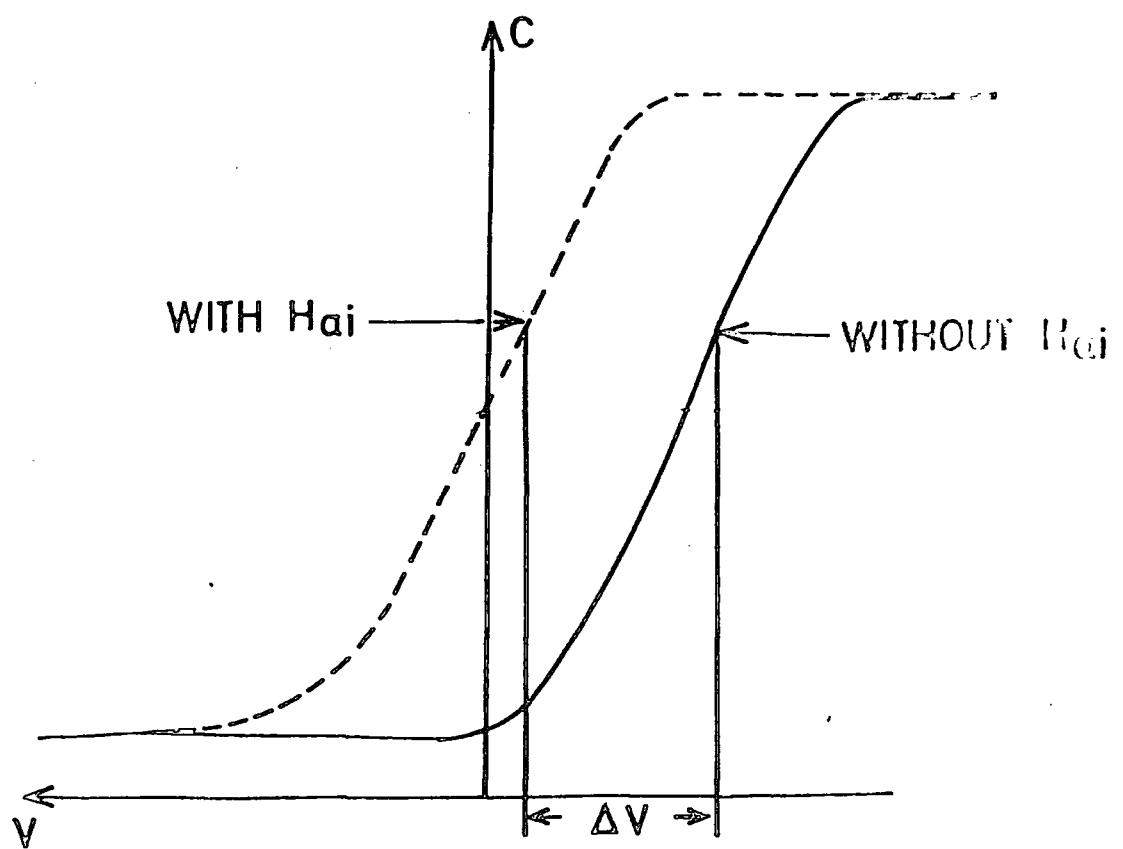

| 6.2 Hydrogen Interactions on Palladium MOS Structures | 76        |

| 6.21 Introduction                                     | 76        |

| 6.22 General Physical Properties                      | 77        |

| 6.23 Palladium MOS Device Properties                  | 78        |

|                                                                      |           |

|----------------------------------------------------------------------|-----------|

| 6.3 Experimental Difficulties                                        | 81        |

| 6.31 Top Contact Area Change                                         | 81        |

| 6.32 Variation in Series Resistance                                  | 82        |

| 6.33 Bias Stress Effects                                             | 83        |

| 6.4 Experimental Results                                             | 83        |

| 6.41 Palladium-Silicon Schottky Barrier Results                      | 83        |

| 6.42 MOS Device Results                                              | 85        |

| 6.5 Summary of Hydrogen Work                                         | 87        |

| 6.51 Discussion of Results                                           | 87        |

| 6.52 A Hydrogen-Induced Surface State?                               | 88        |

| 6.6 Other Gas Effects                                                | 91        |

| <b>CHAPTER 7 Gas Effects on Langmuir Film Devices</b>                | <b>92</b> |

| 7.1 Introduction                                                     | 92        |

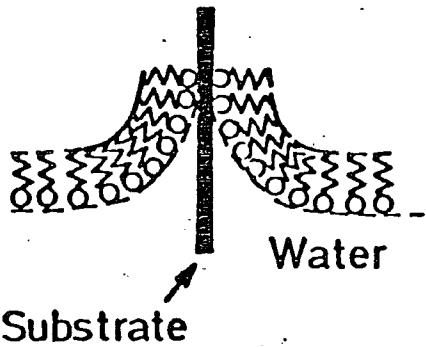

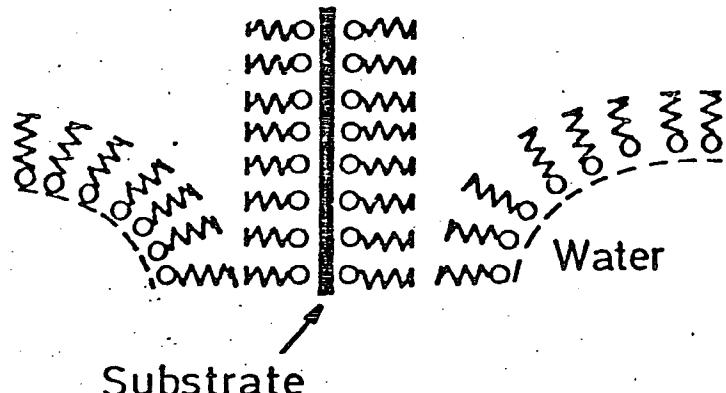

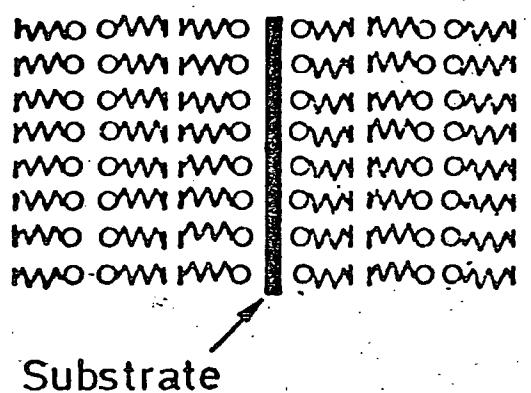

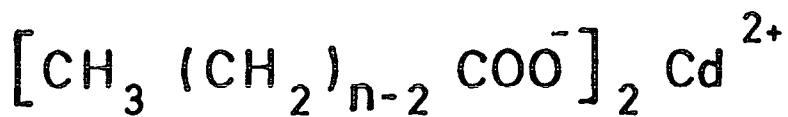

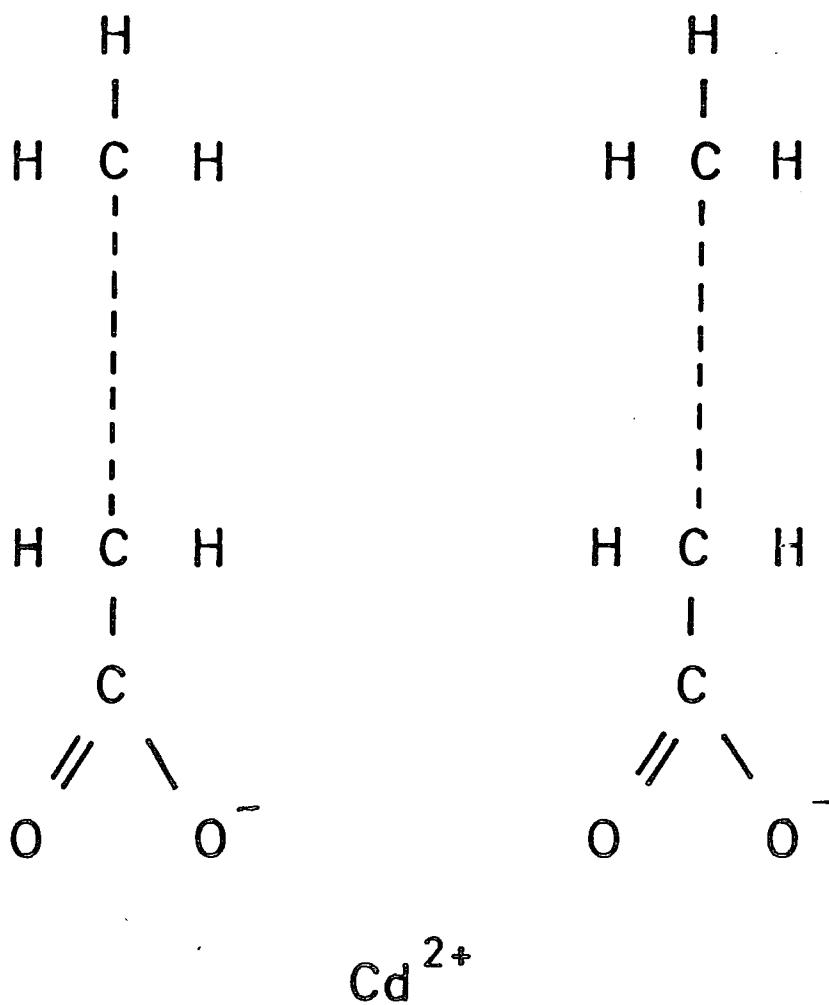

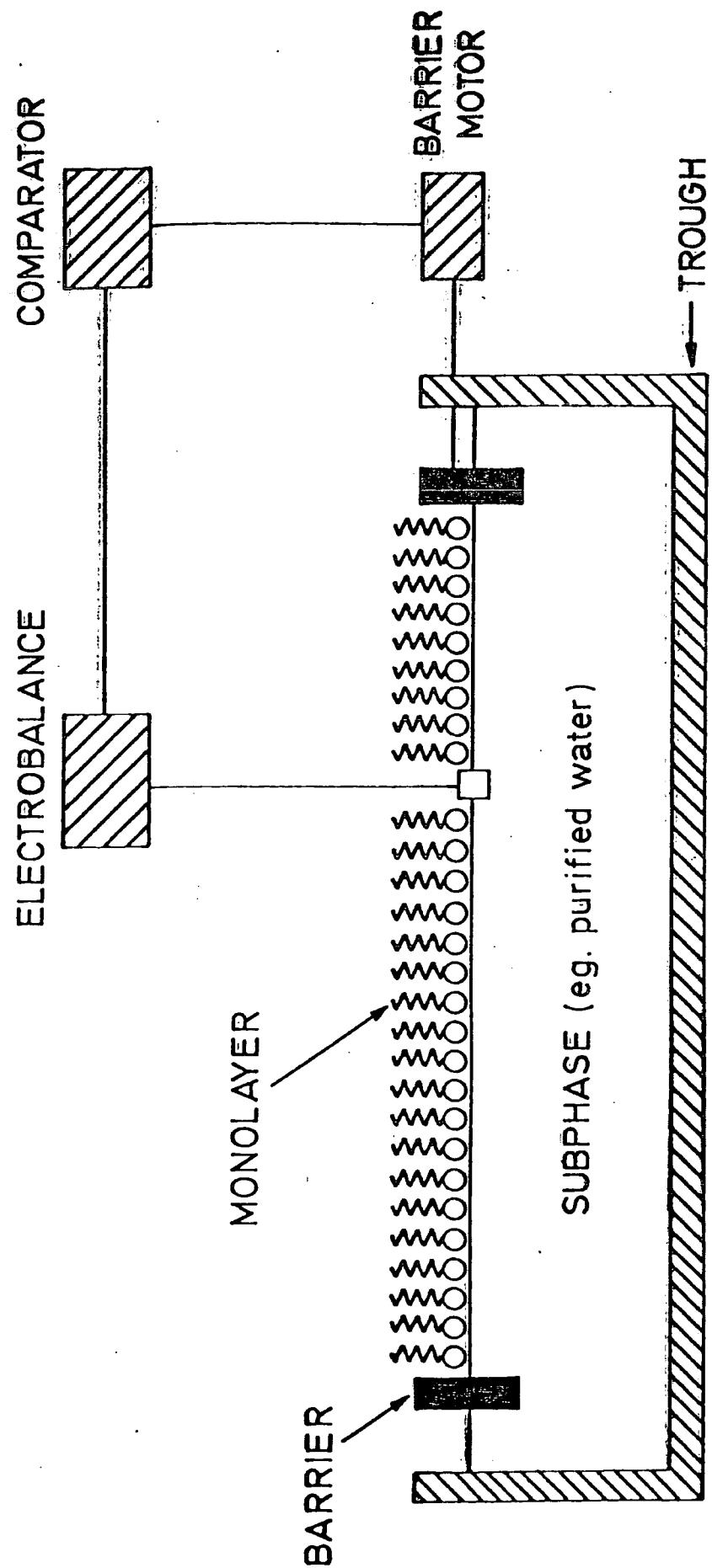

| 7.2 Preparation of Langmuir Films                                    | 93        |

| 7.21 Suitable Materials for Langmuir Films                           | 93        |

| 7.22 Preparation of Langmuir Films                                   | 94        |

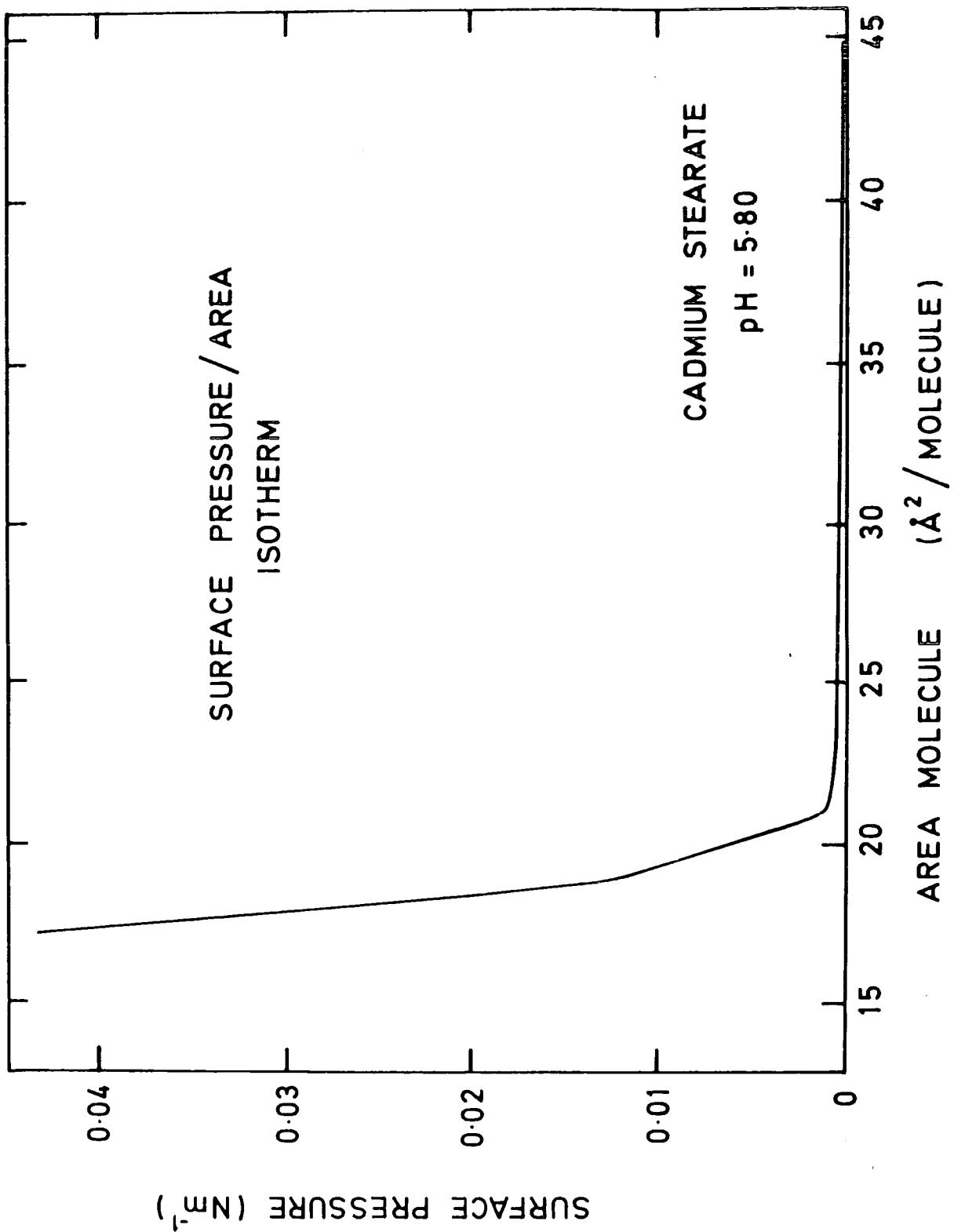

| 7.3 Experimental Results                                             | 96        |

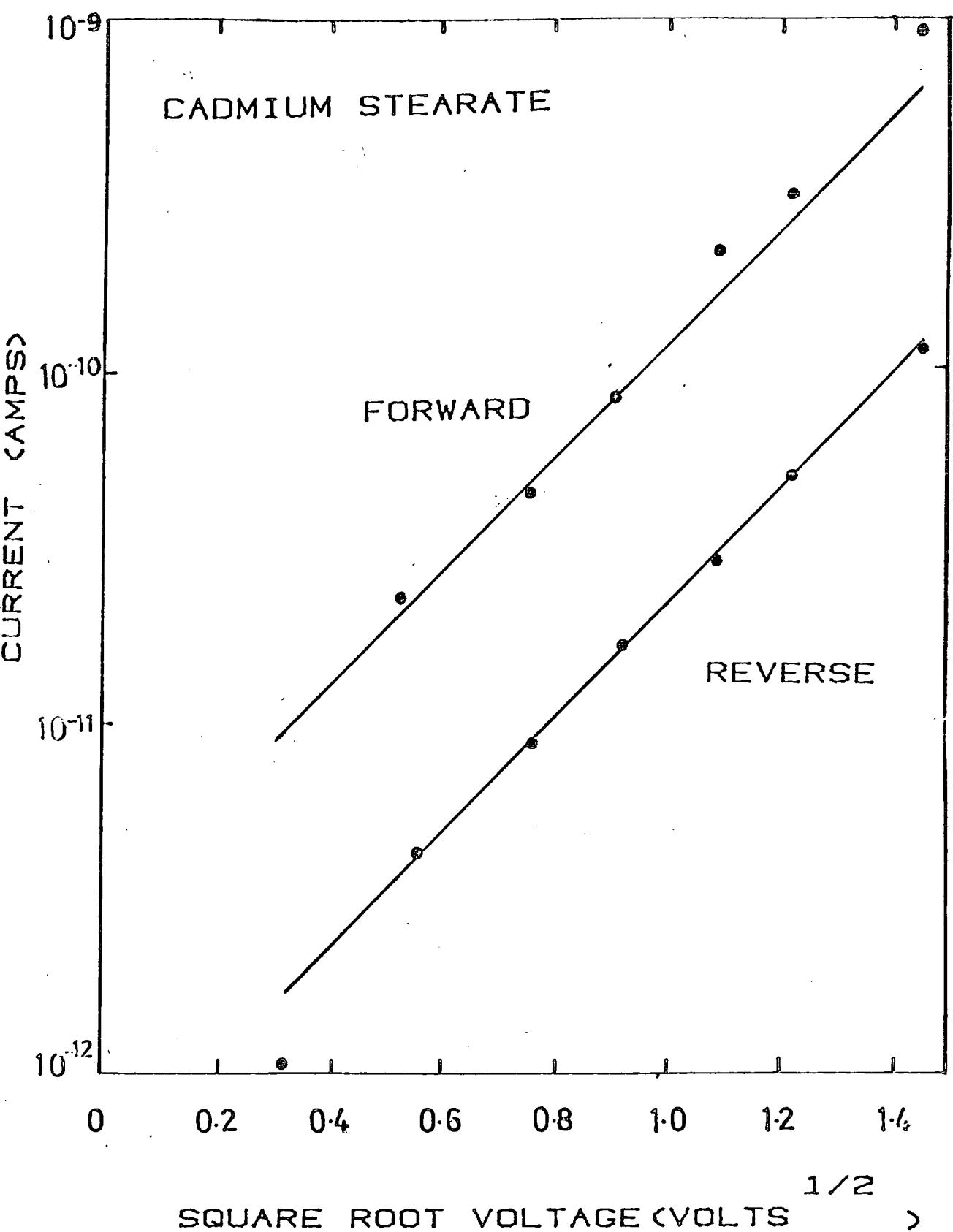

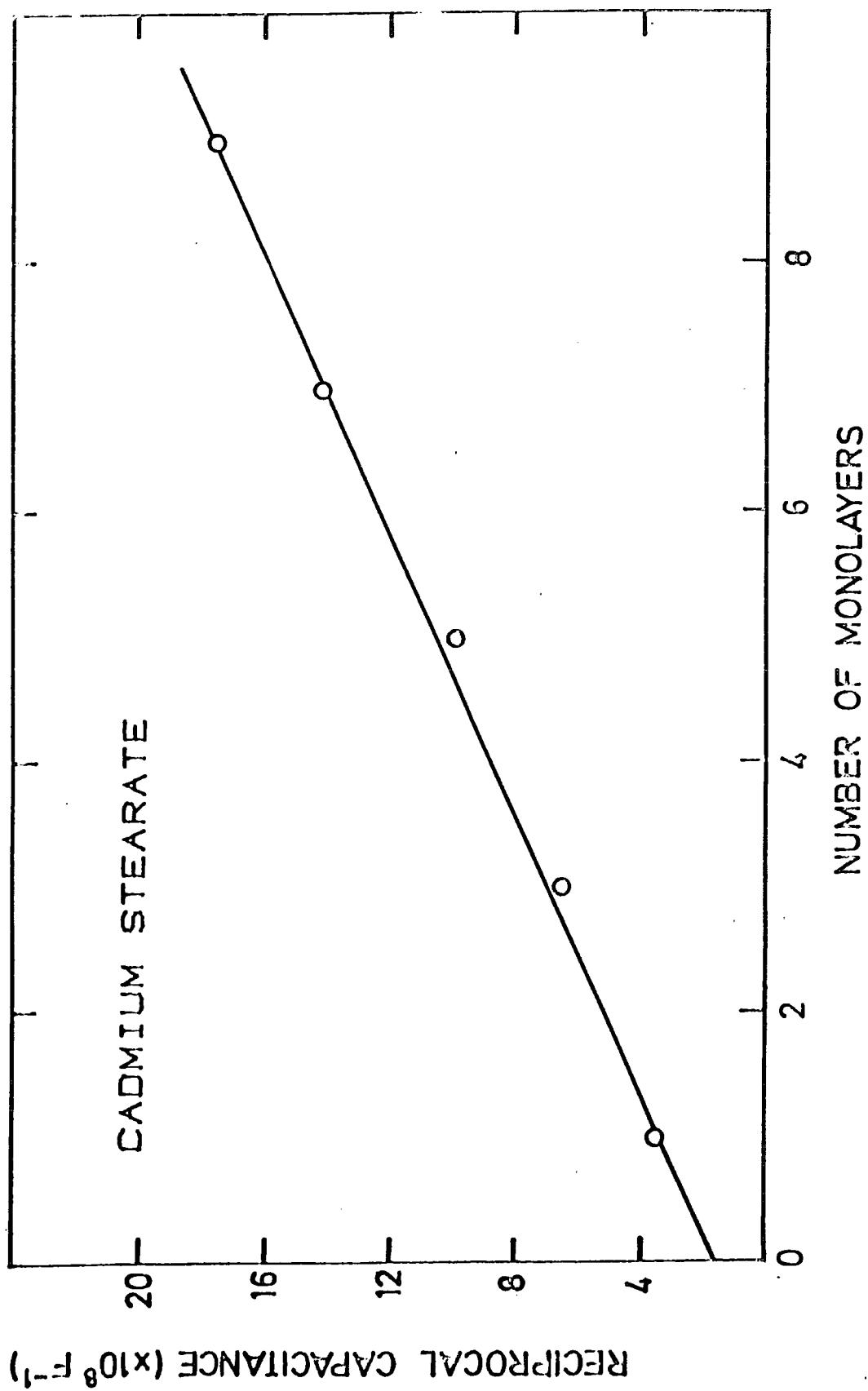

| 7.31 Langmuir Film (MIM) Structures                                  | 96        |

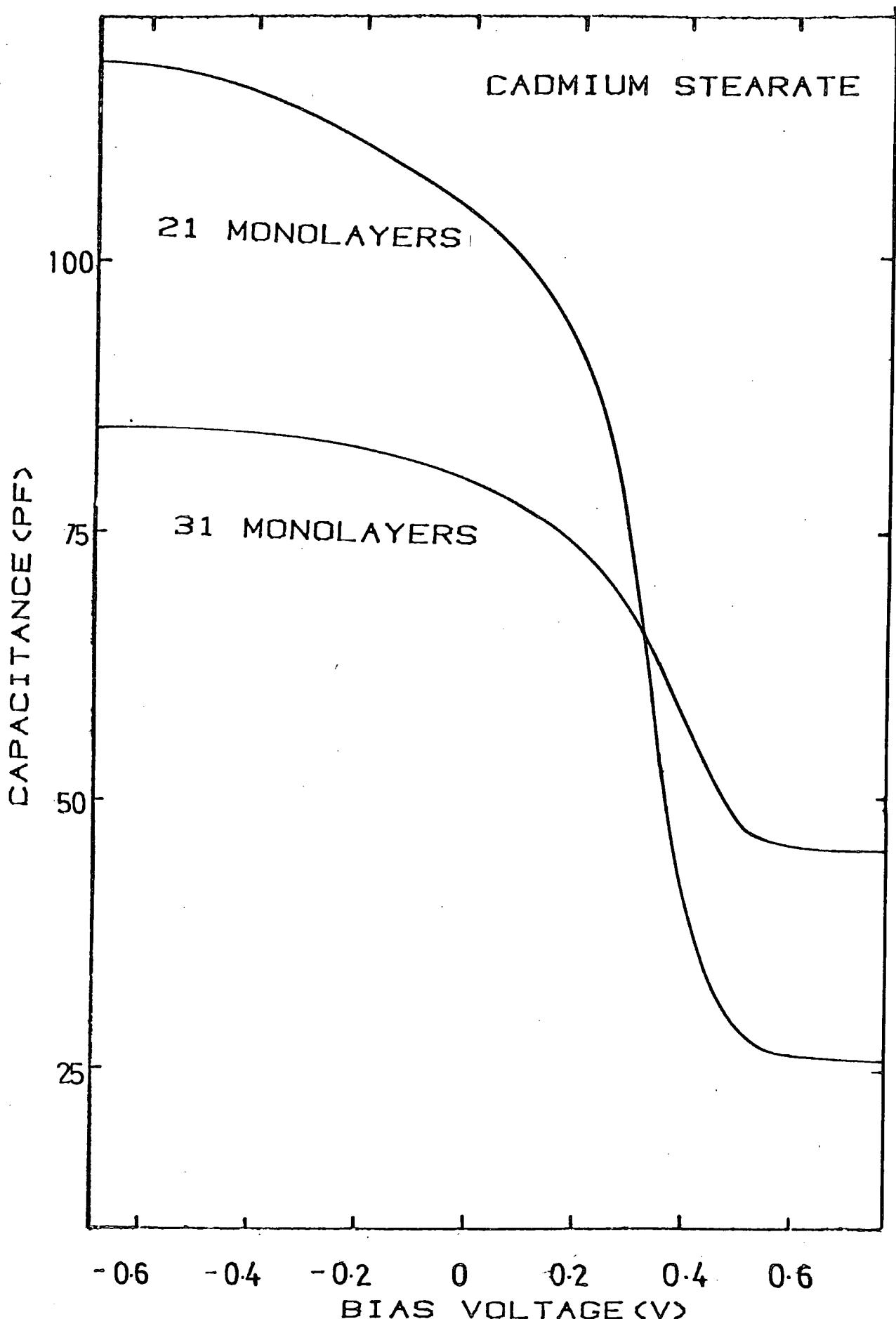

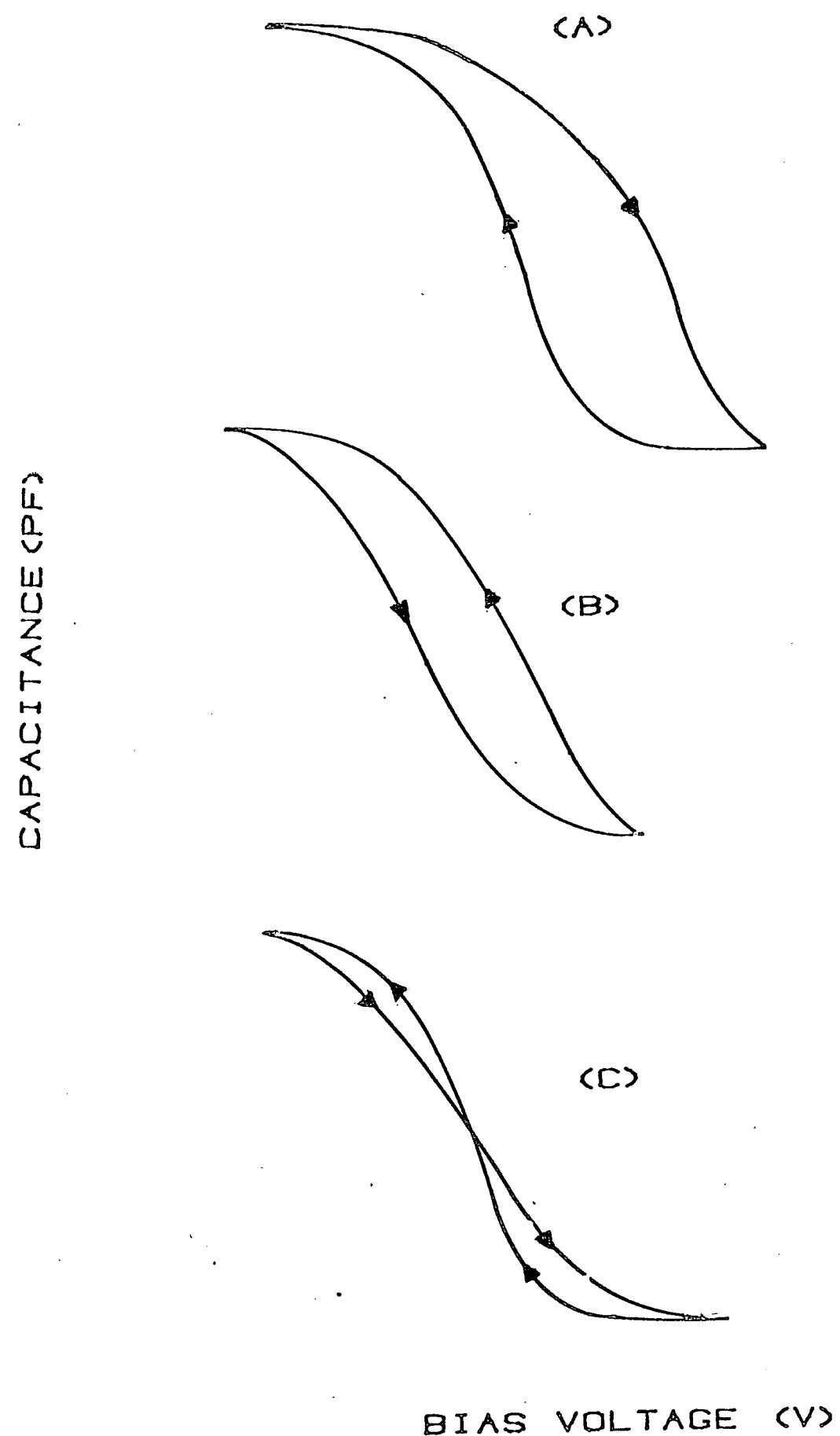

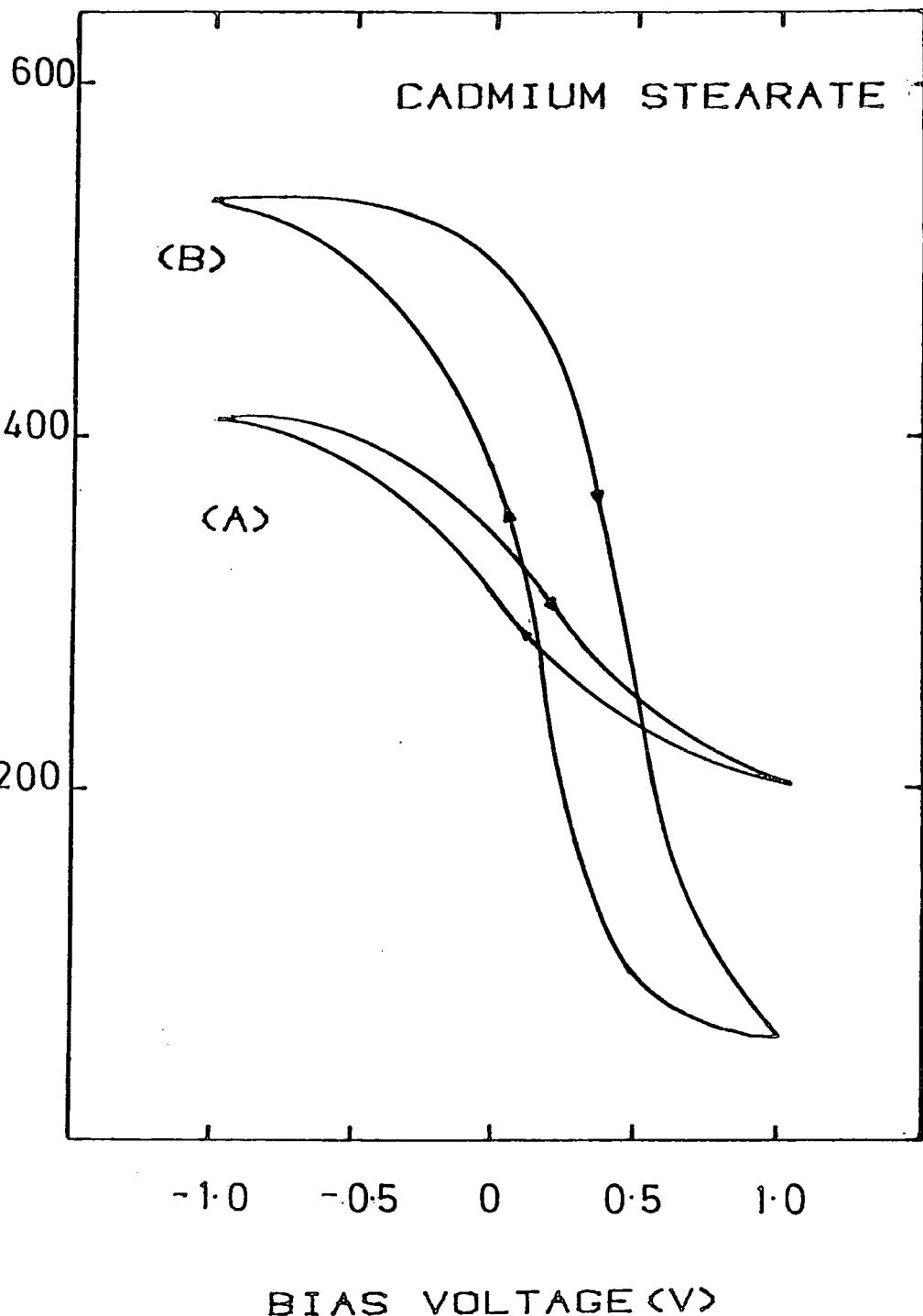

| 7.4 Langmuir Film (MIS) Structures                                   | 98        |

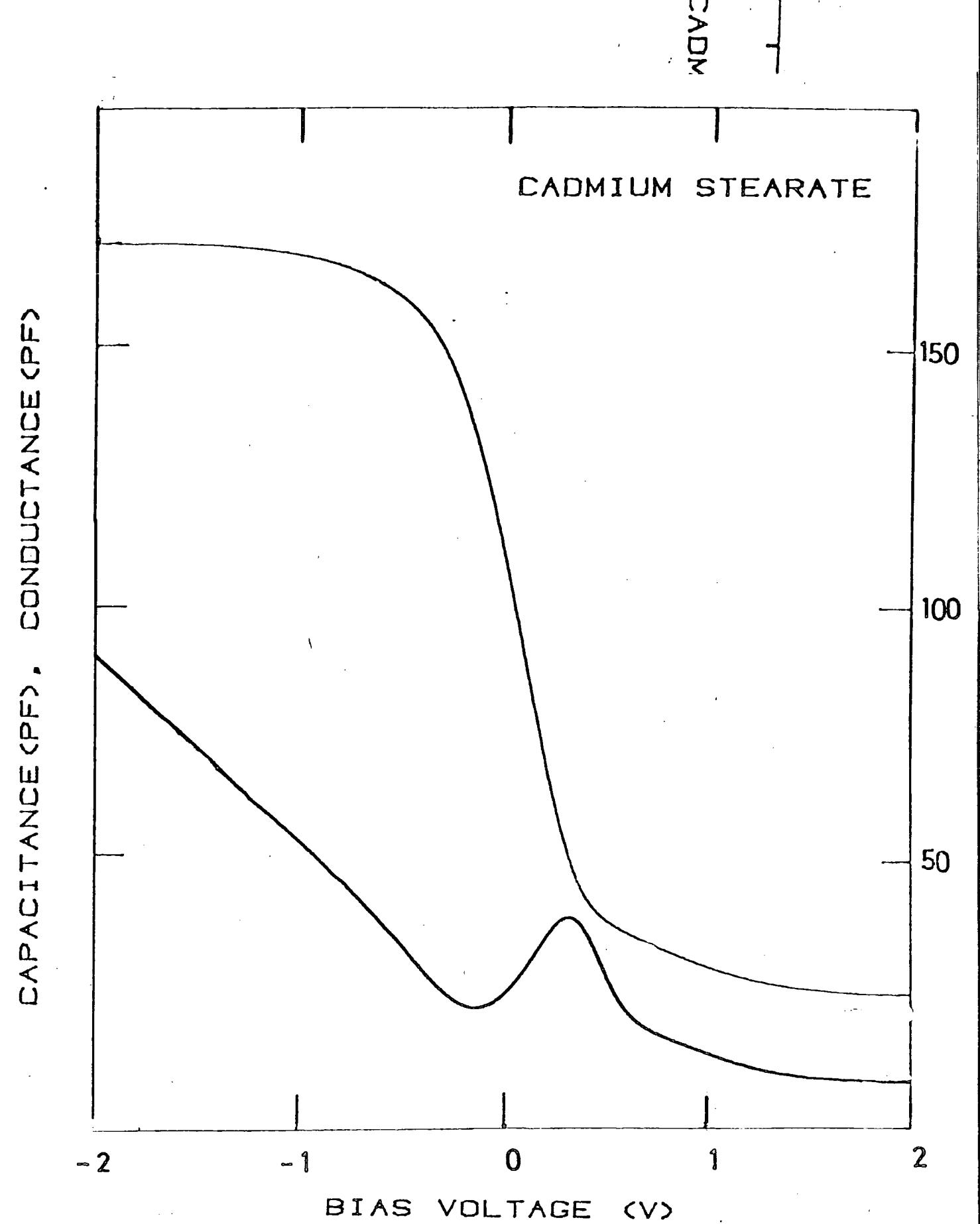

| 7.41 Admittance-Voltage Characteristics                              | 99        |

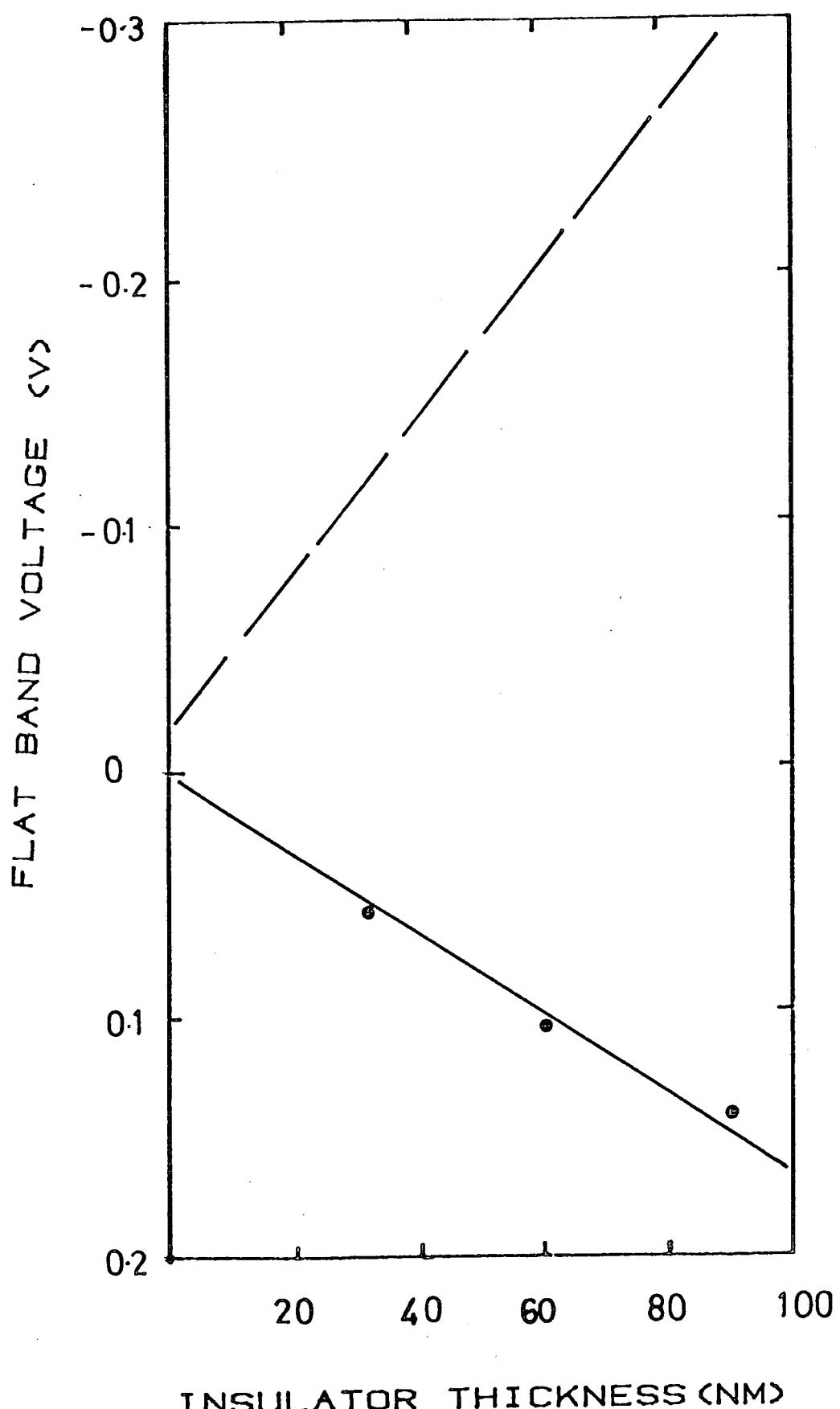

| 7.42 Surface State Analysis                                          | 102       |

| 7.43 Comparison with Langmuir Films<br>on Alternative Semiconductors | 104       |

| 7.5 Gas Effects on Langmuir Films                                    | 105       |

| 7.51 The Action of Moisture                                          | 106       |

| 7.52 Palladium/Langmuir Film/Silicon                                 | 107       |

| 7.53 Effect of Gases on other Langmuir Film<br>MIS Structures        | 107       |

7.54 Summary and Suggestions for Further Work 108

**CHAPTER 8 Summary** III

REFERENCES

APPENDICES

## Chapter I

### Introduction

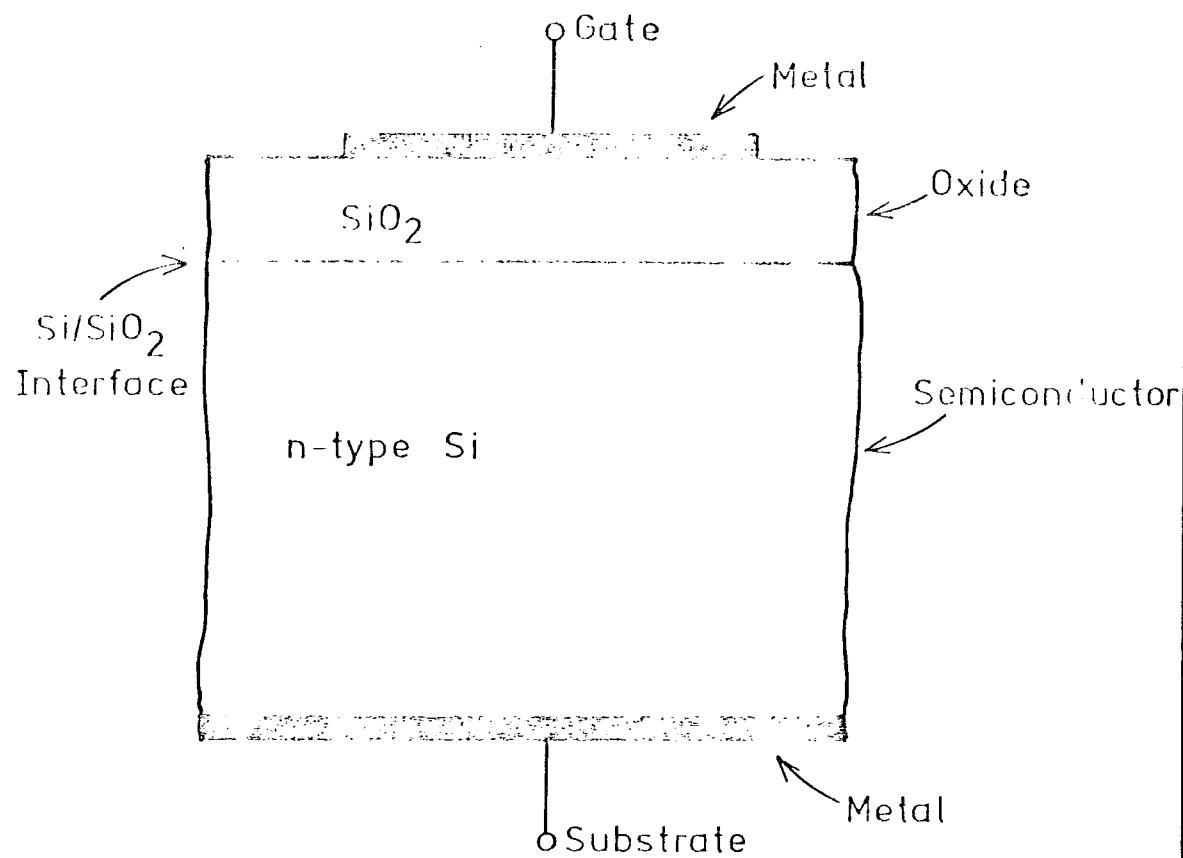

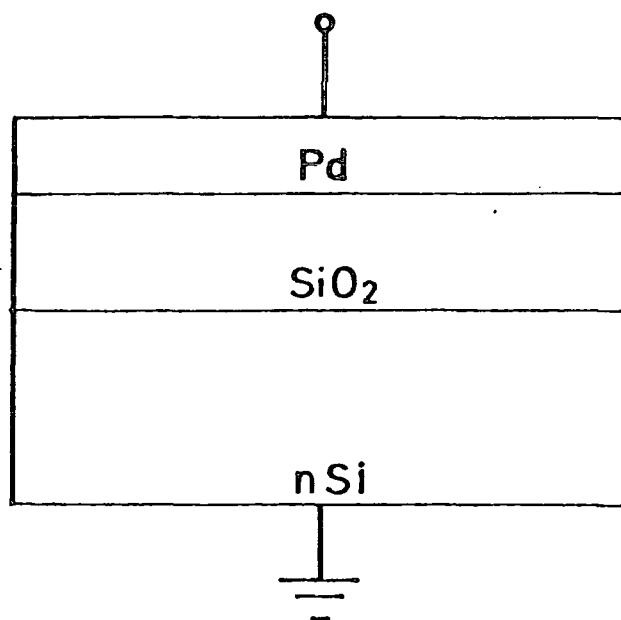

The electronic structure of the interface between an insulator and a semiconductor is of paramount importance in field effect devices such as the metal-oxide-semiconductor (MOS) capacitor shown in figure I.1. The electrical properties of this type of device are dependent upon the presence of trapping centres located at the insulator-semiconductor boundary known as surface or interface states. These are able to communicate with mobile carriers in the semiconductor and make a contribution to the measured admittance characteristic. The interface state density ( $N_{ss}$ ) is influenced by impurities or defects which may be introduced accidentally during the processing of the device. In this thesis, a novel development of the standard interface state density determination procedure is presented. The microprocessor-controlled instrumentation described enables not only rapid evaluation of the surface state density, but also easy location of this density with respect to the band edges which previously had required a separate measurement.

The necessary theory for the comprehension of the operation of metal-insulator-semiconductor (MIS) devices is outlined in Chapter 2. This is done by progressing from a microscopic atomic view of the system through a consideration of the role of charge in various regions of the device to a macroscopic circuit element type of approach. (As in Chapter 3, only a brief summary is given; fuller details will be found in the references.) In Chapter 3, a review is presented of the various electrical techniques that utilise MIS devices to obtain interface state density information. The technique that offers the most detail with the best accuracy is the conductance

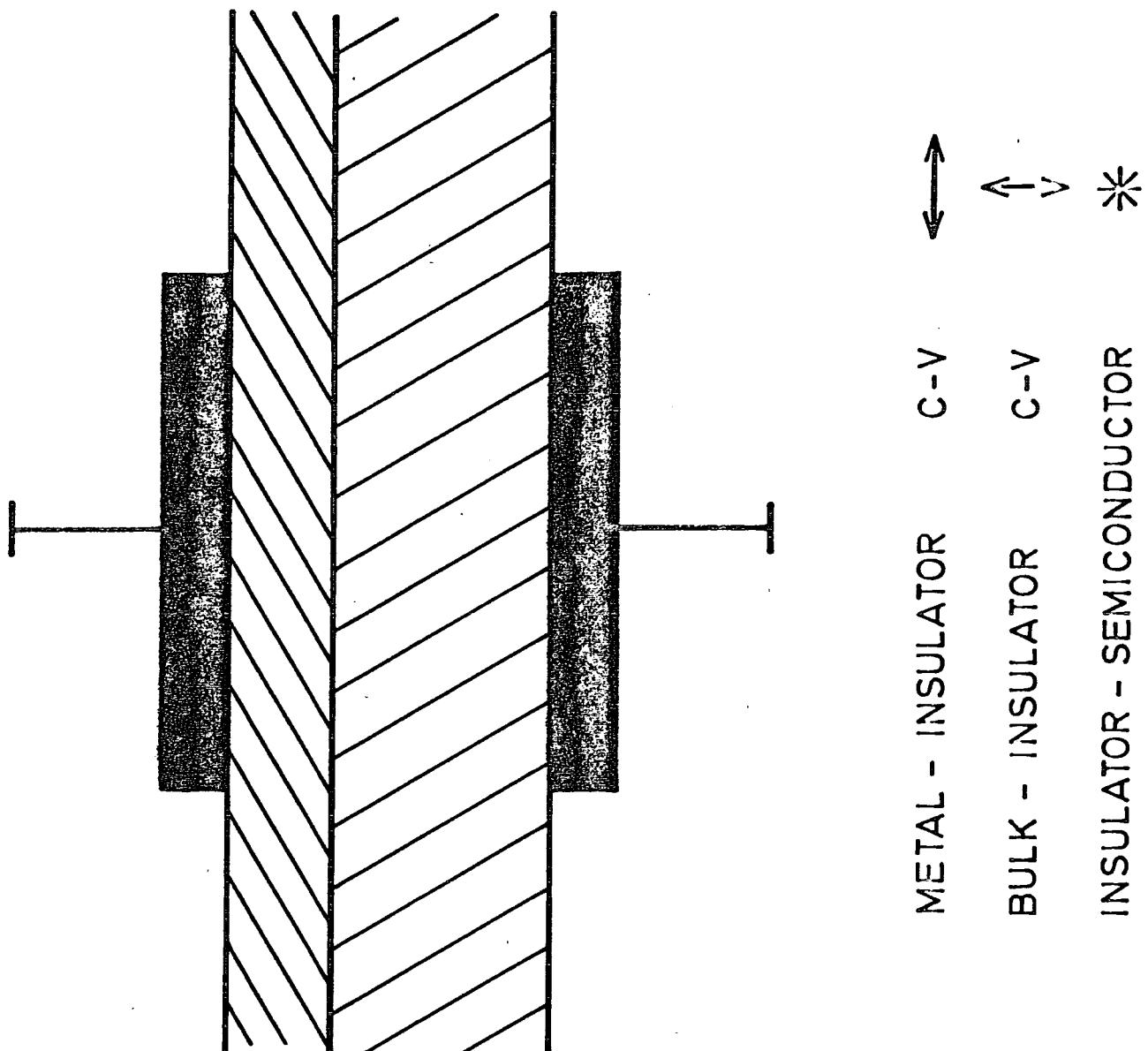

Figure 1.1 Structure of the MOS capacitor.

technique of Nicollian & Goetzberger (1). Unfortunately, however, it is extremely tedious in practice and part of this work has been spent developing a method to reduce the effort involved. This was achieved with the aid of a microprocessor used in a real time mode. This and ancillary equipment are described in Chapter 4 whilst the measurement procedure is outlined in Chapter 5.

The recent need to efficiently interface microelectronic equipment to the outside world has led to a renewed interest in comprehending the effect of the ambient on electronic device structures. We were particularly interested in the change in surface state density of MIS capacitors although, as outlined in the introduction to Chapter 6, other parts of the structure can be influenced. These effects are monitored through measurement of the electrical response. Several workers (2,3) have indicated that surface states may be influenced by the ambient surrounding the device but, owing to the lack of a fast accurate measurement technique, this subject has been little explored. One particular example is the controversy over the role of hydrogen in palladium-coated MOS devices (3,4), which we have tried to resolve using our equipment. The results that we have obtained are described in Chapter 6. We have also investigated the effect of gas on MIS devices incorporating novel Langmuir film insulators. The preparation of these organic monomolecular based films and the gas effects upon them are described in Chapter 7.

## Chapter 2

### Theory of the Insulator-Silicon Interface

#### 2.1 Introduction

There are two main ways to acquire an understanding of the action of defects at the insulator-silicon interface. The first, a microscopic approach, gives an atomic view, and is obtained through a chemical consideration using optical and electron scanning techniques such as ESR (1). Alternatively the interface can be viewed in a macroscopic fashion, characterized by parameters derived from electrical measurements. Accordingly, in this chapter, a physical model is initially outlined which is then developed into an electronic consideration of the metal-insulator-semiconductor diode whose properties we have examined.

#### 2.2 The Atomic Approach

When a collection of semiconductor atoms comes together to form a crystal, there is an interaction between the extreme orbitals with the formation of bands of permitted energy where electrons are allowed to reside. The outermost occupied bands are known as the valence and conduction bands and are separated by a forbidden band (or gap) in electron energy, which in a perfect lattice is devoid of electrons. Whenever the periodicity of the crystal matrix is interrupted by the presence of lattice defects or impurity atoms, then this arrangement will be perturbed. Generally this perturbation manifests itself as an extra amount of energy levels that may be situated in the forbidden gap. Such levels located in the bulk of the material are known as bulk traps, whereas at the surface or at an interface they are called

surface or interface states. The surface of the crystal itself also represents an interruption of this lattice and gives rise to surface states. In silicon these are thought to be due to dangling bonds formed by incompletely filled orbitals of the  $sp^3$  hybridisation of the atoms; one per surface atom on clean cleaved silicon, except for the (111) direction (2).

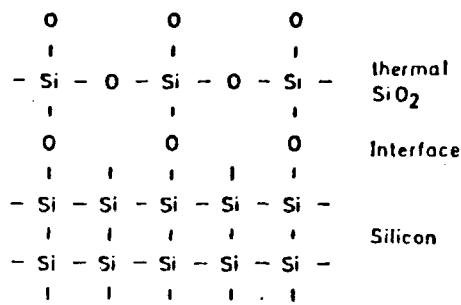

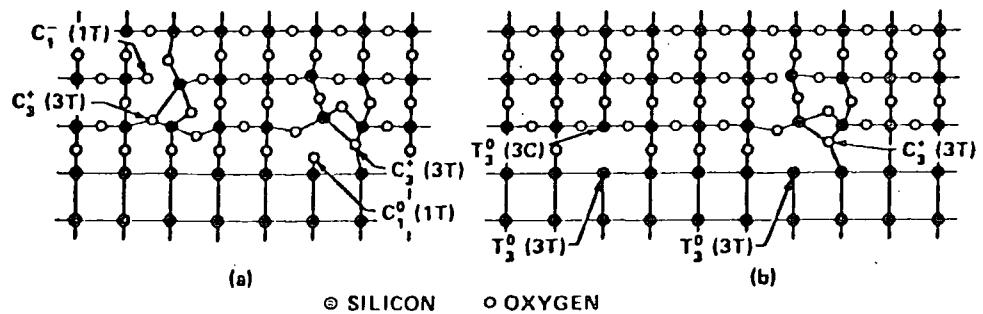

The growth of silicon dioxide reduces the number of surface states by saturating dangling bonds; however, as can be seen from figure 2.1, the silicon dioxide lattice does not quite match the silicon one, and so there will always be a fraction of unsaturated bonds. As a consequence of this misfitting, there will be imperfections which will give rise to strain and other defects. In fact there is a transition region 0.5 to 1 nm wide where  $SiO_x$  ( $x < 2$ ) occurs; thus it can be seen that there will be various unsatisfied bonds in different environments. Several models (3) have been proposed to try and correlate the chemical and electronic nature of the interface in order to explain the origin of two different types of defects that are found. These are fast states which are able to exchange charge very quickly with the silicon and fixed charge ( $Q_{ss}$ ) which cannot. We shall concentrate on two of them.

#### (I) The Trivalent Silicon Model (4)

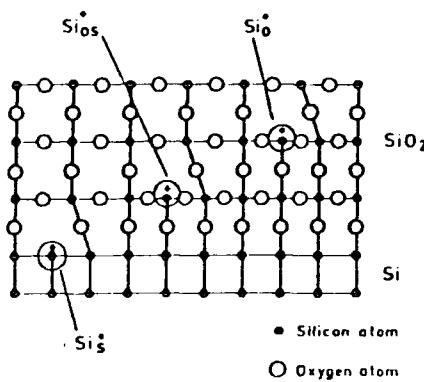

This model is based on the concept of trivalent silicon which can take three different forms (see figure 2.2):

$:Si_s$  bound to three silicon atoms

$:Si_o$  bound to three oxygen atoms

$:Si_{os}$  bound at the interface

Figure 2.1 Simple schematic diagram of the silicon-silicon dioxide interface. (19)

Figure 2.2 The silicon-silicon dioxide interface with three trivalent silicon defects (4)

Figure 2.3 The silicon-silicon dioxide interface with various defect pair configurations. (5)

The first is considered to be a surface state whilst the second two are assumed to be hole traps; the latter much deeper energywise due to its interaction with the silicon surface. This is possibly of the image force type and leads to a lowering of the energy of the defect, so much so that it is assumed to be above the conduction band edge and therefore permanently ionized to  $:Si_{os}^+$ . It is therefore the source of the fixed oxide charge.

The above model can be used to explain several of the experimentally encountered properties. For example, it is well known that the surface state density of Si-SiO<sub>2</sub> is reduced by low temperature annealing in a hydrogen atmosphere (3). The following reaction of the  $:Si_s$  centre with interstitial hydrogen (H<sub>i</sub>) accounts for this by bond saturation:

The reverse reaction represents the increase of surface state density that occurs on annealing at high temperatures and corresponds to the thermal dissociation of the SiH bond. Hydrogen annealing has no effect on oxide charge because  $Si_{os}^+$  is in an unreactive low energy condition. However, the concentration of the above three defects is correlated at high temperatures where the following occurs

## (2) The Defect Pair Model (5)

The second model is based on defect pairs rather than single ones, as above, and follows on from the Street & Mott concept (6) that two dangling bonds might be energetically more stable as two charged centres, the more positive centre lowering its energy by forming three bonds. This reaction is represented by the following equation:

The superscript refers to the charge state, C represents an oxygen atom (we shall use T for silicon), and the subscript refers to the covalent coordination (that is, the number of atomic bonds). For example, in bulk silicon dioxide,  $C_1^-$  could be a non-bridging negatively-charged oxygen atom bonded to a :Si atom, whereas  $C_3^+$  could be an oxygen atom bonded to three silicon atoms of the network. Such a pair of defects is shown on the left of figure 2.3a.

However, the defects right at the interface are more interesting since they can be used to explain various phenomena there. If we assume that the electron associated with the  $C^-$  centre has been injected into the bulk, which is highly likely considering its location, we then have  $C_1^0$  (1T),  $C_3^+$  (3T) - the terms in brackets specifying the atoms that are bonded to the oxygen atoms. The former, which is ESR-active, accounts for the  $P_c$  centre seen by Nishi (7), whereas the latter can be associated with the positive space charge,  $Q_{ss}$ , which again is in a low energy state and thus impervious to the action of hydrogen. If oxygen vacancies are present through imperfection then we have the situation in figure 2.3b that explains the origin of two other ESR defects  $P_a$  and  $P_b$ . The  $P_b$

centre represents the aforementioned dangling bond which can be annealed by hydrogen action through a similar reaction to the above; indeed it has been shown by experiment (8) that the magnitude of the ESR  $P_b$  signal is reduced at the same time.

Now let us consider the influence of extrinsic impurities which may also give rise to surface states. Again there is no absolute theoretical evaluation of their effect and, to further complicate matters, some of the experiments which indicate that extrinsic impurities are the source of surface states are open to question. For example, sodium ions, well known for causing instability problems through their high mobility in silicon dioxide, have been shown to introduce a surface state 0.05 eV below the conduction band edge (9). Some workers (10), however, maintain this is a spurious result due to surface potential fluctuations (see section 2.54). Another example is that supposed surface states introduced by ion implanted impurities, previously thought to be due to those impurities (11), have been shown to be caused by the damage that the implantation produces (12). This was proved by high temperature annealing of the samples which made the above surface states disappear.

It may be the case that the location of the extrinsic impurities restrict them from contributing to the surface state density for the following two reasons. Firstly, interstitial impurities, because of their various possible interstitial spatial locations, do not give rise to identical energy level positions within the band gap and therefore do not augment each other to produce a significant state. Secondly, in general, most imperfections that lie in the oxide will have their resultant energy levels outside the bandgap (13). Since

this is where they are likely to be gettered, owing to the preferential incorporation of impurities in a disturbed region, then this might also explain their lack of effect. On the other hand though, certain elements such as gold (see section 4.24), germanium (14) and the group III & V standard dopant atoms (15) have been conclusively shown to introduce surface states, but the actual mechanism is yet to be fully explained.

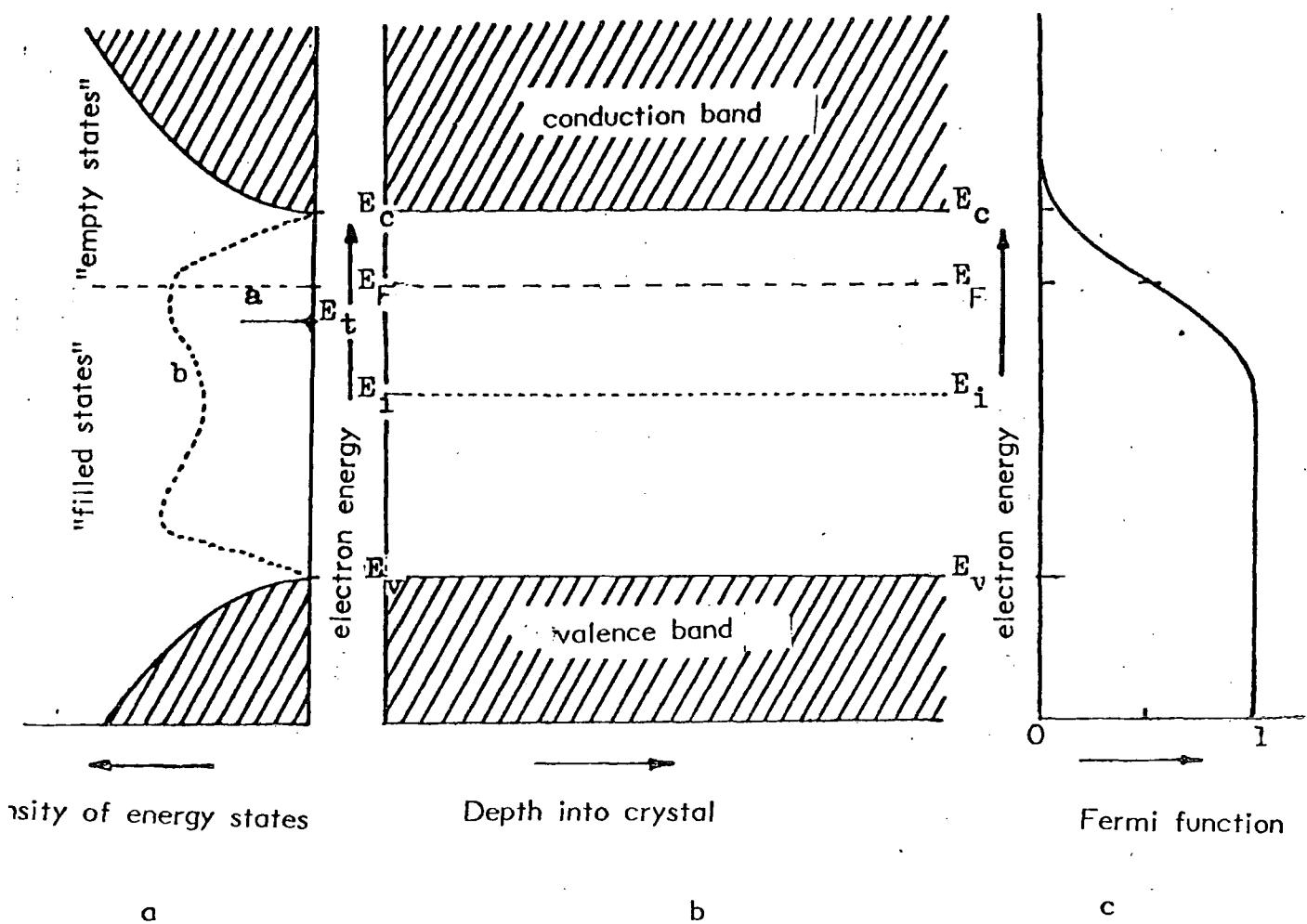

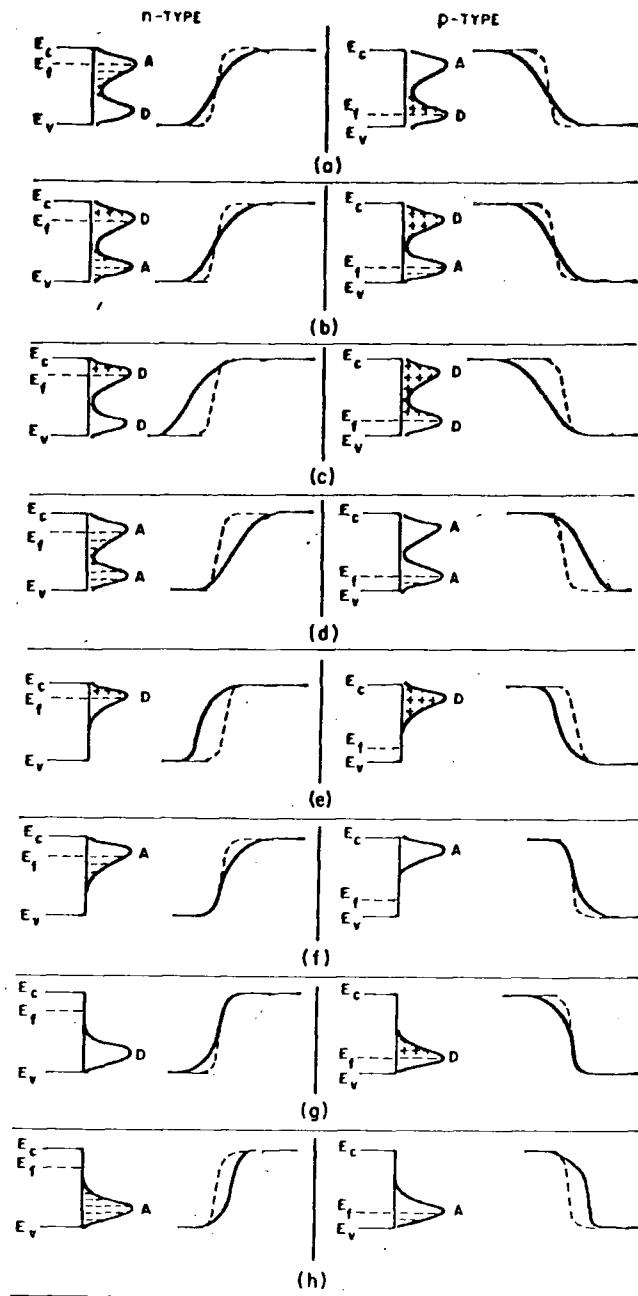

The distribution of surface states in energy throughout the bandgap can have various forms: it can be a single level which could be caused by a specific impurity as has just been outlined (a in figure 2.4a); it may be spread throughout the bandgap (b in figure 2.4a); or it may be a combination of the two. In practical silicon-silicon dioxide devices, an intrinsic U-shaped distribution is obtained, upon which is superimposed structure introduced by extrinsic impurities. The intrinsic spectrum can be separated into two groups of states due to the different response of the  $N_{ss}$  distribution to physical and chemical influences across the bandgap (16). The central portion is found to be particularly influenced by technological processing and the states here may be attributed to dangling bonds. The states that compose the rise towards the band edges are insensitive to a wide range of treatments and are thought to result from bond distortion and strain.

Figure 2.4 Band diagram near the interface and the degree of occupancy of electron states and surface states. (a = single level; b = continuum of states) Flat band situation.

(34)

## 2.3 The Charge Approach

### 2.3.1 The Fermi Function

Surface states are localized energy levels that can be occupied by electrons. The degree of occupancy of all levels, including surface and energy band states, is determined by the Fermi function,  $F(E)$ , given below and shown in figure 2.4. In the expression, degeneracy factors have been ignored: normally, these are equal to 1/2 or 2, but in many situations, for example those where multivalent impurities are involved, the spin degeneracy factor can depart from these two values.

$$F(E) = 1/(1 + \exp(E - E_F)/kT) \quad (2.4)$$

where:

$E$  = Energy of the state

$E_F$  = Fermi (level) energy

$k$  = Boltzmann's constant

$T$  = Absolute temperature

Energy levels far below the Fermi level are occupied since  $F(E)$  is approximately equal to one, whilst those far above are essentially empty. Whenever the Fermi level is shifted with respect to the band edges, the occupancies of the energy levels will alter, particularly those close to the Fermi level. It follows from the latter that the states close to the Fermi energy usually dominate the electrical response of the structure. Positive holes obey the same statistical laws as electrons and their behaviour can be described in terms of the same parameters. If  $F(E)$  is the fraction of quantum states occupied by electrons, then  $(1 - F(E))$  is the fraction occupied by holes. Thus

the Fermi function for these particles is:

$$1 - F(E) = 1/(1 + \exp(E_F - E)/kT) \quad (2.5)$$

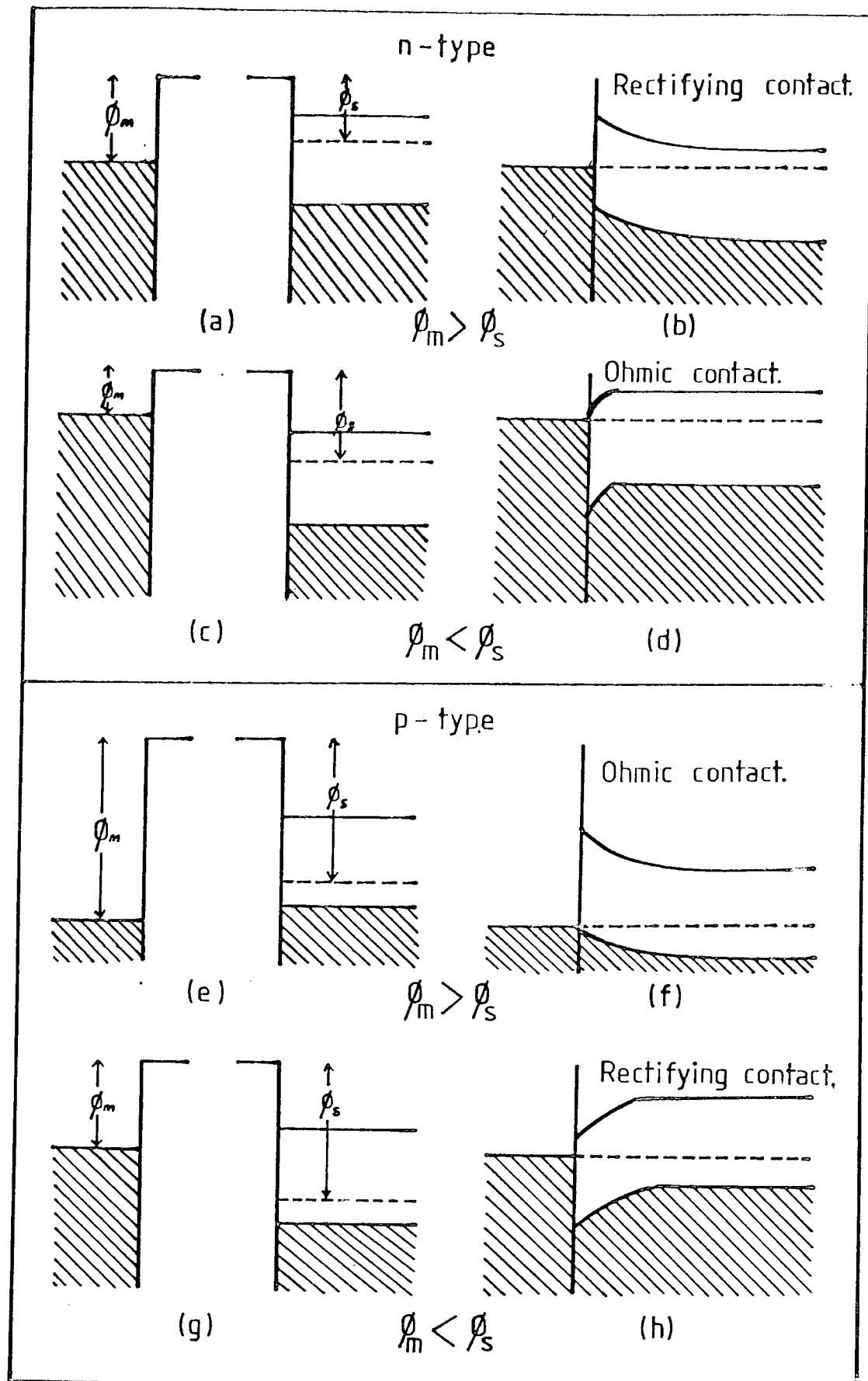

The energy required to eject an electron at the Fermi energy to the vacuum level is defined as the work function,  $\phi$ , of the material. When a metal and semiconductor are joined, it is the difference in their work function values that determines the nature of the contact between them. That is, to maintain a thermodynamic equilibrium, the two Fermi levels must coincide. In an ideal situation where there are no surface states, the flow of charge that results will give rise to a bending of the bands at the semiconductor surface. If the work function of the metal is the larger, then electrons flow from the semiconductor to the metal producing a depletion region in the semiconductor (see figure 2.5b,h). A potential barrier to electron flow from the metal to the semiconductor whose height is independent of applied potential is also formed. This is the situation normally envisaged for a Schottky barrier diode (17). Conversely, if the semiconductor has the larger work function, then electron flow is reversed and an Ohmic contact is obtained (see figure 2.5d,f). Unlike a Schottky barrier, an Ohmic contact permits current flow in both directions. However, the flow may not necessarily be Ohmic in nature, as the name implies; under certain conditions, space charge limited conduction can occur.

Figure 2.5 Energy band diagrams for metal/semiconductor contacts for p and n-type semiconductors.  $\phi_m, \phi_s$  are the work functions of the metal and semiconductor respectively.

## 2.32 The Surface Space Charge Region of the Semiconductor

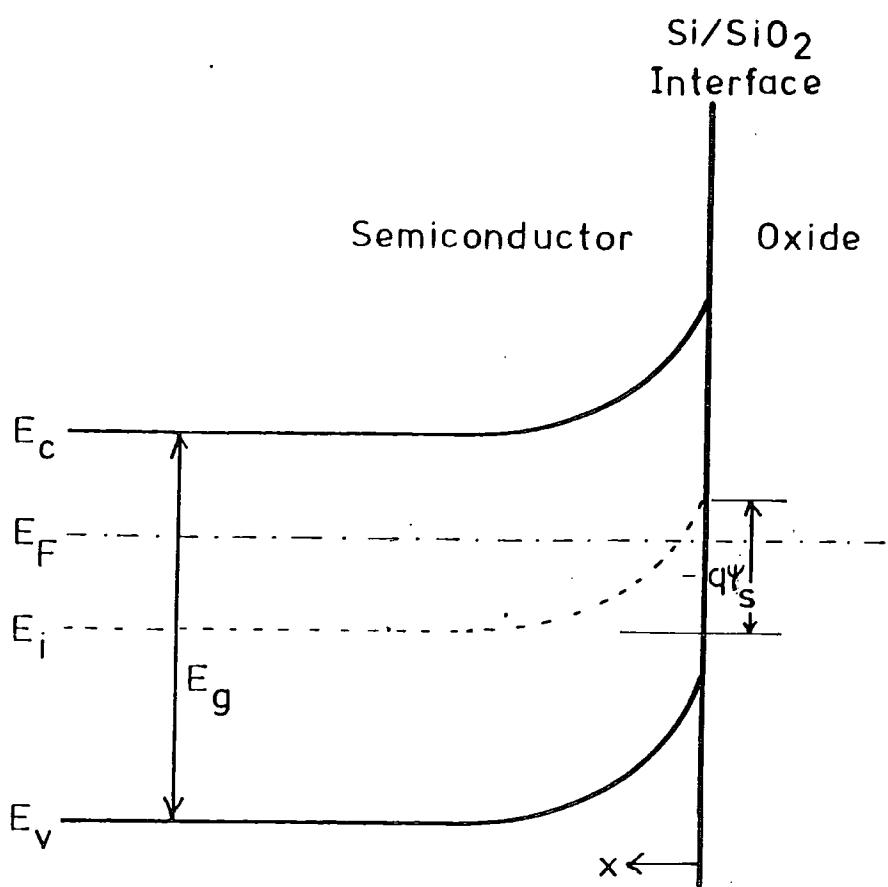

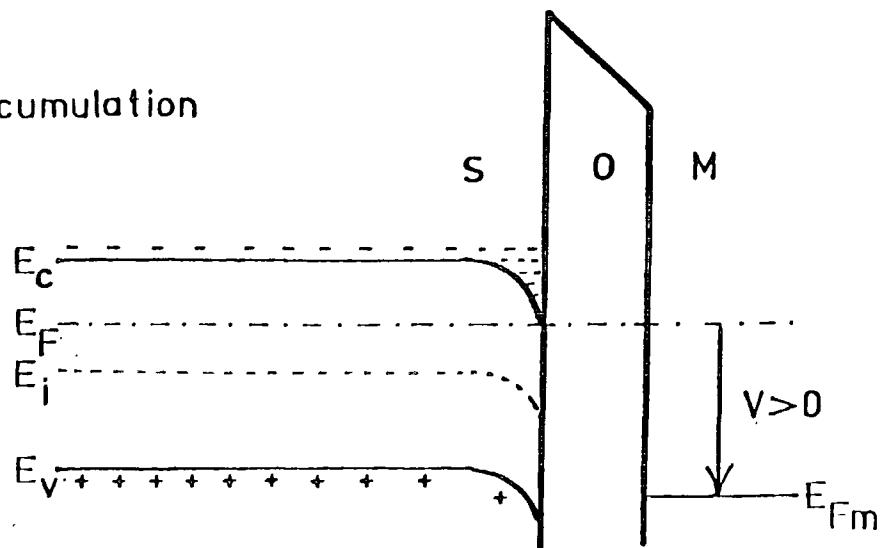

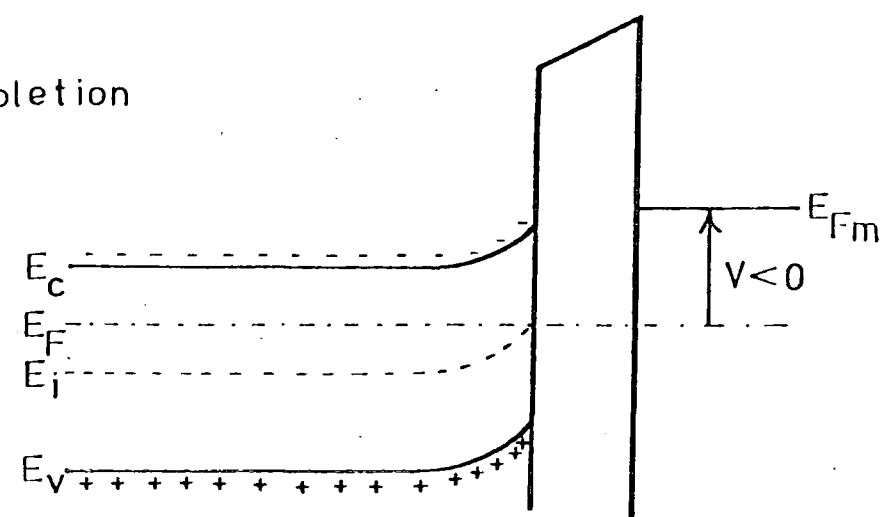

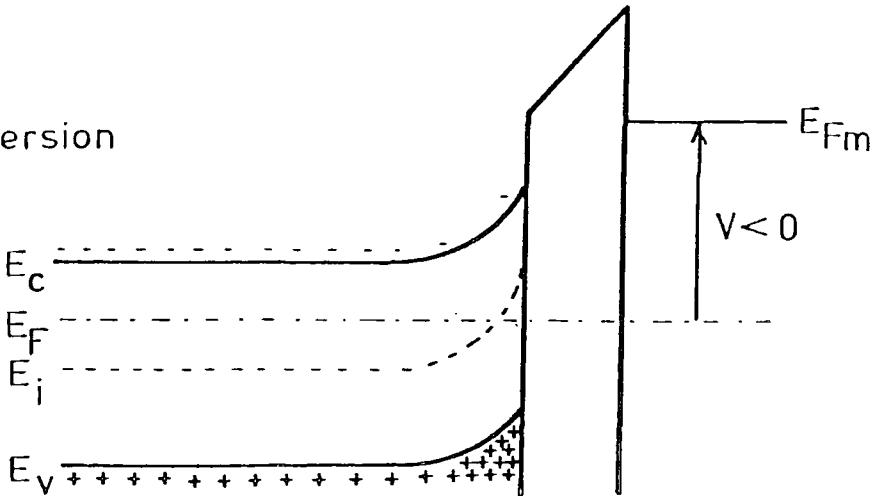

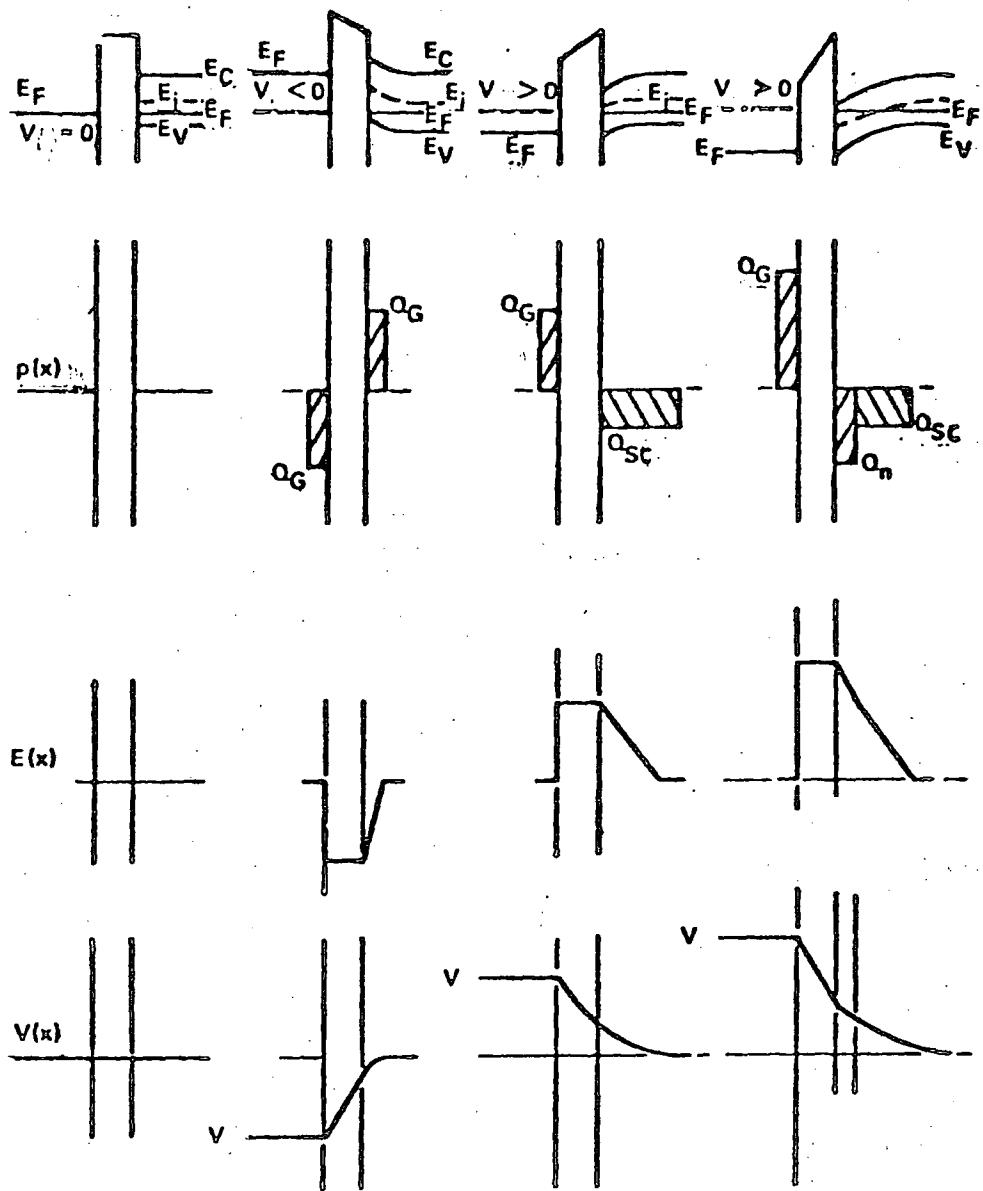

When a bias is applied to a Schottky barrier diode, the width of the depletion region alters, which in turn affects the amount of charge stored at the semiconductor surface. The charge storage situation is complicated when an interfacial layer exists between the semiconductor and the metal for, if the layer acts as an insulator, accumulation of free carriers at the semiconductor surface is possible. This structure is known as a metal-insulator-semiconductor diode (see figure 1.1). The state of the semiconductor surface can be classified by the value and polarity of the surface potential  $\Psi_s$ , which corresponds to the degree of bandbending and is defined in figure 2.6. Practically, there are three possible cases for a biased surface state free diode; these are shown in figure 2.7 for an n-type semiconductor (see figure 2.8a for a p-type semiconductor):

- a)ACCUMULATION, for  $\Psi_s < 0$  for p-type and  $\Psi_s > 0$  for n-type, majority carriers are attracted to the surface and accumulate there. The Fermi level at the surface is in the proximity of the majority carrier band edge.

- b)DEPLETION, for  $\Psi_s > 0$  for p-type and  $\Psi_s < 0$  for n-type, majority carriers are repelled from the surface leaving uncompensated ionized (donor or acceptor) impurities.

- c)INVERSION, if  $\Psi_s$  increases further, the minority carrier density exceeds the majority carrier bulk density and forms an inversion region. The onset of inversion corresponds to the point at which the Fermi level crosses the intrinsic Fermi level,  $E_i$ , at the surface.

Figure 2.6 Band diagram of an MIS diode (Depletion situation).

(a) Accumulation

(b) Depletion

(c) Inversion

Figure 2.7 Energy band diagrams for an MOS structure depicting (a) accumulation, (b) depletion, (c) inversion.

The surface potential may be substituted into the standard expressions relating bulk potential to concentration in order to obtain the electron and hole surface densities (18).

$$n_s = n_{\text{bulk}} \exp(q\psi_s/kT) \quad (2.6)$$

$$p_s = p_{\text{bulk}} \exp(q\psi_s/kT)$$

In addition the surface electric field, potential and charge concentration can be found by integrating Poisson's equation and by using Gauss's law (see figure 2.8).

When surface states are present, charge is distributed among these states and the silicon space charge region, such that the following charge neutrality condition holds:

$$Q_{\text{ss}} + Q_{\text{sc}} = -Q_G \quad (2.7)$$

where these quantities correspond to charge in surface states, in the silicon space charge region and at the metal electrode respectively. These quantities represent effective charges without regard to the complexity of their distribution; charge exchange equilibria also exist between these various regions.

## 2.4 The Capacitance Approach

### 2.41 Semiconductor Surface Capacitance

Since the net charge in the semiconductor varies as the surface potential across the surface layer is changed, a differential

(a) flat band (b) accumulation (c) depletion (d) inversion.

Figure 2.8 Band diagrams, charge, field, and potentials for a p-type substrate for (a) flat band, (b) accumulation, (c) depletion and (d) inversion.

capacitance,  $C_{sc}$ , can be associated with the semiconductor surface.

This capacitance per unit area is defined as:

$$C_{sc} = \frac{dQ_{sc}}{d\Psi_s} \quad (2.8)$$

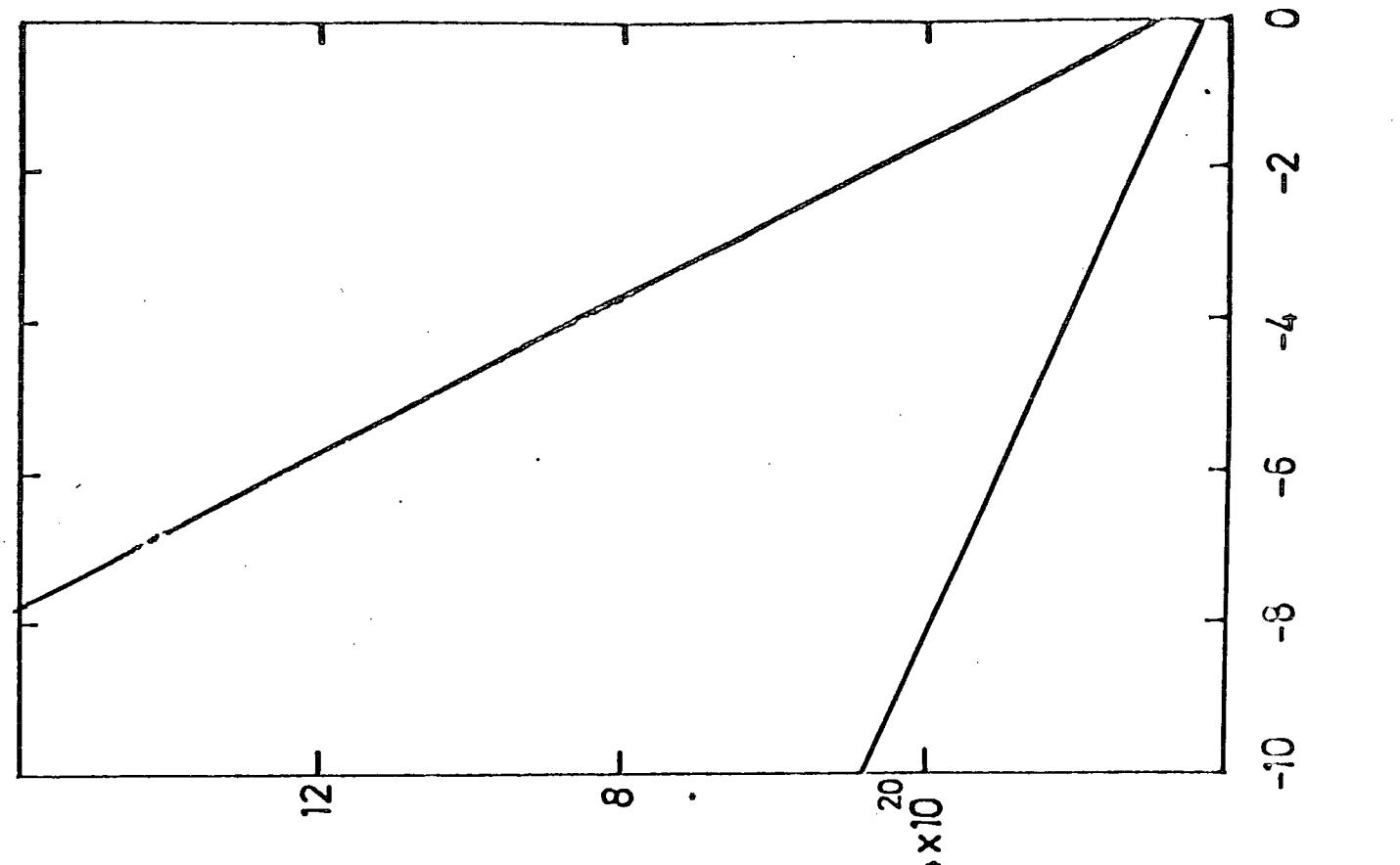

and it is measured by superimposing an alternating voltage upon the applied dc bias. For a Schottky barrier, the surface potential is directly related to the applied bias,  $V$ , and the semiconductor capacitance is simply:

$$C_{sc}^{-2} = \frac{2 (V_b - V - kT/q)}{\epsilon_s N_d q} \quad (2.9)$$

where  $V_b$  is dependent on the barrier height within the diode and  $N_d$  is assumed to be the constant doping density of the semiconductor. Experimental values for these can obviously be obtained from an appropriate plot of this expression. For an MIS diode, the relationship between capacitance and surface potential is far more complicated (19), although it does reduce to a similar expression to the above in the depletion region. In the depletion and accumulation regions, the semiconductor capacitance is independent of frequency but, in the inversion region, it depends on the ability of the minority carriers to follow the applied bias and/or ac signal.

A differential capacitance can also be associated with the charge in the surface states, when present, which is defined as:

$$C_{ss} = \frac{dQ_{ss}}{d\Psi_s} \quad (2.10)$$

Unlike  $C_{sc}$ , which is a unique function of  $\Psi_s$  for a given impurity concentration and temperature,  $C_{ss}$  depends upon the particular spatial and energy distribution of surface states, their occupancy as determined by an external field and the frequency of the ac measurement signal. Since the total surface charge is the sum of  $Q_{sc}$  and  $Q_{ss}$ , the semiconductor surface capacitance,  $C_p$ , is thus:

$$C_p = C_{ss} + C_{sc} \quad (2.11)$$

Therefore, it can be seen that the semiconductor surface capacitance is a parallel combination of  $C_{ss}$  and  $C_{sc}$ .

## 2.42 Capacitance of an Ideal MIS Diode

An MIS capacitor is formed by the addition of an insulator in series with the semiconductor, so the capacitance,  $C$ , of the whole structure is:

$$\frac{1}{C} = \frac{1}{C_{ox}} + \frac{1}{C_{sc} + C_{ss}} \quad (2.12)$$

where  $C_{ox}$  is the geometrical capacitance per unit area of the insulator. The voltage bias applied to an MIS diode falls partially across the insulator and partially across the semiconductor so

$$V_G = V_{ox} + \Psi_s \quad (2.13)$$

where  $V_{ox}$  is the voltage dropped across the insulator given by

$$V_{ox} = \frac{Q_G}{C_{ox}} \quad (2.14)$$

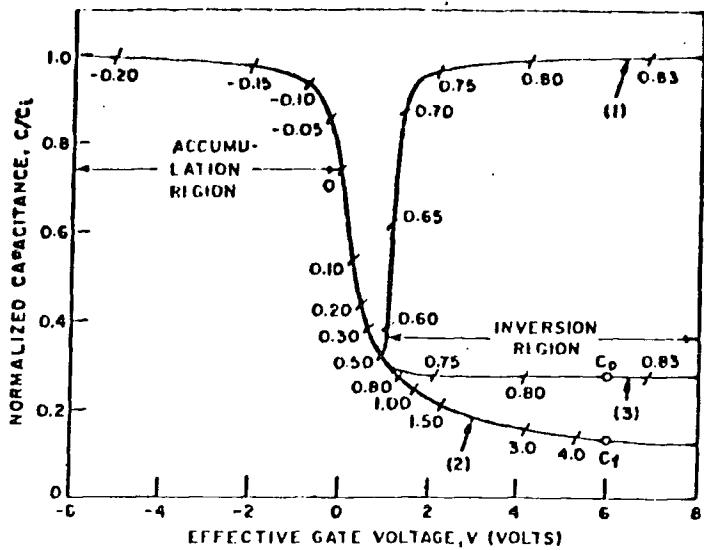

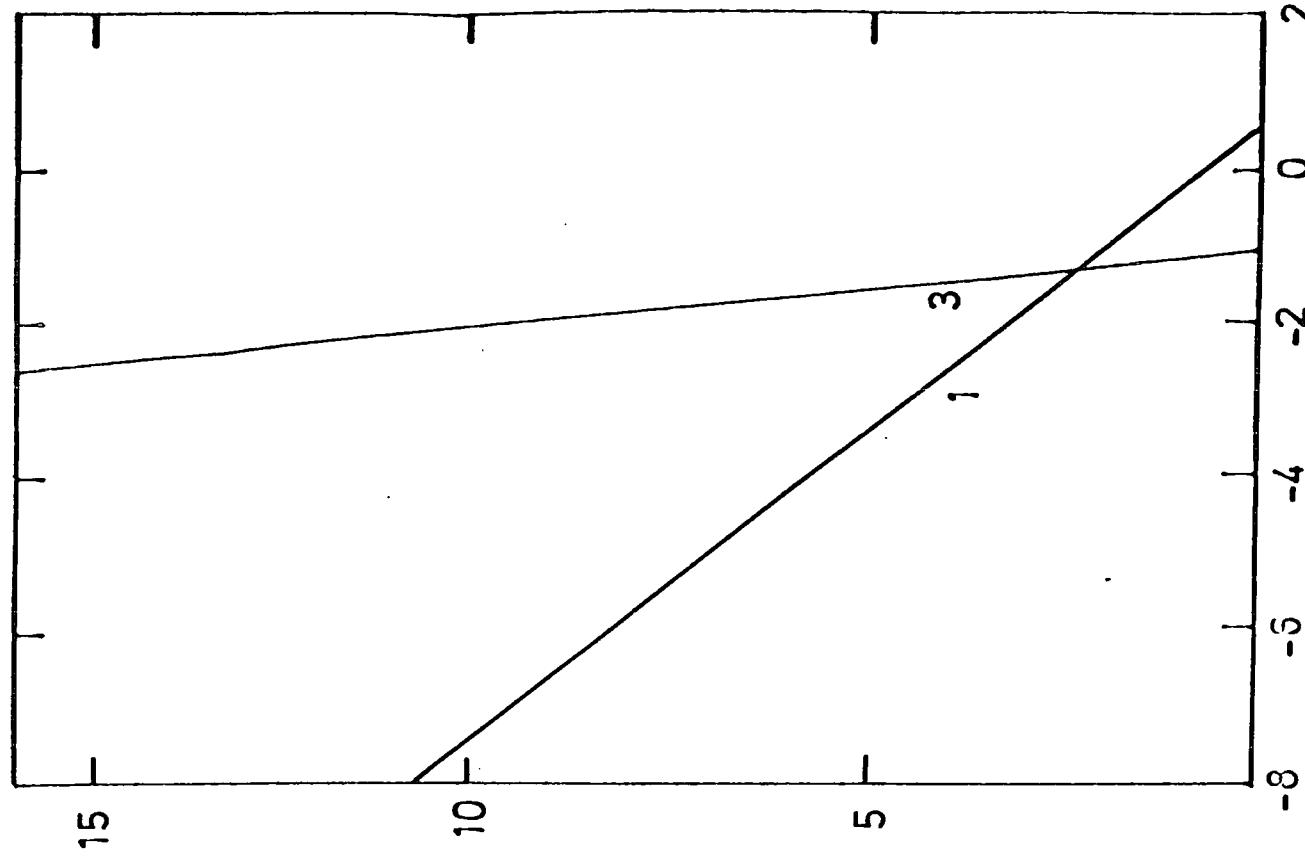

In an idealized case where the insulator is charge free, there is no work function difference between metal and silicon, and no surface charges exist; the C-V curve is called "ideal". Figure 2.9 shows such a curve with three different inversion options: (1) if the minority carriers can follow the applied ac signal; (2) if they cannot; and (3) if they cannot follow the ac signal but if they can follow the dc signal. The left of the curve corresponds to accumulation where there is a high concentration of majority carriers at the surface, holes in this case. As a result the total capacitance is close to the insulator capacitance. By increasing the applied voltage, the bands are made flat which corresponds to a surface potential of zero as indicated on the curve. Further increase produces a depletion region which acts as a dielectric in series with the insulator and therefore decreases the capacitance. Eventually inversion is reached and in equilibrium a minimum capacitance is obtained.

The shape of the capacitance-voltage characteristic varies for different insulator thicknesses and semiconductor doping densities. Goetzberger (20), has provided not only a set of ideal characteristics with respect to these two parameters, but also curves relating surface potential to applied voltage, and flat band capacitance to the above parameters.

In a real situation, the following cases can be differentiated:

(1) If no surface states are present but there is a non-zero work function difference between metal and silicon, there will be a parallel shift of the C-V curve without distortion along the voltage

Figure 2.9 Normalised MIS capacitance vs Gate Voltage for the case of no surface states. The value of the silicon surface potential is shown for several values of capacitance. (34)

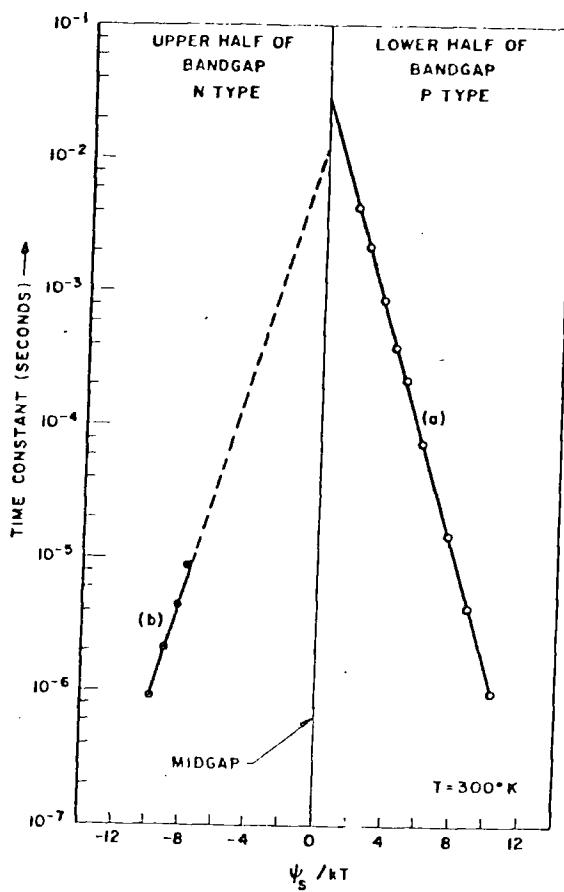

Figure 2.10 Variation of time constant with surface potential. ( $\psi_s$  plotted with respect to midgap) (18)

axis by an amount equivalent to this difference.

(2) If surface states are present whose occupation is independent of applied bias, a similar simple lateral shift will occur which is a measure of the charge in the surface states. These states <sup>might</sup> <sub>correspond</sub> to the defects  $:Si_{os}^+$  or  $C_3^+$  mentioned in section 2.3 that are either outside the band gap or too far into the oxide to respond.

(3) If surface states are present that do not follow the applied ac signal but whose occupancy depends on the dc bias (ie states that are within the silicon forbidden gap), the C-V curve will be displaced and distorted along the voltage axis, but the ratio of maximum to minimum capacitance will remain unchanged. This is the case for very high frequencies and forms the basis of the high frequency method of analysis as described in section 3.22. At lower frequencies the following situation prevails.

(4) If surface states are present that can follow the ac signal then they will displace and distort the C-V curve as well as change the ratio of minimum to maximum capacitance. Whether surface states can follow the applied signal depends on their inverse time constant as compared to the applied frequency. The variation of time constant through the band gap is given in figure 2.10 as a function of surface potential. It is important to note that the time constant is directly proportional to the surface potential: this will be used later.

## 2.43 Insulator Effects

The above assumes that an ideal insulator is present, but real insulators possess defects that introduce instability into the measured C-V curves. One type of instability is a hysteresis (19) in the measured response, ie the forward and reverse characteristics not overlaying one another. Particularly in early work with silicon dioxide, such hysteresis was caused by the presence of mobile sodium ions. A simple explanation of this phenomenon is that, as the applied bias is made more positive, positive sodium ions are repelled from the top contact to the semiconductor interface where they reside. Thus a larger negative bias is required to overcome their presence when the bias is reversed. If the insulator is a polarizable one, such as phosphosilicate glass, then a similar hysteresis direction will be observed; but since there is a large effective dipole layer within the insulator, the whole curve will be shifted laterally along the voltage axis.

Charge injection (21) into the insulator causes the opposite hysteresis direction. The initial bias now becomes important: a large value in accumulation causes injection from the metal whilst a large value in inversion causes injection from the semiconductor. If this biasing is done at elevated temperature, then large horizontal shifts in the measured C-V curves occur when the device is returned to room temperature. This is known as Bias Temperature Stressing and the results can be used to identify the nature of the particular instability (22).

We have also assumed that the carrier transport in the insulator is zero. However, real insulators do pass current, albeit small amounts, which can be characterized by various conduction mechanisms. Different ones exist depending on what factor dominates the current flow (18). In the case of Langmuir films, discussed in Chapter 7, the Poole-Frenkel mechanism has been found to be predominant where the current is given by

$$\ln J \propto \gamma_{PF} F^{1/2} / kT \quad (2.15)$$

in which  $\gamma_{PF} = 2(q^3/4\pi\epsilon_i\epsilon_0)^{1/2}$ . The actual process corresponds to hopping of carriers between localized states or traps within the bulk of the insulator. The factor 2 depends on the charged state of these traps and disappears if the trap can be regarded as neutral. The mechanism then resembles the Schottky one, and distinction can only be made by further experiments investigating contact and thickness effects. If the insulator is thin, tunnelling can occur; this is considered later in this chapter.

## 2.5 The Conductance Approach

The surface state response to an ac signal is also characterized by a loss. This is a consequence of the complex nature of the silicon band structure: more energy is required to fill the interface states than to empty them, since electron promotion involves additional phonon interaction. Therefore each cycle of the signal requires energy to be contributed by the source, and so the diode appears to have a resistive element (conductance). This conductance combined

with the capacitance of the surface states produces a time constant effect which means that the ac current produced will lag behind the applied signal. Put another way, it can be said that the non-instantaneous nature of the charge exchange processes will cause the measured current to be out-of-phase with the applied signal. The following sections calculate the values of the capacitance and conductance of the surface states for various distributions, starting with a single level situation and finishing with the experimentally encountered continuous distribution. As previously mentioned, the surface states that respond to the signal most are those nearest the Fermi level. This is because the fluctuation of the degree of occupancy is greatest at this point.

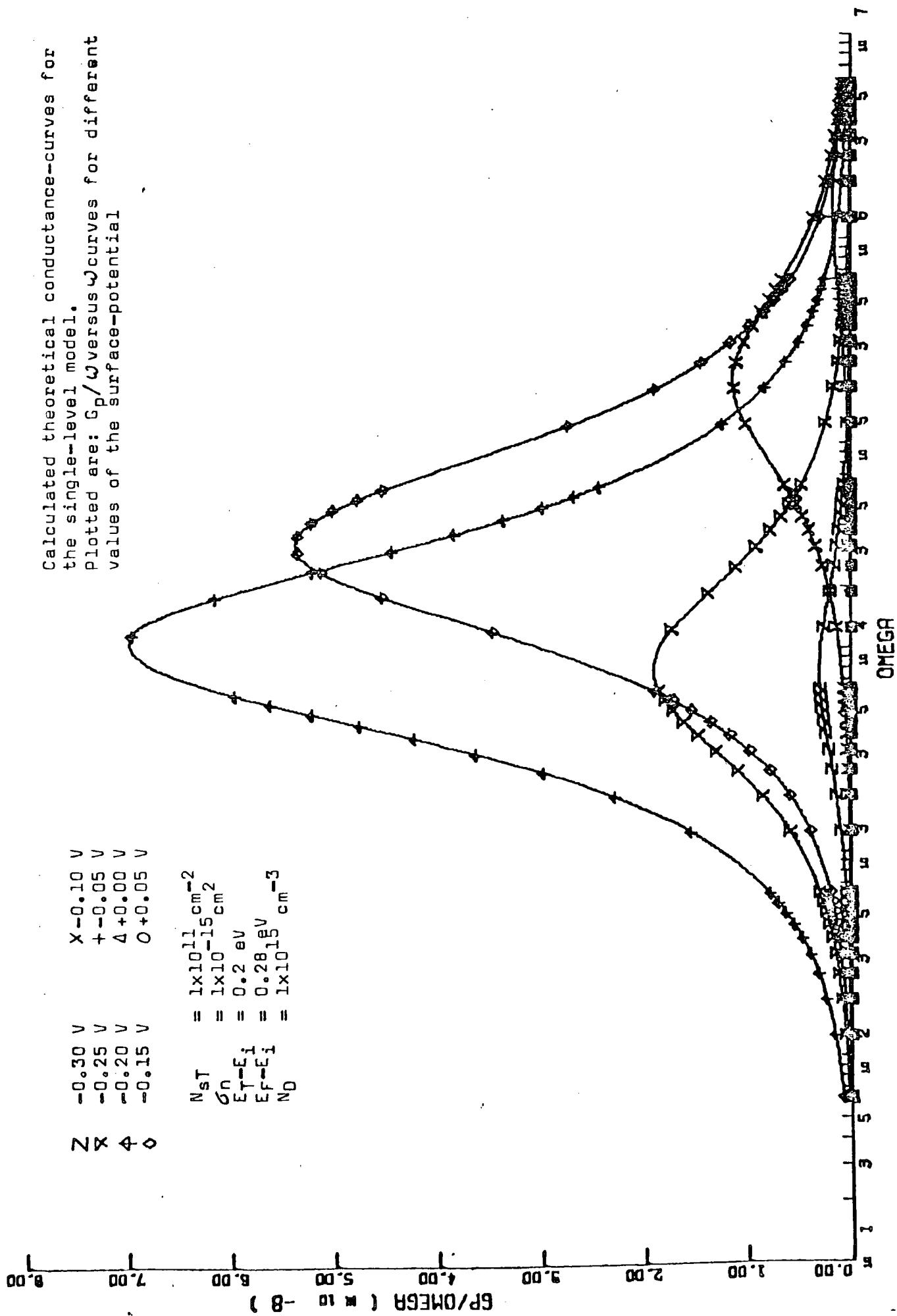

## 2.51 Admittance of a single level state

Let us consider first the case of a single level of surface states in the semiconductor bandgap. Nicollian & Goetzberger (23) have shown through consideration of Shockley-Read-Hall statistics that the admittance can be given as

$$Y_s = j\omega^2 q N_s F_{to} (1 - F_{to}) / (kT(1 + j\omega F_{to} / c_n n_{so})) \quad (2.16)$$

where

$\omega$  = period of applied ac signal (rad/s)

$n_{so}$  = electron concentration at the surface with no ac voltage applied ( $\text{cm}^{-3}$ )

$F_{to}$  = value of the Fermi function at the trap energy  $E_t$  with no applied gate voltage

$c_n$  = capture probability for electrons ( $\text{cm}^3/\text{s}$ ), which equals  $v_{th} \sigma_n$ , where  $v_{th}$  is the thermal velocity of electrons and  $\sigma_n$  their capture cross section ( $\text{cm}^{-2}$ )

$N_s$  = number of states in  $E_F(\text{cm}^{-2})$

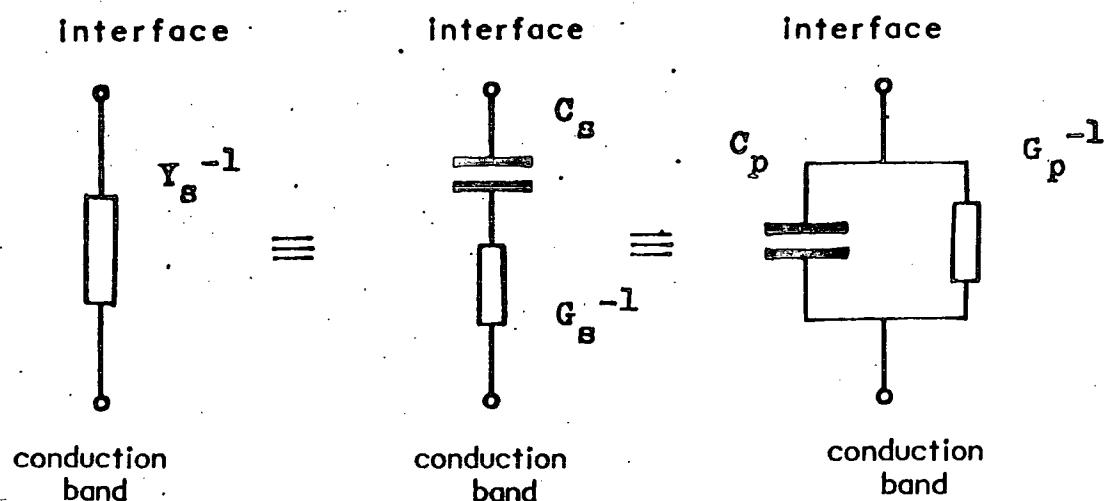

Inspection of the function  $Y_s$  shows that it corresponds to a series admittance of resistance  $G_s^{-1}$  and capacitance  $C_s$  (figure 2.11) where

$$\begin{aligned} Y_s^{-1} &= G_s^{-1} + 1/j\omega C_s \\ G_s^{-1} &= kT/(q^2 N_s (1-F_{to}) c_n n_{so}) \\ C_s &= q^2 N_s F_{to} (1-F_{to})/kT \end{aligned} \quad (2.17)$$

The time constant previously mentioned is defined as

$$\tau_s = G_s^{-1} C_s = F_{to} / c_n n_{so} \quad (2.18)$$

Both  $C_s$  and  $G_s$  are independent of frequency of the applied gate voltage, since they depend only on  $E_F$  and  $E_F$

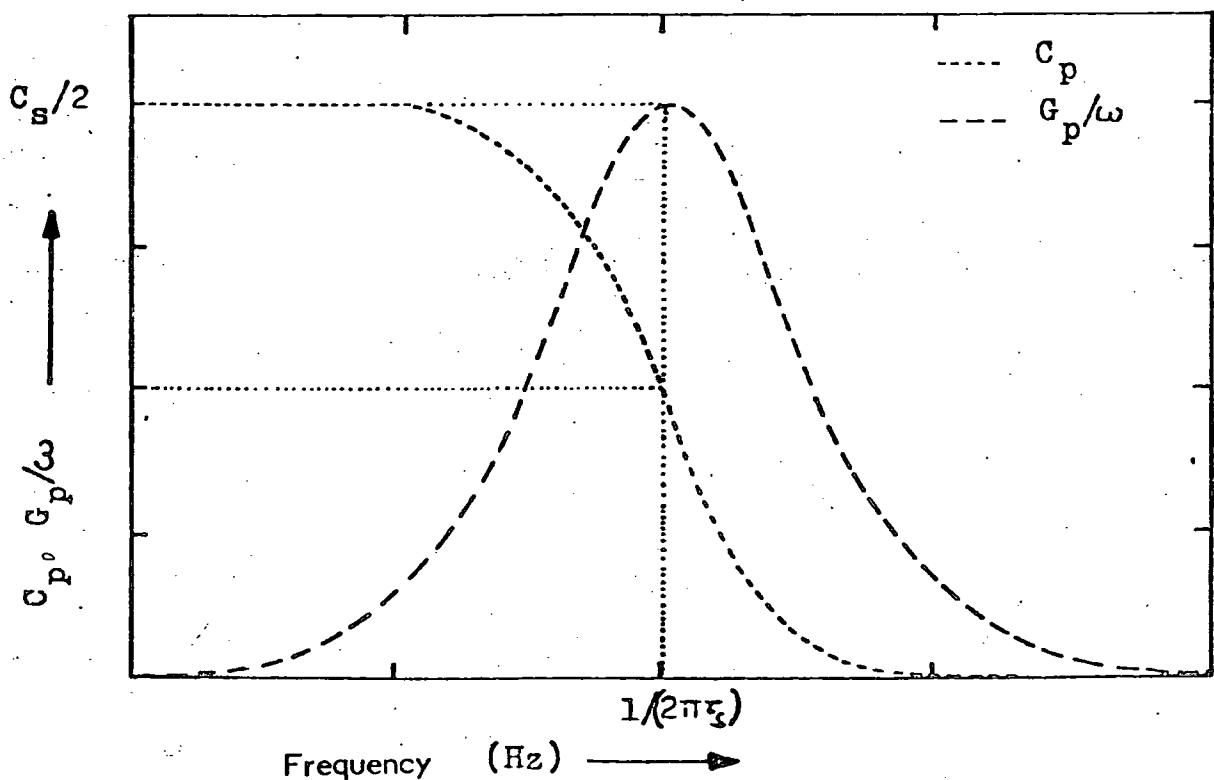

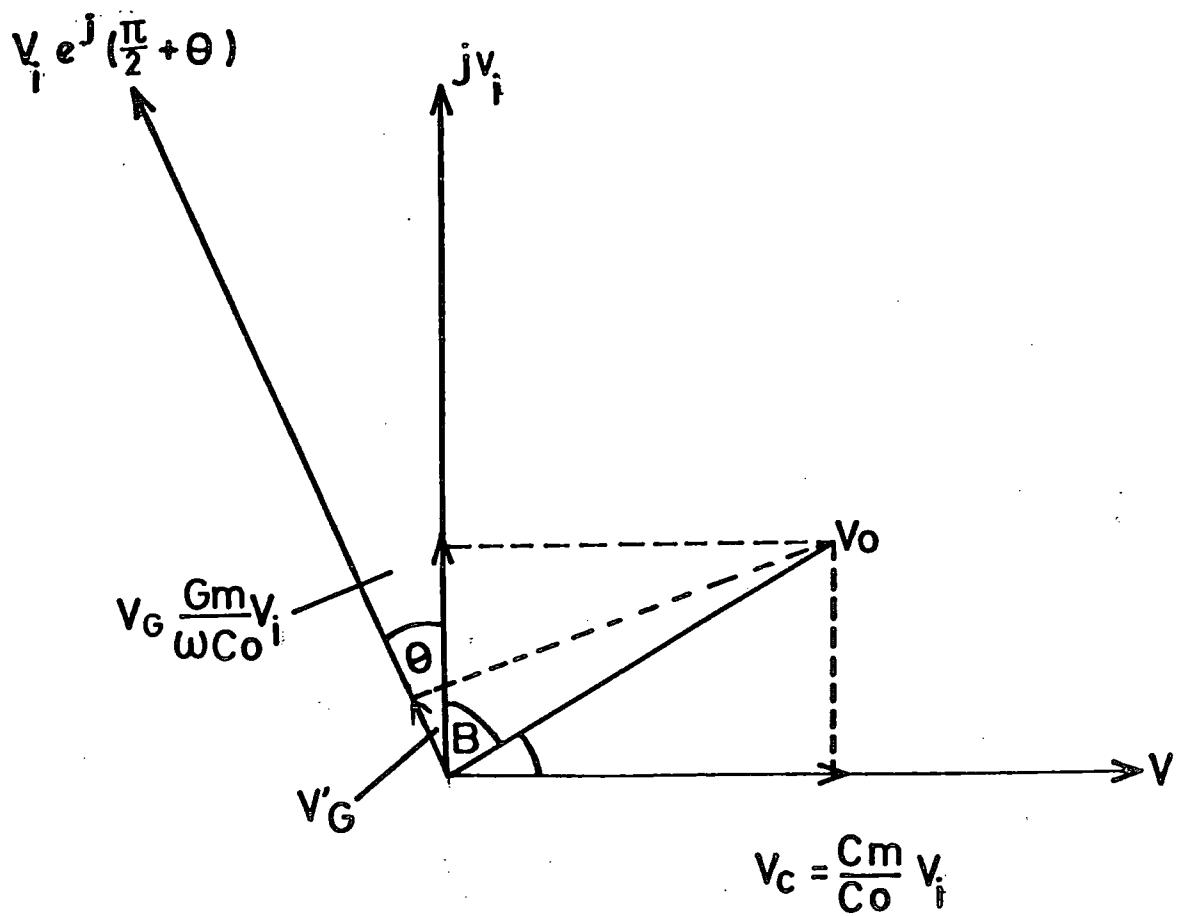

It is found to be more convenient to express  $Y_s$  in terms of a parallel conductance  $G_p$ , and a parallel capacitance  $C_p$  (figure 2.11)

$$\begin{aligned} G_p &= C_s \omega \tau_s / (1 + \omega^2 \tau_s^2) \\ C_p &= C_s / (1 + \omega^2 \tau_s^2) \end{aligned} \quad (2.19)$$

Thus

$$Y_s = G_p + j\omega C_p \quad (2.20)$$

Figure 2.11 Surface state admittance in the single level model.

(34)

Figure 2.12 Parallel conductance and capacitance vs. frequency in the single level model.

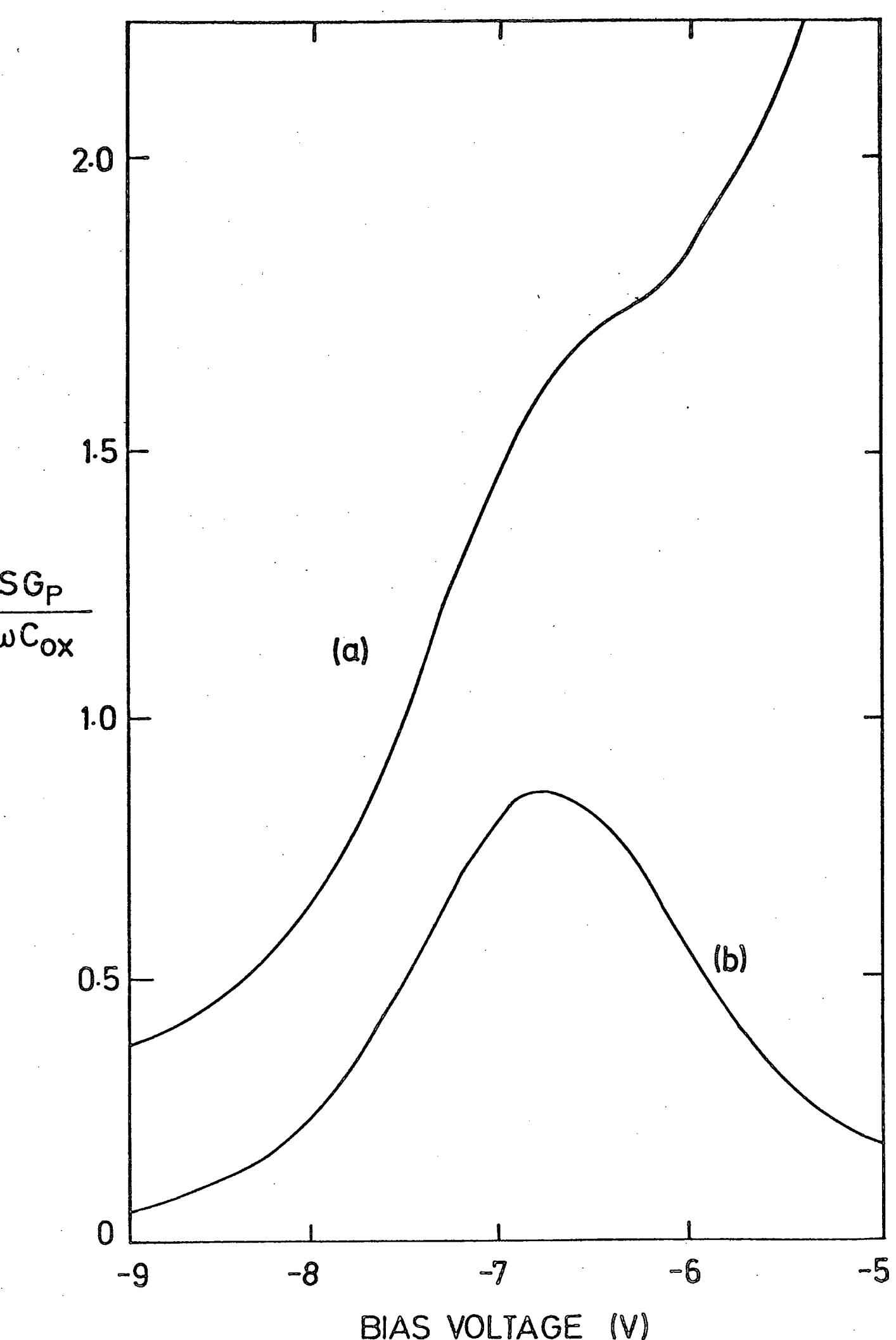

As can be seen in figure 2.12,  $G_p/\omega$  has a maximum as a function of frequency for  $\omega\tau_s = 1$ . The maximum of the  $G_p/\omega$  versus the position of the Fermi level at the surface occurs for maximum  $C_s$  ie for  $E_F = E_t$ . Thus if a  $G_p/\omega$  versus frequency plot is done at a bias such that the Fermi level is maintained at the trap level which gives  $F_{to} (1-F_{to})=1/4$  then

$$G_p/\omega (\text{max}) = C_s/2 = q^2 N_s / 8kT \quad (2.21)$$

Therefore it can be seen that the surface state density can be evaluated. Of course we can obtain  $C_s$  from a measurement of  $C_p$ , but in practice the extraction is difficult since a value of  $C_{sc}$  needs to be accurately known first, which can lead to error. This point will be returned to in the next chapter when various analysis methods are considered.

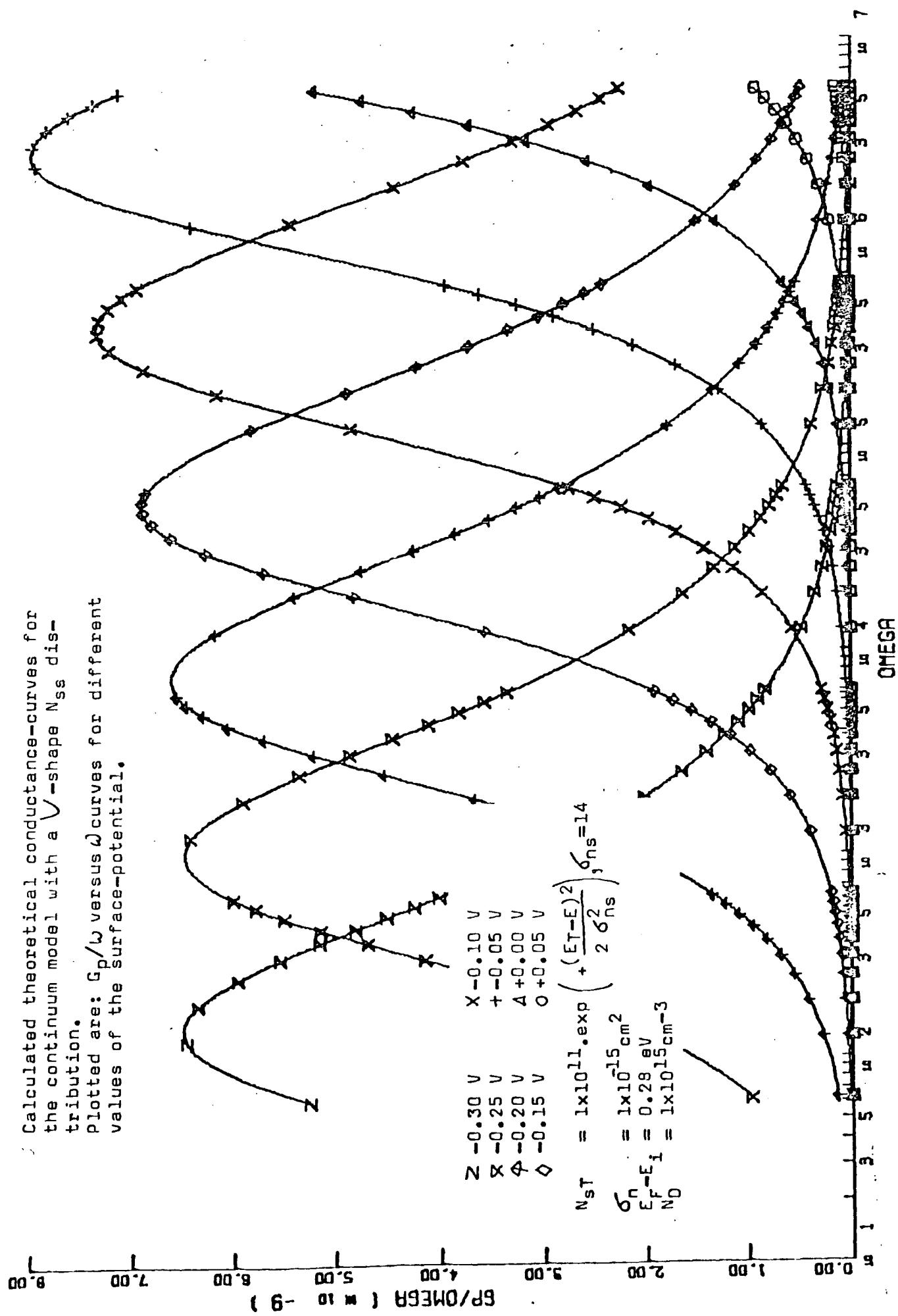

Unfortunately, experimental conductance curves do not display the single time constant character of the single level model (except in the inversion region which does not interest us): they are much broader. This is due to the fact that, as outlined in section 2.2, the surface state distribution in practical device is more complicated, being of a continuous nature rather than a single level. In order to account for this, Nicollian & Goetzberger (23) have extended their model, as outlined in the next section.

## 2.52 Admittance of a Continuum of Surface States

We can envisage a continuous distribution of surface states as a set of infinitely close single levels. In the electrical analogue, we can obtain the total admittance  $Y_{ss}$  by connecting all the single levels in parallel. Mathematically this is represented by integrating  $Y_s$  over all the trap energies in the gap:

$$Y_{ss} = \int_{E_v}^{E_c} Y_s(E_t) dE_t = \frac{j\omega q^2}{kT} \cdot \int_{E_v}^{E_c} \frac{N_{ss} F_{to} (1 - F_{to}) dE_t}{(1 + j\omega F_{to} / c_n n_{so})} \quad (2.22)$$

The integral when it is evaluated (23) gives

$$Y_{ss} = \frac{qN_{ss}}{2\tau_m} \ln(1 + \omega^2 \tau_m^2) + \frac{j\omega qN_{ss}}{\tau_m} \arctan(\omega \tau_m)$$

$$\text{or } Y_{ss} = G_p + j\omega C_p \quad (2.23)$$

where

$$\begin{aligned} G_p/\omega &= qN_{ss} \ln(1 + \omega^2 \tau_m^2) / 2\omega \tau_m \\ C_p &= qN_{ss} \arctan(\omega \tau_m) / \omega \tau_m \end{aligned} \quad (2.24)$$

$$\text{with } \tau_m = 1 / c_n n_{so}$$

The expression for  $Y_{ss}$  is only correct if both  $N_{ss}$  and  $c_n$  are slowly varying functions of energy, because then we can treat them as constants in a limited area of energy. This is generally true for reasonable frequencies and systems.

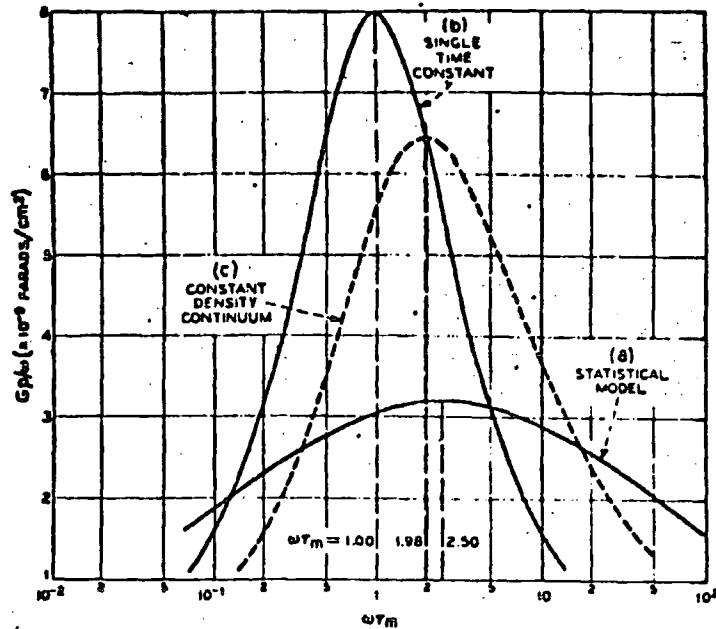

The resulting  $G_p/\omega$  versus frequency curves are wider than those for the single level case and the maximum now occurs for  $\omega\tau_m = 1.98$ . However, experimentally it is found that the parallel conductance curves with frequency are wider still and the maximum occurs at  $\omega\tau_m = 2.5$  rather than  $\omega\tau_m = 1.98$  (see figure 2.13).

### 2.53 The Surface Potential Fluctuation Model

Another factor is necessary to explain the discrepancy. If we assume that the built-in charges and charged interface states are randomly distributed in the plane of the interface, the electric field at the silicon surface will then fluctuate over the plane of the interface. Fluctuations in the electric field will cause corresponding fluctuations in the surface potential. There are several models (24) which take this into consideration and produce expressions for the parallel conductance of the device. Effectively, the previous expressions for parallel conductance and capacitance are integrated over the various surface potential values which means that the parallel conductance curves will have their maxima at different frequencies and will ensure that the resultant curve is broader. Unfortunately it is not possible to simplify the resulting expressions, and therefore the surface state information is found from a fitting of the theoretical curves to the experimental ones. This is accomplished accurately on a computer by adjusting the three variables  $c_n$ ,  $N_{ss}$ , and  $\sigma_s$  which represents the variance of the surface potential. The starting values of these variables can be obtained from the experimental curves using those equations derived for the

Figure 2.13 Calculated parallel conductance vs.  $\log \omega \tau_m$  for the three different theoretical models. (33)

Figure 2.14 Lehovec & Slobodskoy Equivalent Circuit.

continuum model.

Alternative, more expedient, techniques that do not require computer curve fitting are outlined in the next chapter. The benefits gained by the faster analysis are offset by the requirement for an accurate determination of the experimental curve maximum. The height of this is proportional to the surface state density.

#### 2.54 The Tunnelling Model

A different explanation for the experimental  $G_p/\omega$  curve broadening was proposed by Preier (25) based on work by Heiman & Warfield (26). They assumed that the interface states were not located at the interface, but were distributed into the oxide from where they communicated with the conduction band by means of tunnelling. Preier proposed that a variable tunnelling parameter should be used to fit the theoretical curves to the data.

A modification by Warashina & Ushirokawa (27) requires only a single set of measured capacitance and conductance versus bias curves for analysis. They have derived expressions for the parallel conductance which can be used around the maximum in the voltage domain to get the value of  $N_{ss}$ . However, their expressions are complex and the results obtained for  $N_{ss}$  seem to be double-valued in certain parts of the bandgap.

The tunnelling model has not received wide acceptance because most workers (24,28) have been unable to fit their experimental data to it, and also most do not find the predicted low frequency asymmetry in the parallel conductance curve. Therefore most prefer the surface

potential fluctuation approach of Nicollian & Goetzberger (23).

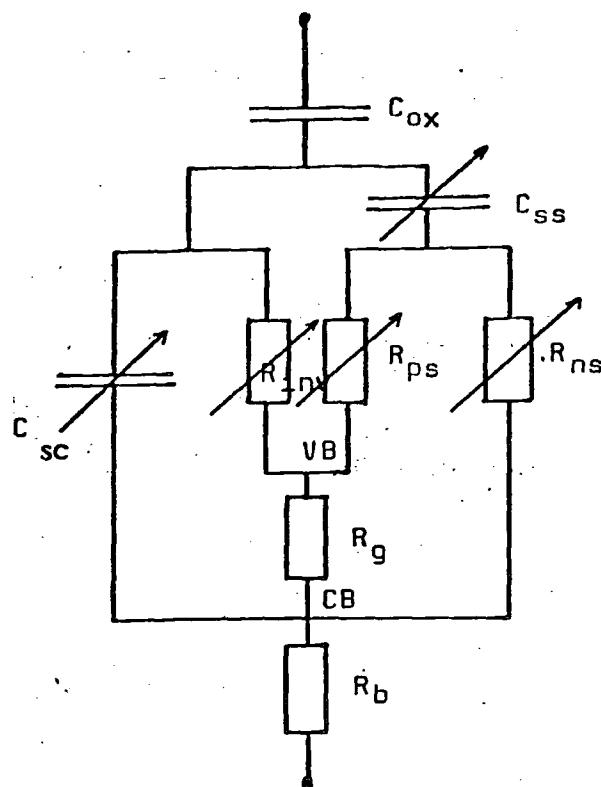

## 2.6 More Complex Equivalent Circuits

We now have the concept of a simple admittance of two effective elements to represent the surface states. Its validity, though, is limited to the depletion region, as the initial equations only included the charge exchange processes of the majority carriers. At other potentials, the action of minority carriers may have to be considered. A full equivalent circuit describing all bias situations has been derived by Lebovec & Slobodskoy (29) by following step by step the flow of charge from the bulk of the semiconductor to the interface under an ac excitation. Each loss can be associated with a resistance, whereas charge storage can be associated with a capacitance (see figure 2.14). The positions of the valence and conduction band can be seen with associated resistances  $R_{ns}$  and  $R_{ps}$  which represent charge exchanges due to electrons and holes.

$R_{inv}$  is a resistance representing the effects of the inversion layer and  $R_g$  is the bulk lifetime resistance. Using this model, a mathematical representation of the loss mechanisms of surface states outside the depletion region has been made (30): however, the matching of the representation to the experimental results is complicated and questionable. The analyses described in this thesis are restricted to the depletion region; even though this gives a limited range of surface potential, simplified analysis enables results to be obtained.

In the equivalent circuits so far, we have assumed that the insulator is thick and perfect; it has been shown (23) that for high accuracy the oxide must be as thin as possible. When it becomes very thin it reaches tunnelling dimensions when the carriers can pass through the insulator into either the conduction band or into the interface states themselves, depending on the insulator thickness. The latter also determines the additional components introduced into the equivalent circuit, which have been reviewed by Deneuville (31). It is possible to calculate the surface state density in spite of the added complication; for example, Kar & Dahlke (32) have obtained values for surface state density over the whole of the bandgap.

Finally, an additional complication when dealing with p-type samples is the interaction of the charge beneath the top contact with an external inversion layer that has been formed by positive charge within the insulator. The process is known as lateral ac current flow (33) and it introduces a second conductance peak into the admittance voltage characteristics. From an equivalent circuit point of view, a distributed resistance capacitance can be considered to have been introduced in parallel with the semiconductor capacitance.

## 2.7 Summary

In this chapter, the theoretical parameters used to describe the interface have been related to their physical origin and the electrical quantities used to measure them. This has been done by starting with a theoretical atomic perspective, developing through a

consideration of the role of charge exchange processes and finishing with an appreciation of the equivalent circuits involved. The approach has included a consideration of the effect of temperature, since its variation can be used to probe surface states close to the band edge. The same order will be preserved in the next chapter which contains a review of most of the current electrical methods that may be used to obtain surface state density information. The chapter begins with a consideration of capacitance techniques performed at room temperature and progresses through methods where temperature variation is important, finishing with the standard ac conductance method. Complications arise when temperature variation is used which, until the recent development of the DLTS technique, have meant a restricted range of measurement within the bandgap.

## Chapter 3

### Determination of Surface State Parameters from Measured Electrical Data

#### 3.1 Introduction

The current electrical methods fall into two main groups: first, those which measure charge in (quasi) equilibrium with the electric field; and second, the ones based on the transient charging and discharging of surface states. The former category covers most capacitance methods and the latter group encompasses the charge pumping, transient capacitance and low temperature hysteresis methods. The choice of technique is determined not only by the information required, but also by the practical ease of obtaining that information ie the complexity of measurement including preparation and data analysis. Since MIS devices are easy to fabricate, we have concentrated upon techniques that utilize them: thus the charge pumping technique (1) and simpler I-V curve (2) measurement procedures which require the use of MOS transistor structures are precluded from this discussion. However, the data analysis is not as straightforward; the required information is obscured by the influence of competing factors which can introduce imaginary surface state density values. In order to recognise and compensate for this, more complicated measurement or analysis procedures are necessary, but the result is a limitation in the valid range of the following techniques. These are now considered in turn.

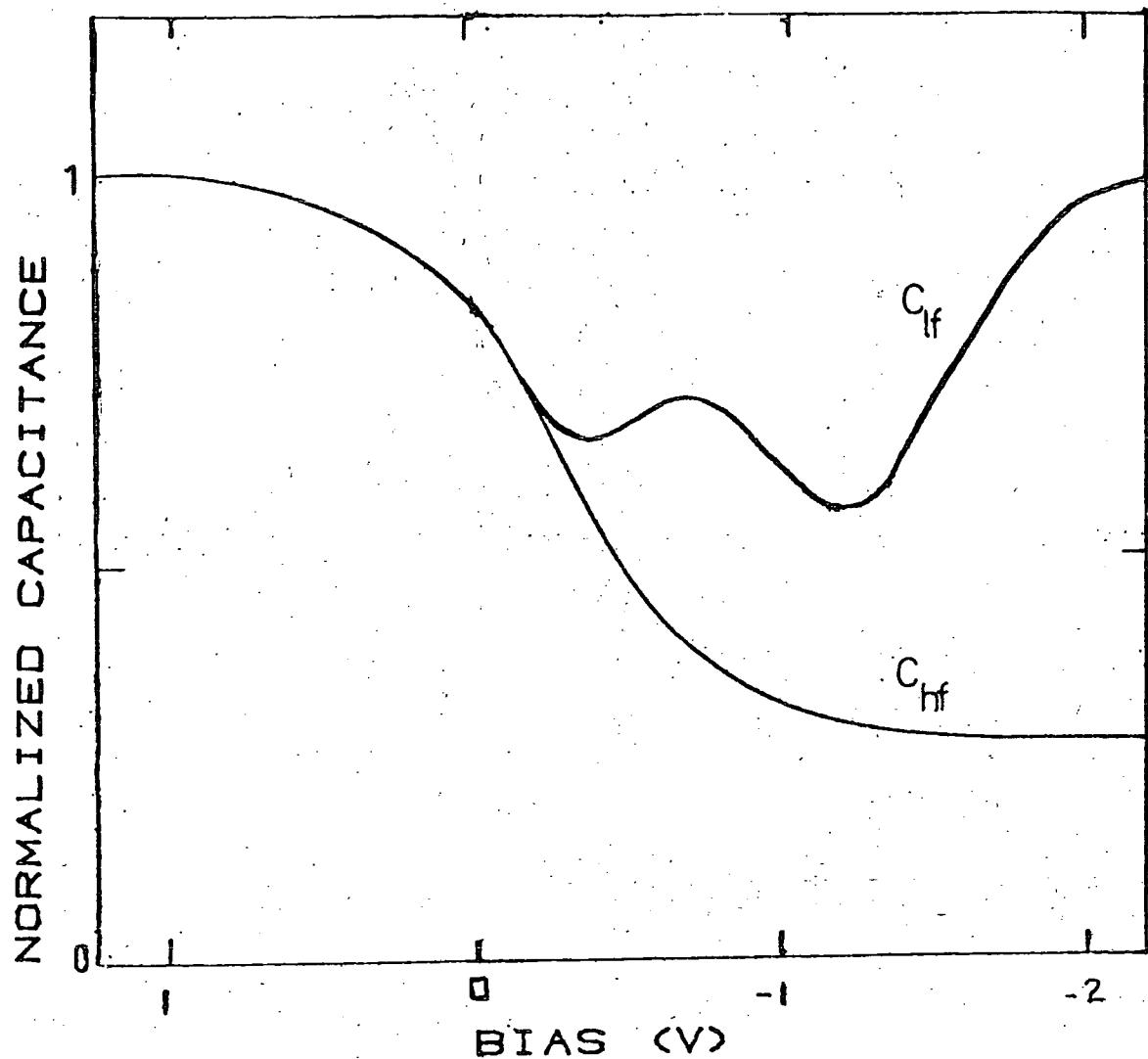

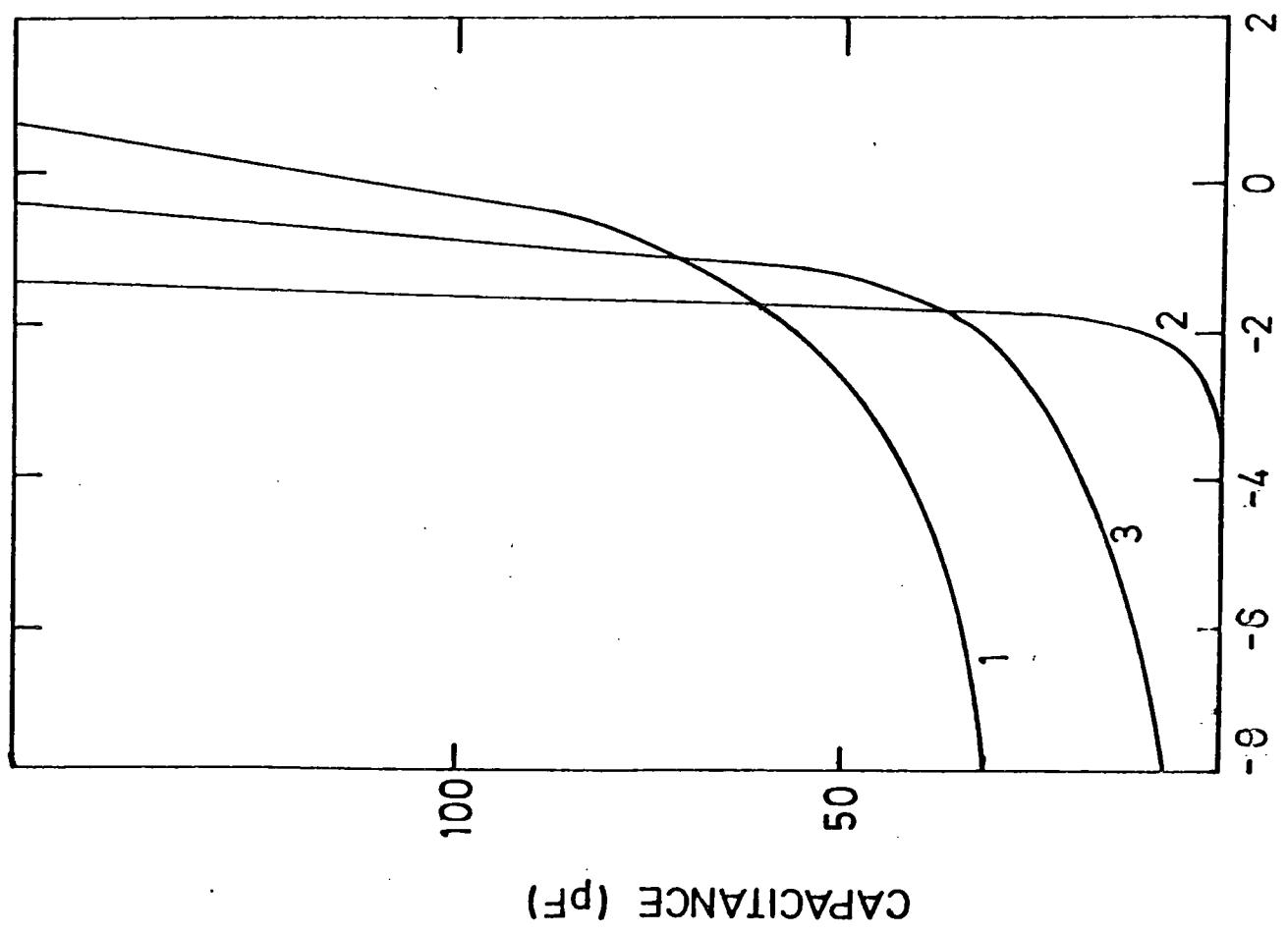

### 3.2 The Capacitance Techniques

The capacitance of an MIS device as a function of applied voltage may be determined under various conditions of frequency and temperature. The frequency of the ac measurement signal is important because different characteristics will be obtained, depending on whether or not the surface states are able to respond. At low frequencies, all the surface states are in equilibrium with the applied signal. However, as the frequency increases, less and less of the surface states are able to follow it and, at very high frequencies, none at all. The two methods outlined below are based at the frequency extremes.

#### 3.2.1 High Frequency Method

Terman (3) suggested that even though surface states did not respond to a high frequency signal, they would still be manifest through the presence of their trapped charge, which would give rise to a lateral shift in the high frequency C-V curve as compared to an ideal theoretical one. This displacement corresponds to an additional voltage,  $V_{shift}$ , developed across the oxide depending on the amount of trapped charge,  $Q'_{ss}$ , that appears for various band bending conditions. The resultant lateral shift for several different surface state distributions are given in figure 3.1. At each energy position:

$$Q'_{ss} = C_{ox} \cdot V_{shift} \quad (3.1)$$

Since  $Q'_{ss}$  represents the sum of the charge (integral) in the states, a graphical differentiation of  $Q'_{ss}$  versus surface potential is required to find  $N_{ss}$  as a function of energy:

Figure 3.1 High frequency capacitance-voltage characteristics with (continuous line) and without (dashed line) interface state distributions shown. States labelled A are acceptors and states labelled D are donors. (23)

$$N_{ss} = - \frac{1}{q} \frac{dQ'_{ss}}{d\Psi_s} \quad (\text{eV}^{-1} \text{ cm}^{-2}) \quad (3.2)$$

Zaininger & Warfield (4) demonstrated that the method was particularly sensitive to inaccuracies in the determined values of  $C_{ox}$  and the doping density used in the calculation of the ideal curve. These could give rise to effective surface state densities that do not really exist. Sah and co-workers (5) put forward improved formulae and curve fitting techniques for deriving these quantities thus overcoming the above problems. However, they did not take into account the effect of surface potential fluctuations which can also introduce spurious surface state densities (6,7). Finally, the measurement signal has to be very large to ensure that all the surface states do not respond; the standard frequency of 1MHz is inadequate for states near the band edges, where the reciprocal time constant is of this value, as figure 2.10 illustrates.

### 3.22 Low Frequency Method

At low frequencies, where the period of the measurement signal is long compared to the time constants of the surface states, there is a contribution from these states to the total capacitance. This means that simple equations, rather than graphical differentiation, can be used to determine the surface state density. Furthermore, the surface potential is easily found by integration of the experimental curve; in Terman's technique, it is found by comparison with the theoretical

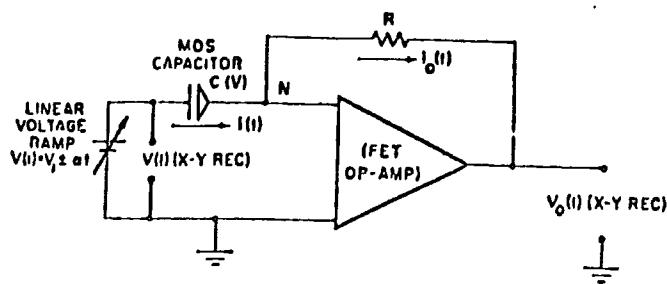

one. Berglund's (8) original technique is perfected in the quasistatic approach of Kuhn (9) where the low frequency becomes equivalent to zero with a dc voltage ramp. The displacement current produced is directly proportional to the low frequency capacitance:

$$i = \frac{dQ}{dt} = \frac{dQ}{dV} \cdot \frac{dV}{dt} = C_{If} (V) \cdot \frac{dV}{dt} \quad (3.3)$$

Now recalling the simple representation for the MIS device capacitance (see equation 2.5):

$$\frac{1}{C} = \frac{1}{C_{ox}} + \frac{1}{C_{sc} + C_{ss}} \quad (3.4)$$

It can be seen by rearrangement and assuming that  $C_{ss} = q.N_{ss}.A$

$$N_{ss}.q.A = \left( \frac{C_{If}}{1 - C_{If}/C_{ox}} - C_{sc} \right) \quad (3.5)$$

$C_{sc}$  can be theoretically calculated or derived experimentally from a high frequency curve. The latter is done by assuming that  $C_{ss}$  is zero in equation 3.4, thus equation 3.5 can be written as:

$$N_{ss}.q.A = \left( \frac{C_{If}.C_{ox}}{C_{ox} - C_{If}} - \frac{C_{hf}.C_{ox}}{C_{ox} - C_{hf}} \right) \quad (3.6)$$

Since it is not necessary to compute a theoretical curve, this equation is far easier to use. However, whereas equation 3.5 is applicable to the whole of the bandgap, equation 3.6 has a limited range depending on the measurement frequency such that  $C_{ss}$  is zero.

The interval extends from the inversion threshold to a value of the surface potential where the surface state time constant has just become equal to the ac signal period. For an ac frequency of 500 kHz this point is 250mV from the majority carrier band edge.

Again, as with Terman's method, if surface potential fluctuations are present, the theoretically calculated value for  $C_{sc}$  will be incorrect and give rise to an apparent  $N_{ss}$  (10). It is better to compare the high and low frequency curves, using equation 3.6, since the effects of the fluctuations will be approximately the same and counteracting. The error is expected to be small for large surface state densities, small surface potential fluctuations and for energy values near midgap resulting in an accuracy in  $N_{ss}$  values of about  $10^{10} \text{ cm}^{-2} \text{ eV}^{-1}$ .

The relation between surface potential and applied bias is obtained using the expression below

$$\Psi_s = \int_{V_{acc}}^V \left( 1 - \frac{C_{lf}}{C_{ox}} \right) dV + @ \quad (3.7)$$

The integration is done either numerically on a computer or direct from the equipment using electronic modules (11). The additive constant, @, may be determined in various ways; normally it is from the horizontal intercept of the inverse capacitance squared versus applied potential curve. Another technique

was suggested by Lopez (12); it calculates the total surface potential and compares it to the theoretical value of 1.1eV. The additive constant is simply the difference between the two.

### 3.23 Quasistatic Measurement Configuration

The basic circuit for performing quasistatic MIS C-V measurements is given in figure 3.2. It is essentially an analog differentiator incorporating the MIS device as the capacitive element. The amplifier ideally maintains point N of the circuit at ground potential so that the output voltage can be written as

$$V_o(t) = -RC(t) dV(t)/dt \quad (3.8)$$

Therefore when  $V(t)$  is a ramp of the form  $V(t) = \frac{+}{-} at$ , the output voltage is directly proportional to the differential capacitance,

$$V_o(t) = \frac{-}{+} aRC(t) \quad (3.9)$$

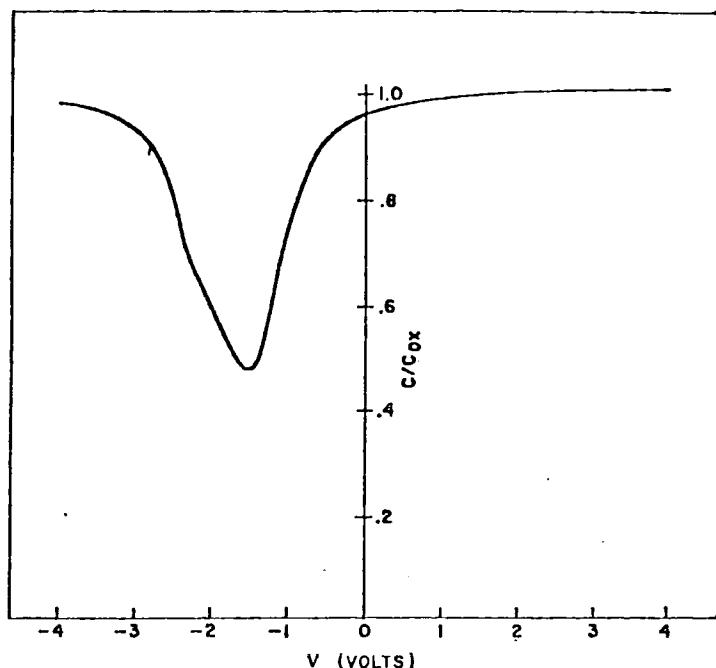

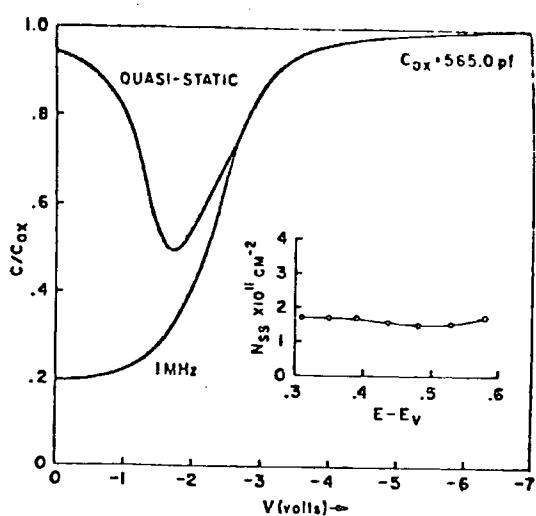

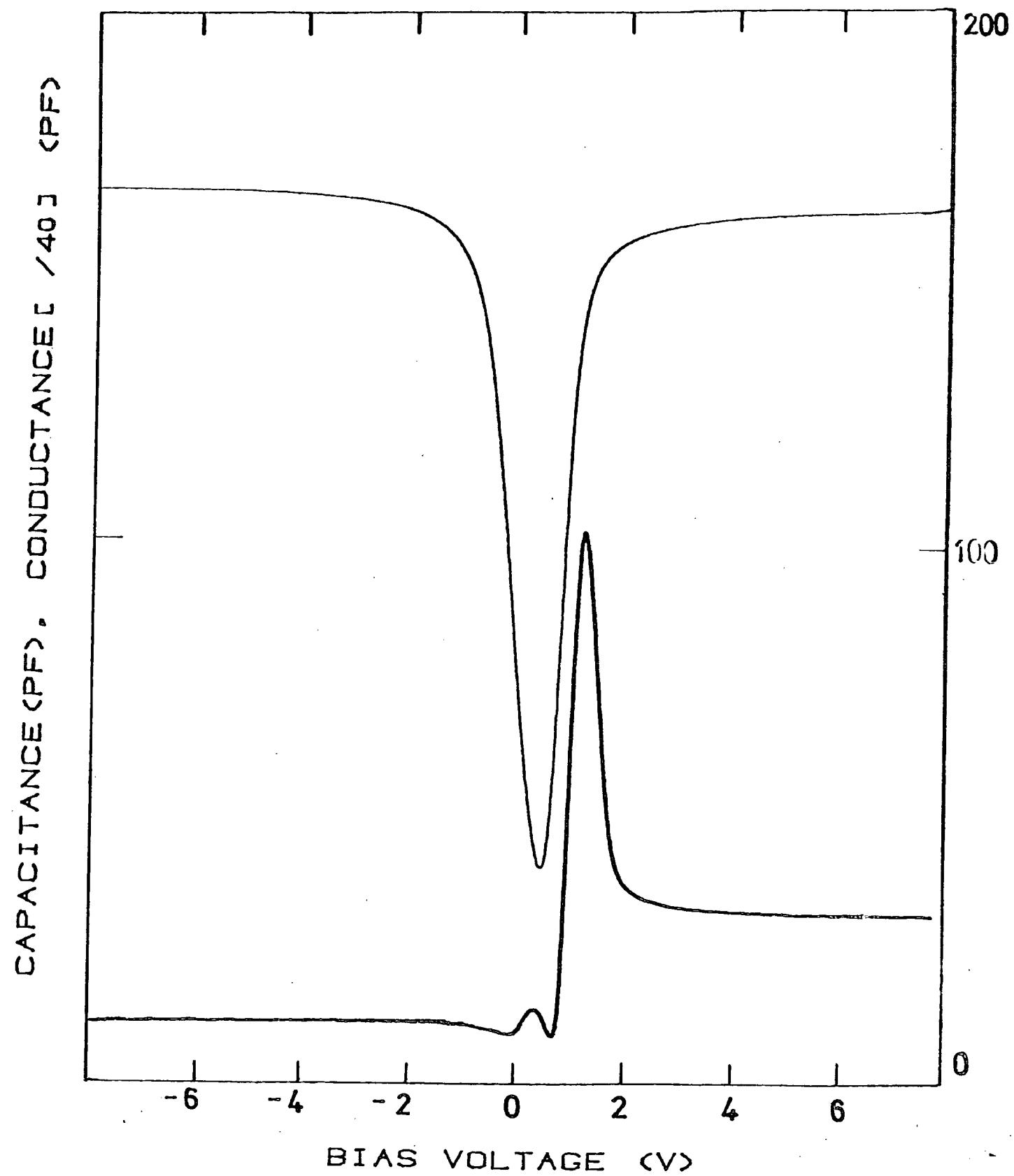

An example of a resultant plot is shown in figure 3.3; by superimposing a high frequency curve as in figure 3.4, the surface state density of the system can be calculated using equation 3.6.

### 3.3 Temperature Techniques

Alternatively, variation of the sample temperature can be used as a basis for obtaining surface state density information. The simplest technique (13) is related to Terman's method, where the high frequency capacitance curve is used to monitor the charge occupancy of the surface states. Instead of altering the bias, it is held constant and temperature change is used to sweep the Fermi level. Then, using expressions very similar to Terman's, surface state densities in a range from 0.2eV to 0.05eV near the majority carrier band can be obtained when the device is cooled to liquid nitrogen temperature.

Figure 3.2 Basic circuit required for quasi-static MOS C-V method.

Figure 3.3 MOS C-V curve obtained with the quasi-static technique for an n-type silicon MOS capacitor. (9)

Figure 3.4 Combined low and high frequency curves and corresponding surface state density.

The technique has drawbacks though: it is difficult to interpret the results over small temperature changes, and the method also produces anomalous peaks in  $N_{ss}$  close to the band edges that do not agree with the latest data. Recent computation (14) has shown that these may be due to the combined effect of an inadequately low measurement frequency and a decreasing capture cross section value nearer to the band edge.

### 3.3I Low Temperature Hysteresis Method

This technique only gives  $N_{ss}$  values averaged over a large portion of the band gap rather than with respect to energy (15). It relies on the difference in capture and emission times of carriers reacting with the surface states at liquid nitrogen temperature which causes a hysteresis in the high frequency C-V curves. This can be explained by considering a voltage cycle. Starting in accumulation, with only majority carriers filling the surface states, it is only after the device has reached inversion, where there is a high concentration of minority carriers, that the occupancy will alter. On going from inversion to accumulation, the states then remain filled with minority carriers. The difference,  $dV$ , in the two curves corresponds to the charge contained by the surface states.

$$Q'_{ss} = C_{ox} \cdot dV \quad (3.10)$$

and

$$N_{ss} = Q'_{ss} / q \cdot A \quad (\text{cm}^{-2}) \quad (3.11)$$

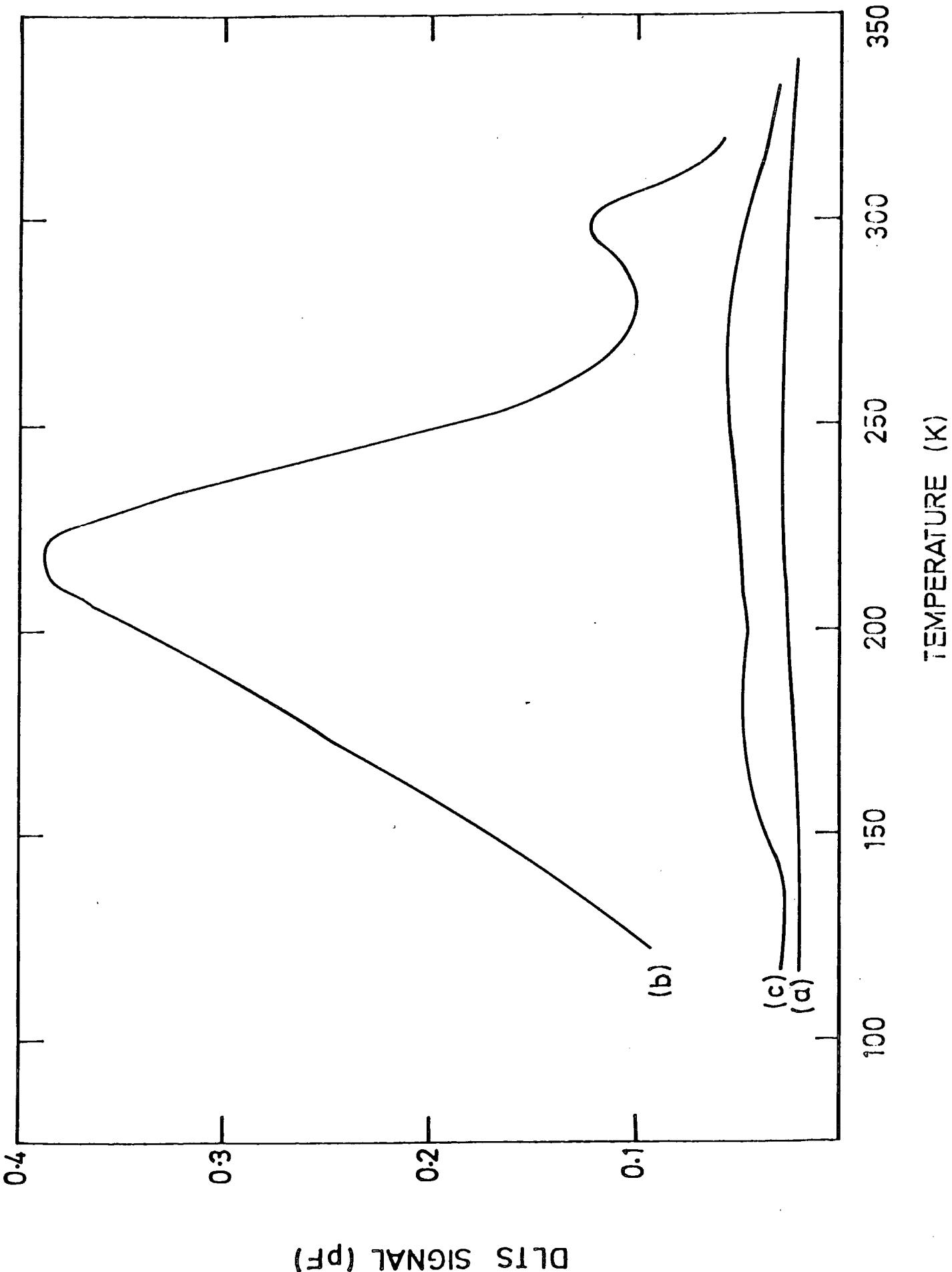

### 3.32 The Transient Capacitance Method

By actually measuring the emission processes, whilst scanning the temperature at the same time, far more information can be obtained. In the normal transient spectroscopy technique, an MIS capacitor is pulsed into accumulation and the resulting high frequency capacitance transient measured as the temperature is increased. The transient is a result of the return to equilibrium of the electron population in the depletion region which has been disturbed by majority carriers introduced by the applied voltage. The overall decay is monitored in the DLTS technique (16) through the use of a "rate window", which produces a peak in the output when the decay rate passes through a predetermined value. When the temperature is altered, the thermal emission rate and hence the capacitance decay rate change. This gives rise to such a peak, which can be used to calculate the surface state density. However, the equipment can be complicated (17), especially if it is to measure the smallest surface state emission times. The analysis, too, is not simple and there is even some doubt as to the validity of some interpretations(18).

We have not used temperature techniques because of the additional variable that would be introduced when considering gaseous interactions which could well be temperature dependent. We have concentrated upon the conductance technique, which is the standard, although a little time consuming. With the aid of a microcomputer, we have been able to cut down the effort involved in extracting the required information. Moreover, we have developed a novel technique that enables fast surface state determination; this is described in Chapter 5.

### 3.4 The Conductance Technique

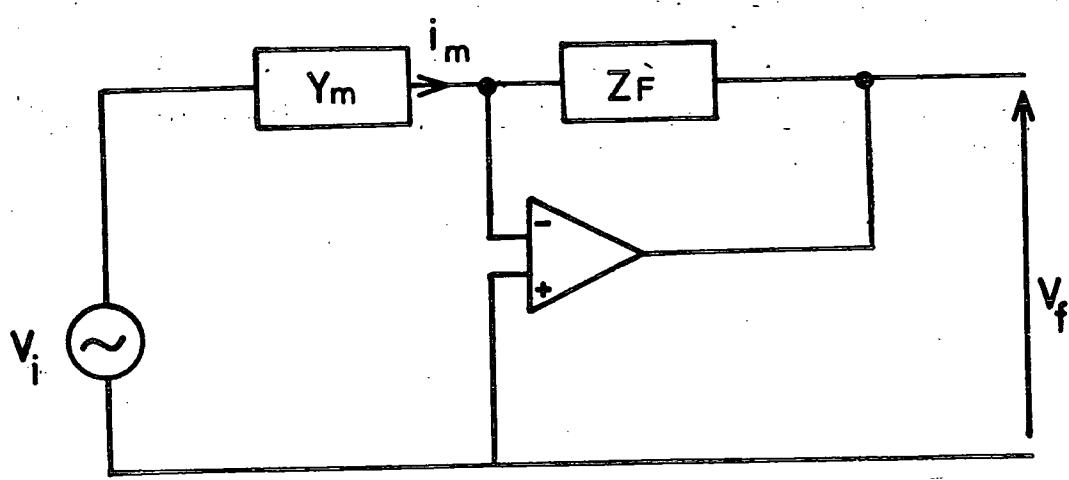

More information on interface states can be obtained if the loss mechanisms in the system are considered and a full frequency response is measured. This involves determining the small signal admittance of the MIS device resolved as a capacitance and conductance and extracting the parallel conductance using algebraic manipulation. The parallel conductance is then examined using the theory in section 2.5 and the surface state information calculated.

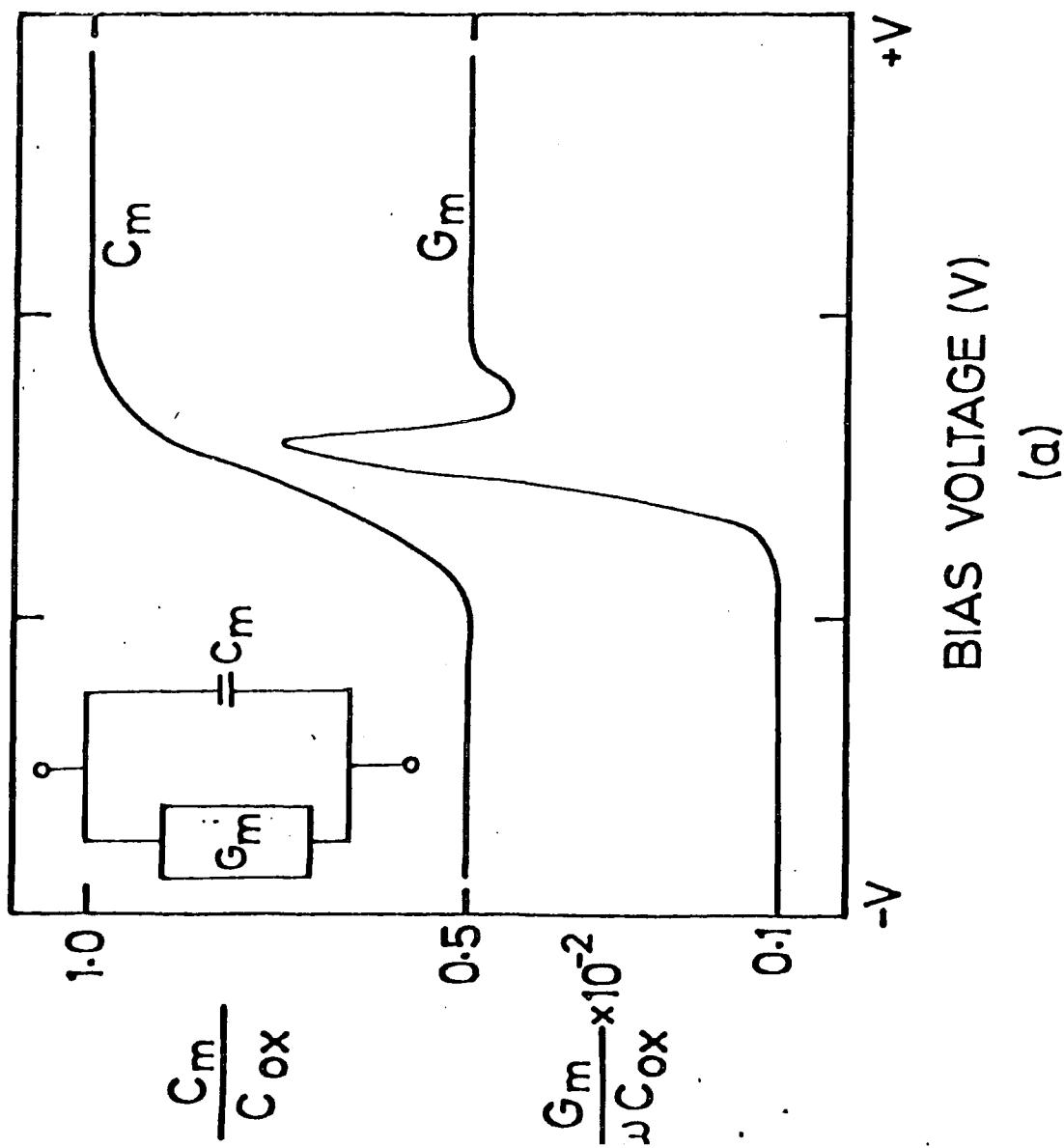

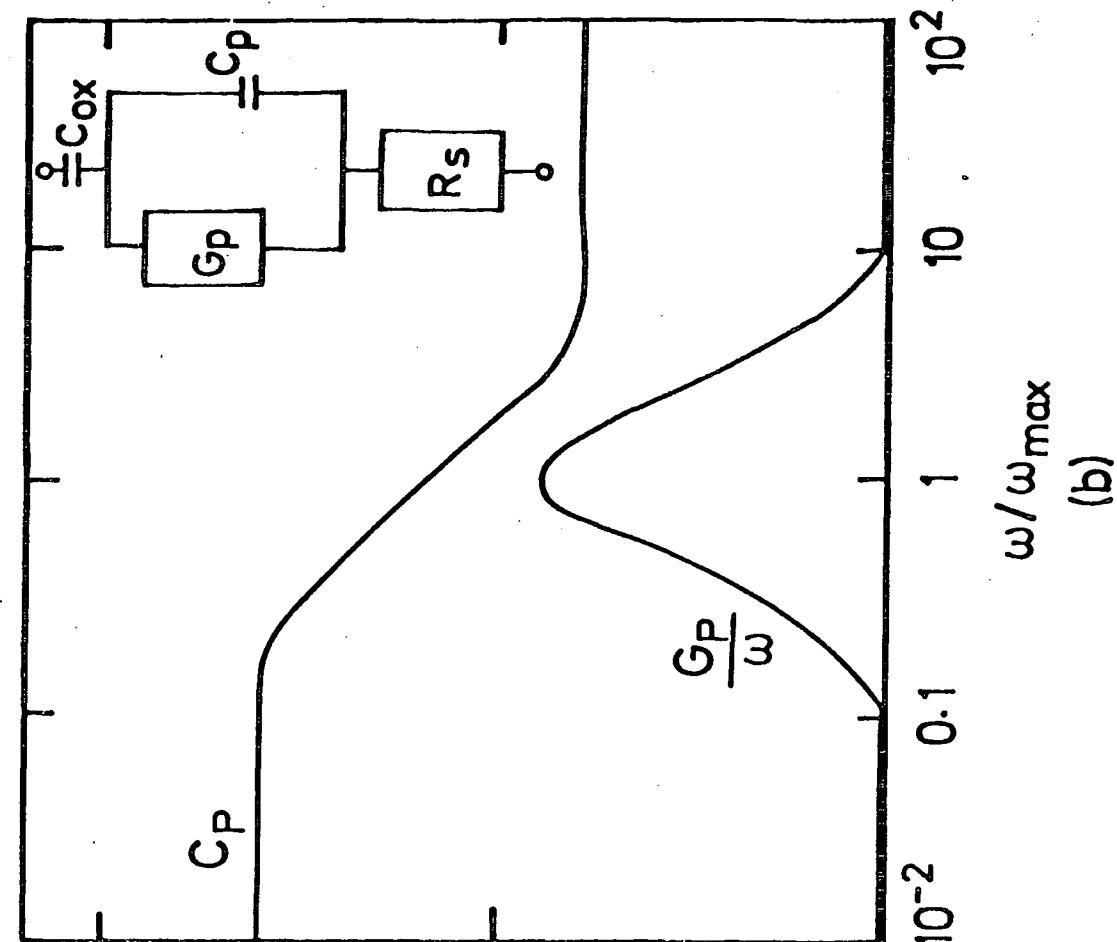

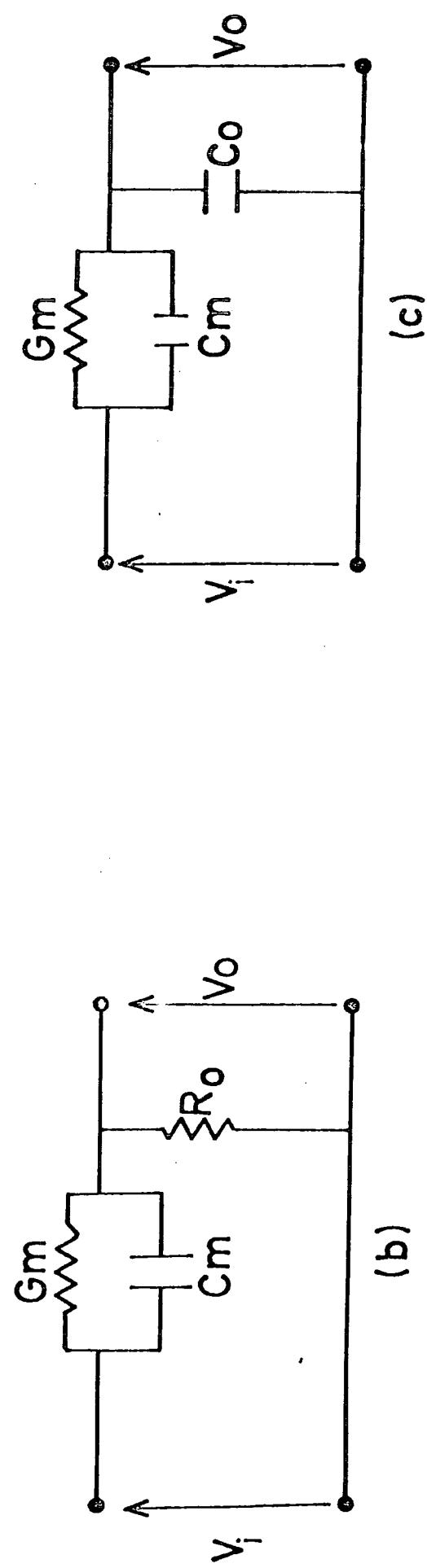

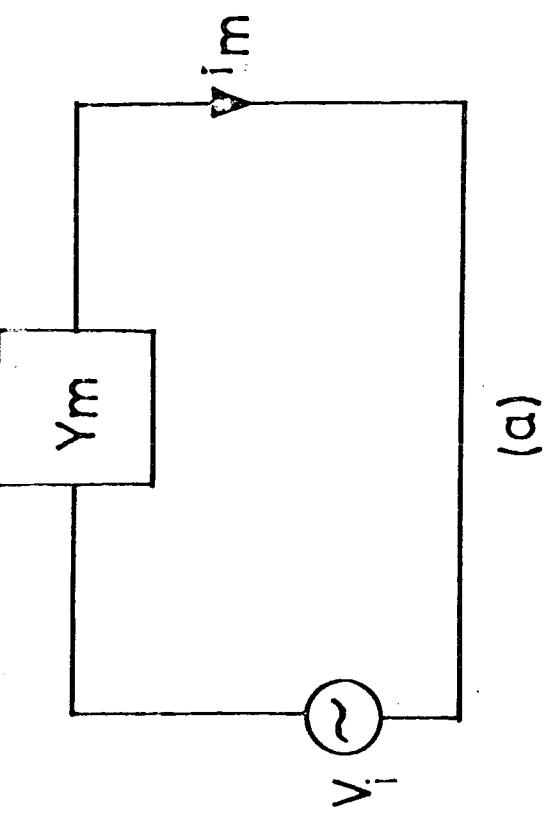

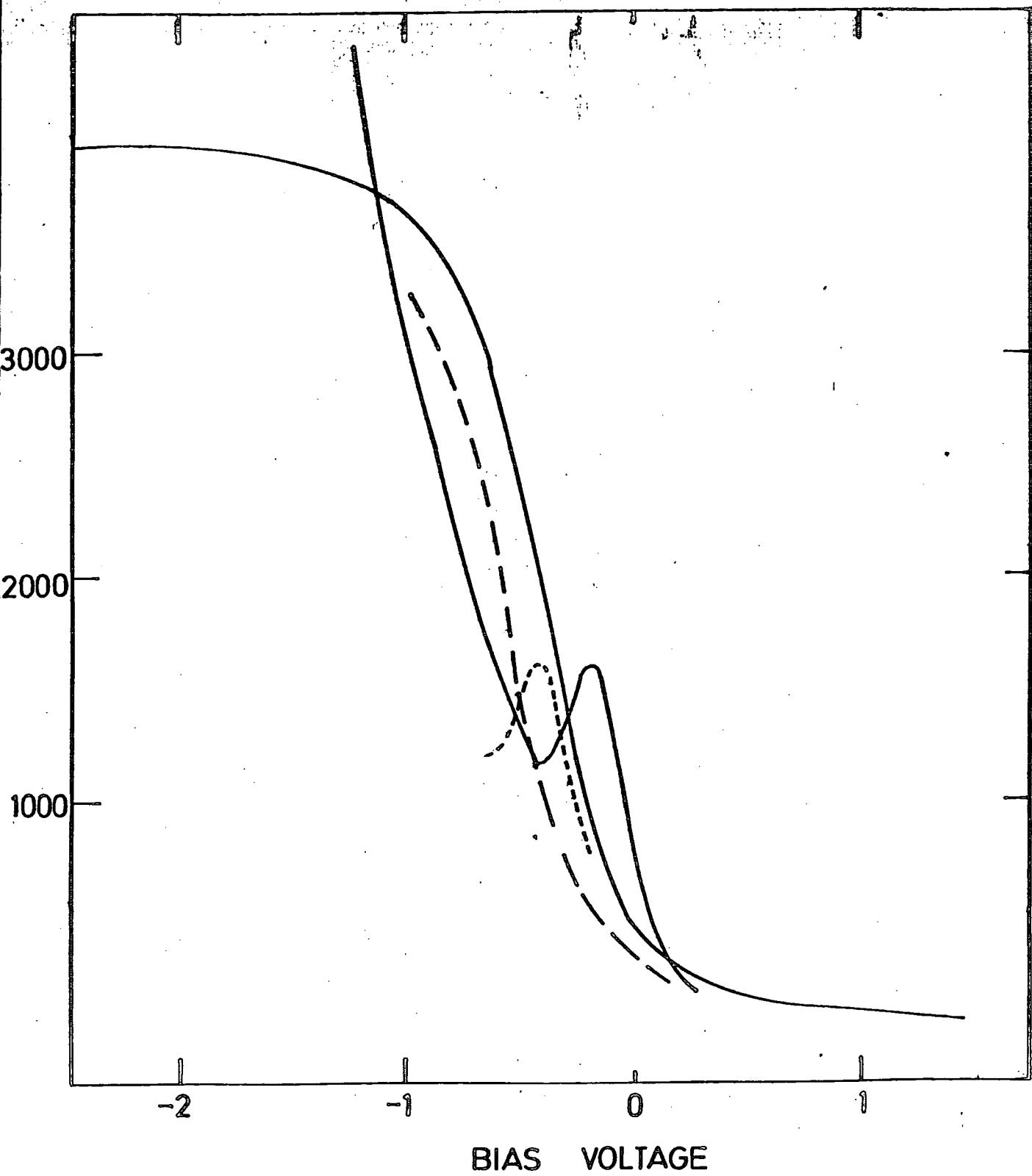

#### 3.4.1 Equivalent Circuits

The measured capacitance and conductance (see figure 3.5a) have to be related to the parallel conductance of the surface states through the use of equivalent circuits. This is because the total admittance of an MIS capacitor consists of several components whose effect has to be compensated for. A circuit model of the device is shown inset in figure 3.5b with a typical corresponding set of measured characteristics. The semiconductor capacitance in parallel with  $G_p$  represents the combination of the surface state and depletion layer capacitance; the increased contribution of the former produces the rise in  $C_p$  as the frequency decreases. The circuit elements  $C_{ox}$  and  $R_s$  are associated with the geometrical capacitance of the oxide and the bulk resistance of the substrate, respectively. Their values can be calculated from the measured values of  $C_m$  and  $G_m$  in strong accumulation:

Figure 3.5 Admittance Characteristics for MIS structure, and corresponding equivalent circuits.

$$R_s = G_m^2 / (G_m^2 + \omega^2 C_m^2) \quad (3.12)$$

$$C_{ox} = C_m (1 + (G_m^2 / \omega^2 C_m^2))$$

The terms defined by these equations are bias and frequency independent for ideal devices, but in a practical situation the insulator may, for example, have a frequency dependent permittivity. Therefore, compensation is required at each frequency. The fact that such compensation is necessary is not commonly recognised.

The interface state contribution is contained entirely in the terms  $C_p$  and  $G_p$ , which are bias and frequency dependent. These terms are extracted from the measured values using the equations below (A is the top contact area).

$$A \cdot G_p = \frac{\omega^2 C_{ox}^2 (G_m - \omega^2 C_m^2 - R_s - R_s C_m^2)}{(\omega^2 C_{ox} R_s C_m - G_m)^2 + \omega^2 (C_{ox} - C_m - C_{ox} R_s G_m)^2}$$

$$A \cdot C_p = \frac{\omega^2 C_{ox} C_m (C_{ox} - C_m) - C_{ox} G_m^2}{(\omega^2 C_{ox} R_s C_m - G_m)^2 + \omega^2 (C_{ox} - C_m - C_{ox} R_s G_m)^2} \quad (3.13)$$

As can be seen,  $C_p$  contains the same information, but to obtain  $N_{ss}$ , a theoretical value for  $C_{sc}$  would have to be assumed, leading to the same problems as suffered by the capacitance techniques previously described. It is better to use the parallel conductance to determine  $N_{ss}$  as this is directly related (see section 2.5). However, a fact not generally appreciated is that it is possible to use  $C_p$  in the depletion region to obtain a value for the surface

potential thus obviating the need to perform the integration normally carried out (equation 3.7). This is explained further in section 5.4.

If highly-doped epitaxial samples are used then  $R_s$  can be assumed equal to zero and

$$A \cdot G_p = \omega^2 C_{ox}^2 G_m / (G_m^2 + (C_{ox} - C_m)^2) \quad (3.14)$$

In the conventional realisation of the conductance technique, frequency response curves are not directly measured as the equipment has to be calibrated at every frequency due to the effects introduced by stray capacitances. Instead, capacitance and conductance characteristics are measured with respect to bias at several frequencies; the parallel conductance is then extracted, compensating for  $C_{ox}$  and  $R_s$ , and replotted in the frequency domain to give the peaks ready for analysis.

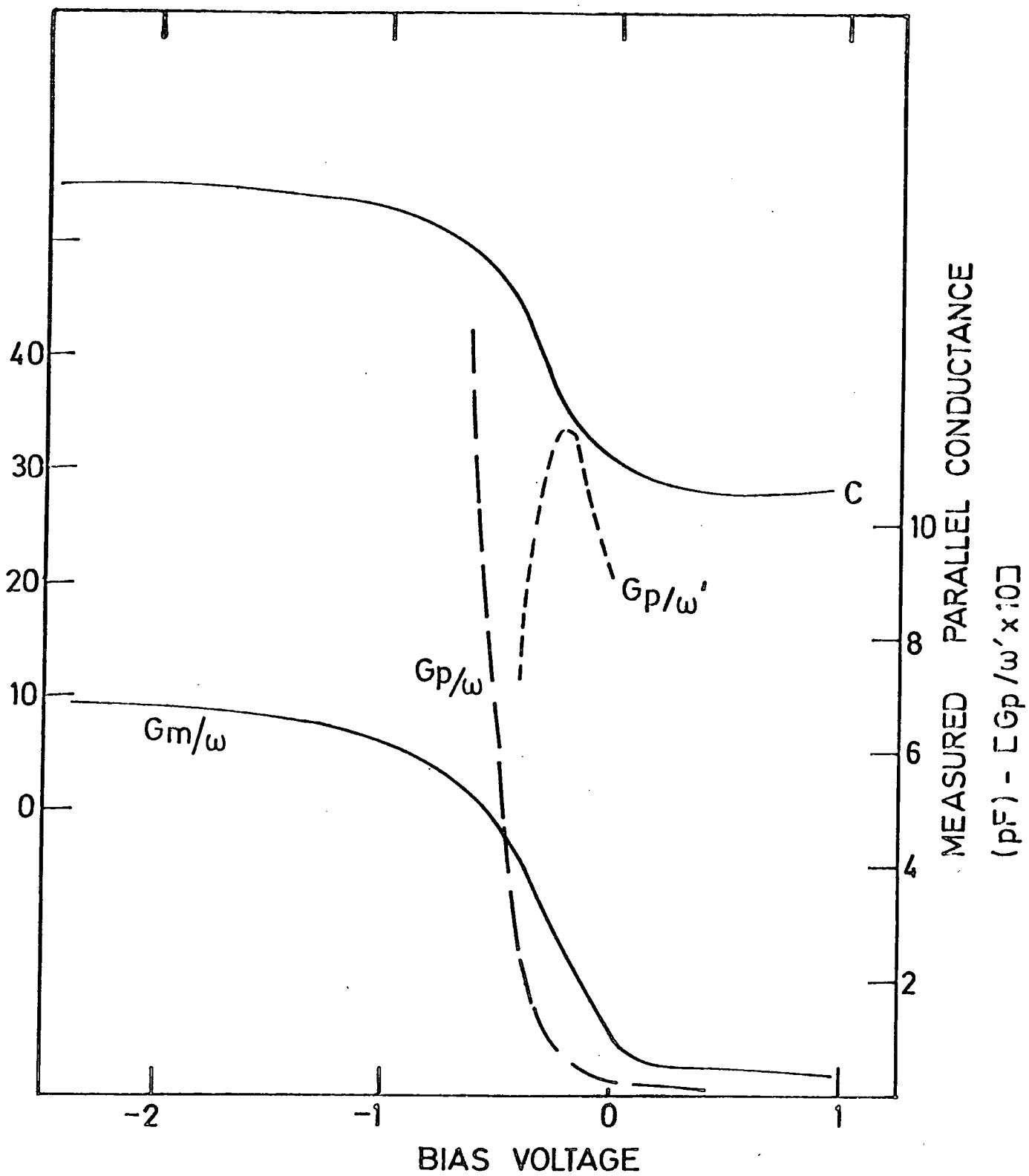

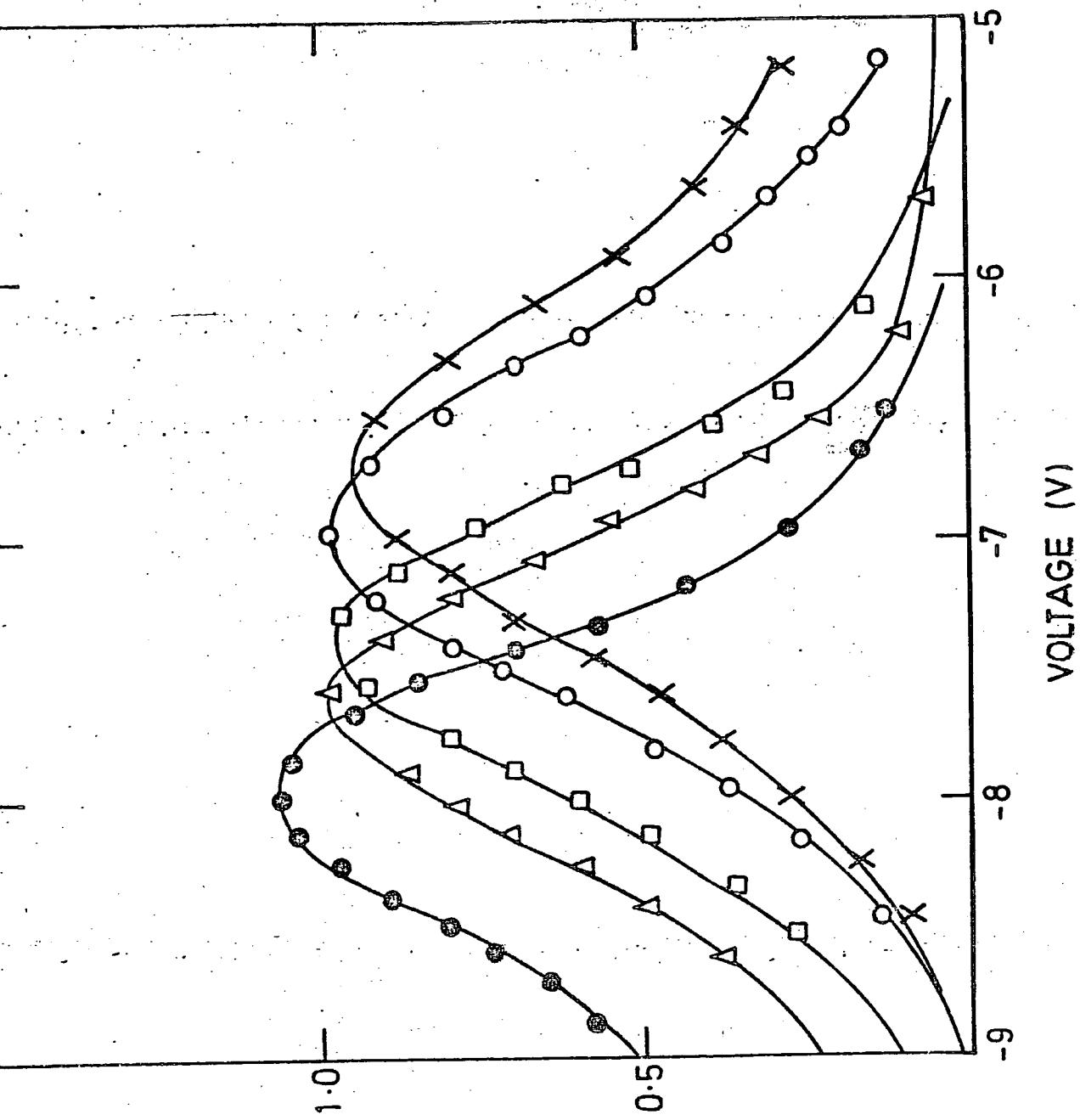

### 3.42 Surface State Evaluation

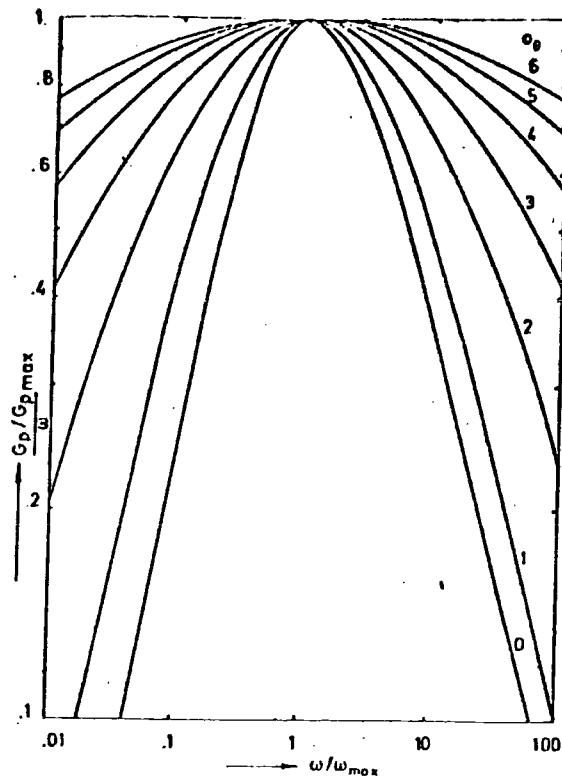

In order to obtain  $N_{ss}$  values from parallel conductance versus frequency curves, it is not necessary to go to complicated computer curve fitting procedures. Two graphical techniques have been proposed that enable desktop evaluation of  $N_{ss}$  to be performed. The first, suggested by Goetzberger et al (19), involves comparing the shape of the experimentally determined curves with standard  $G_p/\omega C_{ox}$  curves that have been plotted in a normalized fashion. The shape of the latter (see figure 3.6) depends only on the variance  $\sigma_g^2$  so, by comparison, the value of the variance for the experimental curves can

Figure 3.6 Normalized parallel conductance plots plotted with respect to the variance  $\sigma_g$  of the surface potential

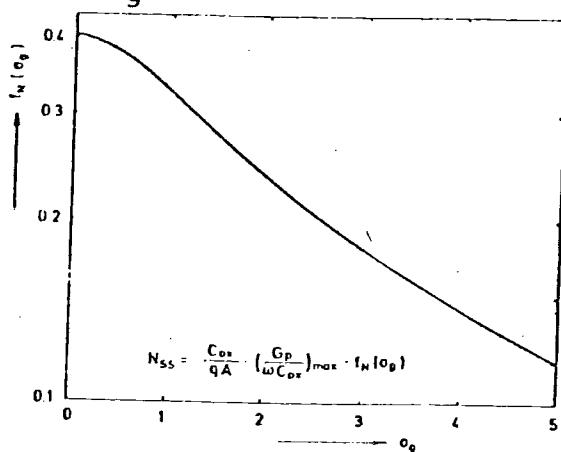

Figure 3.7 A plot of the function  $f_N(\sigma_g)$  versus variance of the surface potential.

(19)

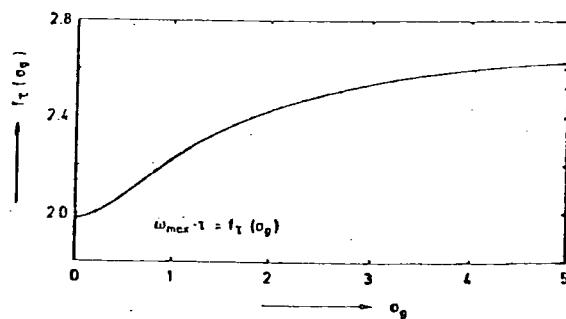

Figure 3.8 The general function  $f_T(\sigma_g)$  plotted with respect to the variance of the surface potential.

be found. The surface state density and the relaxation time are then obtained from the following:

$$N_{ss} = (1/qA) \cdot G_p / \omega_{max} \cdot f_N(\sigma_g)$$

$$\tau = 1 / \omega_{max} \cdot f_\tau(\sigma_g) \quad (3.15)$$

The functions  $f_N$  and  $f_\tau$  are given in figures 3.7 and 3.8. They are dependent only on  $\sigma_g$ . The capture cross section can be determined from  $\sigma_g$  if the surface potential is known, using equation 3.16 ( $v_{th}$  is the thermal velocity taken as  $10^7 \text{ cms}^{-1}$ ).

$$n = (v_{th} \cdot \tau \cdot n_{bulk} \exp(q\psi_s/kT))^{-1} \quad (3.16)$$

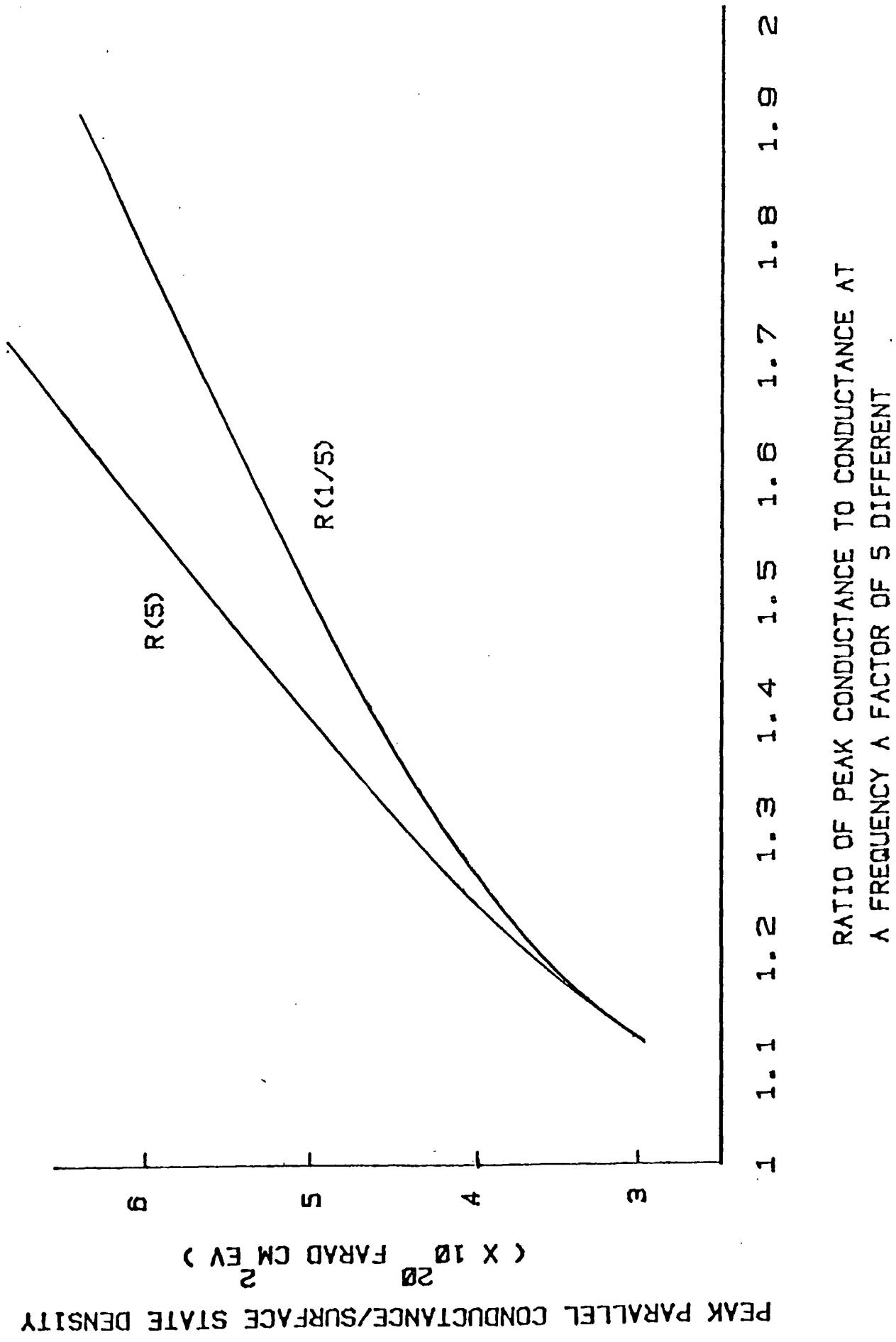

The surface state density is seen to be determined by the peak height and a variable dependent on the curve width. From inspection of figure 3.6, it can be realised that curve fitting is not absolutely necessary; for, sitting at any particular frequency, there is only one possible value of  $G_p/\omega / (G_p/\omega_{max})$  for any particular variance. Thus it can be seen that only two values of the  $G_p/\omega$  curve are necessary. This is the essence of the Simonne technique (20) which goes one step further and combines the curves given in figures 3.6 & 3.7 into one. Practically, an approximate  $G_p/\omega$  versus  $\omega$  curve is first plotted; then, by taking additional data points, the peak position is precisely located. Next, the ratio of the peak parallel conductance compared to the value of  $G_p/\omega$  at a frequency a factor of five different is determined and, from the curve reproduced from (17),  $N_{ss}$  is simply found. This is by far the simplest evaluation method, but it does have its drawbacks which are discussed more in Chapter 5 where they are used to justify the development of our novel technique.

RATIO OF PEAK CONDUCTANCE TO CONDUCTANCE AT

A FREQUENCY  $\lambda$  FACTOR OF 5 DIFFERENT

Figure 3.9 Simonne curve for surface state density extraction.

### 3.5 Summary

This chapter has progressed from simple capacitance techniques that are highly susceptible to error to the more accurate, but also more complicated, transient capacitance and conductance methods, where the response times of the states are measured. There are a few other techniques, such as the static (21) and photovoltage (22), but these are not widespread in use and hence were excluded from this study. A brief outline of the accuracies and valid range of the above is now given:

| Method             | Accuracy                                           | Range                                      |

|--------------------|----------------------------------------------------|--------------------------------------------|

| 1) Terman's Hf C-V | $5 \times 10^{10} \text{ eV}^{-1} \text{ cm}^{-2}$ | $E_i + 0.3 \text{ eV}$                     |

| 2) Quasistatic C-V | $1 \times 10^{10} \text{ eV}^{-1} \text{ cm}^{-2}$ | $E_i + 0.3 \text{ eV}$                     |

| 3) Hf Temperature  | $1 \times 10^{11} \text{ eV}^{-1} \text{ cm}^{-2}$ | $E_i - (E_{\text{maj}} - 0.15) \text{ eV}$ |

| 4) Low Temp. C-V   | $5 \times 10^{10} \text{ eV}^{-1} \text{ cm}^{-2}$ | $E_i + 0.4 \text{ eV}$                     |

| 5) Transient Cap   | $2 \times 10^9 \text{ eV}^{-1} \text{ cm}^{-2}$    | 0.9 eV                                     |

| 6) Conductance     | $10^9 \text{ eV}^{-1} \text{ cm}^{-2}$             | $E_i - (E_{\text{maj}} - 0.1) \text{ eV}$  |

## Chapter 4

### Experimental Details

#### 4.1 Introduction

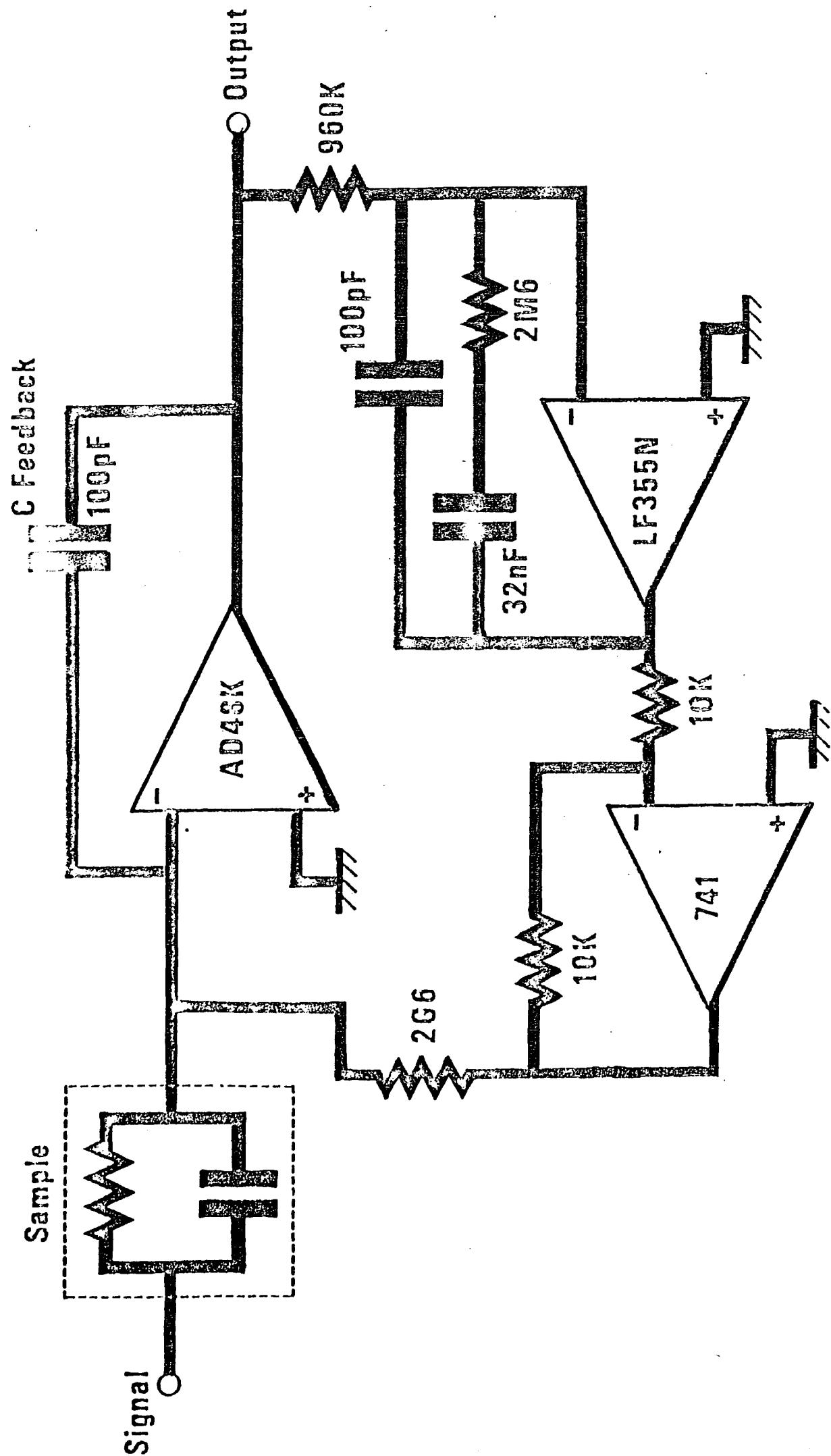

A complete characterization of the semiconductor surface would require many different types of technique which would obviously be experimentally complex to attempt simultaneously. This work has concentrated on electrical measurements of MIS structures with a view to obtaining information on the surface state distribution. The experimental arrangements for the quasi-static and admittance techniques are described below. The microcomputer which has been added to the standard admittance measurement equipment and used to develop our novel technique is also described. In addition, this chapter contains details of sample preparation. The description of the Langmuir film deposition technique and equipment, however, is left until Chapter 7.

#### 4.2 The Quasi-static Technique

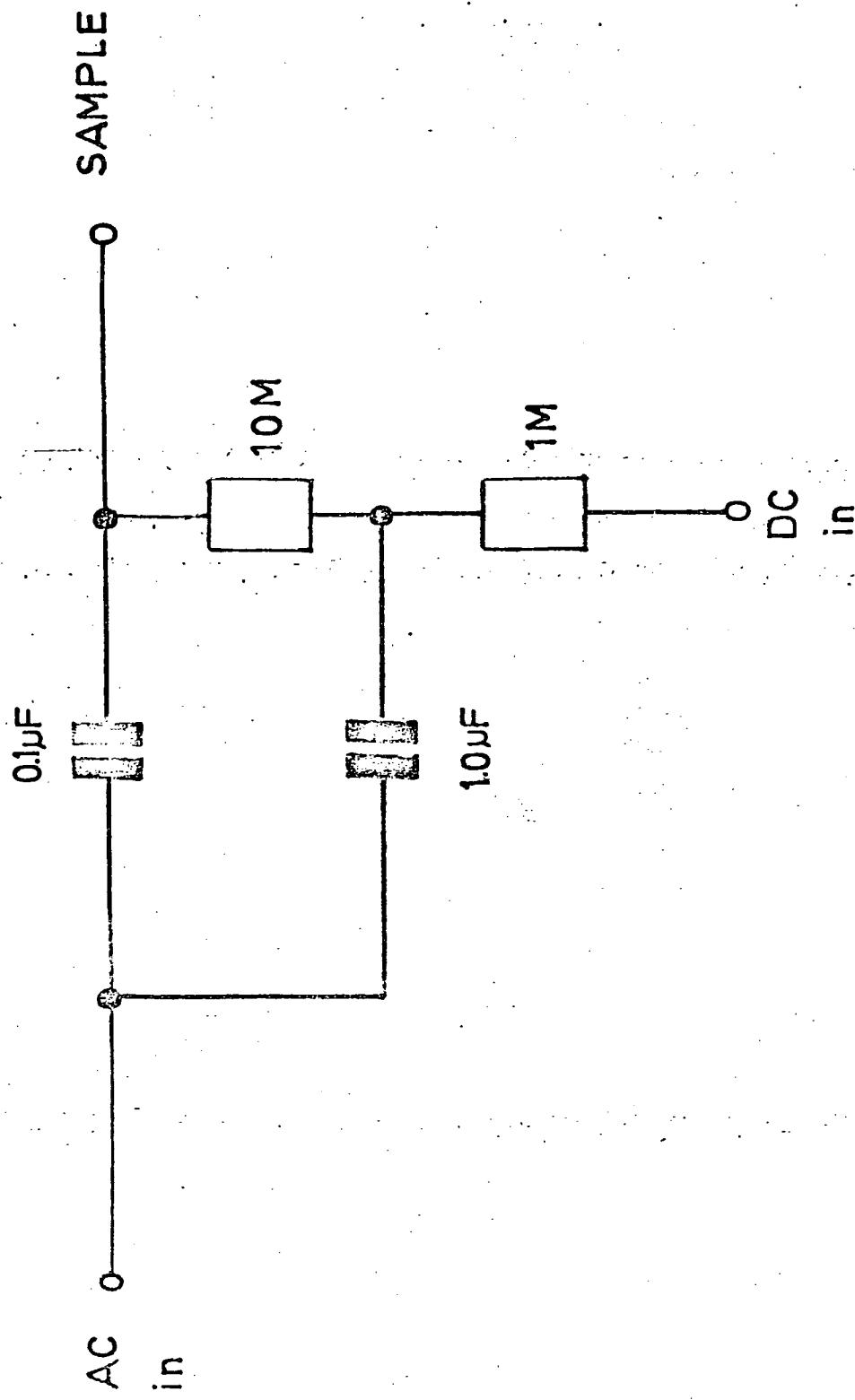

##### 4.2.1 Use of Equipment

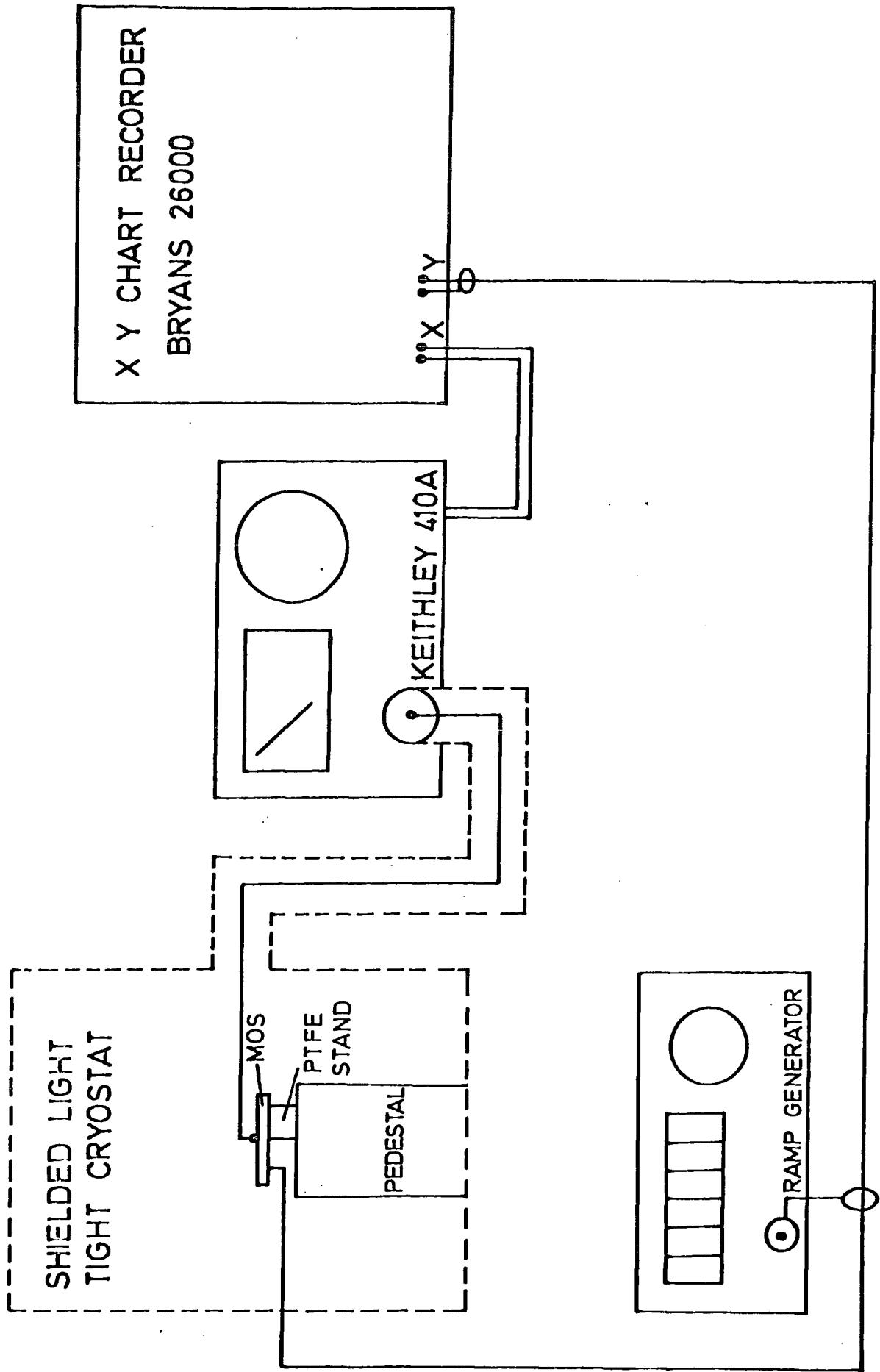

The experimental set-up for this technique is shown in figure 4.1, corresponding to the functional layout given in figure 3.2. The MIS device was driven with a high linearity (1%) low noise ramp voltage generator whose internal circuit was based on a standard OP-AMP integrator. This unit was constructed within the University and possessed presettable start and finish points over a 200 V range, and variable sweep rate down to as low as 5 mV/s. It was connected to the shielded light-tight cryostat which held the sample through stiff cables. A gold wire probe which was ball-shaped at the end to avoid damaging the top electrode completed the contact. The current

Figure 4.1 Experimental configuration for quasi-static method.

produced was monitored with a Keithley 410A picoammeter that acted as the current to voltage converter. Its output voltage, which is directly proportional to the low frequency capacitance of the device, was then displayed on a Bryans 26000 chart recorder. This not only provided additional gain to the system, but also a source of response time type distortion if any filter, eg a capacitor, was used at the input to remove noise. Such distortion is a crucial consideration in such time domain measurements since it can introduce error. The picoammeter rise time on its low ranges is 0.25s; thus, a capacitor with a value less than 0.25mF had to be used (the input impedance of the chart recorder being 1 megohm). These sources of time constant dispersion lead to a limiting of the ramp rate if distortion of the resultant curve is not to occur.

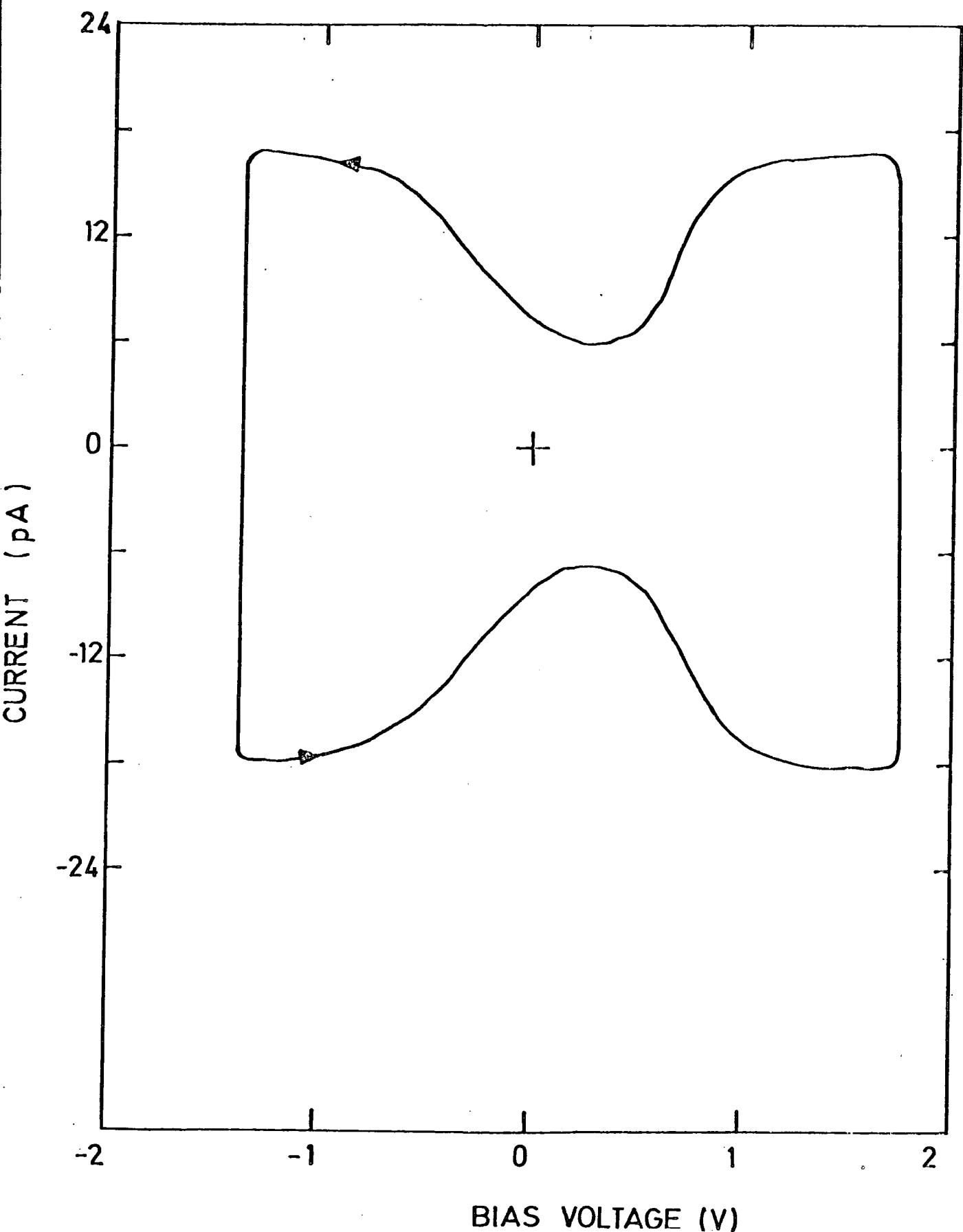

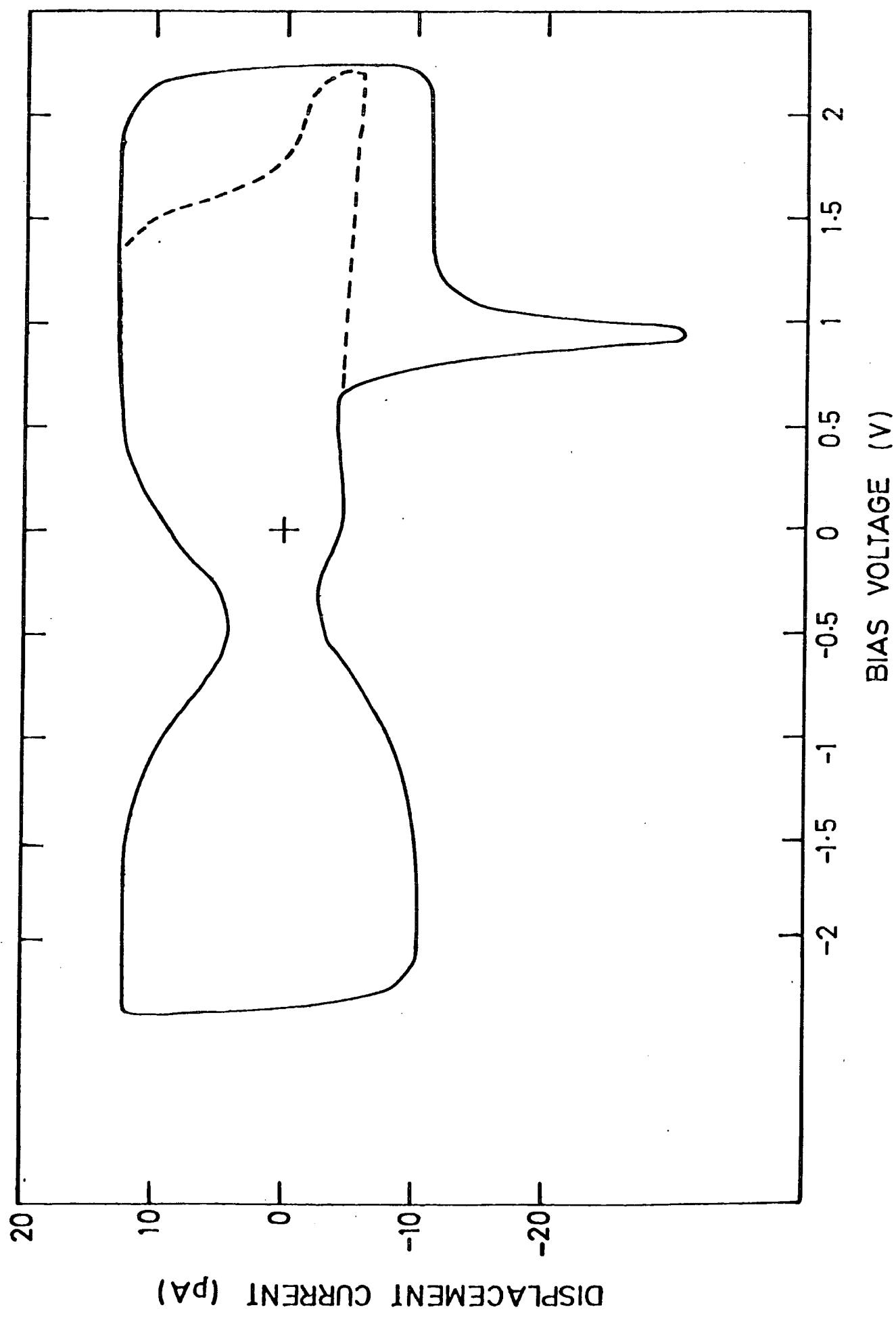

In practice, though, the requirement that the sample be in thermal equilibrium is more important: this limits the ramp rate to less than 50 mV/s. Thermal equilibrium can be seen to exist by sweeping the curve in both directions. Ideally, the two curves obtained above and below the zero line should be mirror images of each other, as shown in figure 4.2. The zero line does not represent zero capacitance because of a current contribution from the stray capacitances present in the circuit. These have to be compensated for and are evaluated by performing a second scan with the sample disconnected. Any slope in the resultant curve indicates leakage, possibly through the input connections. The cryostat used had well-insulated independent entry points to prevent such a problem. If the low frequency capacitance curve slopes, then this means that the device itself possesses a non-ideal insulator which is unsuitable for the following analysis.

Figure 4.2 Experimental quasi-static C-V curves showing presence of thermal equilibrium.

Before the curve can be used to determine surface state density values, it has to be calibrated in terms of capacitance. This was accomplished in two ways:

- (1) Comparison with the resulting structureless curve obtained by ramping with the device substituted by a standard polystyrene capacitor.

- (2) Use of the high frequency capacitance curve: this requires initial matching of the two zero positions followed by a superposition of the measured characteristics in the accumulation region.  $C_{lf}$  is thus given by

$$C_{lf} = C_{ox} \text{ (Height of } C_{lf}) / \text{ (Height of } C_{ox}) \quad (4.1)$$