#### **Durham E-Theses**

## Testability and redundancy techniques for improved yield and reliability of CMOS VLSI circuits

Bensouiah, Djamel Abderrahmane

#### How to cite:

Bensouiah, Djamel Abderrahmane (1992) Testability and redundancy techniques for improved yield and reliability of CMOS VLSI circuits, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/6008/

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

#### TESTABILITY AND REDUNDANCY TECHNIQUES FOR IMPROVED YIELD AND RELIABILITY OF CMOS VLSI CIRCUITS

## by Djamel Abderrahmane Bensouiah

This thesis is submitted to the University of Durham in candidature for the degree of Doctor of Philosophy

# School of Engineering and Computer Science University of Durham May 1992

The copyright of this thesis rests with the author.

No quotation from it should be published without his prior written consent and information derived from it should be acknowledged.

#### **Abstract**

The research presented in this thesis is concerned with the design of fault-tolerant integrated circuits as a contribution to the design of fault-tolerant systems. The economical manufacture of very large area ICs will necessitate the incorporation of fault-tolerance features which are routinely employed in current high density dynamic random access memories. Furthermore, the growing use of ICs in safety-critical application and/or hostile environments in addition to the prospect of single-chip systems will mandate the use of fault-tolerance for improved reliability.

A fault-tolerant IC must be able to detect and correct all possible faults that may affect its operation. The ability of a chip to detect its own faults is not only necessary for fault-tolerance, but it is also regarded as the ultimate solution to the problem of testing. Off-line periodic testing is selected for this research because it achieves better coverage of physical faults and it requires less extra hardware than on-line error detection techniques.

Tests for CMOS stuck-open faults are shown to detect all other faults. Simple test sequence generation procedures for the detection of all faults are derived. The test sequences generated by these procedures produce a trivial output, thereby, greatly simplifying the task of test response analysis. A further advantage of the proposed test generation procedures is that they do not require the enumeration of faults.

The implementation of built-in self-test is considered and it is shown that the hardware overhead is comparable to that associated with pseudo-random and pseudo-exhaustive techniques while achieving a much higher fault coverage through the use of the proposed test generation procedures. The consideration of the problem of testing the test circuitry led to the conclusion that complete test coverage may be achieved if separate chips cooperate in testing each other's untested parts. An alternative approach towards complete test coverage would be to design the test circuitry so that it is as distributed as possible and so that it is tested as it performs its function.

Fault correction relies on the provision of spare units and a means of reconfiguring the circuit so that the faulty units are discarded. This raises the question of what is the optimum size of a unit? A mathematical model, linking yield and reliability is therefore developed to answer such a question and also to study the effects of such parameters as the amount of redundancy, the size of the additional circuitry required for testing and reconfiguration, and the effect of periodic testing on reliability. The stringent requirements on the size of the reconfiguration logic is illustrated by the application of the model to a typical example. Another important result concerns the effect of periodic testing on reliability. It is shown that periodic off-line testing can achieve approximately the same level of reliability as on-line testing, even when the time between tests is many hundreds of hours.

#### **DECLARATION**

I hereby declare that the work reported in this thesis has not been submitted for any other degree.

#### **ACKNOWLEDGEMENTS**

I would like to thank my two supervisors, Dr. M. J. Morant and S. Johnson, for their help and support and for their careful reading of the text.

I also acknowledge the financial support of the ministry of higher education of Algeria.

#### **List of Contents**

| CHAPTER 1                                             |            |

|-------------------------------------------------------|------------|

| INTRODUCTION                                          |            |

| 1.1 Objectives and Focus of the Research              | 2          |

| 1.2 Outline of the Thesis                             | -          |

| CHAPTER 2                                             |            |

| RELATED ISSUES TO FAULT-TOLERANCE:                    |            |

| INTRODUCTION AND REVIEW                               | 5          |

| 2.1 Introduction                                      | 4          |

| 2.2 Sources and Types of Faults                       | 6          |

| 2.2.1 Design Mistakes                                 | 6          |

| 2.2.2 Manufacturing Defects                           | -          |

| 2.2.3 Operational Failures                            | 9          |

| 2.2.4 The Effects of Scaling                          | 12         |

| 2.3 Fault Modelling: The Effects of Faults            | 13         |

| 2.3.1 Logic Level Fault Modelling                     | 14         |

| 2.3.2 Functional Level Fault Modelling                | 17         |

| 2.3.3 Switch Level Fault Modelling                    | 19         |

| 2.3.4 Layout Level Fault Modelling                    | 2(         |

| 2.4 Fault Detection                                   | 22         |

| 2.4.1 On-Line Error Detection Using Coding Techniques | 23         |

| 2.4.2 On-Line Error Detection Using Time Redundancy   | 27         |

| 2.4.3 Off-Line Fault Detection                        |            |

| 2.4.4 Design for Testability                          | 32         |

| 2.5 Fault Correction                                  | 35         |

| 2.5.1 Defect-Tolerance Strategies                     | 37         |

| 2.5.2 Failure-Tolerance Strategies                    | 4(         |

| 2.6 Yield and Reliability                             | <b>1</b> 3 |

| 2.7 Chapter Summary                                   | 46         |

#### CHAPTER 3

| TE  | ST GENERATION FOR CMOS CIRCUITS                           |       |            |     |   |   |   |   |   | • |     | 48         |

|-----|-----------------------------------------------------------|-------|------------|-----|---|---|---|---|---|---|-----|------------|

| 3.1 | Introduction                                              |       |            |     |   |   | • |   |   |   |     | 48         |

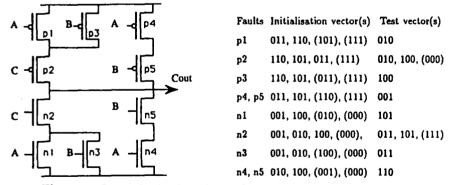

| 3.2 | Testing a CMOS Cell for all Faults                        | •     |            | •   |   |   |   |   |   |   |     | 49         |

|     | 3.2.1 The Fault List                                      |       |            |     |   |   | • |   |   |   | . ' | 49         |

|     | 3.2.2 Test Generation for Specific Faults                 |       |            |     |   |   |   |   |   |   |     | 51         |

|     | 3.2.3 Test Invalidation by Circuit Delays                 |       |            |     |   |   |   |   |   |   |     | 57         |

|     | 3.2.4 Faults that Induce Intermediate Voltages            |       |            |     |   |   |   |   |   |   |     | 61         |

|     | 3.2.5 Complete Test Sequence                              |       |            |     |   |   |   |   | • |   | . 4 | 63         |

| 3.3 | Stuck-Open Faults as a Representative of all Other Fau    | lts   |            |     |   |   |   |   |   |   |     | 65         |

|     | 3.3.1 Stuck-at Faults                                     |       |            |     |   |   |   |   |   |   |     | 66         |

|     | 3.3.2 Stuck-on Faults                                     |       |            |     |   |   |   |   |   |   |     | 67         |

|     | 3.3.3 Bridging Faults                                     |       |            |     |   |   |   |   |   | • | . 1 | 68         |

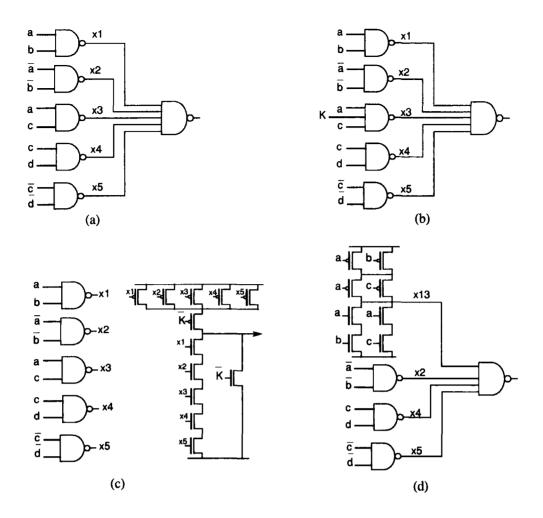

| 3.4 | Test Sequence Generation Procedures                       |       |            |     |   |   |   |   |   |   |     | 68         |

|     | 3.4.1 Exhaustive Stuck-Open Fault Testing                 |       |            |     |   |   |   |   |   |   | . 1 | 69         |

|     | 3.4.2 Minimum Length Test Sequences                       |       |            | •   |   |   |   |   |   |   |     | 70         |

|     | 3.4.3 Robust Test Sequences                               |       |            |     |   |   |   |   |   |   | •   | <b>7</b> 4 |

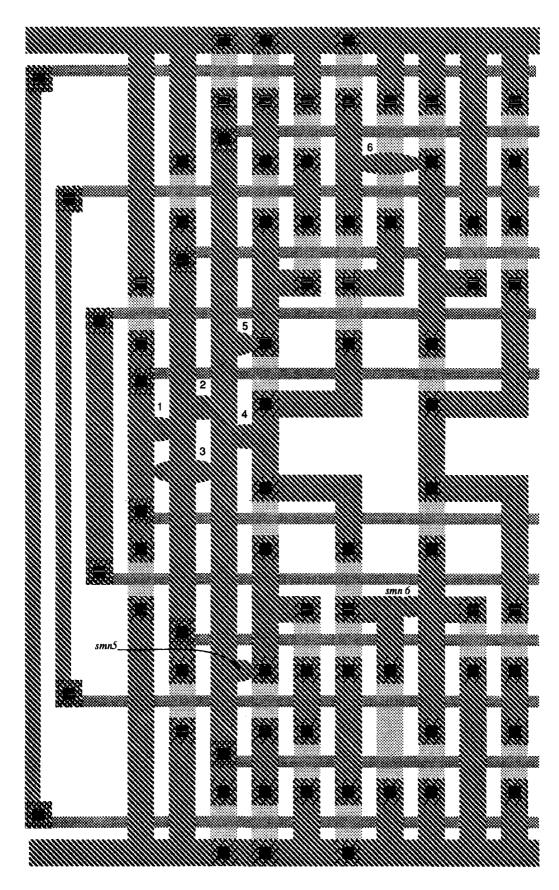

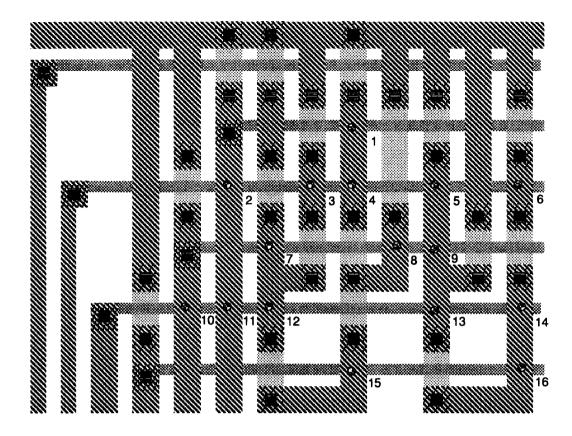

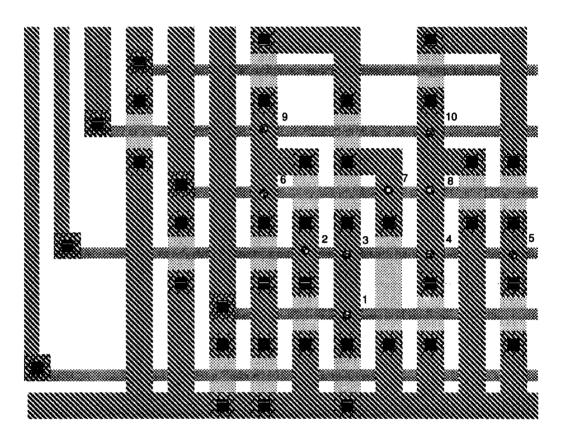

|     | 3.4.4 Test Generation for Multi-Level Circuits            |       |            |     |   |   |   |   |   |   | •   | 77         |

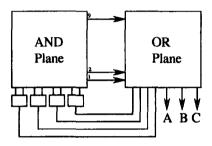

|     | 3.4.5 Testing Multi-Output Circuits                       |       |            |     |   |   |   |   |   |   | •   | 83         |

| 3.5 | Chapter Summary                                           |       | . <b>.</b> |     | • | • |   |   | • |   | . ! | 84         |

| СН  | IAPTER 4                                                  |       |            |     |   |   |   |   |   |   |     |            |

| BU  | TILT-IN SELF-TEST FOR CMOS CIRCUITS                       |       |            |     |   |   |   |   |   |   | . ; | 86         |

| 4.1 | Introduction                                              |       |            |     |   |   |   |   |   |   |     | 86         |

| 4.2 | Detection of all Faults in a Built-In Self-Test Implement | itati | on         |     |   |   |   |   |   |   | . : | 88         |

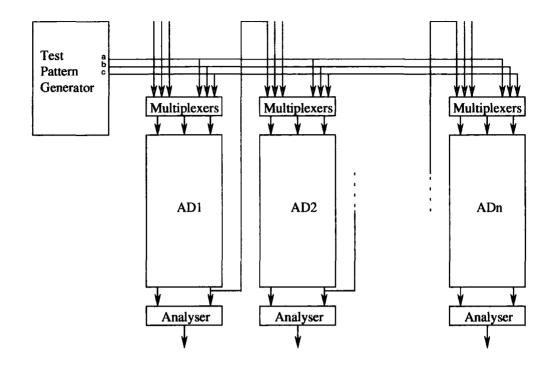

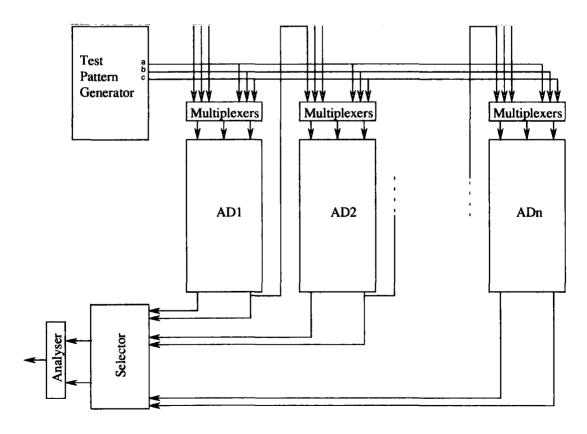

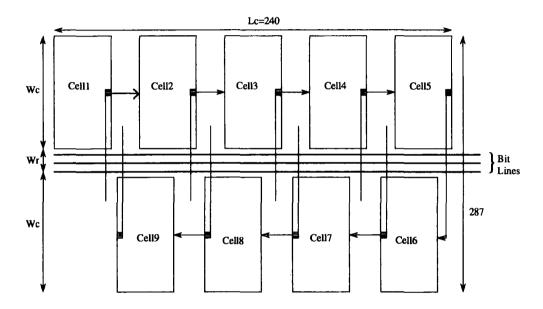

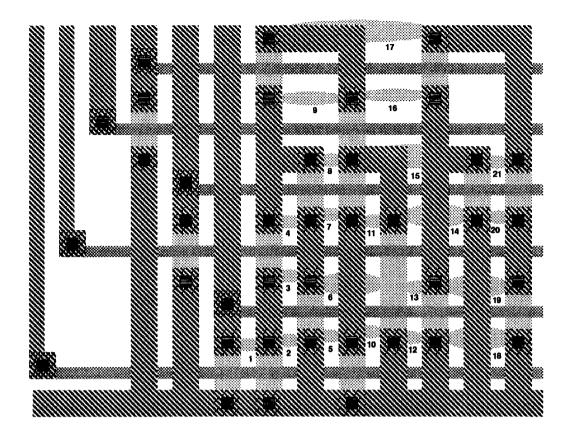

|     | 4.2.1 Distributed vs Centralised Analyzer                 |       |            |     |   | • |   | • |   |   |     | 89         |

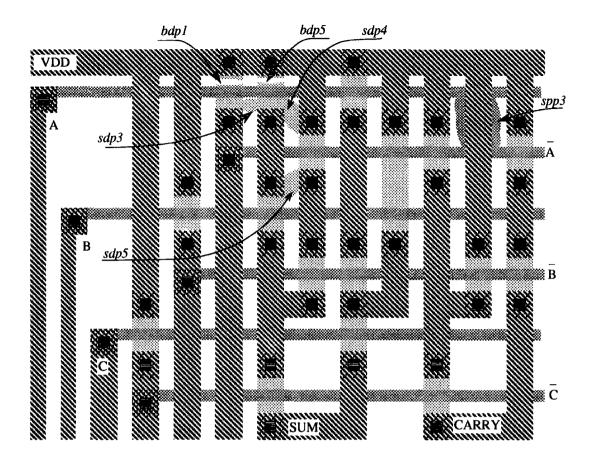

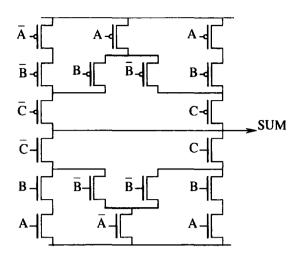

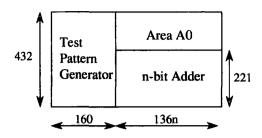

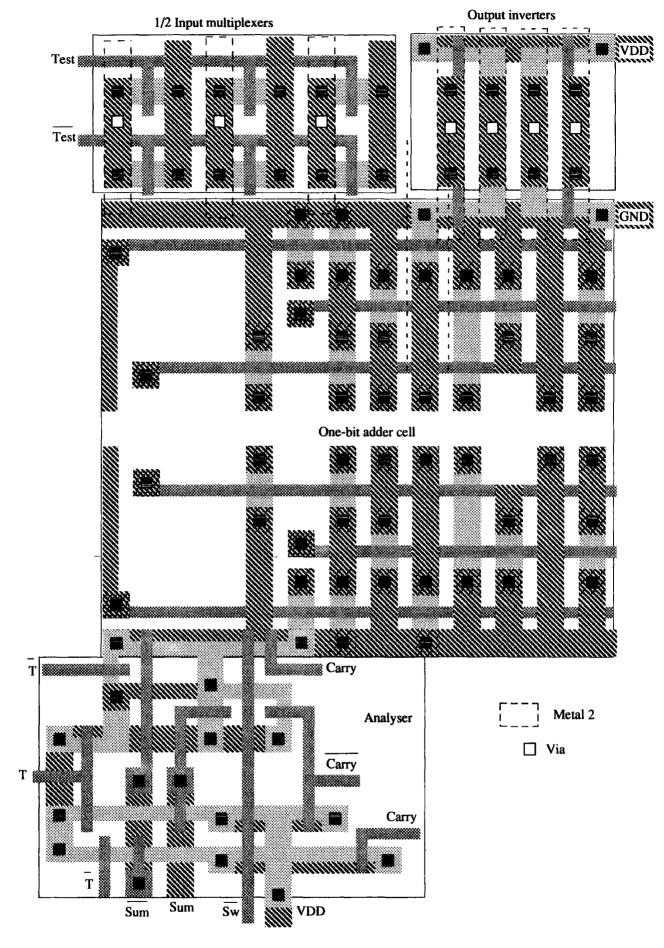

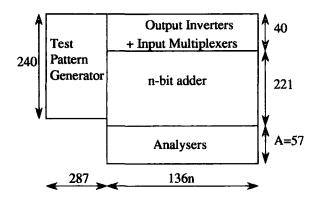

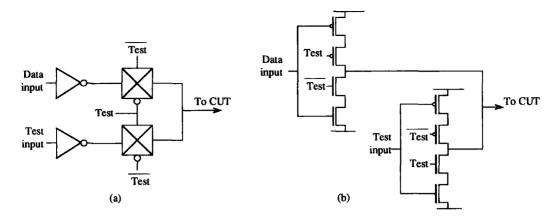

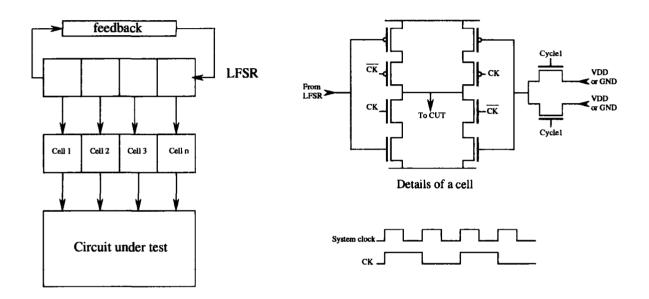

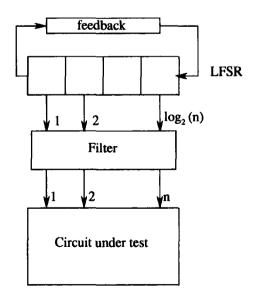

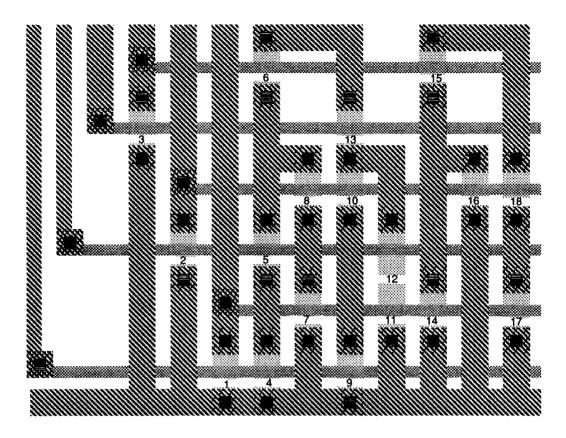

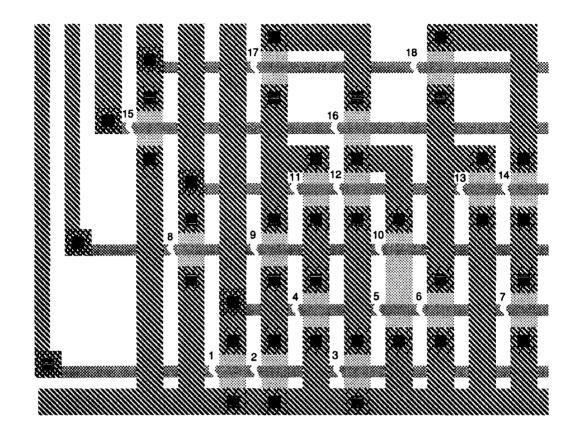

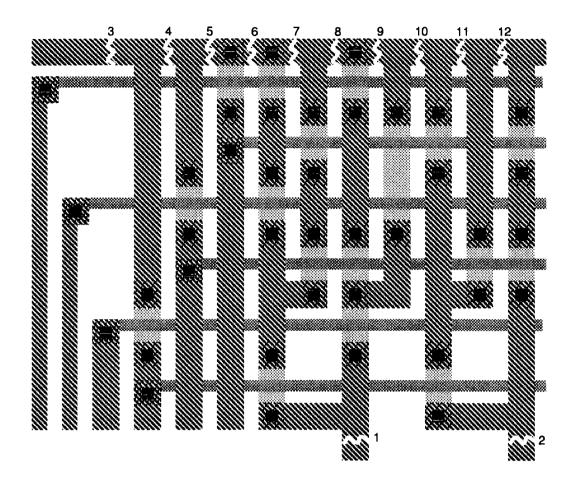

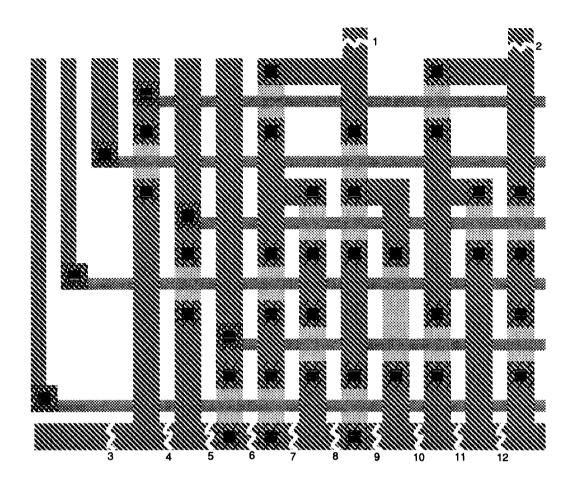

|     | 4.2.2 Design and Placement of the Test Pattern Generat    | tor   |            |     |   |   | • |   |   |   | . ' | 92         |

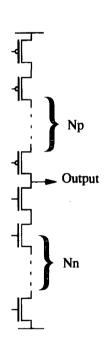

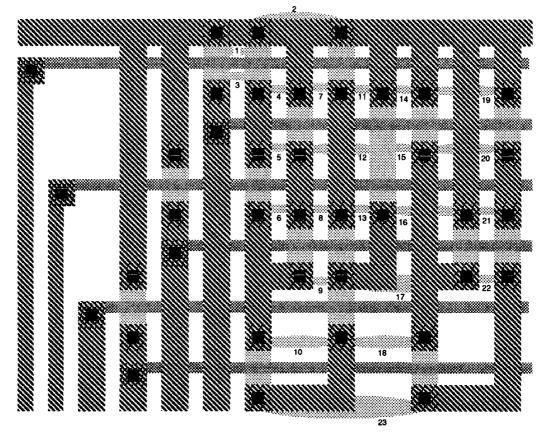

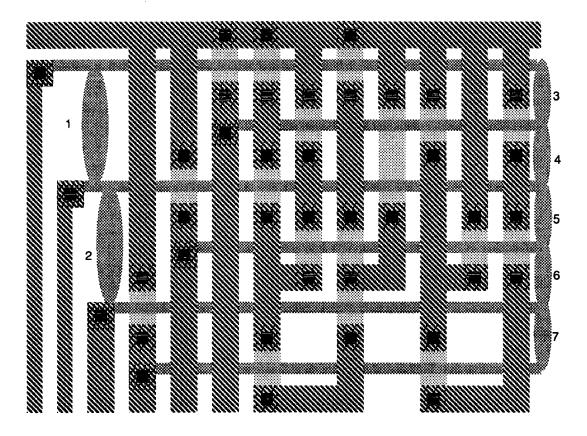

|     | 4.2.3 Design and Placement of the Analyzer Circuit .      |       |            |     |   |   |   |   |   |   | . ( | 97         |

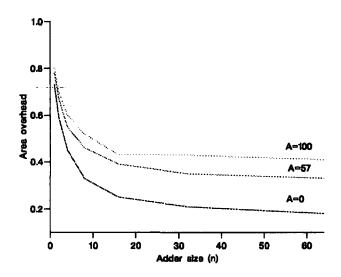

|     | 4.2.4 Area Overhead Figures                               |       |            |     |   |   |   |   |   |   | . ' | 98         |

| 4.3 | Testing the Extra Hardware: Is Complete Test Coverage     | e P   | ossi       | ble | ? |   |   |   |   |   | 1   | 00         |

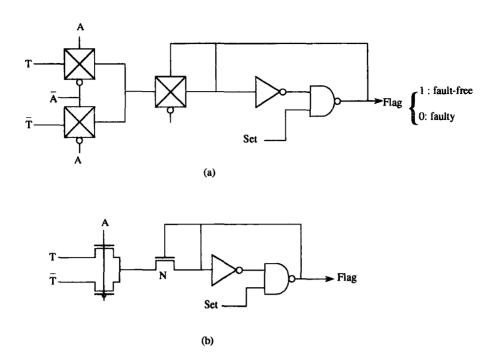

|     | 4.3.1 Testing the Analyzer Circuit                        |       |            |     |   |   |   |   |   |   | 1   | 01         |

| 4     | 4.3.2 Testing the Test Pattern Generator                                 | <br>           | 100 |

|-------|--------------------------------------------------------------------------|----------------|-----|

| 4     | 4.3.3 Testing the Remaining Test Circuitry                               | <br>           | 107 |

| 4     | 4.3.4 Is Complete Test Coverage Possible?                                | <br>           | 108 |

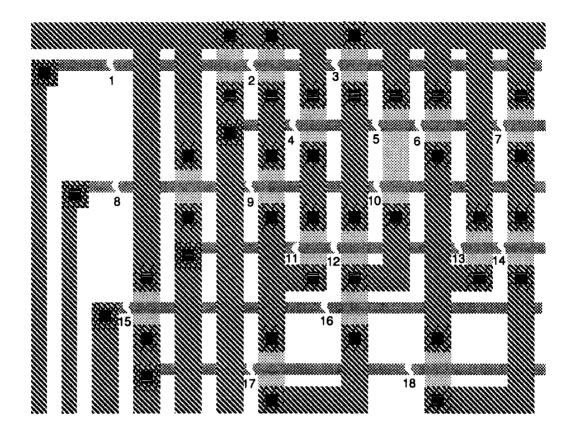

| 4.4 ] | Effect of Partitioning                                                   | <br>           | 110 |

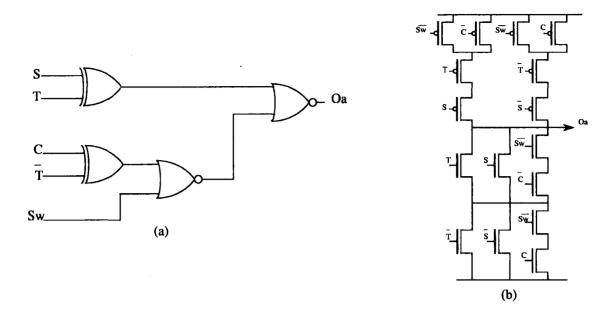

| 4     | 4.4.1 Test Sequence Derivation for an $n_0$ -Bit Adder Block             | <br>           | 111 |

| 4     | 4.4.2 Hardware Requirements                                              | <br>           | 111 |

| 4     | 4.4.3 Hardware Overhead Figures                                          | <br>           | 113 |

| 4.5 ° | Test Sequence Generators                                                 | <br>           | 114 |

| 4     | 4.5.1 Review of Proposed Techniques                                      | <br>           | 115 |

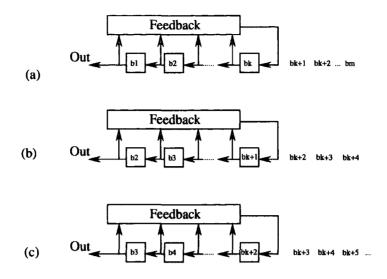

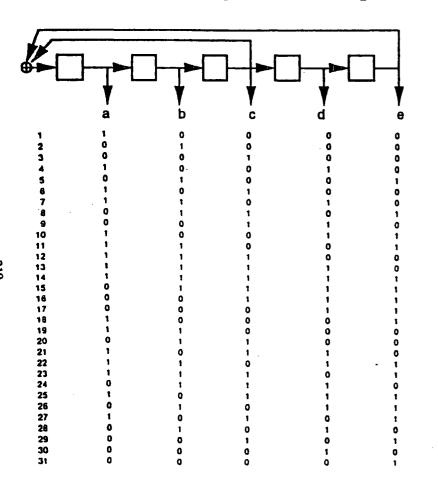

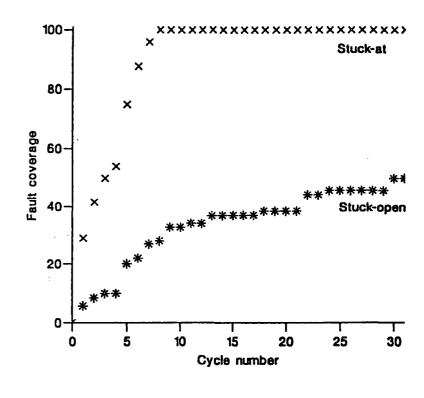

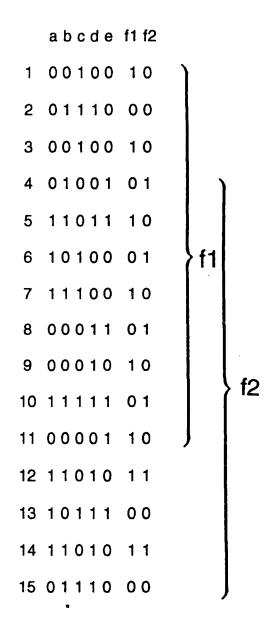

| 4     | 4.5.2 Test Sequence Generation Using Shift Registers                     | <br>           | 116 |

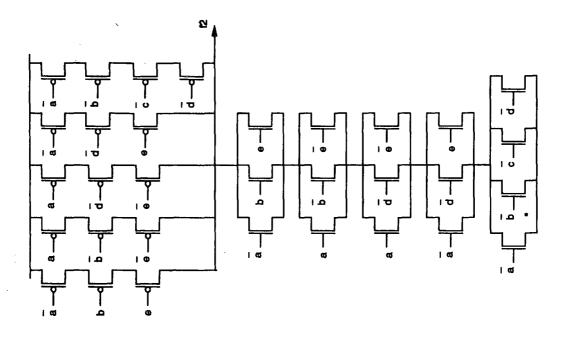

| 4     | 4.5.3 Finite State Machine Implementation of the Test Sequence Generator |                | 120 |

| 4.6 ´ | Time Redundancy for Fault Detection                                      | <br>           | 122 |

| 4.7   | Chapter Summary                                                          | <br>           | 124 |

|       |                                                                          |                |     |

| CHA   | APTER 5                                                                  |                |     |

| YIE   | ELD AND RELIABILITY MODELLING                                            |                |     |

| FOI   | R FAULT-TOLERANT VLSI CIRCUITS                                           |                | 126 |

| 5.1   | Introduction                                                             | <br>           | 126 |

| 5.2 1 | Review of Modelling Techniques                                           | <br>           | 127 |

| :     | 5.2.1 Yield Modelling for Non-Fault-Tolerant Integrated Circuits         | <br>           | 127 |

|       | 5.2.2 Yield Modelling for Fault-Tolerant Integrated Circuits             | <br>           | 130 |

| :     | 5.2.3 Reliability Modelling                                              | <br>           | 132 |

|       | Chip Model and Assumptions                                               |                |     |

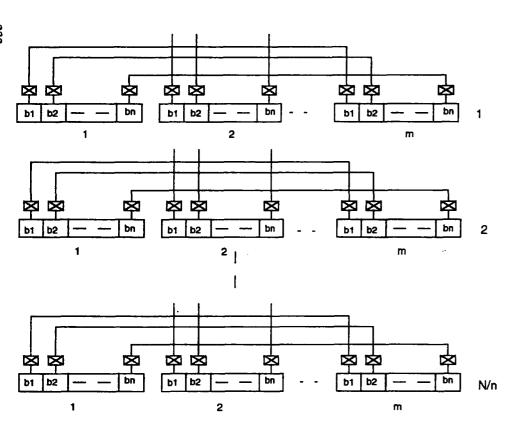

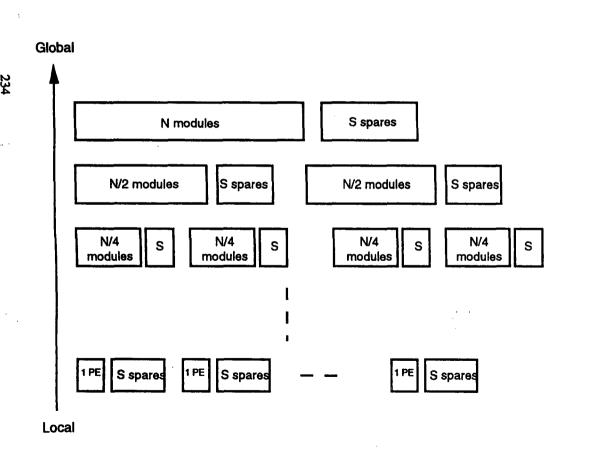

| :     | 5.3.1 Redundancy Strategy                                                | <br>           | 136 |

|       | 5.3.2 Reconfiguration Logic Area                                         | <br>           | 136 |

| :     | 5.3.3 Defect Distribution                                                | <br>, <b>.</b> | 137 |

|       | New Models                                                               |                | 138 |

|       | 5.4.1 The Yield Model                                                    |                | 138 |

|       | 5.4.2 The Expectation of What?                                           |                | 139 |

|       | 5.4.3 Failure Rate of a Section of a Chip                                |                |     |

|       | 5 4 4 The Reliability Model                                              | _              | 144 |

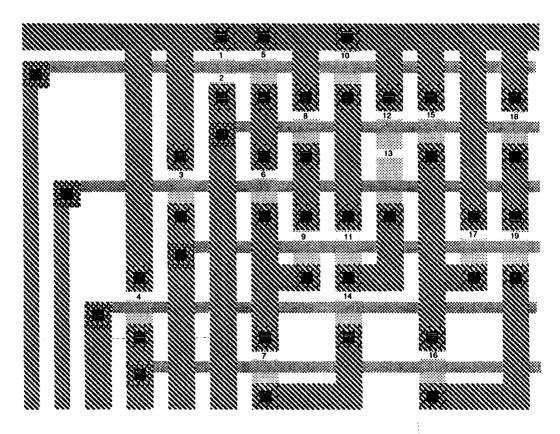

| 5.5 A Case Study                                          |   | • | <br>• |   | . 148 |

|-----------------------------------------------------------|---|---|-------|---|-------|

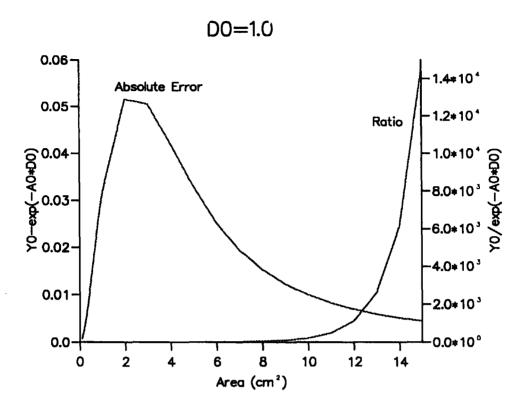

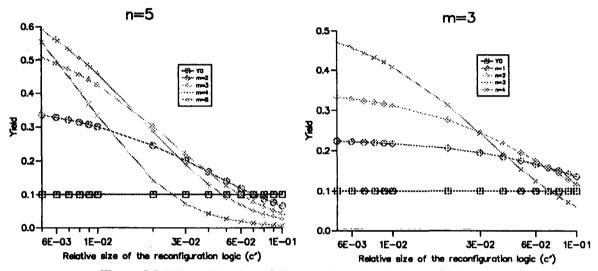

| 5.5.1 The Effect of the Size of the Reconfiguration Logic |   |   |       |   | . 148 |

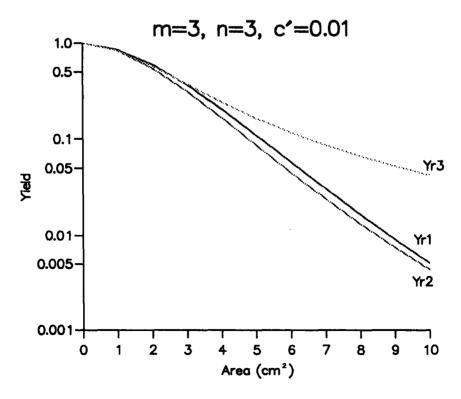

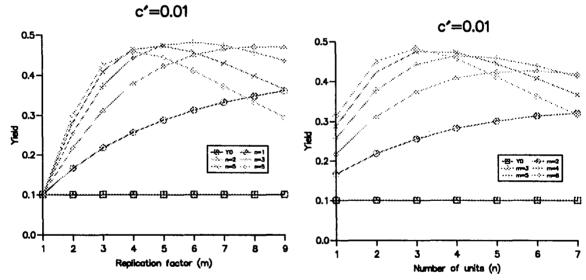

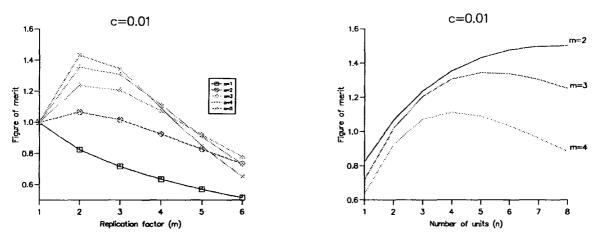

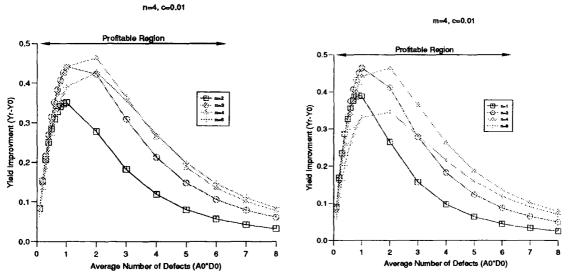

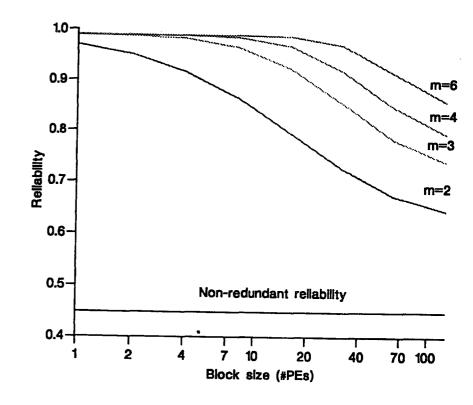

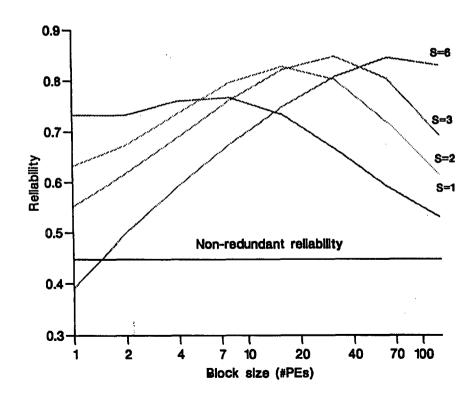

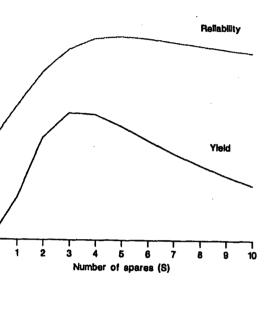

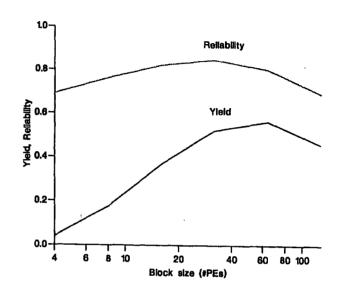

| 5.5.2 Optimum Replication Factor and Unit Size            |   |   |       |   | . 150 |

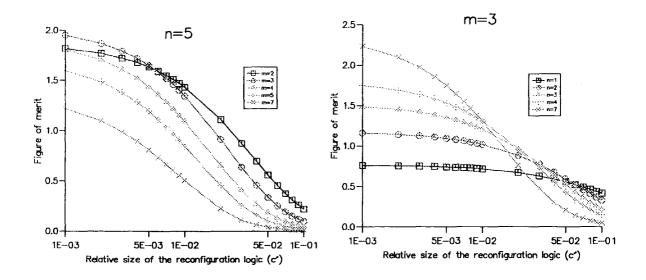

| 5.5.3 Figures of Merit                                    |   |   |       |   | . 153 |

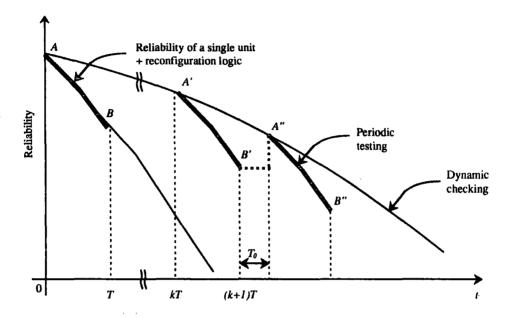

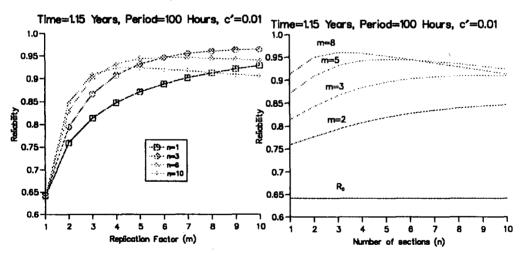

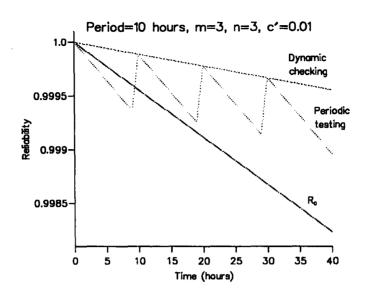

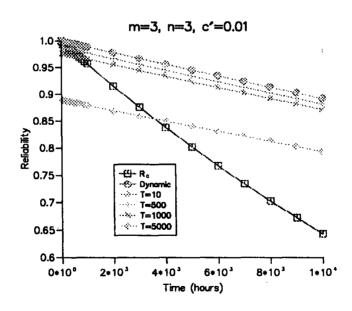

| 5.5.4 Effects of Periodic Testing on Reliability          |   |   |       |   | . 153 |

| 5.6 Chapter Summary                                       | • | • | <br>• |   | . 156 |

| CHAPTER 6                                                 |   |   |       |   |       |

| SUMMARY AND CONCLUSIONS                                   |   | • |       |   | . 157 |

| 6.1 The Main Achievements of the Research                 |   |   | <br>• | • | . 158 |

| 6.1.1 Fault Detection                                     |   |   |       |   | . 159 |

| 6.1.2 Built-In Self-Test                                  |   |   |       |   | . 159 |

| 6.1.3 Evaluation of Yield and Reliability Improvements    | ٠ |   |       |   | . 160 |

| 6.2 General Conclusions of the Research                   |   |   |       |   | . 161 |

| 6.3 Suggestions for Further Research                      |   |   |       |   | 162.1 |

| 6.3.1 Reconfiguration                                     | • |   |       |   | 162.1 |

| 6.3.2 Testing                                             | • | ٠ | <br>٠ | • | 162.1 |

| APPENDIX A                                                |   |   |       |   |       |

| FAULT ANALYSIS                                            | • | • | <br>• | • | . 163 |

| APPENDIX B                                                |   |   |       |   |       |

| YIELD AND RELIABILITY CALCULATIONS                        | • | • | <br>• | • | . 205 |

| APPENDIX C                                                |   |   |       |   |       |

| PUBLICATIONS                                              | • | • | <br>• | • | . 214 |

| REFERENCES                                                | • | • |       |   | . 236 |

### Chapter 1 Introduction

The era of Very Large Scale Integration (VLSI) has been going on since the late 70's early 80's [1]. This is a long period by the standards of the semiconductor industry where rapid progress is the norm. A new era of higher levels of integration would have been expected to be in place by now. The two likely successors to the VLSI era are Ultra Large Scale Integration (ULSI) and Wafer Scale Integration (WSI).

In ULSI, higher levels of integration are achieved through the reduction in the minimum feature sizes\*. This is the trend that has been followed since the first ICs were introduced. So far, it has allowed the successful production of 64-bit microprocessors and 64-Mbit DRAMs. However, there are limits to this trend, some of which are theoretical or fundamental, such as the disappearance of the transistor effect below a certain channel length [3, 6], while others are practical or economical, such as the colossal investment required for sub-micron technology.

In WSI, higher levels of integration are attainable by increasing the area occupied by chips, up to a whole wafer. The major limitation in this case being the daunting problem of defects in manufacture. Furthermore, the prospect of a perfect manufacturing process is extremely unlikely. However, this problem is of a practical nature, rather than

Our interpretation of ULSI is the increase of the number of devices per chip through the reduction of device dimensions and without significant increases in chip area. However, because of its unpopularity [2] and the reluctance of many authors to using the term WSI, some publications use the term ULSI to refer to very large area ICs. Even Maly et. al. [2] use the term 'ULSI-WSI' to refer to such ICs. Most publications on scaling theory [3, 4, 5] use the term ULSI. With this interpretation, ULSI does not require defect-tolerance. On the other hand, WSI does not require, but neither does it exclude the reduction in device dimensions.

fundamental and there exists design techniques that address this problem successfully as illustrated by commercial defect-tolerant DRAMs. Hence, from the manufacturability point of view, defect-tolerance might make large area ICs economically feasible.

At the application level, other considerations, besides manufacturability, also have to be addressed. Chief among them is reliability. Even when the ICs supplied by a manufacturer contain no defects and no weaknesses, they are still susceptible to numerous phenomenon that might cause a chip to fail. Depending on the application, the consequences of chip failures can range from a slight inconvenience to very dramatic ones, especially with the increasing use of ICs in many different areas, often with hostile environments and/or safety critical applications. Furthermore, with higher levels of integration, a system that previously consisted of few tens or few hundreds chips will be designed around one or two chips. In this case, the reliability of the system will be dominated by the reliability of the chips themselves. Hence, failure-tolerance is also a very desirable feature for highly integrated circuits.

Even when current systems are integrated onto single chips or wafers, there is no doubt that new applications will emerge that will require a number of such highly integrated or wafer scale circuits, resulting in systems consisting of billions of devices. This raises the question of how to ensure the integrity of such systems given that chips consisting of only few hundred thousand devices are already causing headaches in testing and fault diagnosis tasks. Test requirements in a fault-tolerant integrated circuit are even more stringent since precise information concerning the presence of faults and their locations is necessary for performing corrective actions.

#### 1.1 OBJECTIVES AND FOCUS OF THE RESEARCH

The main objective of the research presented in this thesis is the development of design techniques to improve the yield and reliability of ICs by making them tolerant to faults.

Preliminary investigations suggested a breakdown of this main objective into the following sub-objectives:

- (i) To attempt to derive a method of testing for all detectable faults: Complete information on every type of fault is required to undertake corrective actions. This information can only be obtained by aiming at the detection of all faults, rather than just the high percentage of faults thought to be adequate by earlier workers.

- (ii) To apply the method developed in (i) to the implementation of built-in self-test:

As part of the requirement of detecting all faults, we must also find out how to test

the BIST circuitry itself. Another point of focus is the investigation of the effect of partitioning on the hardware overhead associated with BIST.

- (iii) To identify a way of implementing fault-tolerance that is compatible with the methods of (i) and (ii).

- (iv) To develop a method for assessing the effects of design decisions on both yield and reliability: The design decisions of interest include the amount of redundancy, the level at which redundancy is introduced (i.e., the size of the replaceable units), and off-line periodic testing vs continuous checking, all of which were to be considered.

The yield and the reliability of ICs are continually enhanced through improvements in the manufacturing process, but this is beyond the control of most IC designers. For the same reason, design techniques that rely on the addition or modification of some processing steps are not considered.

The nature of the faults and the way in which they affect the operation of circuits depend on the technology used. CMOS, being the dominant technology for high density ICs, is selected for this research. A special emphasis is given to transistor stuck-open faults which are peculiar to this technology. In this thesis, a stuck-open fault is defined as any fault that would prevent conduction from the source to the drain of a transistor. This may happen as a result of breaks in the connections or contacts between the source/drain and other parts of the circuit or because of the impossibility of driving the gate to the required voltage level to turn the transistor on.

The special emphasis on CMOS stuck-open faults is due to the stated aim of this work which is to detect all faults rather than just a high percentage.

#### 1.2 OUTLINE OF THE THESIS

The concept of fault-tolerance appeared with the first applications of digital systems. Hence, there is an abundant literature on the subject. Chapter Two is a review of this extensive subject with particular emphasis on those areas of relevance to the implementation of fault-tolerant ICs. The sources of faults, their effects on the operation of circuits, and the different abstraction levels used to model faults are discussed. The treatment of fault detection mechanisms highlights the differences between on-line and off-line approaches. In particular, it is found that the former cannot provide high fault-coverage and it also requires high hardware overheads, compared to the latter. In the discussion of fault-correction techniques, a clear distinction is made between defect-tolerance and failure-tolerance. Defect-tolerance deals with manufacturing defects and

it has very limited capabilities for dealing with field failures, whereas failure tolerance techniques also have the potential of dealing with manufacturing defects.

A major aspect of off-line fault-detection is the generation of tests that establish the presence or absence of faults. Test generation is a complex problem, even for classical faults. In Chapter Three, it is shown that tests derived for stuck-open faults can also detect all other detectable faults. This result is used to derive simple test generation procedures for CMOS combinational circuits that produce test sequences for the detection of all stuck-open faults. An important attribute of the procedures presented in Chapter Three is that the generated test sequences should produce a trivial fault-free response. This represents a novel solution to the problem of test response analysis. The fact that these procedures generate test sequences, as opposed to test patterns, is a further advantage, since fault enumeration is no longer required.

The hardware implementation of Built-In Self-Test (BIST) is considered in Chapter Four. It is shown that, using the procedures of Chapter Three, BIST can be implemented with a hardware overhead comparable to that associated with pseudo-random and pseudo-exhaustive testing, while achieving a much higher fault coverage. The problem of the detection of faults in the test circuitry itself is also considered and it is proposed that the most effective solution is to design the test circuits in such a way that they are tested while performing their functions.

In Chapter Five, new yield and reliability models for fault-tolerant ICs are developed. The models are relatively simple and yet, they incorporate important effects such as the dependence of reliability on the manufacturing yield and the impact of off-line periodic testing on reliability. The illustration of the application of the models reveals the crucial importance of the size of the test and reconfiguration logic in determining whether there is any yield or reliability improvement. The reconfiguration logic is often ignored in many proposed fault-tolerance strategies, and even when it is not ignored, the assumptions concerning its size are shown to have an effect in determining the optimum amount of redundancy and the optimum size of the replaceable unit.

The main argument that can be used against off-line periodic testing is that the chip may produce errors between tests. It is shown in Chapter Five that this is nearly as likely as a complete failure of a continuously checked chip, provided that the time between tests is short enough: **up to many hundred hours**.

# Chapter 2 Related Issues to Fault-tolerance: Introduction and Review

#### 2.1 INTRODUCTION

Fault-tolerance for electronic circuits is an involved subject, comprising many aspects of design, manufacturing, and testing. Research on the subject began in the early 1950's. In these early days, the research was motivated mainly by the high unreliability of electronic systems. In the following years, and as electronic systems began appearing in many safety-critical applications, research into fault-tolerance became mandatory. This resulted in many techniques and methods for implementing fault-tolerant systems. This Chapter is a review of the previous research work and an introduction to the many aspects related to fault-tolerance and their relevance in implementing fault-tolerant integrated circuits.

A fault-tolerant system is a system that would continue to provide correct operation despite the presence of faults. The fault-tolerance attribute can be described in terms of two factors: detection of faults and correction of faults. This does not imply that the two factors are always physically separated, but only that they can be separated conceptually [7].

The presence of a fault in a circuit results in errors. An error is said to have occurred if the output of the circuit deviates from its specified behaviour. A fault is the physical phenomenon that produces errors. Faults may originate in any of the three phases of the life of an integrated circuit: design, manufacturing, and operation. The types of fault in each of these phases are discussed in Section 2.2. Section 2.3 discusses the effects of faults on circuit operation, the knowledge of which is necessary for deriving fault detection and fault correction techniques, discussed in Sections 2.4 and 2.5, respectively.

and 2.5, respectively. Faults introduced in the manufacturing stage have a direct effect on the yield, and an indirect effect on reliability, whereas faults occurring during normal operation affect the reliability only. Yield and reliability are the two main criteria for evaluating fault-tolerance strategies. They are discussed in Section 2.6. Section 2.7 summarises the Chapter.

#### 2.2 SOURCES AND TYPES OF FAULTS

Faults may be introduced into an integrated circuit in the design phase, at the manufacturing stage, or during normal operation.

#### 2.2.1 Design Mistakes

In the design phase of an IC, a top-down approach is usually adopted, as illustrated in Fig. 2.1. Design mistakes may be introduced at any of the transitions between levels. Note that the term used is design mistakes instead of the commonly used terms design errors or design faults. We do so firstly to avoid the circular situation (design fault—fault—error or design error—fault—error) and secondly to stress the fact that they should not occur. However, because of the increasingly complex ICs that VLSI has made possible, and the usual practice of having such chips designed by large teams of designers, design mistakes do occur even in the best design offices [8].

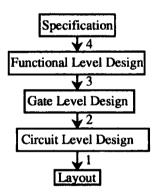

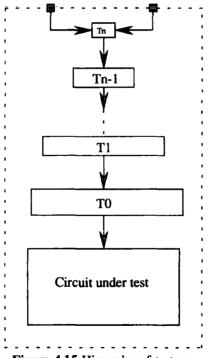

Figure 2.1 The top-down approach to IC design.

Design mistakes likely to be introduced in transitions 1 and 2 (incorrect transistor dimensions, layout prone to failure, circuit design mistakes, etc...) can usually be avoided by the use of efficient CAD tools such as design rule and electrical rule checkers combined with circuit extractors. Mistakes in transitions 3 and 4 are much harder to avoid, although extensive and comprehensive simulation can deal with transition 3 to a certain extent. Transition 4 is the most crucial. It prompted the introduction of the concept of formal verification based on theorem proving techniques. However these

methods are still in their infancy [9, 10]. One of the early results of these methods was in the design of the VIPER processor intended for use in high reliability applications [11, 12], the basic idea being in the use of a very simple processor architecture so that formal verification techniques could be employed.

mistakes

Design faults are best handled by ensuring that they do not occur in the first place, which means providing good specification tools and a means of evaluating the proposed design before proceeding to realisation [13].

#### 2.2.2 Manufacturing Defects

Faults occurring in the manufacturing stage are due to various defects introduced by a less than perfect processing. The manufacturing phase is considered to comprise all the stages that start with the raw silicon material and end with a packaged chip. Defects that affect the silicon die and those introduced in the assembly/packaging stage are discussed separately, because of their different nature and because of the fact that fault-tolerance strategies tend to deal with faults affecting the die only.

#### a) Die-Related Manufacturing Defects

Defects that affect the silicon die have been well studied in the literature because of their prime importance in yield forecasting and process improvement [2]. In most cases, processing defects can be classified as either global or local. Global defects affect large areas of the wafer or the IC, and they are usually easily detected at an early stage in the manufacturing process, well before the dicing of the wafer (through visual inspection in the case of area and line defects and by the continuous monitoring (test site observation) in the case of global process parameter variations). Their frequency should be low in a well controlled processing line.

Local defects, on the other hand, affect small areas of the wafer or die and are usually considered as spot defects. They are much more numerous than global defects and tend to be randomly distributed over the wafer.

Besides their global or local nature, processing defects can also be classified according to whether they are caused by photolithography errors or by process quality errors [14]. Basically, photolithographic errors result in a missing or extra feature on any of the layers of the IC. Table 2.1 is a list of such defects for a CMOS process.

Process quality errors result from instability in the process conditions or from variations in the physical properties of the chemicals used [2]. They are listed in Table 2.2. Most process quality errors will result in a change in the I-V (current-voltage) characteristic of the MOS device, which in turn may cause higher power consumption, lower

Table 2.1 Main Photolithographic Errors for a Standard CMOS Process.

| Layer         | Defect           | Possible effects                                                                     |

|---------------|------------------|--------------------------------------------------------------------------------------|

| Diffusion     | Missing          | Shorts to GND or VDD                                                                 |

|               | Extra            | Short circuits                                                                       |

| Implant       | Missing or wrong | Variations in V <sub>T</sub>                                                         |

| impiant       | Extra or wrong   | Variations in V <sub>T</sub>                                                         |

| i .           | Missing          | - Missing device                                                                     |

| Gate oxide    |                  | - Short between gate and channel regions                                             |

| Gate Oxide    | Extra            | Parasitic device                                                                     |

|               |                  | - Missing device                                                                     |

|               | Missing          | - Floating gate                                                                      |

| Polysilicon   |                  | - Open circuits                                                                      |

| 1 ory sincesi | Extra            | - Parasitic device                                                                   |

|               |                  | - Short circuits                                                                     |

|               |                  | - Shorts between poly and metal                                                      |

|               | Missing          | - Shorts between poly and substrate                                                  |

| Field oxide   |                  | - Shorts between metal and substrate - Shorts between Poly/metal and active regions. |

|               | Extra            | Open circuits                                                                        |

| Metal         | Extra            | Short circuits                                                                       |

| 1VACUUI       | Missing          | Open circuits                                                                        |

noise margins, higher propagation delays, etc. These are usually referred to as performance faults. However, in extreme cases, process quality errors also result in breaks and short circuits.

#### b) Package and Assembly-Related Manufacturing Defects

The wire bond is considered to be one of the weakest areas of device packaging [15]. Poor bonding pressure can lead to bonds with a low fracture strength, while high bonding pressure may result in substrate cracking or partial detachment of the die from the carrier. If the loop formed between the semiconductor and the lead frame droops too much there is a susceptibility to shorts between adjacent bond wires. On the other hand, if the loop is too tight, the tension created may lead to fractures.

In plastic encapsulated devices, the plastic compounds used may force the bond wires against each other resulting in shorts. In hermetic packages, debris from the materials used in packaging and assembly may be introduced, later becoming loose and causing short circuits. Poor bonding may also enhance the formation of intermetallic compounds through gold-aluminium interdiffusion [15].

#### 2.2.3 Operational Failures

During the operational phase, faults occur because of physical failures. Chip failure implies that the chip was initially good and then, for some reason, it became faulty. Hence, those faulty chips that escape the manufacturer's screening process and then 'fail' in operation are not considered to have failed since they were never good. Chip failures may be due either to weaknesses introduced during the manufacturing phase or to ageing. In the same way as for manufacturing defects, failures are classified into those affecting the die and those related to the packaging/assembly process.

#### a) Die-Related Operational Failures

Many of the failures occurring in normal operation can be related to manufacturing defects. A processing defect may not be severe enough to cause a chip to fail the manufacturer's tests, but the presence of the defect constitutes a weakness that can be aggravated in operation because of temperature, voltage or mechanical stress.

There are many failure mechanisms that affect the metallisation. The most important is electromigration. It is caused by the continuous impact of electrons on the aluminium grains in high current density situations, resulting in a movement of aluminium atoms in the direction of electron flow, giving rise to voids [15]. Contact regions are also subject to migration of aluminium atoms into silicon or Si atoms into Al which results

Table 2.2 CMOS Process Quality Errors.

| Affected Layer  | Defect                  | Possible Effects                          |

|-----------------|-------------------------|-------------------------------------------|

| Substrate       | Crystal imperfections   | Excessive leakage currents                |

|                 | Doping levels           | Variations in $V_T$                       |

| Implant         | Ion implant dose        | Variations in V <sub>T</sub>              |

|                 | Implant energy          | Resistance variation of implanted regions |

| Gate oxide      | Bad quality             | Variations in V <sub>T</sub>              |

|                 | Pinholes                | Short circuits                            |

|                 | Thickness variations    |                                           |

|                 | Contamination           |                                           |

| Polysilicon     | Bad quality             | Variations in channel length              |

| II.             | Variation in thickness  | Variation in RC time constants            |

|                 | (over or under etching) |                                           |

| Field oxide     | Contamination           | Short circuits                            |

|                 | Thickness variations    | Variations in RC time constants           |

|                 | Pinholes                | (capacitance of conductors to substrate)  |

| Metal           | Grain size              | Short circuits                            |

|                 | Microcracks             | Open circuits                             |

|                 | Metal liftoff           |                                           |

| Contact windows | High resistance         | Short circuits                            |

|                 | Spiking                 | Open circuits                             |

|                 | Bad metal coverage      | RC time constant variations               |

| Photoresist     | Contamination           | Over or under etching of poly, metal      |

|                 | Over or under exposure  | or field oxide                            |

|                 | Thickness variations    |                                           |

in open circuits or spiking of Al into Si. Corrosion is also a major cause of failure of the metallisation, especially in plastic encapsulated devices where the porosity of the plastic material is responsible for the diffusion of moisture through the package and down to the metallisation [15]. Due to their lower power, CMOS devices are more susceptible to this mechanism than bipolar where the high power dissipation at the semiconductor surface reduces the moisture content. Microcracks are yet another type of failure affecting the metallisation layer. They are due to badly processed oxide steps where the metallisation layer is spread thinly and weakened, enhancing its susceptibility to electromigration.

The oxide is also prone to many types of failures. The gate oxide is susceptible to breakdown under the influence of high electric fields generated by electrical overstress or static discharge [15]. Ion contamination at the manufacturing stage, introduced by human contact, processing or packaging materials, causes the ions to accumulate at the oxide-silicon interface of the gate region of MOS devices under the influence of the electric field. Inversion layers may also be created outside the active regions of transistors because of the movement of electrical charges through the oxide, resulting in threshold voltage shifts, shorts between adjacent active regions, or the formation of parasitic transistors. Another important effect occurs when the electrons in the channel region acquire a high enough energy (hot electrons) to cross the Si-SiO<sub>2</sub> interface, getting trapped in the gate oxide and resulting in a shift of the threshold voltage [15].

Radiation constitutes another source of failures in the field. In addition to radiation produced by trace impurities of radioactive elements in the packaging materials, semiconductor devices are also prone to external radiation sources [16, 17]. Radiation may result in threshold voltage shifts, reduction in transconductance, 'soft' errors in programmed devices, or the activation of parasitic elements. Other external factors that may cause failures include heat, mechanical stress, and electromagnetic interferences [15, 18].

#### b) Package-Related Operational Failures

The commonly observed failures affecting the package [15] are:-

- (i) Bonding failures: In most cases, failures are due to bonds lifting, giving complete open-circuits. This can occur due to formation of intermetallic compounds or insufficient bonding pressure in manufacture. High resistance bonds can also be formed by intermetallics.

- (ii) Die Attachment: The die, or part of it, may break loose under excessive mechanical/electrical stress. The die attachment is the first link in dissipating the heat

- generated in the silicon die. If a void is present, then a local hot spot is formed, leading to further failure.

- (iii) Particulate contamination: Any loose particles introduced during the assembly process may not be detected in screening, or alternatively, particles may become loose after the assembly process as a result of breakages within the device itself. Conducting particles found in failed devices include ends of bond wires, particles of silicon from scribing, gold flakes, and solder balls from cover sealing. Basically, they may all cause short circuits. These have been reported as the primar y cause of 'one-off' failures, prompting the introduction of X-ray inspection as well as Particle Impact Noise Detection (PIND) tests for high reliability devices [18].

#### 2.2.4 The Effects of Scaling

The trend toward greater chip complexity has been accomplished by scaling down feature sizes and increasing die sizes. As device dimensions are reduced, most of the defects and failures listed in the previous sections become more prominent for several reasons. The first is the increasing role played by smaller defects which are much more numerous than larger ones [2]. These smaller defects would not have been fatal in non-scaled devices, but they will cause serious yield and reliability problems when they become commensurate with the reduced device dimensions [19].

Another reason for increased problems with small devices is that the reduction in device dimensions has so far been carried out following constant voltage scaling which is worse for chip power density, current density, and electric field strengths than constant field scaling. High power dissipation leads to higher chip temperatures and thus higher failure rates for those mechanisms with positive activation energies [19]. Higher current densities make metallisation interconnects more susceptible to electromigration, while higher electric field strengths have an impact on hot-electron injection and dielectric breakdown. On the other hand, if the power supply is scaled down with the dimensions, then signal strength and noise margins will suffer. However, capacitive coupling of signal lines will be worse in scaled down devices in both constant field and constant voltage scaling [19].

From a packaging point of view, larger dies are more susceptible to cracking of the passivation layer or the die itself. Higher lead counts can also be detrimental due to the increased probability of a bad or weak bond [19].

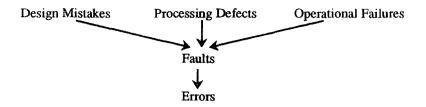

Figure 2.2 Cause-effect relationships.

#### 2.3 FAULT MODELLING: THE EFFECTS OF FAULTS

It was stated previously that errors are caused by faults which, in turn, may be caused by design mistakes, processing defects, or operational failures, as illustrated in Fig. 2.2.

The effects of processing defects and operational failures, listed in the previous section, ranged from short and open circuits to threshold voltage variations and excessive leakage currents. If we want to demonstrate the presence or absence of a fault in a circuit we need to be able to test it so as to produce an error at the output of the circuit, because it is impractical, and most often impossible, to check every interconnect for short or open circuits and every MOS device for the correct threshold voltage. An error is simply the appearance of an output which deviates from the expected one.

The problem is then how to make a fault at one of the thousands of MOS devices or interconnects inside a VLSI chip, such as a threshold voltage variation for example, produce an error at the output of the circuit. Clearly, a general solution to this problem would be very difficult. The problem is usually simplified by making some assumptions about the behaviour of circuits under fault conditions. The process of constructing these assumptions about faults is called *fault modelling*, and the resulting fault assumptions are called a *fault model*.

Hayes [20] defines fault modelling as 'the systematic and precise representation of physical faults (defects and failures) in a form suitable for simulation and test generation. This representation usually involves the definition of abstract or logical faults that produce approximately the same behaviour as the actual physical fault'.

Faults and fault effects may be considered at many different levels: technological, structural, or device levels, as in [21], and circuit, switch, gate or functional levels, as in [20, 22], in order of increasing levels of abstraction. The effects of the failures and defects listed in Section 2.2 belong to the circuit level. At this level, faults are characterised by changes in voltages, currents, or propagation delays which do not lead to efficient fault modelling, so that higher levels of abstraction are usually required. In

the following we will discuss the different abstraction levels commonly adopted to deal with faults.

#### 2.3.1 Logic Level Fault Modelling

Logic level modelling is the most widely used abstraction level in test generation and (fault) simulation of digital circuits. At this level, circuits are represented by an interconnection of logic gates, and all defects and failures are assumed to result in a single node being permanently stuck-at logic one or logic zero [23]. The model was originally proposed as a means by which logic circuits could be tested without the need to apply every possible input [23].

The popularity of the single stuck-at fault model is illustrated by its widespread use, virtually as an industry standard, even for present day VLSI chip testing. There are three main reasons for this popularity. Firstly, the model proved simple and cost-effective for testing logic circuits made up of discrete components mounted on a PCB (the technology for which it was initially proposed). Secondly, even after the introduction of SSI and MSI TTL devices, it still proved adequate, since many of the typical faults in TTL resulted in stuck-at lines. Finally, and most importantly, almost all automatic tools for test related activities (test pattern generation, fault simulation, testability measures) are still based on this model.

The simplicity brought about by the stuck-at fault model stems primarily from it being a gate level model. This can be illustrated by considering the circuit level representation of a single logic gate. The circuit model has many components and interconnects, all subject to a variety of faults. The logic model of the gate has only a single component and few interconnects that are subject to a restricted set of faults [20]. In fact, in the stuck-at fault model, only the inputs and outputs of the gate are considered as possible fault sites; the gate itself is assumed to be fault-free.

An important question about the usefulness of such a simple model is whether physical faults at the circuit level can really be modeled by permanent stuck-at 0's and 1's at the input or output of logic gates. Several studies have attempted to answer this question with results ranging from those still accepting the validity of the model [22, 24, 25] to those doubting its usefulness [26, 27, 28, 29]. However, all such studies agree on the fact that there are certainly many physical faults that cannot be modelled as stuck-at faults.

In studies that found the model acceptable, the main argument is usually that a test derived for single stuck-at faults would detect many of the circuit level faults that cannot be modeled as line stuck-at. Studies that found the model inaccurate propose

its extension to include other faults that are usually observed in circuits, such as shorts between lines, multiple lines stuck-at, and transistor stuck-on and stuck-open faults.

In the extension of the stuck-at fault model to include shorts, or bridging faults, it is assumed that the shorted lines take the same logical value which is the AND or the OR of the values on the lines involved. With this extension, it is clear that some bridging faults cannot be detected: an AND-type short between the inputs to an AND gate, or an OR-type short between the inputs to an OR gate, are examples. Necessary and sufficient conditions for the undetectability of bridging faults are given in [30], together with the cases where an undetectable bridging fault invalidates a test set derived for single stuck-at faults.

A short between nodes a and b where the value of a is a function of b, or b is a function of a, is called a feedback bridging fault. Shorts that create feedback loops represent an additional difficulty because they may introduce asynchronous behaviour and they may cause oscillations even in a combinational network [31].

A major problem in test generation is due to the very large number of possible bridging faults, compared to the number of single stuck-at faults. In a circuit containing n lines, there are 2n possible single stuck-at faults, compared with  $\binom{n}{r}$  possible bridging faults involving r lines. This number can be reduced by looking at the actual layout and considering only bridging faults between nodes that are physically close. However, in a typical VLSI circuit, the number of bridging faults is so large that it is prohibitively expensive to consider each fault individually and derive a test for it. Historically, bridging faults have often been detected by aiming at a high level coverage of single stuck-at faults (in the high 90%) [32]. Mei [24] has shown that, indeed, many bridging faults are detected by single stuck-at test sets, and the remaining faults can be detected by a **reordering** of test vectors or a modification of the single stuck-at test generation algorithm.

In a recent study [33], simulation runs were performed on sample circuits to assess the effectiveness of stuck-at test sets in detecting bridging faults. It was found that stuck-at test sets provide over 98% coverage of bridging faults which is judged (by the authors of the paper) to be inadequate for today's VLSI chips. Their proposed technique to increase the bridging fault coverage is, again, to reorder the stuck-at test vectors so that all nodes change value as often as possible.

Multiple stuck-at faults present the same difficulties as bridging faults: their very large number and the fact that they might invalidate single stuck-at test sets. Hence, they have usually been dealt with in a similar manner, i.e., no attempt is made to derive

tests for individual multiple stuck-at faults, instead, there have been attempts to show that most multiple stuck-at faults are detected by single stuck-at test sets.

There are  $3^n - 1$  possible multiple stuck-at faults in a circuit consisting of n nodes. Even with the use of techniques such as fault equivalence and fault collapsing [34, 35] to reduce the number of faults that need to be considered, it is not possible to bring the total number of faults to manageable limits, especially for large circuits.

For certain classes of circuits, such as two-level combinational networks, and 'restricted' internal fanout-free circuits [36], it has been shown that any single stuck-at test set will detect all multiple faults. However, most practical circuits do not belong to these classes and for general combinational circuits, the undetectability of multiple stuck-at faults by single stuck-at test sets is due to fault masking. A detectable fault f1 is said to be masked by another fault f2, with respect to a test set T, if T detects f1 but fails to detect the simultaneous occurrence of f1 and f2. The task of determining all the conditions under which fault masking occurs is as complex as the task of considering all multiple faults for test generation [37, 38]. In addition, simulating all multiple faults to determine which of them are covered is not practical, although it has been partially carried out for a small circuit, the 74LS181 4-bit ALU [39]. In this study, 16 different complete single stuck-at test sets, generated by different methods, were simulated against all possible double stuck-at faults. Only four test sets (the longest ones) detected all double faults. For the remaining test sets, there were between 1 and 30 undetected double stuck-at faults.

The approach usually adopted in estimating the effectiveness of single stuck-at test sets in detecting multiple faults is to theoretically evaluate some lower bounds on the multiple fault coverage of these test sets [37, 38]. Impressive multiple fault coverage figures can be obtained by such theoretical studies. For example, Jacob et.al [37] show that, in a circuit having three or more outputs, at least 99.67% of all multiple faults are guaranteed to be detected by any single stuck-at test set, irrespective of the size of the circuit. In a small circuit, consisting of 100 nodes, this leaves  $1.4 \times 10^{45}$  undetected multiple faults (the total number of multiple faults is  $5.15 \times 10^{47}$ )!

The great majority of multiple faults are of relatively high multiplicities, and these faults are easily detected because of their drastic effect on circuit operation. However, low multiplicity faults, say up to 5 or 6, are more likely to occur in practice and they are more difficult to detect. In [37], it was found that for a circuit of 10000 lines and 5 outputs, the lower bound on the overall multiple fault coverage of any single stuck-at test set was 99.9929%. Using the same calculations employed in [37], we find that the lower bound on the coverage of double faults is only around 50%.

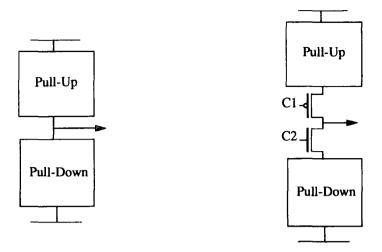

Physical faults that cause a transistor to be permanently on or permanently off, independently of the gate voltage value, cannot be readily modelled at the gate level [40]. An obvious reason for this is that the gate level representation hides the internal structure of the gate. Another reason is that transistor stuck-on faults typically result in certain nodes assuming intermediate voltage levels, while transistor stuck-open faults give rise to high impedance states. Attempts to adapt the gate level model to these types of fault are reported in [41, 42]. The approach is to replace the pull-down and the pull-up networks of each gate by separate networks of logic gates controlling a flip-flop that simulates the memory effect due to stuck-open faults. Besides the complexity of such workaround circuits, they contain nodes that have no correspondence in the real circuits.

The above discussion has shown the limitations of gate level modelling. With the advent of VLSI, all the three reasons for the popularity of the single stuck-at fault model, mentioned earlier, are becoming irrelevant. First, the simplicity brought about by the model is more than offset by the exponential growth in circuit densities, and the resulting large numbers of faults that need to be considered. Secondly, there is definite evidence that many physical faults can result in faulty behaviour that cannot be modelled by stuck-at nodes in a gate-level schematic [26, 27, 28, 29]. Thirdly, the tools used for automatic test pattern generation, fault simulation, and testability analysis are facing increasing problems for chips of VLSI complexities because of the prohibitive computational costs involved.

From the above discussion, we can formulate the following two main problems in modelling circuits at the gate-level:

- For VLSI circuits, the number of primitive elements (gates) becomes very large, leading to a prohibitive number of faults.

- The fault model at the gate level does not cover all realistic physical faults.

Unfortunately, efforts have been made to solve the above problems separately and this has led to the situation where a solution to one problem exacerbates the other.

#### 2.3.2 Functional Level Fault Modelling

Functional-level modelling is usually adopted to cope with the complexity of VLSI circuits. At the functional level, digital circuits are represented by an interconnection of functional units. Each unit is described in terms of the function it implements rather than its internal structure. As an example, a decoder circuit can be described functionally

as having n inputs and  $2^n$  outputs, and in normal operation, only one output line is activated, corresponding to the input address.

The most general functional fault model is based on the appearance of arbitrary changes in the truth table of a combinational circuit or in the state table of a sequential circuit [20]. In the presence of a fault a combinational circuit with inputs can therefore be changed to any of the  $2^{2^{n^4}}$ —1 other —input combinational circuits. The disadvantage of such an approach to fault modelling is that test generation based on this model essentially requires exhaustive testing. A simpler alternative approach that has been suggested consists of considering stuck-at faults on the inputs and outputs of functional units themselves ('pin faults'). However, this was shown to be inadequate even for simple functional units [43].

A more useful approach is to look at a particular function to determine whether any functional fault models are suggested by the function itself. Continuing with the example of the decoder circuit, this approach would lead to the following set of functional faults [22]:

- Instead of the correct line, an incorrect line is activated.

- In addition to the correct line, an incorrect line is also activated.

- No line is activated.

For a general function, deriving a list of functional faults, as above, would normally require an extensive analysis of the effects of physical faults at lower levels of abstraction. This analysis needs to be carried out only at the first time a particular function is used. However, because there is no limit to the number of possible functional units, such analyses have been done only for the most commonly used building blocks in VLSI chips (decoder, multiplexer, PLA, RAM, etc.) [29, 44, 45].

It should be noted that 'functional testing' was in common use before the introduction of the stuck-at fault model which caused a shift towards 'structural testing'. The renewed interest in functional testing, by test engineers in the first instance, has been prompted partly by the unavailability of structural information for many off-the-shelf components (microprocessors and their support circuitry). But perhaps the main reason for the current interest in functional modelling for test generation and fault simulation is that it is hoped that it will bring the same reduction in computational complexity brought about by the replacement of gate level simulation by functional simulation. However, this does not yet appear to be an immediate prospect.

#### 2.3.3 Switch Level Fault Modelling

Switch level modelling was developed in the 1970's primarily to meet the requirements of the then emerging MOS technologies. It was made possible by the fact that an MOS transistor has a switching behaviour that is closer to that of an ideal switch, unlike a bipolar transistor.

At the switch level, logic circuits are modelled as a set of nodes connected by transistor switches. MOS transistors are modelled as resistive switches, with the resistance being a function of the dimensions of the transistor. Nodes have capacitances associated with them. In addition to the two logic levels 0 and 1, nodes also have strength levels, which take into account the impedance of the node, the impedances of the other nodes that are connected to it through MOS transistors, and the conductances of these connecting transistors. For a more formal description of these concepts see [46, 47].

Switch level modelling is very similar to circuit level modelling as in SPICE for example. However, in switch level modelling, transistor resistances, node values, strengths and capacitances are confined to a small set of possible discrete values, unlike the analog circuit level modelling. It is more accurate than gate level modelling, for both the behaviour and the structure of MOS circuits, while avoiding the high computational costs associated with analog electrical models.

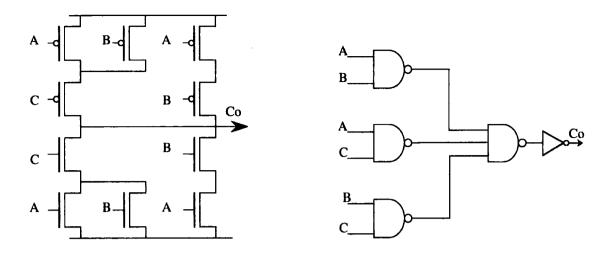

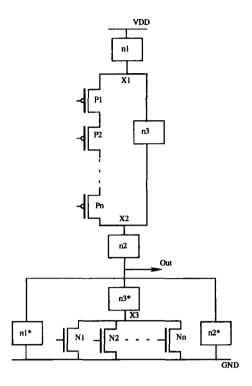

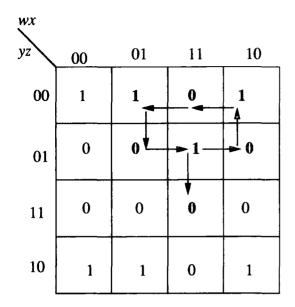

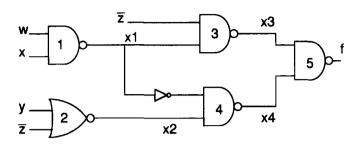

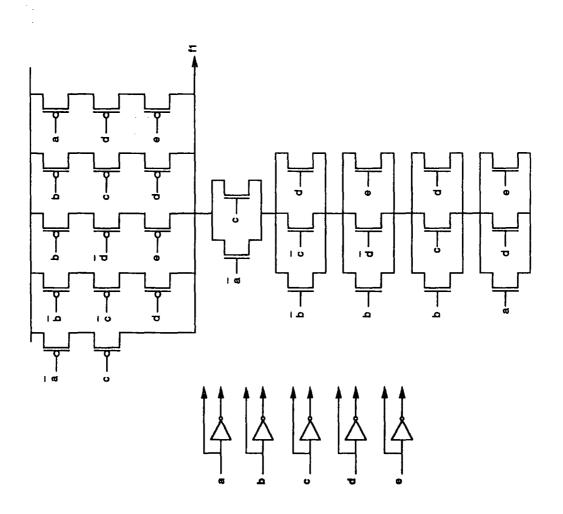

The fact that switch level models operate on a direct representation of transistor structure makes it possible to model important phenomenon in MOS digital circuits, such as bidirectionality of signal flow and dynamic charge storage. Furthermore, MOS logic circuits often contain structures, such as pass transistors and dynamic latches, that have no correspondence in logic gates. For instance, a CMOS complex gate, implementing a non-primitive logic function, can be represented by a network of primitive gates at the logic level, as shown in Fig. 2.3. However, it can be seen that some of the nodes on the gate level representation do not exist in the real circuit, while some of the nodes in the real circuit have no correspondence in the gate level representation.

The most appealing feature of switch level modelling is the ease of modelling faults without the need for the complex work-around circuits that have to be added for gate level modelling, especially for CMOS faults. For instance, stuck-open and stuck-on faults can be modelled by setting an MOS transistor resistance to a very large (infinite) value or to zero. Alternatively, a stuck-open fault can be modelled by inserting a series transistor with the gate tied to a fixed value. Similarly, stuck-on faults can be modelled by adding parallel transistors. Line breaks and bridging faults can be modelled by just breaking or adding connections.

Figure 2.3 A CMOS complex gate and its gate level representation.

Rajsuman et.al. [48, 49] found that switch level modelling of bridging faults in NMOS and CMOS complex gates can be in good agreement with the equivalent circuit level modelling. The only difference between the two was that when the switch level analysis results in an indeterminate value, the circuit level analysis can often predict a definite voltage. However, this voltage is so dependent on the circuit parameters used that it is best taken as indeterminate.

Hayes [46] claims that the adoption of switch level modelling of fault-free circuits results in only a moderate increase in computational costs, whereas Bryant [47] claims that it can be implemented without incurring any increase at all, compared to gate level modelling. However, when it comes to fault modelling, the switch level is clearly more computationally intensive, since the number of primitive elements is much larger, and the set of possible faults per primitive element is also larger than in gate level models.

#### 2.3.4 Layout Level Fault Modelling

Analyzing the effects of manufacturing faults at the layout level is not as widespread as the higher modelling levels mentioned in the previous sections. In fact, only a single research group advocates its use [50, 51, 52], and it is included here only because of the somewhat controversial results reported by this group.

In their first paper [50], the authors describe the method, called 'inductive fault analysis', by which they relate point defects to faulty behaviour at circuit level and then logic level. The method consists of injecting spot defects of random sizes, at random locations on the layout, and then extracting the resulting electrical circuit and analyzing it to determine any deviations from the fault-free circuit. The sizes and locations of

the defects are randomly generated so that they follow probability distribution functions usually observed on processing lines. The observed faults are then ranked according to their frequency of occurrence, hence the label 'realistic'.

The results of the application of inductive fault analysis to n-MOS circuits are reported in [51]. It is indicated that only 10% of the simulated defects actually produce significantly faulty behaviour at the circuit level. Among these, only 28% of the faults can readily be modelled by line stuck-at faults at the gate level. It is also pointed out that most of the transistor stuck faults can be 'implicitly' modelled by the classical line stuck-at fault model, which is not surprising for an n-MOS circuit. This makes the classical fault model able to account for 64% of all possible faults. Although the simulation involved an n-MOS circuit, it is pointed out that less than 3% of the faults were transistor stuck-off faults.

In their latest paper [52], the authors apply their method to CMOS circuits. It is found that, for the simulated circuits, the classical single stuck-at fault model accounts for less than half of the faults. Furthermore, it is claimed that the adoption of switch level modelling provides little improvement. It is claimed that only 1% of the faults result in the sequential behaviour due to transistors being stuck-off. It should be noted that 70% of the transistors in the example circuits used by the authors are either pass transistors or parts of an inverter. Although the authors recognise that this might be the reason for the very low percentage of stuck-open faults resulting in sequential behaviour, they still maintain that this type of fault does not deserve the considerable research effort devoted to it in recent years. Shen [53] considers such type of faults as being arbitrary, and the research devoted to it as an academic exercise.

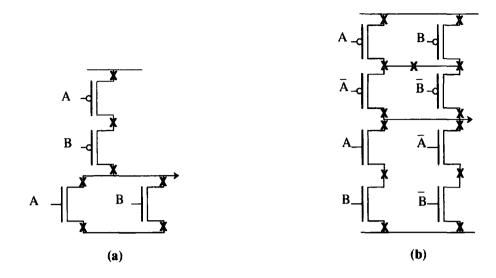

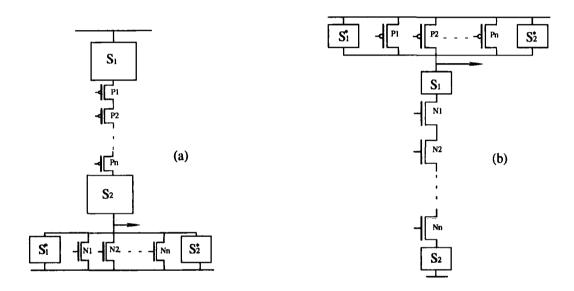

It should be noted that a large proportion of the simulated defects reported in the above papers resulted in breaks. The authors do not seem to realise that a break is a potential source of CMOS stuck-open faults. For example, in the NAND gate, shown in Fig. 2.4(a), four out of the seven possible breaks shown result in stuck-open faults, whereas in the EX-OR gate at (b) all possible breaks result in a stuck-open faults.

Besides the controversial results, inductive fault analysis is believed to go against the philosophy of integrating design and test activities. If a chip designer has to wait until the layout phase is completed to find out that the chip is difficult to test, then it would be very expensive to redesign the chip so that it is easily testable. Furthermore, the suggested approach of submitting a ranked fault list for test pattern generation is attractive only to the person generating the tests: it allows him/her to claim impressive fault coverage, since tests are generated for the most likely faults and these faults are given a higher weight in computing the fault coverage. From a user's point of view, the

Figure 2.4 Possible sites of CMOS stuck-open faults.

presence of an undetectable fault is unacceptable, even if the fault has a low probability of occurrence.

#### 2.4 FAULT DETECTION

Fault detection is the cornerstone of any fault-tolerance strategy. Several techniques for fault detection have been developed over the years. They can be broadly classified as either off-line or on-line detection techniques. In off-line fault detection, the normal operation of the circuit is interrupted and a stimuli are applied to the circuit to produce errors at the outputs if a fault is present. In on-line techniques, error detection is performed during normal operation by monitoring the output of the circuit or by some form of repetition of the function of the circuit. Duplication is the standard for comparison with all other fault detection techniques, since it is the simplest and it covers a wide variety of fault types.

There is a fundamental difference between off-line fault detection and on-line error detection that is often overlooked. In off-line techniques, stimuli are applied to the circuit so that, if a fault is present, an erroneous output is produced. Thus, they effectively detect the presence of faults by producing errors at the outputs. On-line error detection, on the other hand, will detect a fault only if and when the fault produces an error. For example, single error detecting schemes will, eventually, detect only those faults that result in a single error at the output. This does not imply that all single faults are eventually detected, since a single fault can cause more than one output to be erroneous. When deriving a test for a fault which causes more than one output to be erroneous,

the fault is considered to be easily detectable, whereas in on-line detection techniques, this situation is undesirable.

The various fault detection techniques are discussed in the next subsections.

#### 2.4.1 On-Line Error Detection Using Coding Techniques

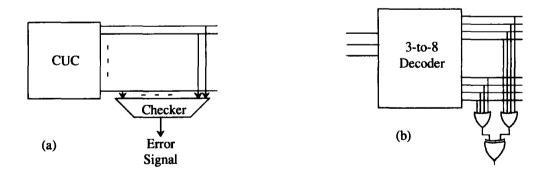

Coding techniques, as applied to digital circuits, are based on the idea that if, for an m-output circuit, only k out of the  $2^m$  possible output combinations may occur in a fault-free circuit, then the occurrence of any of the remaining  $2^m - k$  output combinations is an indication of the presence of a fault. The outputs of the circuit under consideration (CUC) are continuously monitored by another circuit, called a checker, for the occurrence of invalid outputs. The combination of a CUC and its checker then becomes a self-checking circuit (see Fig. 2.5a). Formally, the k valid output combinations are called 'code words' and the remaining  $2^m - k$  output combinations are called 'non-code words'. For example, in a decoder circuit only one output line should be activated at a time. This fact can be used to design a simple circuit that will check for correct operation as illustrated in Fig. 2.5(b) where the outputs are assumed to be active high. Here, all the output code words will have exactly a single 1 and seven 0s. Note that if a fault in the decoder causes an incorrect line to be activated, then the checker will not detect it. This is because the fault has changed one code word into another, incorrect, code word. In addition, a stuck-at 1 fault on the output of the checker is undetectable. Solutions to the above problems, and some others, will be discussed in the following.

Figure 2.5 A self-checking circuit (a) and a self-checking decoder (b).

If a circuit function allows all  $2^m$  possible output combinations, which is the case in most practical circuits, then there are two approaches to the use of coding techniques for error detection. In the first approach, the number of outputs is increased to some value

$m_1$  so that there would be  $2^{m_1-m}$  output combinations that are non-code words. In addition, if the faults on the inputs to the circuit are to be detected, then it is necessary to increase the number of inputs so that a proportion of the input combinations would be invalid, or non-code words. Although the number of inputs and outputs can be augmented in an arbitrary fashion, and the circuit redesigned accordingly, in practice, this augmentation is carried out using error detecting codes [54, 55]. Once a code has been selected, the circuit must then be redesigned in such a way that:

- 1) any fault in the circuit must cause the output to be either a non-code word or the correct code word, but never an incorrect code word, and

- 2) for each fault in the circuit, there must exist at least one input code word that would produce a non-code word at the output, if the fault is present.

A circuit that has property 1) is said to be *fault-secure*. Fault-secureness ensures that the circuit output is either correct or, if it is incorrect, it is a non-code word and hence it is detected by the checker. A circuit having property 2) is said to be *self-testing*. This property ensures that every fault will eventually produce a non-code word, and therefore, will be detected by the checker. A circuit that is both fault-secure and self-testing is called a *totally self-checking*, TSC, circuit [54].

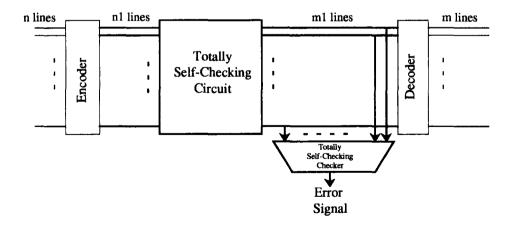

To address the problems of faults in the checker itself, it is necessary to make the checker totally self-checking as well. However, since the inputs to the checker, i.e., the outputs of the circuit, are already encoded, the design of a totally self-checking checker is usually simpler than the design of a TSC circuit. Figure 2.6 shows the resulting general form of a totally self-checking network when both the circuit under consideration and the checker are totally self-checking.

Figure 2.6 The general form of a totally self-checking network.

It should be noted that if the encoder and the decoder are considered to be part of the network, then it is no longer a TSC network. Faults in the encoder may result in an incorrect code word being applied to the circuit, and so that some faults will not be detected. The detection of faults within the encoder requires that the encoder itself be totally self-checking, i.e, a second encoder is needed before the first one. Similarly, the detection of faults in the second encoder requires a third encoder, and so on, *ad finitum*. The same problem exists on the output side: if faults in the decoder circuit are to be detected, then the outputs of the decoder must form a code that is decoded by another decoder. These problems can be lessened, but not eliminated, if the inputs to the CUC are already encoded, and if the outputs do not need to be decoded before being used by subsequent units. This requires that the same coding scheme be used uniformly throughout the system.

There is no systematic method for designing an arbitrary circuit so that it is totally self-checking. Most, if not all, publications on the subject concentrate on the design of totally self-checking checkers for different codes, and the design approach usually consists of designing a checker and then verifying that it is TSC.

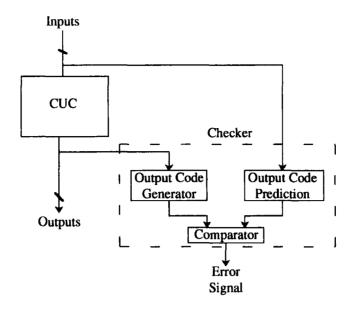

The second approach in using coding techniques for concurrent error detection does not require the redesign of the CUC so that it is TSC, as illustrated in Fig. 2.7. It is therefore somewhat simpler than the first approach. Only separable codes can be used in such a manner and most applications of coding techniques in digital circuits use this approach. The only section that is TSC is the comparator even though such a structure is able to detect all single errors. Note that this is different from single fault detection. A single fault in the CUC may cause more than one erroneous output that may not be detected.

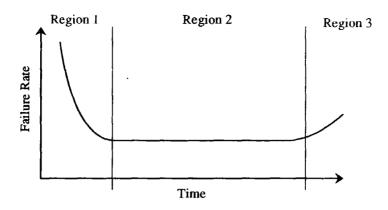

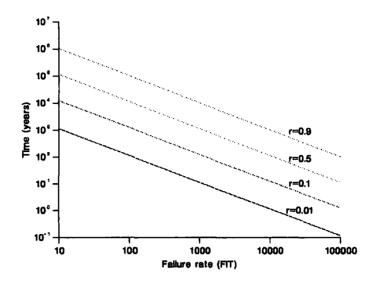

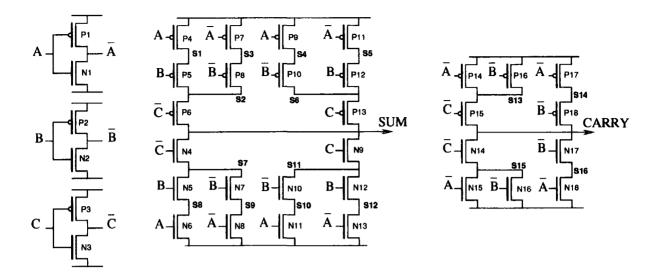

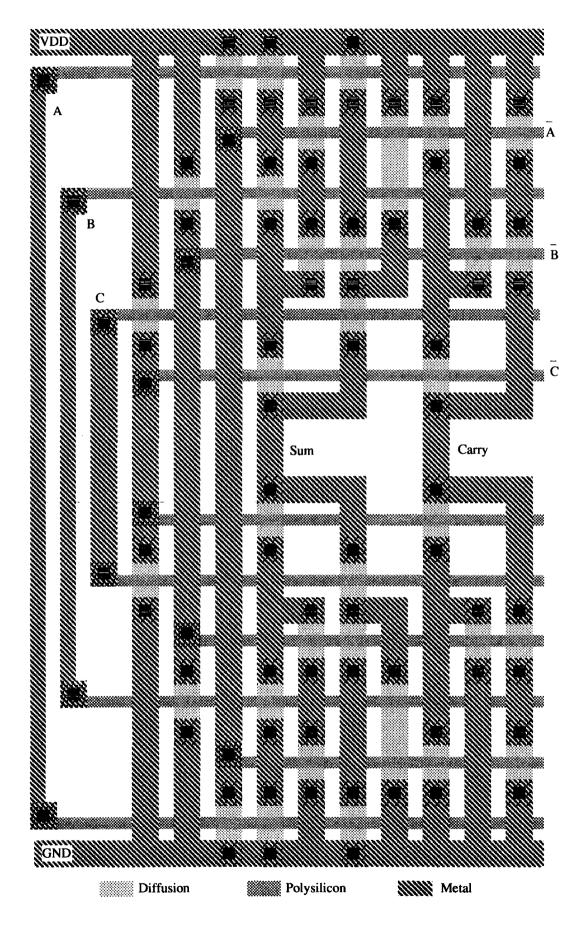

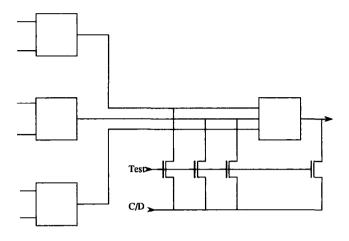

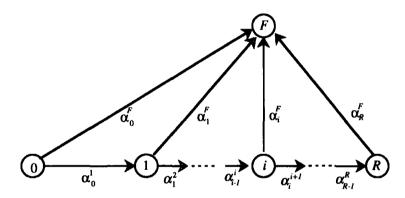

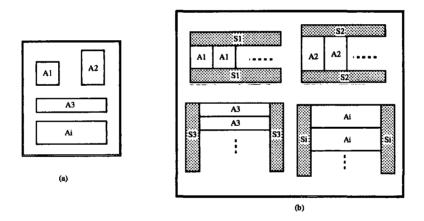

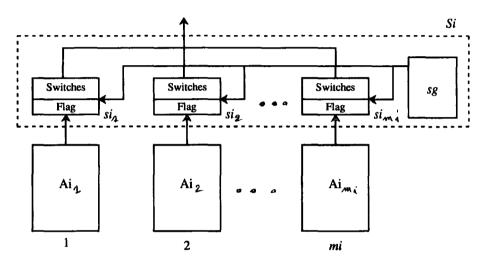

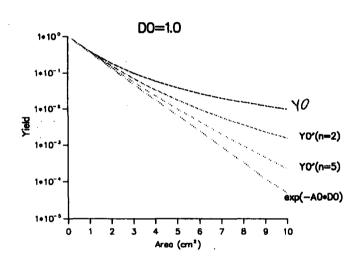

The output code generator in this approach is simply an encoder. It is clear that the output code prediction requires some knowledge of the function implemented by the CUC. In the simple case of an adder circuit using a residue code, for example, the output code prediction involves generating the check bits of the input operands and summing these check bits. In more general cases, the output code prediction circuitry can be as complex as the functional circuit.