### **Durham E-Theses**

### Parallel solution of power system linear equations

Grey, David John

#### How to cite:

Grey, David John (1995) Parallel solution of power system linear equations, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/5429/

#### Use policy

$The full-text\ may\ be\ used\ and/or\ reproduced,\ and\ given\ to\ third\ parties\ in\ any\ format\ or\ medium,\ without\ prior\ permission\ or\ charge,\ for\ personal\ research\ or\ study,\ educational,\ or\ not-for-profit\ purposes\ provided\ that:$

- $\bullet\,$  a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

Academic Support Office, The Palatine Centre, Durham University, Stockton Road, Durham, DH1 3LE e-mail: e-theses.admin@durham.ac.uk Tel: +44 0191 334 6107 http://etheses.dur.ac.uk The copyright of this thesis rests with the author. No quotation from it should be published without his prior written consent and information derived from it should be acknowledged.

# Parallel Solution of Power System Linear Equations

David John Grey B.Eng. (York)

School of Engineering and Computer Science University of Durham

A thesis submitted in partial fulfilment of the requirements of the Council of the University of Durham for the Degree of Doctor of Philosophy (Ph.D.).

February 1995

i

e

### Abstract

At the heart of many power system computations lies the solution of a large sparse set of linear equations. These equations arise from the modelling of the network and are the cause of a computational bottleneck in power system analysis applications. Efficient sequential techniques have been developed to solve these equations but the solution is still too slow for applications such as real-time dynamic simulation and on-line security analysis. Parallel computing techniques have been explored in the attempt to find faster solutions but the methods developed to date have not efficiently exploited the full power of parallel processing.

This thesis considers the solution of the linear network equations encountered in power system computations. Based on the insight provided by the elimination tree, it is proposed that a novel matrix structure is adopted to allow the exploitation of parallelism which exists within the cutset of a typical parallel solution. Using this matrix structure it is possible to reduce the size of the sequential part of the problem and to increase the speed and efficiency of typical LU-based parallel solution. A method for transforming the admittance matrix into the required form is presented along with network partitioning and load balancing techniques.

Sequential solution techniques are considered and existing parallel methods are surveyed to determine their strengths and weaknesses. Combining the benefits of existing solutions with the new matrix structure allows an improved LU-based parallel solution to be derived. A simulation of the improved LU solution is used to show the improvements in performance over a standard LU-based solution that result from the adoption of the new techniques. The results of a multiprocessor implementation of the method are presented and the new method is shown to have a better performance than existing methods for distributed memory multiprocessors.

### Declaration

•

I hereby declare that this thesis is a record of work undertaken by myself, that it has not been the subject of any previous application for a degree, and that all sources of information have been duly acknowledged.

.

### © Copyright 1994, David John Grey

The copyright of this thesis rests with the author. No quotation from it should be published without his written consent, and information derived from it should be acknowledged.

This thesis is dedicated to Anna, my wife and best friend.

### Acknowledgments

The following people have been vital to the production of this work; either in their direct advice and input or just in putting up with me whilst I was going crazy writing it.

- To my wife, Anna for her love and support.

- To my supervisor, Doctor Janusz Bialek of the University of Durham for his direction and advice.

- To Kelvey Marden of the University of Durham for friendship.

- To Alan, Alex, John, Raghu, Jeremy, Juliette, Sue, Matt, Chris, Phil, Howard and Hayley – for companionship and a good laugh when in need.

- To Alan with grateful thanks for all the proof reading

The following trademarks are acknowledged: IMS, INMOS, TRAM and occam are trademarks of Inmos Limited; I.B.M. and P.C./A.T. are a trademarks of International Business Machines Corp.; Unix is a trademark of AT & T.

v

# List of Abbreviations

| BBDF    | Bordered Block Diagonal Form                                         |  |  |

|---------|----------------------------------------------------------------------|--|--|

| CEGB    | Central Electricity Generating Board (now the National Grid Company) |  |  |

| CSP     | Communicating Sequential Processes                                   |  |  |

| FPU     | Floating Point Unit                                                  |  |  |

| IBM     | International Business Machines                                      |  |  |

| IEEE    | Institute of Electrical & Electronic Engineers                       |  |  |

| I/O     | Input and Output                                                     |  |  |

| MD      | Minimum Degree                                                       |  |  |

| MDML    | Minimum Degree Minimum Length                                        |  |  |

| MDMLLRU | Minimum Degree Minimum Length Least Recently Used                    |  |  |

| MFLOPS  | Million Floating point Operations per Second                         |  |  |

| MIMD    | Multiple Instruction stream Multiple Data stream                     |  |  |

| MISD    | Multiple Instruction stream Single Data stream                       |  |  |

| ML      | Minimum Length                                                       |  |  |

| MLMD    | Minimum Length Minimum Degree                                        |  |  |

| RAM     | Random Access Memory                                                 |  |  |

| RBBDF   | Recursive Bordered Block Diagonal Form                               |  |  |

| RISC    | Reduced Instruction Set Computer                                     |  |  |

| RP      | Recursively Parallel                                                 |  |  |

| SIMD    | Single Instruction stream Multiple Data stream                       |  |  |

| SISD    | Single Instruction stream Single Data stream                         |  |  |

| TRAM    | Transputer Application Module                                        |  |  |

|         |                                                                      |  |  |

# Contents

•

,

| 1 | Intr | oducti  | on                                              | 1  |

|---|------|---------|-------------------------------------------------|----|

|   | 1.1  | The C   | omponents of a Power System                     | 1  |

|   | 1.2  | Power   | System Analysis                                 | 4  |

|   |      | 1.2.1   | The Power Flow Problem                          | 5  |

|   |      | 1.2.2   | Power System Simulation                         | 5  |

|   |      | 1.2.3   | Power System Security                           | 9  |

|   |      | 1.2.4   | System Planning                                 | 10 |

|   |      | 1.2.5   | Operator Training                               | 11 |

|   | 1.3  | Power   | Systems Analysis and Computer Architectures     | 12 |

|   | 1.4  | Paralle | el Processing and Parallel Architectures        | 14 |

|   |      | 1.4.1   | Classification of Computer Architectures        | 14 |

|   |      | 1.4.2   | SIMD Architectures                              | 17 |

|   |      | 1.4.3   | MIMD Architectures                              | 18 |

|   |      | 1.4.4   | Interconnection Networks for MIMD Architectures | 20 |

|   |      | 1.4.5   | The INMOS Transputer                            | 22 |

|   |      | 1.4.6   | Bounds on Multiprocessor Performance            | 23 |

|   | 1.5  | Paralle | el Processing in Power System Analysis Problems | 28 |

|   | 1.6  | Summa   | ary                                             | 29 |

|   | 1.7  | Outlin  | e of Thesis                                     | 30 |

| 2 | Solv | ving th | e Network Equations                             | 33 |

|   | 2.1  | Modeli  | ng the Power System                             | 33 |

|   |      | 2.1.1   | The Generator Model                             | 33 |

|   |      | 2.1.2   | The Load Model                                  | 34 |

|   |      | 2.1.3   | The Transmission Line Model                     | 34 |

.

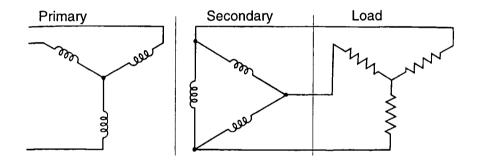

|   |     | 2.1.4   | The Transformer Model                                           | 35 |

|---|-----|---------|-----------------------------------------------------------------|----|

|   | 2.2 | Forma   | lizing the Problem                                              | 35 |

|   | 2.3 | Linear  | · Equations, Matrices and Sparsity                              | 38 |

|   | 2.4 | Direct  | Solution of the Linear Equations                                | 39 |

|   |     | 2.4.1   | Gaussian Elimination and Fill-Ins                               | 39 |

|   |     | 2.4.2   | LU Decomposition                                                | 42 |

|   |     | 2.4.3   | LDU Decomposition                                               | 43 |

|   |     | 2.4.4   | Bifactorisation                                                 | 44 |

|   | 2.5 | Pivota  | l Ordering                                                      | 50 |

|   |     | 2.5.1   | Pre - Ordering                                                  | 50 |

|   |     | 2.5.2   | Dynamic Ordering                                                | 51 |

|   | 2.6 | Elimin  | ation Trees                                                     | 53 |

|   | 2.7 | Near (  | Optimal Ordering Strategies                                     | 55 |

|   |     | 2.7.1   | The Minimum Degree Algorithm                                    | 55 |

|   |     | 2.7.2   | The Minimum Length Algorithm                                    | 57 |

|   |     | 2.7.3   | The Minimum Degree Minimum Length Algorithm                     | 58 |

|   |     | 2.7.4   | The Minimum Length Minimum Degree Algorithm                     | 58 |

|   |     | 2.7.5   | The Minimum Degree Minimum Length Least Recently Used Algorithm | 59 |

|   |     | 2.7.6   | Comparative Analysis of the Ordering Methods                    | 59 |

|   |     | 2.7.7   | Deriving the Elimination Tree                                   | 61 |

|   | 2.8 | Impler  | nenting a Sequential Solution of the Network Equations          | 62 |

|   |     | 2.8.1   | Storage of Sparse Matrices                                      | 62 |

|   |     | 2.8.2   | Determination of Elimination Ordering                           | 63 |

|   |     | 2.8.3   | Coefficient Matrix Factorisation Using Bifactorisation          | 64 |

|   | 2.9 | Summ    | ary                                                             | 65 |

| 3 | Par | allel M | Iethods of Solving the Network Equations                        | 67 |

|   | 3.1 | Introd  | uction                                                          | 67 |

|   | 3.2 | Iterati | ve Methods for Solving Linear Equations                         | 68 |

|   |     | 3.2.1   | The Jacobi Method                                               | 68 |

|   |     | 3.2.2   | The Gauss-Seidel Method                                         | 70 |

|   |     | 3.2.3   | The Conjugate Gradient Method                                   | 71 |

|   | 3.3 | Direct  | vs Iterative Methods                                            | 75 |

|     | 3.4                               | Parall                                                                                                      | el Algorithms for Direct Solution                                                                                                             | 78                                                                                      |

|-----|-----------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|     |                                   | 3.4.1                                                                                                       | Granularity of Solution                                                                                                                       | 78                                                                                      |

|     |                                   | 3.4.2                                                                                                       | Task Mapping and Load Balancing                                                                                                               | 79                                                                                      |

|     |                                   | 3.4.3                                                                                                       | Ordering Strategies for Parallel Solutions                                                                                                    | 81                                                                                      |

|     | 3.5                               | Diakoj                                                                                                      | ptical Based Solution Methods                                                                                                                 | 82                                                                                      |

|     |                                   | 3.5.1                                                                                                       | The Method of Diakoptics                                                                                                                      | 82                                                                                      |

|     | 3.6                               | The M                                                                                                       | Iultiple Factoring Method                                                                                                                     | 84                                                                                      |

|     | 3.7                               | Paralle                                                                                                     | el LU Decomposition Techniques                                                                                                                | 88                                                                                      |

|     |                                   | 3.7.1                                                                                                       | Chan's Method                                                                                                                                 | 91                                                                                      |

|     |                                   | 3.7.2                                                                                                       | The W-matrix Method                                                                                                                           | 92                                                                                      |

|     | 3.8                               | Choles                                                                                                      | sky Factorisation Techniques                                                                                                                  | 95                                                                                      |

|     |                                   | 3.8.1                                                                                                       | The Parallel Fan-In Algorithm                                                                                                                 | 97                                                                                      |

|     |                                   | 3.8.2                                                                                                       | The Parallel Fan-Out Algorithm                                                                                                                | 98                                                                                      |

|     |                                   | 3.8.3                                                                                                       | Frontal Methods                                                                                                                               | 98                                                                                      |

|     | 3.9                               | Summ                                                                                                        | ary                                                                                                                                           | 99                                                                                      |

| 4   | Elin                              | ninatio                                                                                                     | on Trees, Network Partitioning and Load Balancing                                                                                             | 101                                                                                     |

|     | 4.1                               | Introd                                                                                                      | uction                                                                                                                                        | 101                                                                                     |

|     |                                   |                                                                                                             |                                                                                                                                               |                                                                                         |

|     | 4.2                               | Balanc                                                                                                      | ring the Computational Load                                                                                                                   | 102                                                                                     |

|     | 4.2                               | Balance<br>4.2.1                                                                                            | The Two Approaches to Load Balancing                                                                                                          | 102<br>105                                                                              |

|     | 4.2                               |                                                                                                             |                                                                                                                                               |                                                                                         |

|     | <ul><li>4.2</li><li>4.3</li></ul> | 4.2.1<br>4.2.2                                                                                              | The Two Approaches to Load Balancing                                                                                                          | 105                                                                                     |

|     |                                   | 4.2.1<br>4.2.2<br>The E                                                                                     | The Two Approaches to Load Balancing                                                                                                          | 105<br>109<br>110                                                                       |

|     |                                   | 4.2.1<br>4.2.2<br>The E                                                                                     | The Two Approaches to Load Balancing                                                                                                          | 105<br>109<br>110                                                                       |

|     |                                   | 4.2.1<br>4.2.2<br>The E<br>4.3.1                                                                            | The Two Approaches to Load Balancing                                                                                                          | 105<br>109<br>110<br>112                                                                |

|     |                                   | 4.2.1<br>4.2.2<br>The E<br>4.3.1<br>4.3.2                                                                   | The Two Approaches to Load Balancing                                                                                                          | 105<br>109<br>110<br>112<br>114                                                         |

| -   |                                   | 4.2.1<br>4.2.2<br>The E<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4                                                 | The Two Approaches to Load Balancing Load Balancing Methodologies Adopted by Other Parallel Solutions limination Tree and Parallel Processing | 105<br>109<br>110<br>112<br>114<br>116                                                  |

|     | 4.3<br>4.4                        | 4.2.1<br>4.2.2<br>The E<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Summ                                         | The Two Approaches to Load Balancing Load Balancing Methodologies Adopted by Other Parallel Solutions limination Tree and Parallel Processing | 105<br>109<br>110<br>112<br>114<br>116<br>119<br>119                                    |

| . 5 | 4.3<br>4.4<br>An                  | 4.2.1<br>4.2.2<br>The E<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Summ                                         | The Two Approaches to Load Balancing Load Balancing Methodologies Adopted by Other Parallel Solutions limination Tree and Parallel Processing | 105<br>109<br>110<br>112<br>114<br>116<br>119<br>119<br><b>121</b>                      |

| . 5 | 4.3<br>4.4<br><b>An</b><br>5.1    | 4.2.1<br>4.2.2<br>The E<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Summ<br>Improv<br>Introd                     | The Two Approaches to Load Balancing Load Balancing Methodologies Adopted by Other Parallel Solutions limination Tree and Parallel Processing | 105<br>109<br>110<br>112<br>114<br>116<br>119<br>119<br><b>121</b>                      |

| 5   | 4.3<br>4.4<br>An                  | 4.2.1<br>4.2.2<br>The E<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Summ<br>Improv<br>Introd<br>Develo           | The Two Approaches to Load Balancing                                                                                                          | 105<br>109<br>110<br>112<br>114<br>116<br>119<br>119<br><b>121</b><br>121<br>122        |

| 5   | 4.3<br>4.4<br><b>An</b><br>5.1    | 4.2.1<br>4.2.2<br>The E<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Summ<br>Improv<br>Introd<br>Develoo<br>5.2.1 | The Two Approaches to Load Balancing Load Balancing Methodologies Adopted by Other Parallel Solutions limination Tree and Parallel Processing | 105<br>109<br>110<br>112<br>114<br>116<br>119<br>119<br><b>121</b><br>121<br>122<br>122 |

| 5   | 4.3<br>4.4<br><b>An</b><br>5.1    | 4.2.1<br>4.2.2<br>The E<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Summ<br>Improv<br>Introd<br>Develo           | The Two Approaches to Load Balancing                                                                                                          | 105<br>109<br>110<br>112<br>114<br>116<br>119<br>119<br><b>121</b><br>121<br>122        |

٠

|   |                   | 5.2.4                                                         | Reducing the Sequential Part of the Method | 131                                                                                                   |

|---|-------------------|---------------------------------------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------|

|   | 5.3               | A Sim                                                         | ulation of the Recursively Parallel Method | 132                                                                                                   |

|   |                   | 5.3.1                                                         | Implementation                             | 133                                                                                                   |

|   |                   | 5.3.2                                                         | Results of the Simulation                  | 137                                                                                                   |

|   | 5.4               | Summ                                                          | nary                                       | 143                                                                                                   |

| 6 | Issu              | es of I                                                       | Parallel Implementation                    | 145                                                                                                   |

|   | 6.1               | Introd                                                        | luction                                    | 145                                                                                                   |

|   | 6.2               | Algori                                                        | thmic Issues                               | 146                                                                                                   |

|   |                   | 6.2.1                                                         | Program Structure and Task Design          | 146                                                                                                   |

|   |                   | 6.2.2                                                         | Data Storage and Data Structures           | 150                                                                                                   |

|   |                   | 6.2.3                                                         | Reducing the Communication Overhead        | 159                                                                                                   |

|   | 6.3               | Archit                                                        | ectural Issues                             | 160                                                                                                   |

|   |                   | 6.3.1                                                         | The Software Architecture                  | 160                                                                                                   |

|   |                   | 6.3.2                                                         | The Hardware Architecture                  | 166                                                                                                   |

|   | 6.4               | Perfor                                                        | mance of the Recursively Parallel Solution | 172                                                                                                   |

|   | 6.5               | Summ                                                          | ary                                        | 189                                                                                                   |

| 7 | Fur               | ther W                                                        | Vork                                       | 190                                                                                                   |

|   | 7.1               | Autom                                                         | natic Network Partitioning                 | 190                                                                                                   |

|   | 7.2               | The Se                                                        | earch for an Optimal Ordering              | 193                                                                                                   |

|   | 7.3               | Block-                                                        | oriented Solution and Vector Processing    | 196                                                                                                   |

|   | 7.4               | Summ                                                          | ary                                        | 199                                                                                                   |

| 8 |                   |                                                               | ary                                        |                                                                                                       |

| - | Con               | clusio                                                        |                                            | 201                                                                                                   |

|   | <b>Con</b><br>8.1 | clusio                                                        |                                            |                                                                                                       |

| A | 8.1               | <b>clusio</b><br>Conclu                                       | ns                                         | 201                                                                                                   |

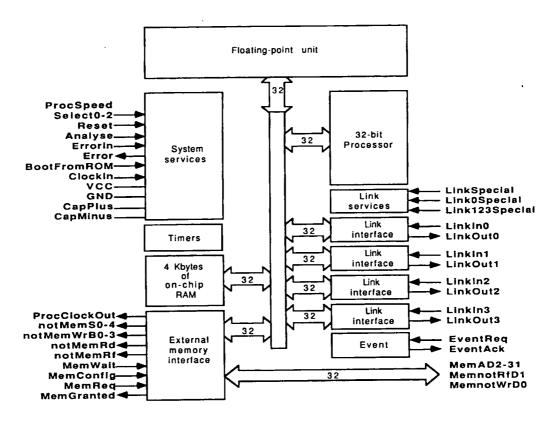

| _ | 8.1               | clusion<br>Conclu<br>INM(                                     | ns<br>1sions                               | <b>201</b><br>201                                                                                     |

| _ | 8.1<br><b>The</b> | clusion<br>Conclu<br>INM(                                     | ns<br><sup>1sions</sup>                    | <ul><li>201</li><li>201</li><li>215</li></ul>                                                         |

| _ | 8.1<br><b>The</b> | clusion<br>Conclu<br>INM<br>The A                             | ns<br>1sions                               | <ul> <li>201</li> <li>201</li> <li>215</li> <li>216</li> </ul>                                        |

| _ | 8.1<br><b>The</b> | clusion<br>Conclu<br>INMO<br>The A<br>A.1.1                   | ns<br>Isions                               | <ul> <li>201</li> <li>201</li> <li>215</li> <li>216</li> <li>218</li> </ul>                           |

| _ | 8.1<br><b>The</b> | clusion<br>Conclu<br>INMO<br>The A<br>A.1.1<br>A.1.2<br>A.1.3 | ns<br>Isions                               | <ul> <li>201</li> <li>201</li> <li>215</li> <li>216</li> <li>218</li> <li>219</li> </ul>              |

| _ | 8.1<br>The<br>A.1 | clusion<br>Conclu<br>INMO<br>The A<br>A.1.1<br>A.1.2<br>A.1.3 | ns Usions                                  | <ul> <li>201</li> <li>201</li> <li>215</li> <li>216</li> <li>218</li> <li>219</li> <li>219</li> </ul> |

| в | Der                                                         | ivation Of The Models of Power System Elements                                                                 | 225                                                            |

|---|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

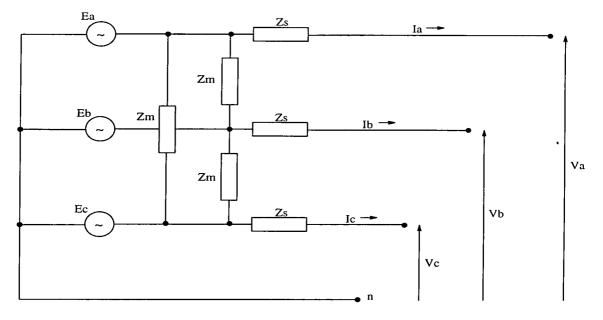

|   | <b>B.</b> 1                                                 | The Generator Model                                                                                            | 225                                                            |

|   | B.2                                                         | The Transmission Line Model                                                                                    | 227                                                            |

|   |                                                             | B.2.1 Short Lines                                                                                              | 228                                                            |

|   |                                                             | B.2.2 Medium Length Lines                                                                                      | 228                                                            |

|   |                                                             | B.2.3 Long Lines                                                                                               | 230                                                            |

|   | B.3                                                         | The Transformer Model                                                                                          | 233                                                            |

|   | B.4                                                         | The Load Model                                                                                                 | 236                                                            |

| С | Der                                                         | iving the Bus Admittance Matrix                                                                                | 239                                                            |

|   |                                                             |                                                                                                                |                                                                |

| D | Net                                                         | work Partitioning and Diakoptics                                                                               | 242                                                            |

| D | Net<br>D.1                                                  | work Partitioning and Diakoptics Node Tearing                                                                  | <b>242</b><br>243                                              |

| D | D.1                                                         | <b>–</b> –                                                                                                     |                                                                |

| _ | D.1<br>D.2                                                  | Node Tearing                                                                                                   | 243                                                            |

| _ | D.1<br>D.2                                                  | Node Tearing                                                                                                   | 243<br>244                                                     |

| _ | D.1<br>D.2<br><b>Pro</b>                                    | Node Tearing                                                                                                   | 243<br>244<br><b>247</b>                                       |

| _ | D.1<br>D.2<br><b>Pro</b><br>E.1                             | Node Tearing       .         Branch Cutting       .         of of Liu's Tree Theorems         Notation       . | <ul> <li>243</li> <li>244</li> <li>247</li> <li>247</li> </ul> |

| _ | D.1<br>D.2<br><b>Pro</b><br>E.1<br>E.2<br>E.3               | Node Tearing                                                                                                   | 243<br>244<br><b>247</b><br>247<br>247                         |

| E | D.1<br>D.2<br><b>Pro</b><br>E.1<br>E.2<br>E.3<br><b>Red</b> | Node Tearing                                                                                                   | 243<br>244<br><b>247</b><br>247<br>247<br>248                  |

# List of Figures

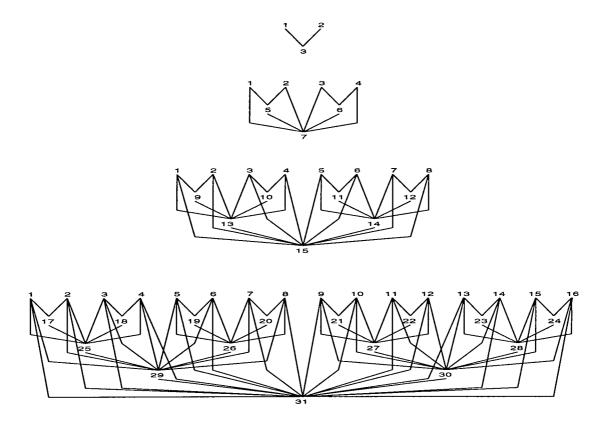

| 1.1  | The components of a modern power system                                      | 2  |

|------|------------------------------------------------------------------------------|----|

| 1.2  | A model of a synchronous generator connected to the transmission network     | 6  |

| 1.3  | The basic von Neumann machine                                                | 15 |

| 1.4  | Instruction and data streams in the von Neumann machine $\ldots$             | 16 |

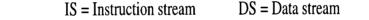

| 1.5  | Functional design of a MIMD computer                                         | 18 |

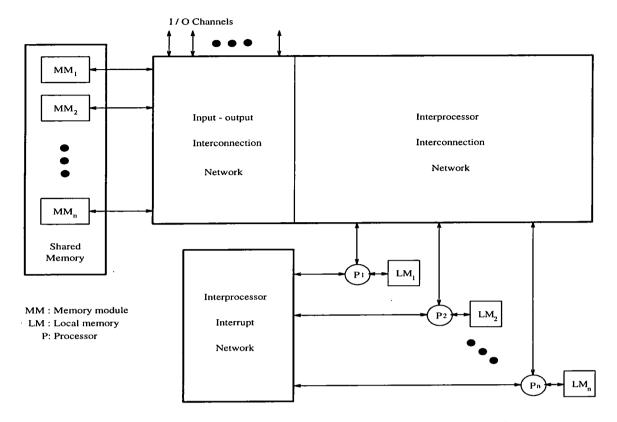

| 1.6  | Static interconnection network topologies                                    | 21 |

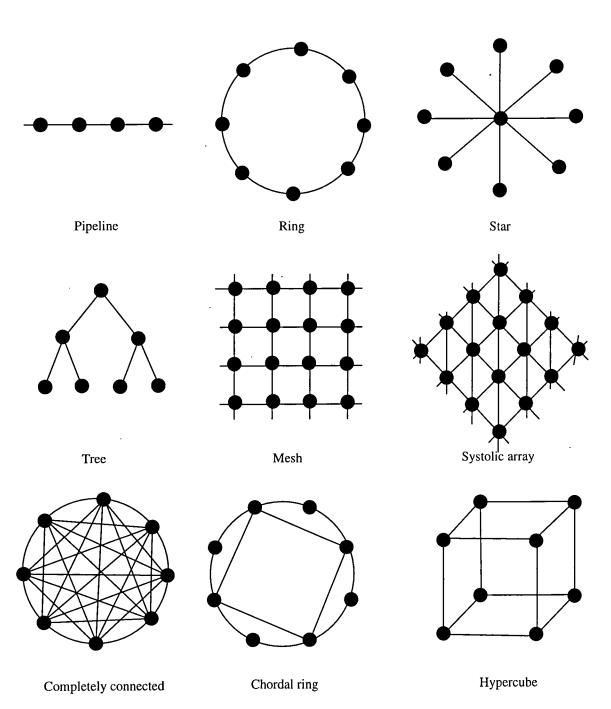

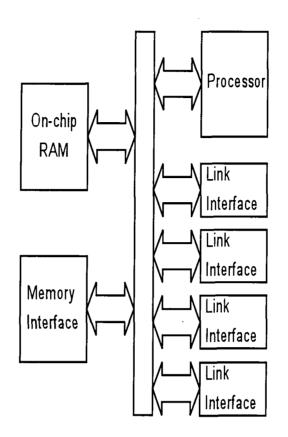

| 1.7  | Conceptual overview of the configuration of the Transputer based parallel    |    |

|      | machine                                                                      | 23 |

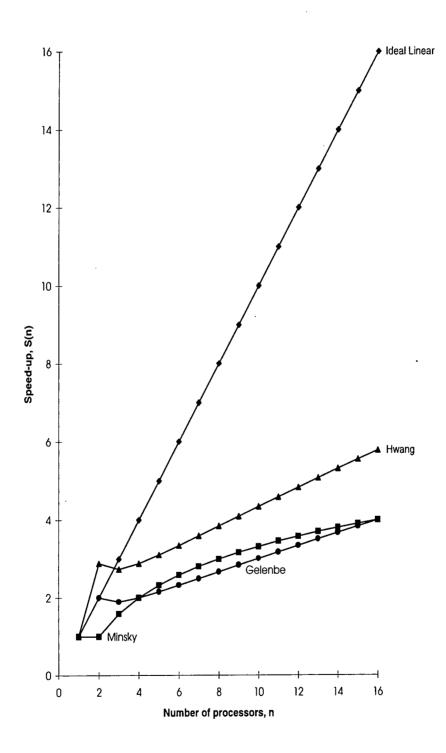

| 1.8  | Various bounds on parallel performance                                       | 25 |

| 1.9  | Speed-up predicted by Amdahl's Law                                           | 27 |

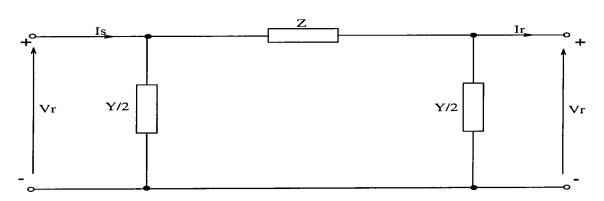

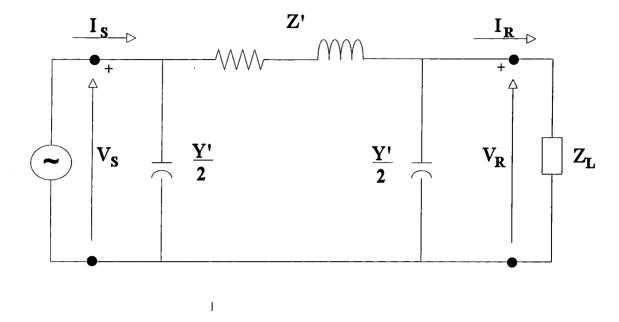

| 2.1  | Transmission line equivalent $\pi$ circuit model                             | 35 |

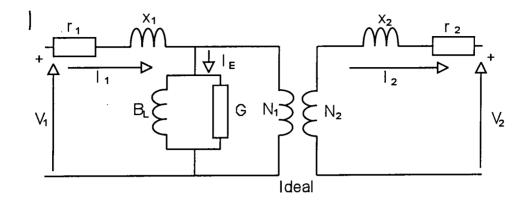

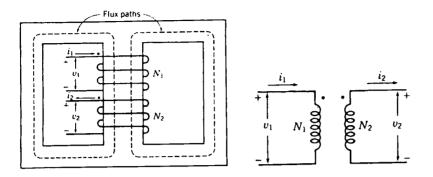

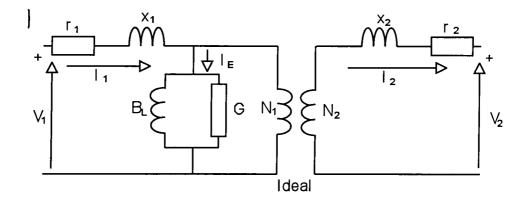

| 2.1  | Equivalent circuit of a practical single phase transformer                   | 36 |

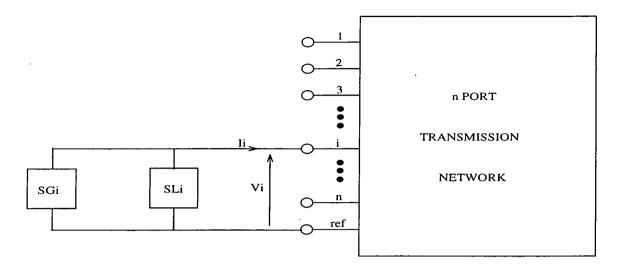

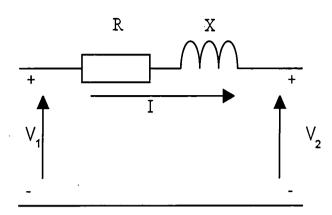

|      |                                                                              | 37 |

| 2.3  | General <i>n</i> -port representation of a power system                      |    |

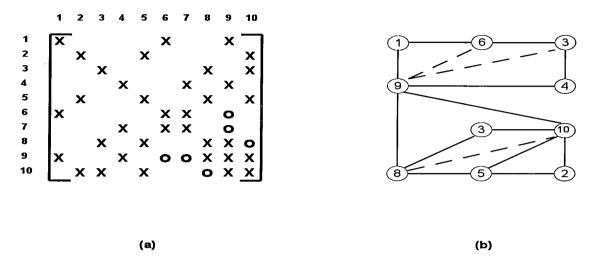

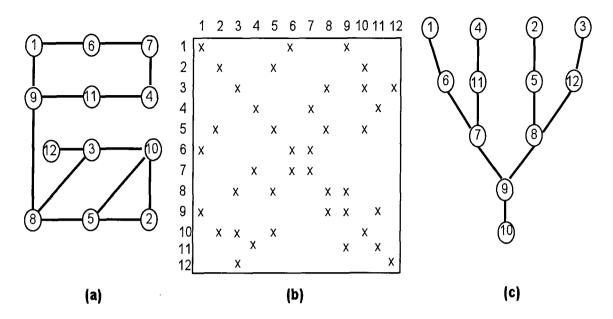

| 2.4  | A simple 10 node graph and its associated matrix                             | 53 |

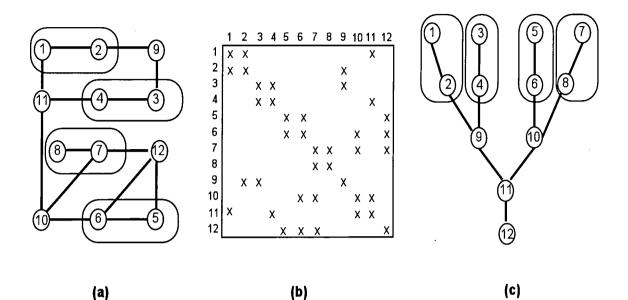

| 2.5  | Filled graph and associated matrix for the simple 10 node example $\ldots$ . | 54 |

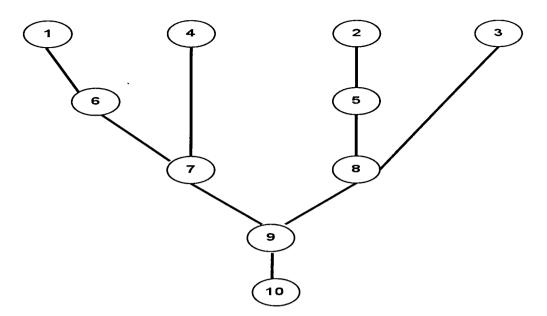

| 2.6  | The elimination tree of the 10 node example                                  | 55 |

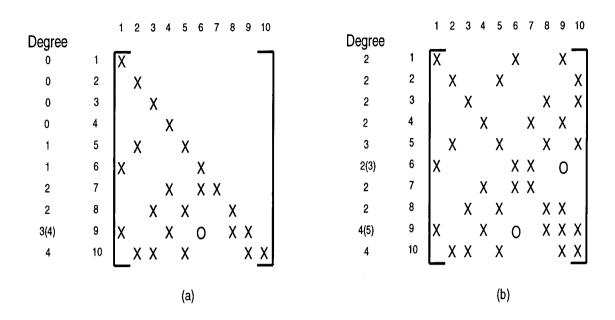

| 2.7  | The effect of storage scheme on nodal degree                                 | 56 |

| 2.8  | Storage Of Sparse Matrix Rows In Linked Lists                                | 63 |

| 2.9  | Storage Of Extra Information About The Matrix                                | 63 |

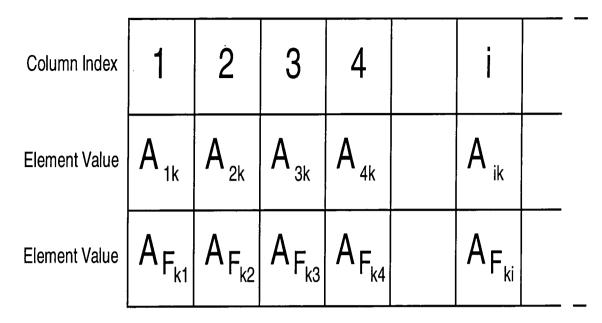

| 2.10 | The information array used for updating                                      | 64 |

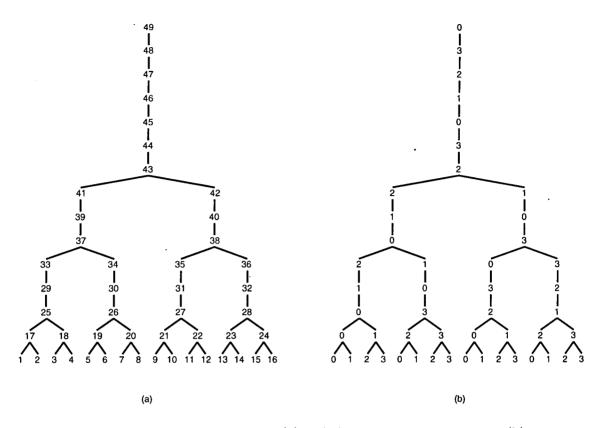

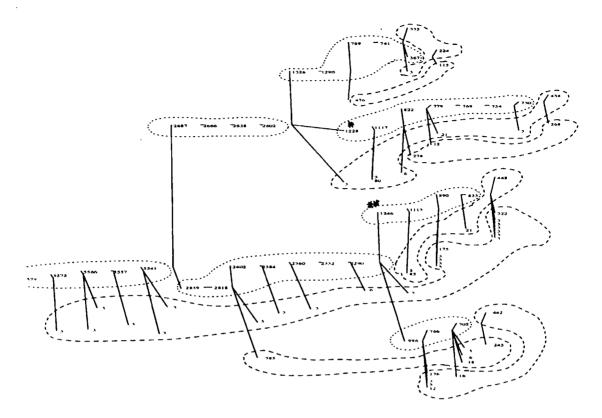

| 3.1  | An elimination tree and the wrap mapping strategy                            | 80 |

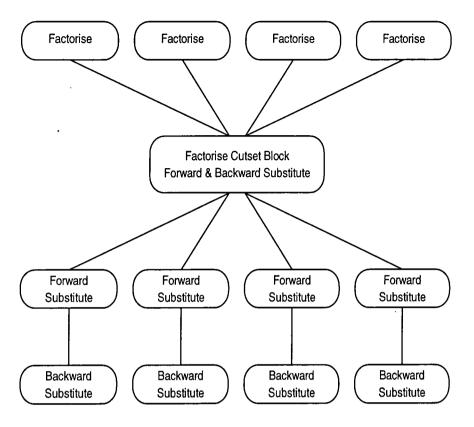

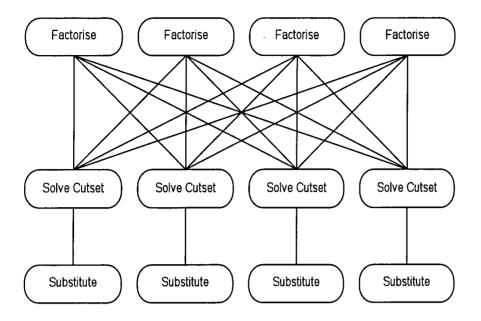

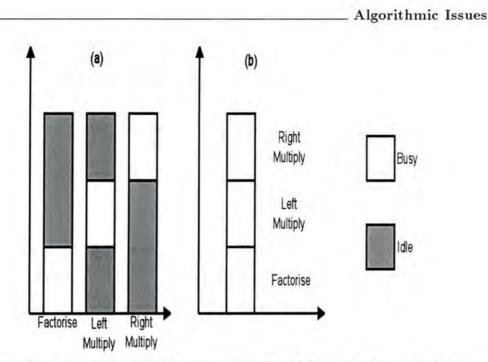

| 3.2  | Structure of conventional parallel solution algorithm                        | 89 |

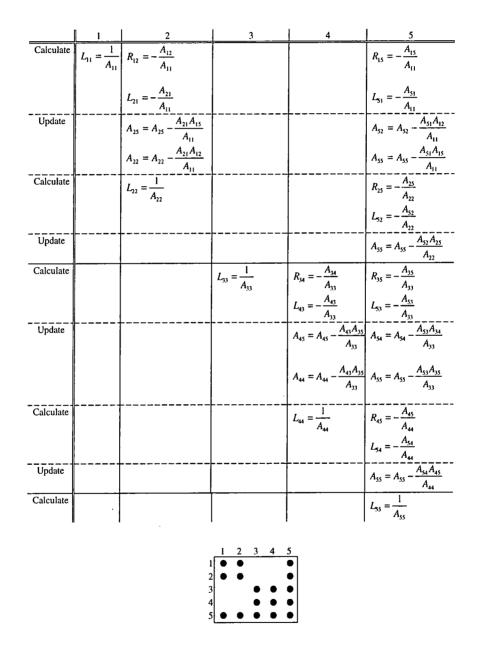

| 3.3  | Simple BBDF factorisation example, showing independence between operations   | 90 |

| 3.4  | Algorithm structure of Chan's method, using duplicate cutset computation     | 93 |

|      |                                                                              |    |

.

•

.

### FIGURES

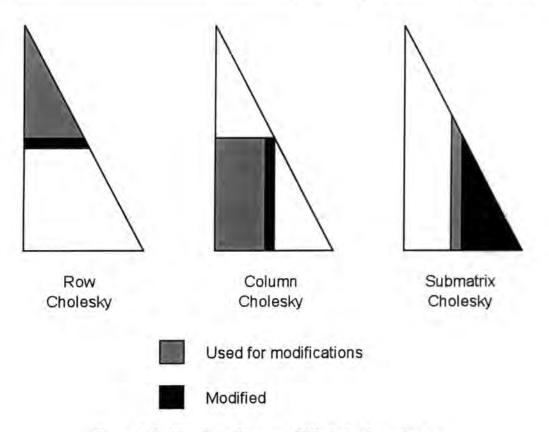

| 3.5  | The three flavours of Cholesky factorisation                                                   | 97   |

|------|------------------------------------------------------------------------------------------------|------|

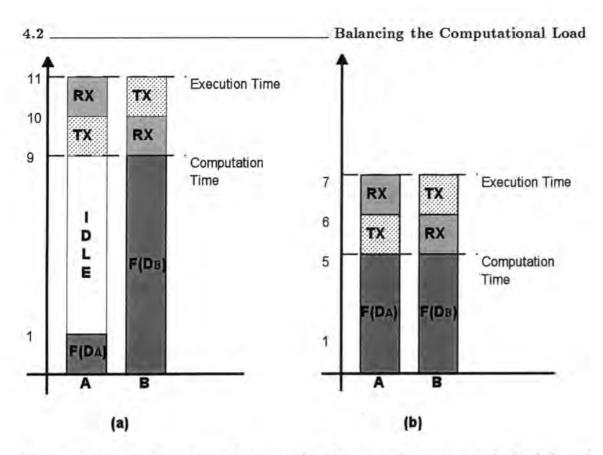

| 4.1  | Simple load balancing example                                                                  | 103  |

| 4.2  | Graphical depiction of the execution of the example program                                    | 104  |

| 4.3  | Three task implementation of the LU-based solution                                             | 106  |

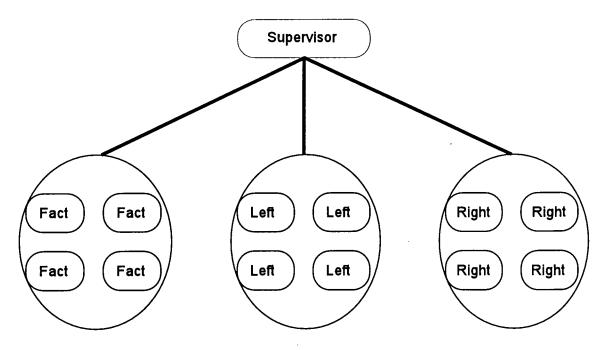

| 4.4  | A supervisor/worker approach to parallel bifactorisation $\ldots \ldots \ldots \ldots$         | 107  |

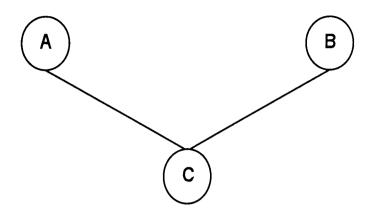

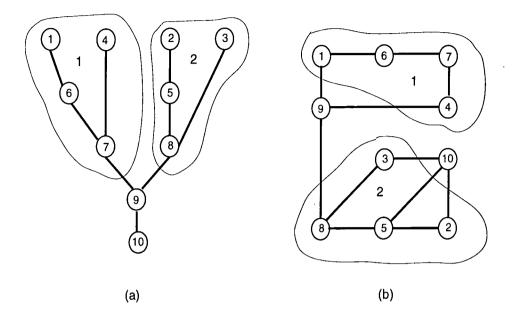

| 4.5  | $Partitioning \ of \ the \ elimination \ tree \ and \ corresponding \ network \ partitions  .$ | 111  |

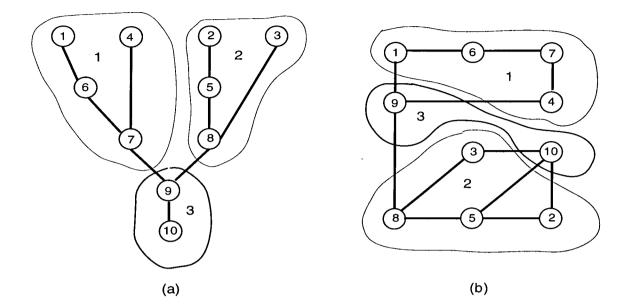

| 4.6  | Treating the lower portion of the tree as a separate subnetwork $\ldots$ .                     | 116  |

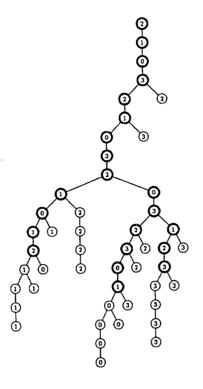

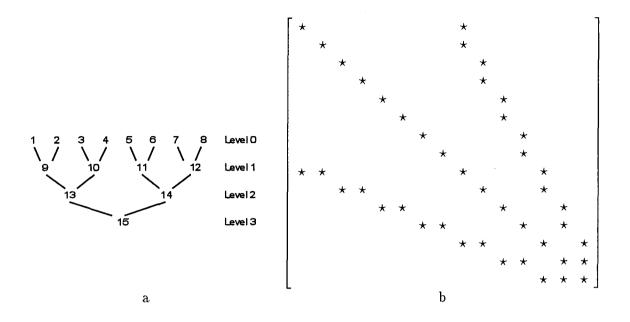

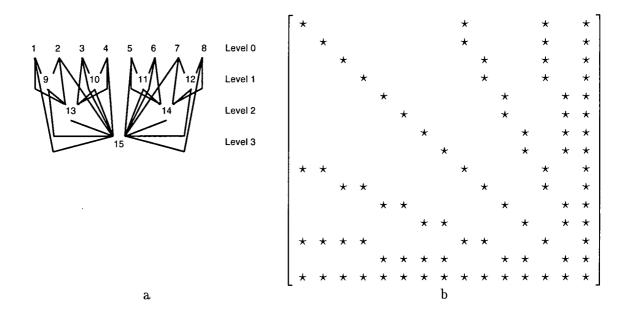

| 4.7  | Geist & Ng's partitioning method applied to a simple tree $\ldots$                             | 117  |

| 5.1  | The simple 12 node example system                                                              | 122  |

| 5.2  | Partitioned topologically reordered network                                                    | 123  |

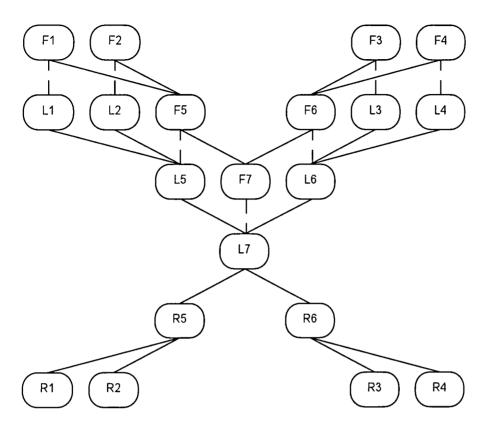

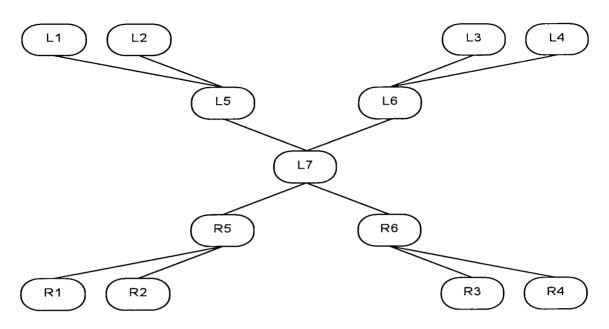

| 5.3  | Subnetworks constrained to a binary tree connection structure $\ldots$ .                       | 126  |

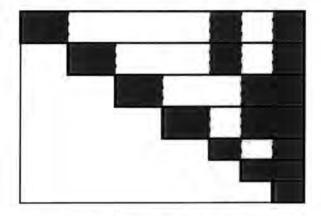

| 5.4  | The interconnections giving rise to RBBDF                                                      | 128  |

| 5.5  | The constrained subnetwork interconnections $\ldots \ldots \ldots \ldots \ldots \ldots$        | 129  |

| 5.6  | Partitioning of the reduced CEGB 734 node system for solution on 8 processor                   | s131 |

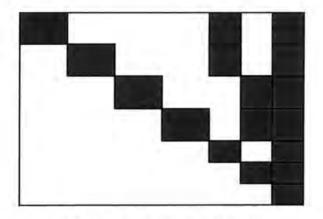

| 5.7  | The block oriented data structure                                                              | 133  |

| 5.8  | The row oriented data structure                                                                | 134  |

| 5.9  | Algorithm structure for the Recursively Parallel method $\ldots \ldots \ldots \ldots$          | 135  |

| 5.10 | Algorithm structure for repeated substitution with multiple right hand sides                   | 137  |

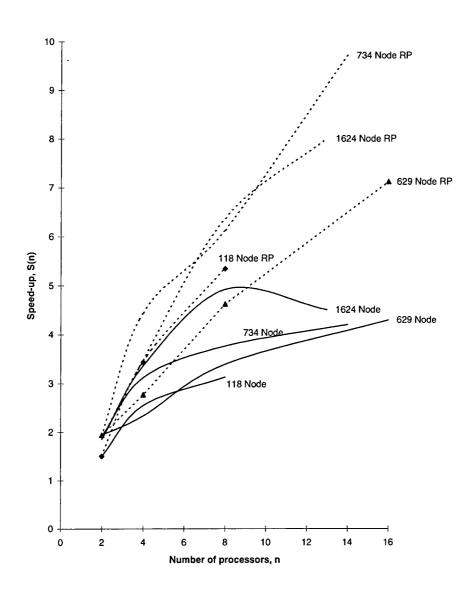

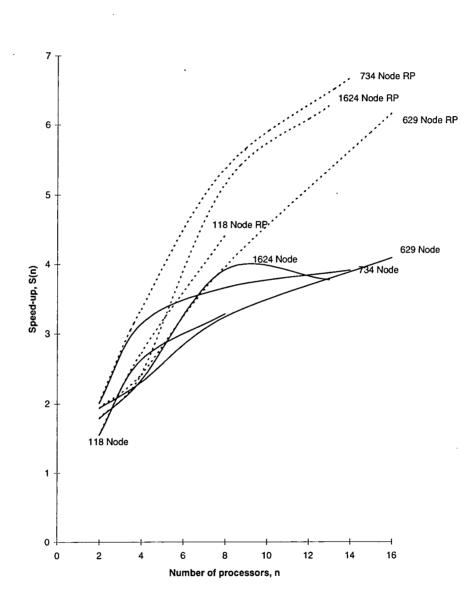

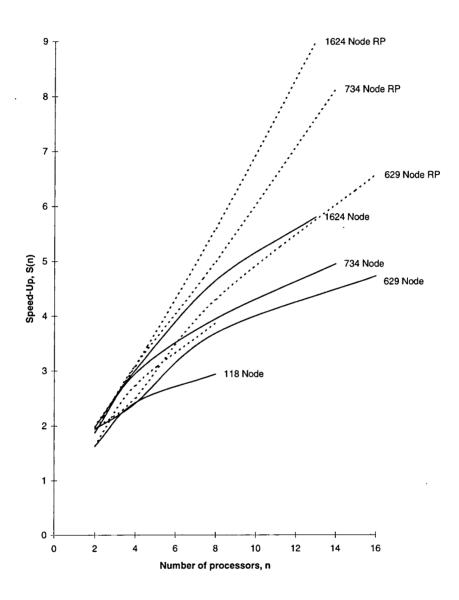

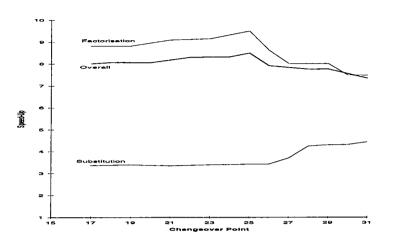

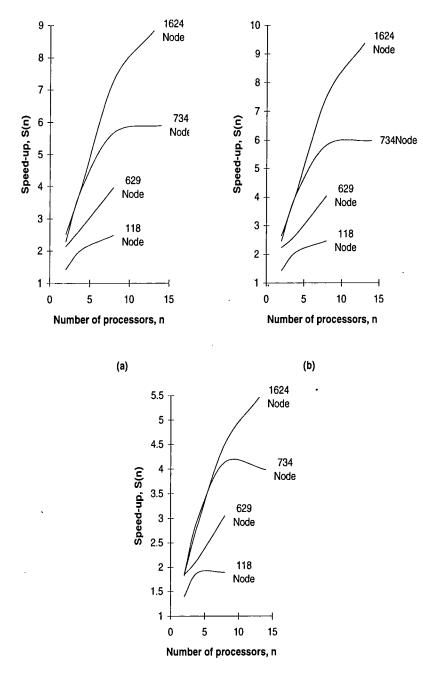

| 5.11 | Overall speed-up results of simulated solution of the four test systems $\ldots$               | 138  |

| 5.12 | Factorisation speed-up results of simulated solution of the four test systems                  | 139  |

| 5.13 | Substitution speed-up results of simulated solution of the four test systems                   | 140  |

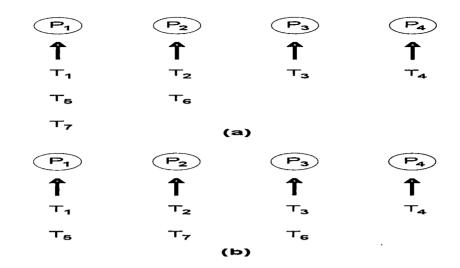

| 6.1  | Task structures with different granularity                                                     | 147  |

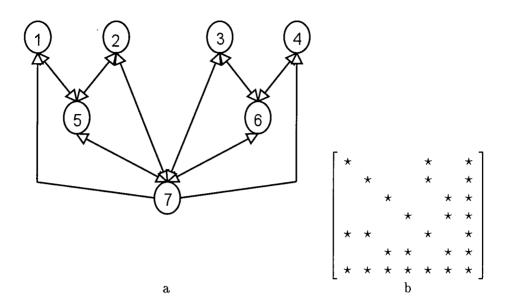

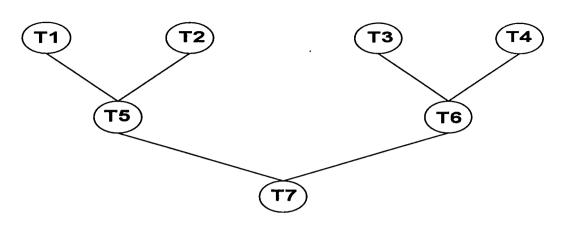

| 6.2  | Intertask communications in a 7 subnetwork solution                                            | 148  |

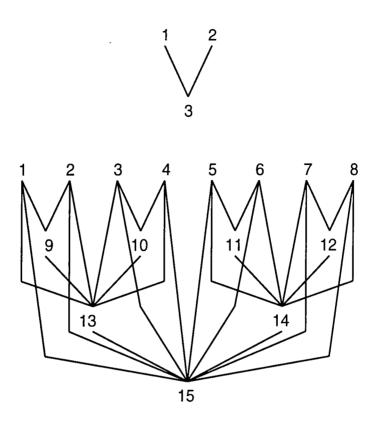

| 6.3  | Intertask communications in 3 and 15 subnetwork solutions                                      | 149  |

| 6.4  | The generic task of the Recursively Parallel solution                                          | 150  |

| 6.5  | RBBDF matrix structure showing 'r' segments                                                    | 151  |

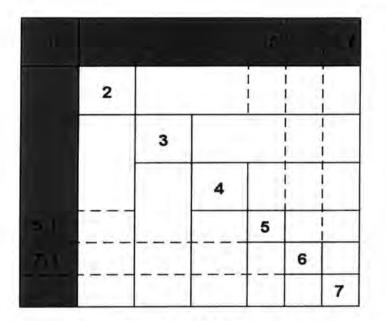

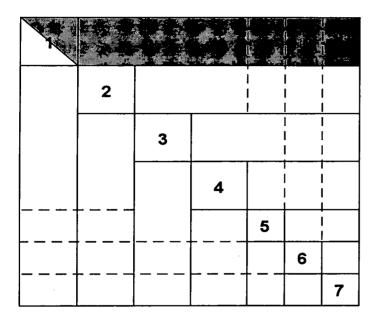

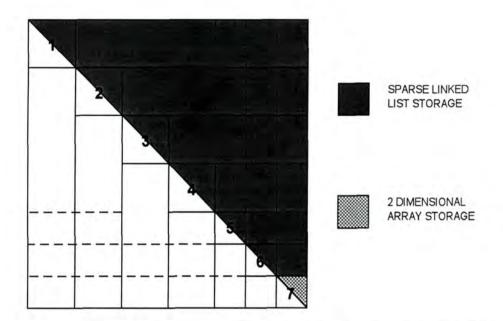

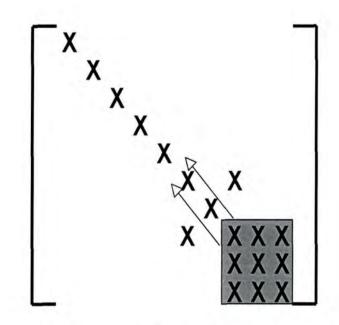

| 6.6  | Portion of the coefficient matrix stored by a single task                                      | 152  |

| 6.7  | Storage techniques used by the Recursively Parallel method                                     | 153  |

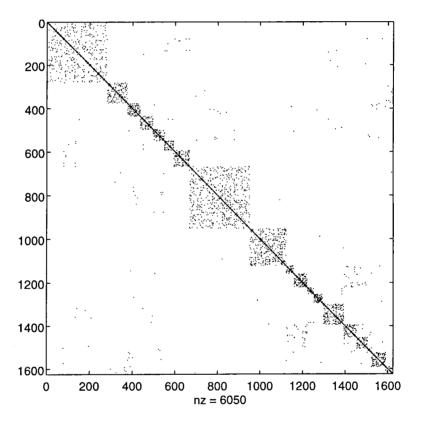

| 6.8  | Assessing the density of the coefficient matrix                                                | 153  |

| 6.9  | Variation of speed-up with location of changeover point in hybrid storage,                     |      |

|      | for US 1624 node system                                                                        | 155  |

### FIGURES

•

.

| 6.10 | Modified intertask communications for a 7 subnetwork system 15                          |     |

|------|-----------------------------------------------------------------------------------------|-----|

| 6.11 | A many to one task allocation strategy                                                  | 162 |

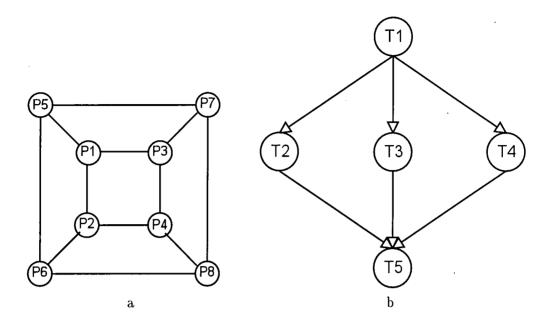

| 6.12 | The acyclic graphs used in determining task allocations $\ldots \ldots \ldots$          | 163 |

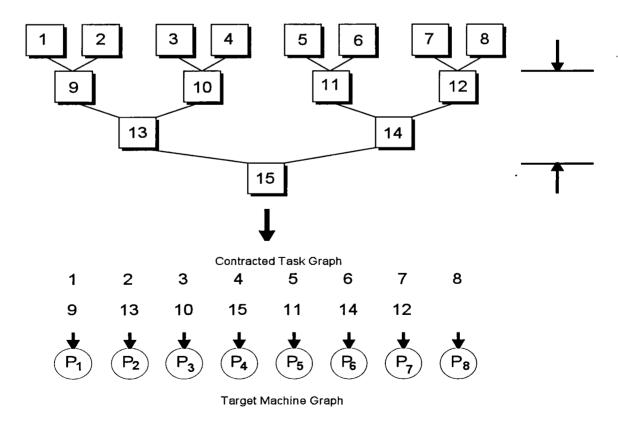

| 6.13 | Contraction mapping for Recursively Parallel task allocation $\ldots \ldots \ldots$     | 163 |

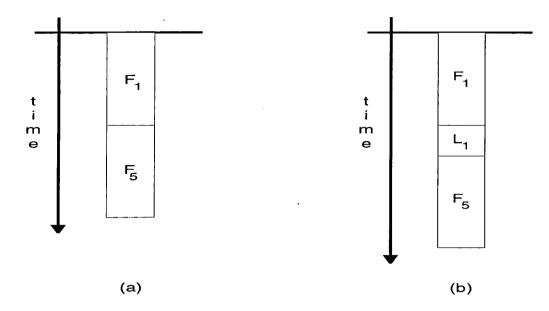

| 6.14 | Task execution, showing the effect of multitasking $\ldots \ldots \ldots \ldots \ldots$ | 164 |

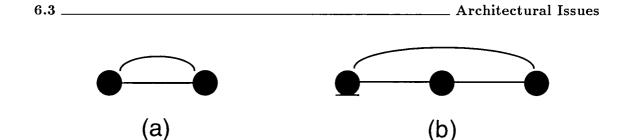

| 6.15 | Direct and indirect communication                                                       | 167 |

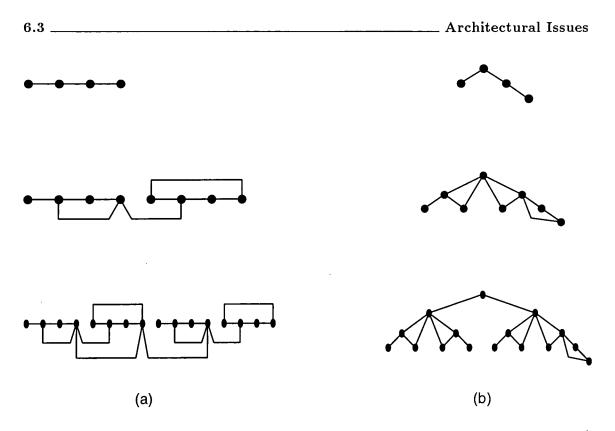

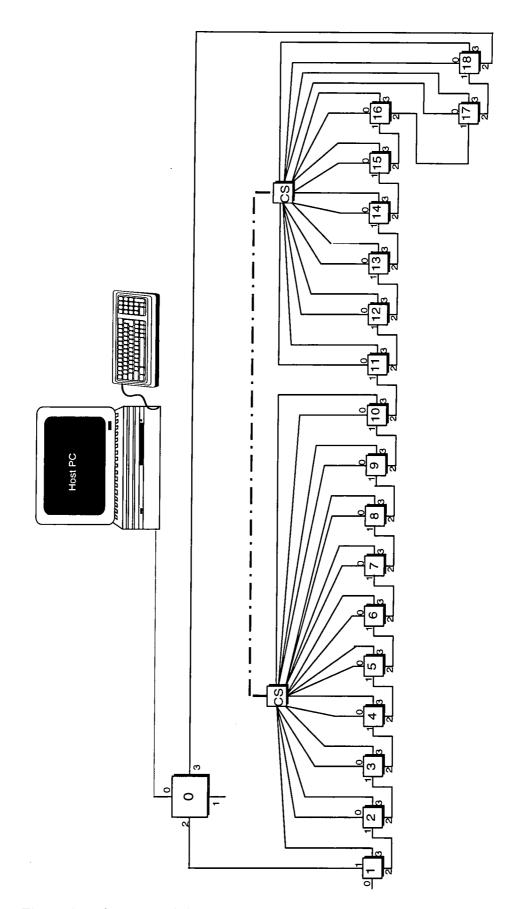

| 6.16 | The Mutated Tree interconnection network                                                | 170 |

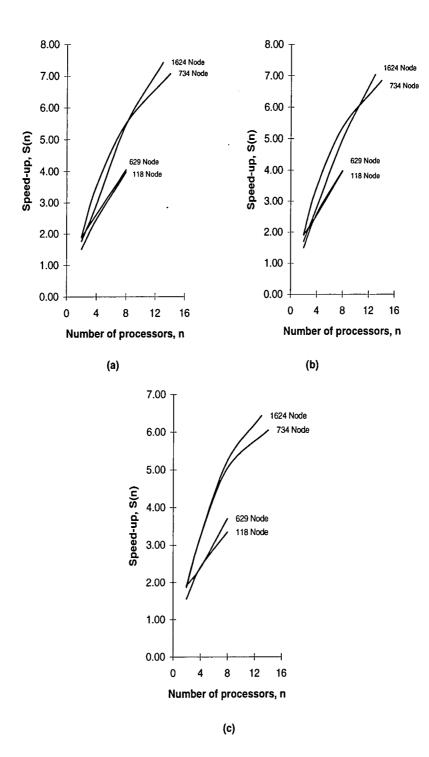

| 6.17 | Performance curves for the Recursively Parallel method, with 2-1 task allo-             | -   |

|      | cation                                                                                  | 175 |

| 6.18 | Speed-up against uniprocessor for the Recursively Parallel method, with 2-1             |     |

|      | task allocation                                                                         | 179 |

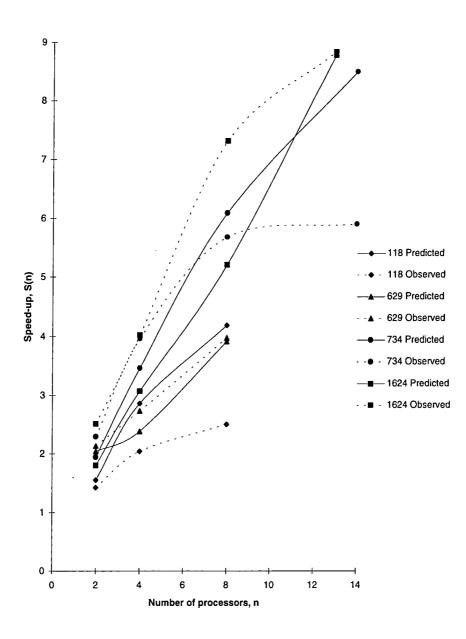

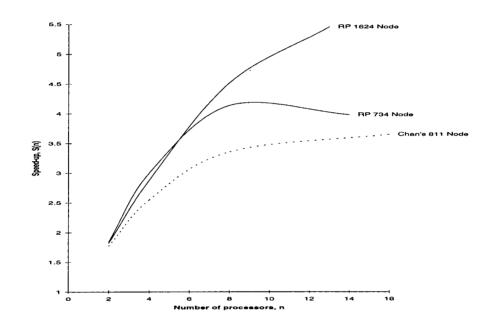

| 6.19 | RP method compared to predicted performance                                             | 180 |

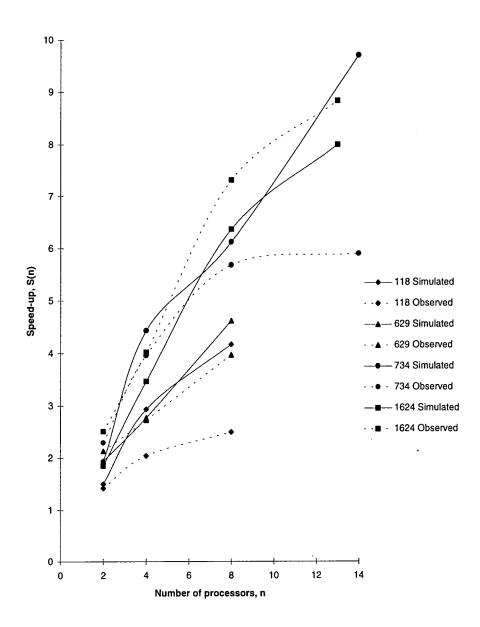

| 6.20 | RP method compared to simulated performance                                             | 181 |

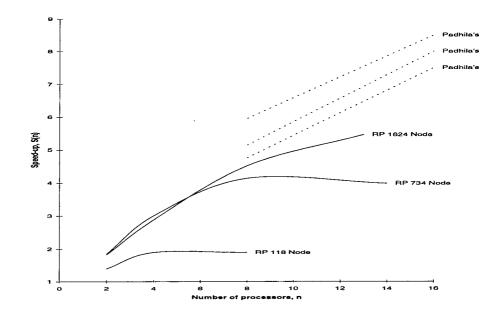

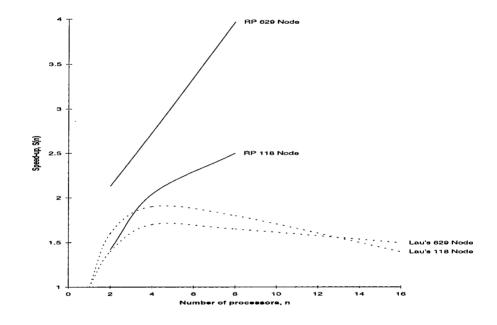

| 6.21 | RP method compared to Padhila's W-matrix method                                         | 184 |

| 6.22 | RP method compared to Lau's method                                                      | 186 |

| 6.23 | RP method compared to Chan's method                                                     | 187 |

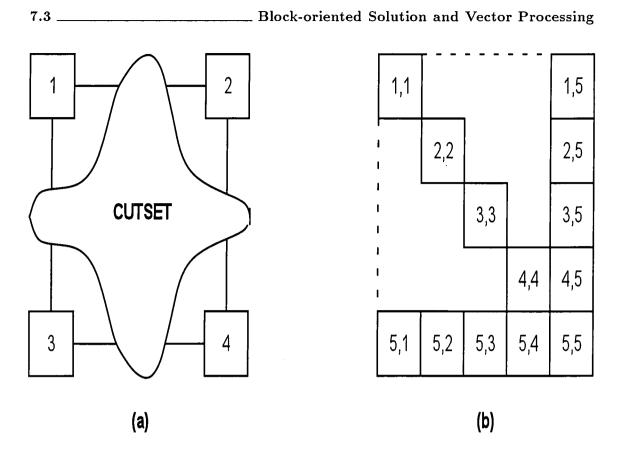

| 7.1  | Conceptual view of a simple four subnetwork system and its BBDF matrix                  | 196 |

.

•

# List of Tables

| 1.1 | Flynn's Taxonomy.                                                             | 15  |

|-----|-------------------------------------------------------------------------------|-----|

| 2.1 | Statistical performance of the ordering algorithms                            | 60  |

| 2.2 | The effect of elimination ordering on speed-up                                | 61  |

| 3.1 | Operation counts for direct and iterative solution schemes $\ldots$           | 76  |

| 4.1 | Speed-ups for the load balancing example                                      | 105 |

| 4.2 | Effect of load balancing on speed-up for an LU-based solution                 | 106 |

| 4.3 | The effect of load balancing on speed-up                                      | 119 |

| 5.1 | Results of the simulated solution of the four test systems                    | 141 |

| 5.2 | Simulated RP solution vs best sequential solution                             | 143 |

| 6.1 | The effect of storage scheme on speed-up                                      | 154 |

| 6.2 | Effect of load imbalance on performance                                       | 165 |

| 6.3 | Comparison of performance using pipeline and hypercube architectures          | 171 |

| 6.4 | Characteristics of the test systems                                           | 172 |

| 6.5 | Performance of the best sequential algorithm                                  | 173 |

| 6.6 | Performance of the Recursively Parallel solution of the test systems          | 174 |

| 6.7 | Performance of the Recursively Parallel solution of the test systems, using   |     |

|     | 1-1 task allocation                                                           | 176 |

| 6.8 | Performance of the Recursively Parallel solution of the test systems - speed- |     |

|     | up over uniprocessor                                                          | 178 |

| 6.9 | Simulated, predicted and observed factorisation speed-ups for the RP solu-    |     |

|     | tion of the test systems                                                      | 178 |

### Chapter 1

### Introduction

odern electrical power systems represent some of the largest non-linear systems in existence. Today's power systems are complex interconnected networks consisting of many thousands of nodes and the analysis of these systems and planning their expansion and performance is no simple task. The modern power engineer is forced to rely upon powerful software tools to enable him to get the best out of the system. As systems continue to grow more complex and engineers wish to gain deeper insight into their workings there is a continually growing demand for faster and more powerful software analysis tools. Many such tools have been developed over the past four decades but there is always more that can be done. This thesis focuses on the solution of one of the problems which currently limits the performance of many power system analysis applications. Solving this problem surmounts an important obstacle in the creation of more efficient analysis tools.

#### The Components of a Power System 1.1

Gross [1] defines an electrical power system as

"a network of interconnected components designed to convert non-electrical energy continuously into the electrical form; transport the energy over potentially large distances; transform the electrical energy into a specific form subject to close tolerances; and convert the electrical energy into a usable non-electrical form."

This definition shows that the power system consists of three basic components

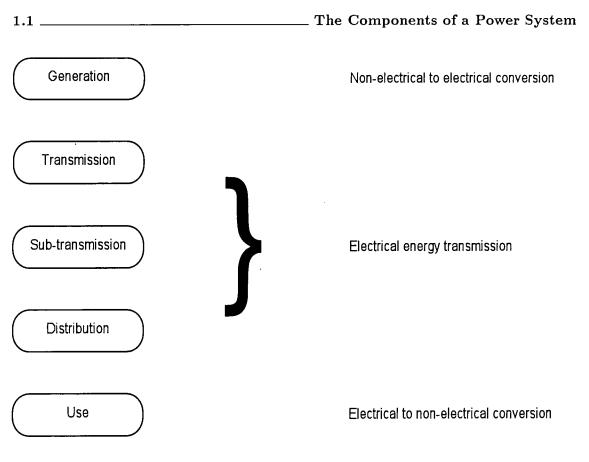

Figure 1.1: The components of a modern power system

- Non-electrical to electrical energy conversion

- Electrical energy transmission

- Electrical to non-electrical energy conversion

In fact this can be subdivided further and the modern power system thus has the five facets shown in Figure 1.1

The generation process turns non-electrical kinetic energy of a rotating shaft into electrical energy. Kinetic energy is imparted to the shaft by some form of turbine. Steam, gas and hydro turbines are the most common prime movers, although wind turbines are making an increasing contribution to electricity generation. The generator itself makes use of the principle of electromagnetic induction to generate three sinusoidal alternating voltages which differ in phase by 120°. This is the most efficient form for electrical energy transmission as it makes best use of the transmission cables and give constant power in balanced loads. The aim of generation is simply to pump enough electrical energy into the system to satisfy the demand of the end users and to account for the losses which occur in transmission.

Strictly speaking the transmission network takes power from substations at the generating sites and delivers it to substations in the load centres. The generation sites are often remote from areas of load for many reasons. Originally generators were located where there is a ready supply of fuel e.q near coal fields, but such areas are seldom areas of electricity demand. As it is cheaper and easier to transport the electrical energy to areas of demand, power stations have tended to be sited near the fuel supplies. In some cases this is essential as the 'fuel' cannot be moved e.q. hydropower and wind power. Government policy in the UK has also affected the location of power generation plant with current legislation dictating that all fossil fuel burning power plant have to be sited outside urban areas. Consequently there is a need for transmitting electrical energy from generators to loads in the most efficient way possible. The UK national grid is a typical transmission system consisting of transmission lines with a total length exceeding 7,500 kilometres. This network of lines provides a high degree of interconnectivity between the sites of generation and the major load centres. It also ties the UK system into other continental systems to increase the reliability of the system and the availability of power. The transmission system has to be able to deliver large amounts of power to the loads and to ensure reliability it has to be able to deliver this power by a number of alternative routes. The process of transmitting electrical energy is not 100% efficient and the losses are proportional to the square of the current, making it more efficient to transmit power at high voltage and low current. The UK grid developed in three distinct phases and it now operates at three different voltage levels of 132 kV, 275 kV and 400 kV. Transmission voltage levels vary throughout the world but they all lie in the range 100 kV to 1MV.

The distinction between subtransmission and distribution is not altogether clear but is dependent upon voltage levels and geographical extent. Subtransmission systems take electrical power from the point of arrival in the load area and deliver it to a number of distribution substations throughout this area. Subtransmission operates at much lower voltages than transmission, with 11kV and 33kV being the typical voltages used in the UK. As well as the lower voltages, subtransmission systems also have a much smaller geographical extent. Transmission systems extend to cover countries and whole continents whereas subtransmission systems are usually limited to the extent of a given urban area.

The distribution network is the final link in the chain between the generator and the user. Distribution is distinguished from subtransmission by its lower voltage levels with 12kV down to 2.4kV being common. The distribution system takes power from the distribution substation and forwards it to individual users who are located within a short distance (2km) of the substation.

The purpose of transmitting electrical power through the various stages of the network is to supply the end user with electrical energy. Upon receipt of this energy the user converts it back into some more usable non-electrical form using any one of the electrical appliances available to him. To ensure that his appliances work correctly the user expects his electricity supply to have constant voltage magnitude, constant voltage frequency and an ideal sinusoidal waveform. To meet these criteria the power companies specify three performance measures to which they must adhere

- Voltage regulation the deviation of voltage magnitude as load varies. Typically this is around 5%.

- Frequency regulation the deviation of system frequency from the nominal value. For a 50Hz system this is typically  $\pm 0.1$ Hz.

- Harmonic content The ideal supply has only a single sinusoidal component.

There is a complex control system at the heart of every power system which allows the system operators to control these three parameters so that the user's demands on the quality of his electricity are satisfied. Controlling such a large and complicated system is no simple problem and to do so efficiently requires a detailed understanding of the system and how its constituent parts interact with one another.

### 1.2 Power System Analysis

Modern power systems are extremely large and complex entities. Planning, maintaining and operating such a system would be difficult if it were not for the wide range of analytical methods available to help the power engineer. Today there is a wealth of software analysis tools to help in understanding any conceivable aspect of the power system. Prior to 1940 there were very few interconnected systems of any complexity and analysis methods existed only for dealing with generators, transformers and transmission lines. With the advent of interconnected systems came the development of techniques which enable the engineer to determine the electrical state of the network and how it would respond to given disturbances (*i.e.* load flow, stability analysis). Further work has led to the development of power flow programs, contingency analysis tools and economic analysis packages. Requirements for

low operating and construction costs and the ever increasing complexity of systems have led to a constant demand for powerful new automated analysis methods. Software tools are available to aid analysis in the areas of operations planning, systems planning, contingency and security analysis, reliability and economics. Several of these areas are worth considering in more detail but first the power flow problem must be examined.

### 1.2.1 The Power Flow Problem

The applications outlined in the previous section are all limited in their performance by the time taken to solve the *power flow* equations for the system under consideration. At the heart of the power flow solution lies a large sparse set of linear network equations. It is the solution of these equations which is so time consuming and over the last 35 years much research effort has been expended on improving and accelerating this solution. The set of algebraic equations is of the form

$$\mathbf{A}\mathbf{x} = \mathbf{b} \tag{1.1}$$

where  $\mathbf{A}$  is the matrix of coefficients of the set of equations.  $\mathbf{b}$  is a vector of known values whilst the elements of vector  $\mathbf{x}$  are the unknowns in the equations. One of the earliest and most successful improvements came through the application of sparse matrix techniques. The matrix,  $\mathbf{A}$ , has few non-zero elements and many zero elements; often more than 95% of the matrix elements are zero. It is wasteful both of memory and solution time to store the zero elements of this sparsely populated matrix. Sparse matrix techniques are used to store and process only the non-zero coefficients and this gives a significant increase in the speed of solution [2, 3].

### 1.2.2 Power System Simulation

Like many other simulations, power system simulation involves an iterative process of solving the equations which model the system. On each iteration the simulation time is incremented and the system equations must be solved again for this new time step. If the time for one iteration is less than the time constant of the fast dynamics of the system then the simulation can be considered real-time. The integration time step of a typical power system simulation is of the order of one second. This is sufficient to allow all but the very fast (sub-transient) dynamics to be modeled. If the simulation is to operate in real-time it is necessary to solve all the mathematical equations which model the system more than once a second if real-time

0

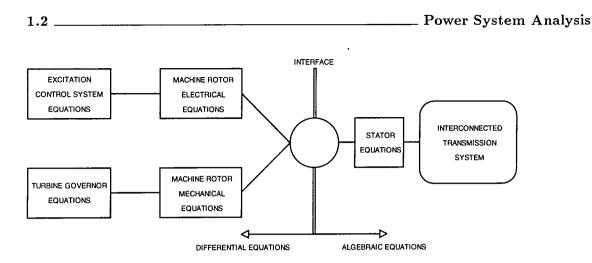

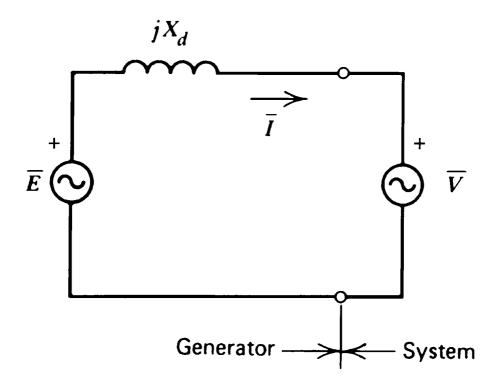

Figure 1.2: A model of a synchronous generator connected to the transmission network

simulation is to be achieved.

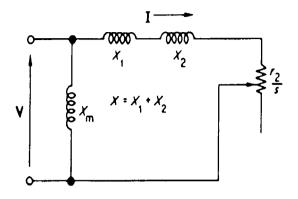

A power system simulation consists of two distinct sets of equations relating to the different parts of the system. Firstly there is the network model which describes the transmission network of the system and the stators of all the machines connected to the system. The network model consists entirely of algebraic equations. Secondly there is a set of non-linear machine models which may be broken down into first order non-linear differential equations that describe all the generators and loads connected to the network. On each iteration the differential equations must be solved to determine the currents which are injected into the transmission network. The linear equations must then be solved to determine the power flows around the system and the voltage at each system bus. Figure 1.2 depicts a single machine connected to the transmission network and it shows how the model is divided into a set of differential equations and a set of algebraic equations.

The differential equations are of the form

$$\dot{y} = f(y, x) \tag{1.2}$$

and this set of equations contains the differential equations of every machine connected to the network. Each machine in the system is only coupled to other machines through the transmission network and, as the network is treated separately, the differential equations are a collection of uncoupled sets of equations, one set for each machine. The equations may be represented as [4]

$$\dot{y} = f(y, u) = \mathbf{A}y + \mathbf{B}u \tag{1.3}$$

where A is a sparse, square, block diagonal matrix and B is a rectangular sparse matrix

with a block structure. When the effects of saturation are neglected A and B become constant in most models. Chapter 2 and Appendix B discuss the mathematical models of machines in detail.

The algebraic equations are of the form

$$\mathbf{y} = g(\mathbf{x}, \mathbf{u}) \tag{1.4}$$

where **u** is the vector of stator voltages and is the input to the equations whilst **y** is a vector of currents. The equations may be separated into two parts

$$I(\mathbf{E}, \mathbf{V}) = \mathbf{Y}\mathbf{V} \tag{1.5}$$

and

$$u = u(\mathbf{E}, \mathbf{V}) \tag{1.6}$$

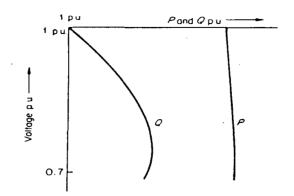

where  $\mathbf{Y}$  is the bus admittance matrix,  $\mathbf{V}$  is the vector of terminal voltages at load busses and  $\mathbf{E}$  is the vector of stator voltages at generation busses. I is the vector of bus injection currents. Injection current at a generator bus is a function of stator voltage whilst the injection current at a load bus is a function of the terminal voltage. It is important to note that coefficients of  $\mathbf{Y}$  depend on the topology of the network and these coefficients may vary. If the topology of the transmission network changes due to equipment outages then the values in the matrix  $\mathbf{Y}$  are changed. When auto-tap changing transformers are represented  $\mathbf{Y}$  can change frequently.

For power system simulation the problem is to solve the differential and algebraic equations simultaneously. The conventional approach is to solve (1.3) separately by integration to yield values for y. Equation (1.5) is then solved and the solutions are alternated in some manner. Another approach is to solve (1.3) and (1.5) simultaneously using the implicit trapezoidal rule. The solution of (1.5) is the bottleneck in the solution process and three methods of solution exist.

Gauss-Seidel - This method is simple to program and easily accommodates changes in Y as the method operates directly on admittance matrix values [4]. The method is iterative and convergence to acceptable accuracy varies from problem to problem. Simple problems may converge in 2 or 3 iterations whereas difficult problems may require hundreds of iterations 2. Factorisation of Y - Triangular factorisation of Y is a direct method for solving the algebraic equations. LU decomposition is used to yield the factored form of Y and

$$\mathbf{I} = \mathbf{L}.\mathbf{U}.\mathbf{V} \tag{1.7}$$

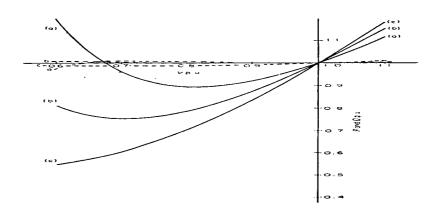

where L is a lower triangular matrix and U is an upper triangular matrix. Forward and backward substitution with I is used to provide a solution for V. If Y does not change then L and U remain constant and V may be obtained by repeat solution of (1.7). Any change in Y requires a complete refactorisation to yield new values of L and U, before (1.7) can be solved for V. It is observed that factorisation takes up to six times as long as forward/backward substitution [4] but substitution only takes about 1.5 times as long as a single iteration of the Gauss-Seidel method and it is difficult for Gauss-Seidel to be competitive.

3. Newton's Method - Newton's Method is also an iterative method for solving systems of non-linear equations. Equation (1.5) becomes non-linear when non-impedance loads are connected to the network. Under these conditions the relationship between node voltage and bus current is non-linear and is defined by the impedance characteristics of the load. Newton's method linearises the equations using a truncated Taylor series approximation and forms the Jacobian matrix J [1]. Equation (1.5) can be rewritten as

$$F = \mathbf{I} - \mathbf{Y} \cdot \mathbf{V} \tag{1.8}$$

and F = 0 when the correct solution of V is obtained. The solution is obtained by iterative correction and each iteration requires the solution of the Jacobian matrix equation

$$F = -\mathbf{J}.\Delta\mathbf{V} \tag{1.9}$$

LU factorisation and triangular substitution may be used to give a direct solution to this equation on each iteration. A strict implementation of Newton's method requires J to be updated and factorised for each iteration but this is computationally intensive. Faster solutions are achieved by allowing the triangular factors of J to be used for several consecutive iterations.

The choice of the models used in the simulation has implications for the method chosen to solve the network equations. If there is no saliency, saturation or non-impedance loads in the model then the injection currents, I, are a function of stator voltage, E, only. An exact solution for the node voltages, V, can rapidly be obtained using (1.7). Introducing machine saliency leads to a constant term being introduced into the admittance matrix Y. To compensate for this a corrective term is added to V and this term is a function of I. It is necessary to iterate repeat solutions of (1.7) until V achieves convergence. The representation of non-impedance loads similarly leads to a portion of each load being represented by a shunt admittance in Y. The remainder of the load appears as a non-linear function of I in V. Again it is necessary to iterate repeat solutions of (1.7) until V achieves convergence.

### 1.2.3 Power System Security

In power system engineering terms security is defined as the

'ability of the system to withstand any one of a predefined list of possible contingencies without serious consequences'

where a contingency is an interruption in the normal functioning of the network caused by objects in the environment. The objective of power system operators is to maintain system voltages and power flows within defined limits regardless of changes in generation and load. Operating interconnected systems requires strict control over synchronisation; any loss of synchronisation may be catastrophic. Equipment outages themselves seldom cause much damage but the readjustment of voltages and power flows throughout the system may lead to a dangerous cascade of overloads causing large sections of the system to be switched out or damaged. In the past system security has been assured through the construction of robust systems. Rising costs and environmental concerns have meant that it is no longer economically or environmentally feasible to build extremely robust systems. As a result systems are being operated closer to their limits with smaller safety margins leading to a greater exposure to unsatisfactory recovery following disturbances. System security is no longer seen as a systems planning concern but as an exercise in risk aversion which is controlled by the system operators. There is therefore a pressing need for operators to keep a close eye on the security of the system.

Assessment of system security is performed by determining the probability that the system will move from its normal operating conditions into an abnormal, or emergency state. These calculations are based upon a knowledge of the current state of the system, the conditions at the time and a forecast of load demand. In order to determine the response of the system it is necessary to apply these data to a model of the system and this is achieved using computer simulation. Contingency analysis packages attempt to determine what the response of the system will be to any of a list of possible contingencies, based upon a knowledge of current system state. A full analysis requires a simulation of the system for each combination of the contingencies in the list.

Many utilities operate their control systems in conjunction with on-line security monitoring and contingency analysis tools. Operators can continually monitor the state of system security and how that might be changed by future events (the contingencies). Using contingency analysis on this basis allows operators to determine what is likely to happen to the state of the system and take the appropriate preventative, or corrective, action as necessary. The many thousands of cases that have to be considered for a full contingency analysis make it prohibitively slow for on-line usage. Many techniques have been developed which reduce the list of contingencies to include only those which are most likely to occur. This reduces the time needed to perform an analysis and makes on-line contingency analysis possible. Such packages are still slow requiring between 5 and 15 minutes [5] to generate their results. If the contingency analysis package takes more than 15 minutes to complete its calculations then it is not worth using it as its predictions are based upon a model of the system which was updated too long ago for it to be accurate. Due to the high volume of calculations and the speed required, contingency analysis tools usually have to be executed on expensive, dedicated, high performance computers.

Many of the current contingency analysis tools only consider the steady state system and ignore the dynamic response of the system to transients. Dynamic analysis is possible but this requires many more calculations than the steady state analysis and as yet is too slow for on-line operation. Future developments would ideally make real - time dynamic analysis packages available to operators giving them much faster response to contingencies and improving standards of system security. With the increasing speed and capacity of modern computers it should soon be possible to develop such tools using the techniques of parallel and distributed computing in conjunction with the latest generation of high performance processors.

### 1.2.4 System Planning

System planners are continually seeking ways to improve and expand the current system. Analysis tools can be useful in this work by allowing the designer to perform 'what-if' studies

on various designs. Such studies are performed using computer models of the systems to simulate what happens to the systems when various changes are made. As system planning is not an on-line application there is no pressing need for real - time simulation but continued improvements in the speed of the tools used by system planners will manifest themselves in a reduction in the design to construction time of system improvements. As a final stage in the design assessment it may be necessary to undertake a real - time dynamic simulation to determine the performance of the new design.

### 1.2.5 Operator Training

The flow of power in the power system, or part of the system, is controlled from a central control room by trained operators known as dispatchers. The dispatchers meet the demand from users by controlling the flow of power around the network and have to deal with emergencies such as sudden changes in load demanded or equipment outages. New dispatchers must be trained to operate the control room mechanisms and to handle the various emergency situations that may arise. Trained dispatchers need to continually improve their skills, especially those relating to potentially catastrophic emergencies which seldom occur. It would be foolhardy to let trainees practice on the real system as an error in their responses could place the system into a potentially unstable state. Recent advances in reliability have meant that it is difficult to acquire the skills needed to cope with all conceivable operating conditions within the actual operating environment [6]. Some form of simulated environment is the most effective method of providing the necessary training. Training with a simulator gives the dispatcher greater confidence to take the correct actions when faced with the same situation in the actual system. To be most effective it is necessary for the simulator to provide the same interfaces to the system as the control room provides. This requires the development of a control room mock-up in which all interaction with the simulator is made through the same computers, screens and other hardware used in the real control room. Due to their effectiveness dispatcher training simulators are now an integral part of the energy management systems of many power utilities [7].

All dispatcher training simulators have two main components; a control centre model and a power system model. The control centre model provides all the main functions of a real dispatch control centre including data acquisition, supervisory control, system monitoring and man-machine interfaces. The system model provides an equivalent model of the system being controlled which must be sophisticated enough to realistically reproduce the responses

### 1.3 \_\_\_\_\_ Power Systems Analysis and Computer Architectures

of the actual system. This requires the model to accurately simulate the dynamics of the system. Two distinct components of the system model can be identified in all dispatcher training simulator designs [6, 7, 8] - the static model and the dynamic model.

- Dynamic model Models the system components to provide dynamic simulation of generators, loads, prime mover systems, protective relays, substation controls *etc.*

- Static model Models the power system network and provides the power flow solution, network topology analysis, system frequency deviation and transient stability calculations.

Biglari [7] and other researchers observe that it is the solution of the power flow equations which is the most time consuming stage in the power system model. Furthermore, the solution time of the power flow equations directly determines the iteration cycle time of the power system model component of the simulator. Although fast decoupled solution techniques are employed the time taken to solve for power flow equations is significant. The long solution times mean that it is not possible to accurately represent the responses of the system's fast dynamics.

### **1.3** Power Systems Analysis and Computer Architectures

Digital computer analysis of power systems developed in the 1960's when the availability of large digital computers made it feasible to use such technology as a fast and flexible tool for modeling power system behaviour. Early research into computer analysis techniques quickly highlighted the disparity between problem size and the capabilities of the computer technology available at that time [9]. Researchers concentrated on developing highly efficient algorithms which would extract the maximum performance from machines which were primitive and limited in their performance. As computers have become more powerful, engineers have exploited this increased power by creating analysis tools to run on these machines. With the development of extremely high performance supercomputers the software designers have naturally looked toward these machines to see what benefits they have in store for power engineering applications. Whilst they are extremely efficient and offer incredible performance these machines are expensive and beyond the budget of most power utilities.

As the sequential computer nears the limits of its performance much attention has been

### 1.3 \_\_\_\_\_ Power Systems Analysis and Computer Architectures

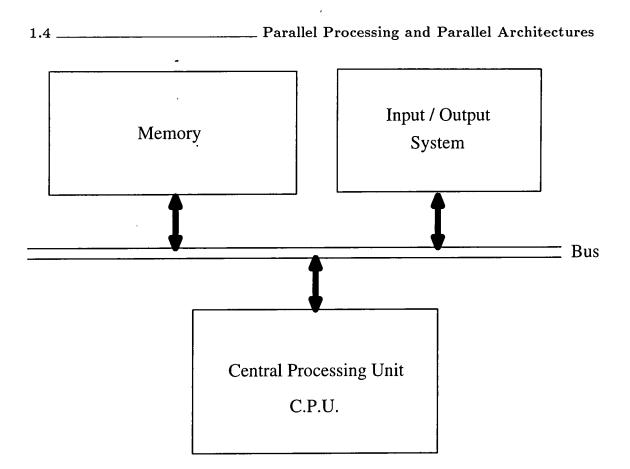

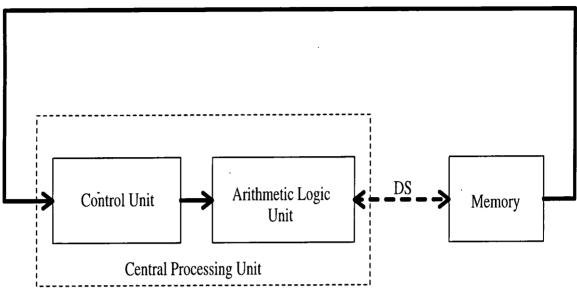

focused on the development of parallel computers which offer higher performance from existing technology than conventional sequential machines. These computers are built from tried and tested processors and achieve their performance by allowing many operations to be performed simultaneously, thereby reducing the total amount of time taken to execute a given algorithm. Parallel computers are not new; they have been in existence since the digital computer was first developed. Given their performance benefits it may seem surprising that they have not achieved widespread usage in commercial, scientific and engineering applications. This apparent unpopularity is due to the lack of commercial software and the difficulties of developing applications software. Whilst it may be argued that concurrency is a more natural and logical way of solving problems, a different approach is required for the development of parallel programs than is used in developing sequential programs. Many programmers used to sequential machines are used to the von Neumann model and find it difficult to work with the different architectural models and programming paradigms associated with parallel machines

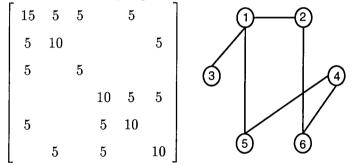

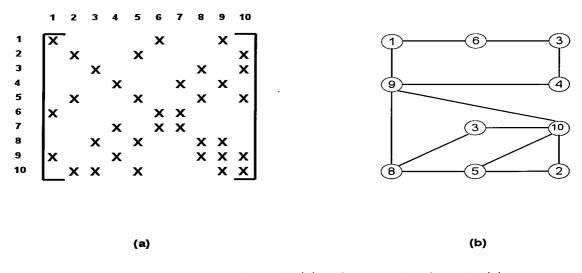

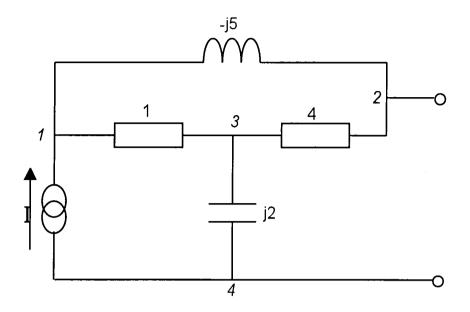

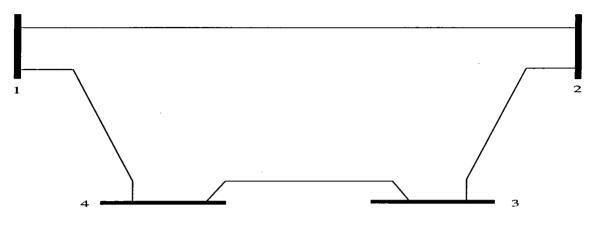

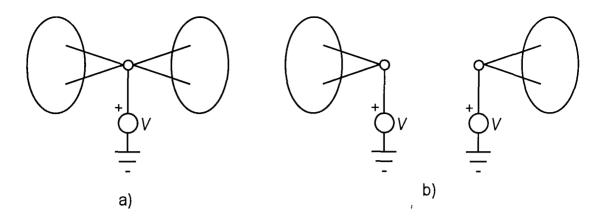

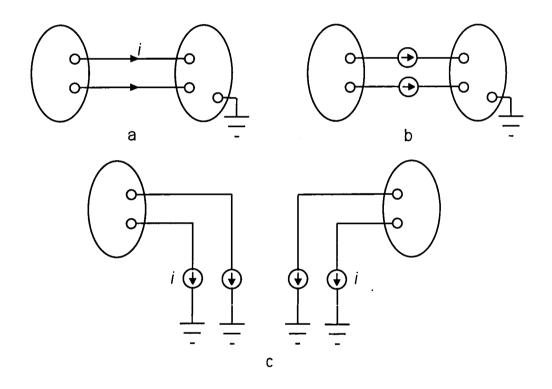

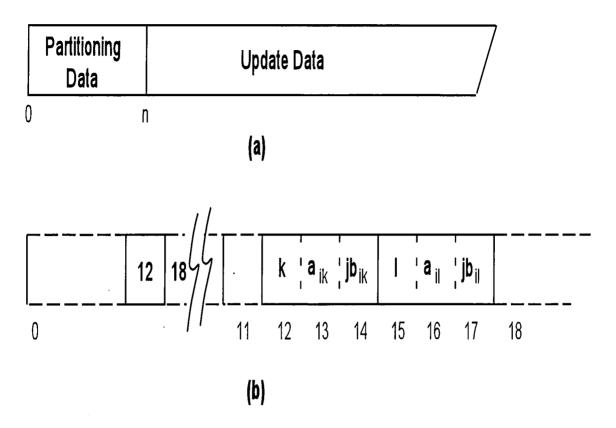

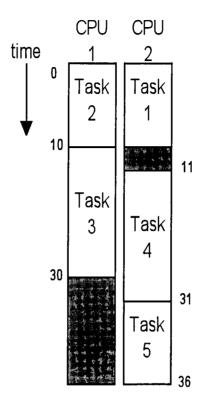

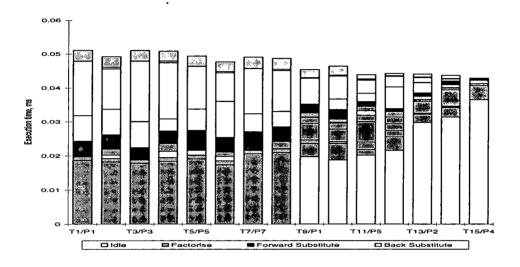

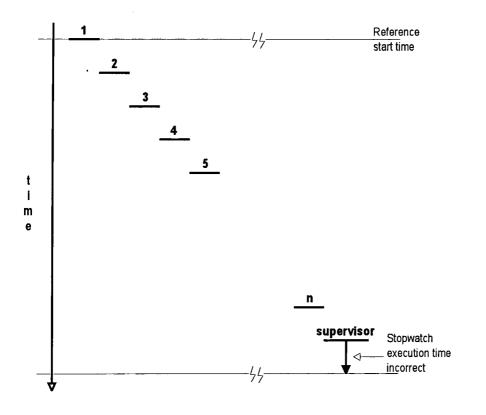

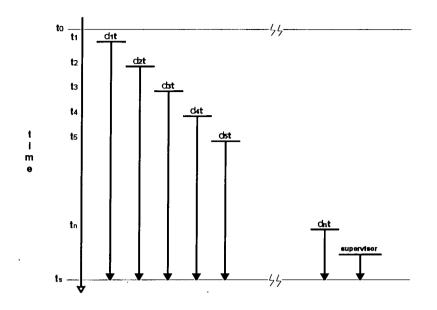

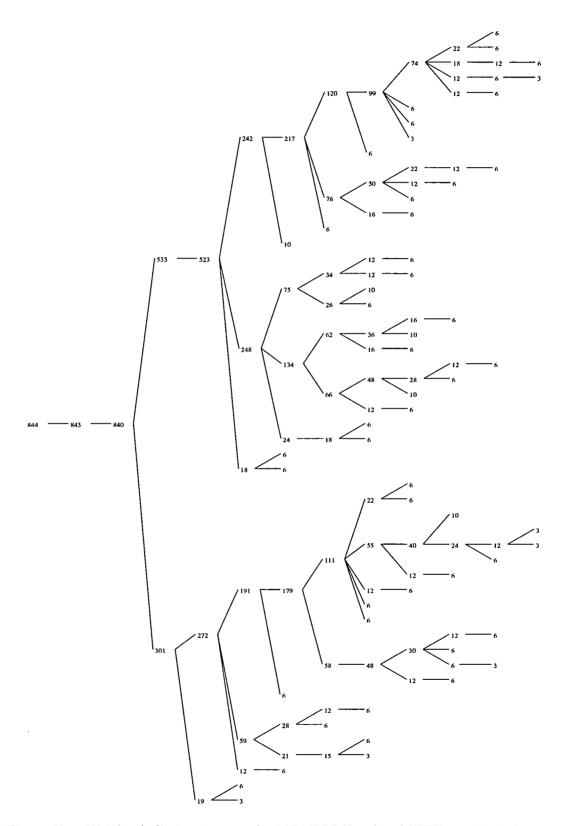

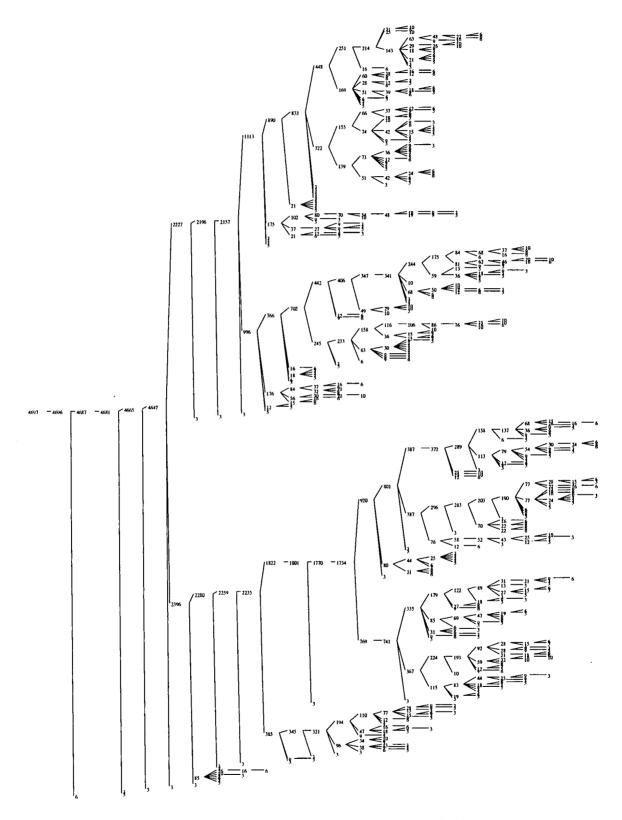

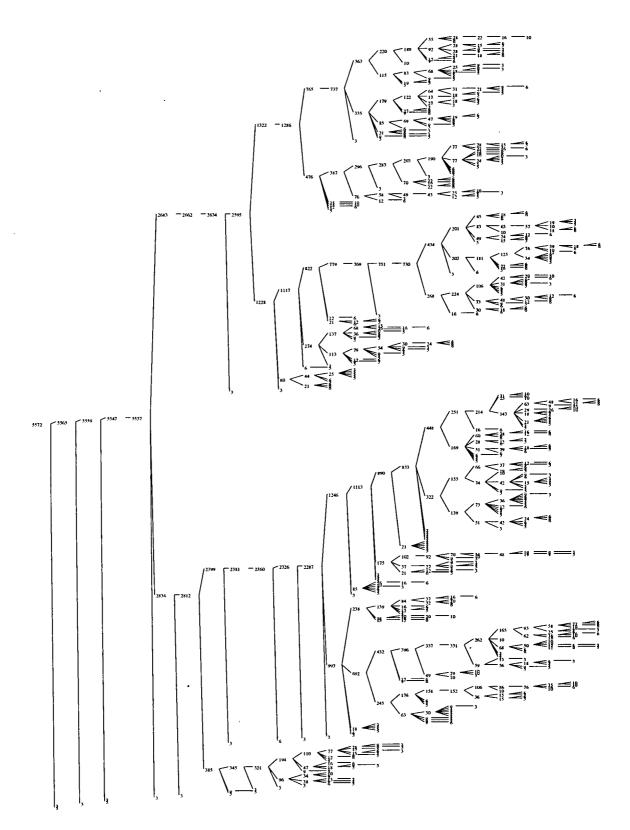

In recent years a number of smaller 'turnkey' parallel computing systems have arrived in the marketplace (e.g. Intel iPSC, Meiko Computing Surfaces and INMOS Transputer based systems). These systems are built from readily available microprocessors which makes them cheap and accessible to a wide user base. Even in 1988 for as little as £15,000, the price of a mid-range workstation, it was possible to buy an off-the-shelf parallel system with more than 8 processors and a performance approaching 100 MFLOPS [10], which exceeded the performance of the similarly priced workstation. With the introduction of such systems the software developers have seen a market niche opening up. Software manufacturers have expanded to fill this niche and there are now a variety of operating systems available for these entry level parallel systems, including the ever-popular Unix. The development of parallel versions of traditional sequential languages (e.g. C and FORTRAN) along with the introduction of new parallel languages (e.g. Occam) has eased the process of developing software applications. In the past one criticism that has been levelled at parallel computers is that algorithm development and hardware architecture are too deeply intertwined to be treated independently. The advent of high-level 'parallel' languages has seen a move toward abstracting the logical development of programs away from the architectural details of the machine. As these systems fall in price and more software is developed, more details of the hardware become hidden from the programmer making the machines easier to program.