# **Durham E-Theses**

# The reliability of small digital controllers

Pearson, Jonathon C.

#### How to cite:

Pearson, Jonathon C. (1983) The reliability of small digital controllers, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/7217/

#### Use policy

$The full-text\ may\ be\ used\ and/or\ reproduced,\ and\ given\ to\ third\ parties\ in\ any\ format\ or\ medium,\ without\ prior\ permission\ or\ charge,\ for\ personal\ research\ or\ study,\ educational,\ or\ not-for-profit\ purposes\ provided\ that:$

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

Academic Support Office, The Palatine Centre, Durham University, Stockton Road, Durham, DH1 3LE e-mail: e-theses.admin@durham.ac.uk Tel: +44 0191 334 6107 http://etheses.dur.ac.uk

# THE RELIABILITY OF SMALL

## DIGITAL CONTROLLERS

#### by

Jonathan C.Pearson BSc(Eng), ACGI

The copyright of this thesis rests with the author. No quotation from it should be published without his prior written consent and information derived from it should be acknowledged.

Thesis submitted for the degree of Doctor of Philosophy in the Faculty of Science University of Durham

September 1983

# 25. JAN. 1984

Thesis 1983/PEA ł

# Dedicated to

C

# MY MOTHER AND FATHER

.

.

, ··

#### ABSTRACT

Increasing use is being made of small digital controllers in Industry The failure of such controllers is important since it may and Commerce. either cause, plant to become unsafe or the interruption of production. Faulttolerant techniques are discussed for improving the reliability of digital hybrid development of а special reference the to with controllers electromechanical gas governor, whose electronic controller is an example of a small digital controller. Three microprocessors are used in a two out of three majority voting configuration and the memory is Hamming code Redundancy techniques are used to protect against faults in protected. parts of the controller and it will tolerate most classes of other transient fault.

When comparing designs or attempting to meet reliability criteria, it is necessary to predict the reliability of a system and its individual Several sources of failure rate prediction are compared and components. integrated circuits İS of failure rates wide variation in the the The comparison concludes by recommending which reliability highlighted. data source is likely to be most accurate for each type of component.

The gas governor is an example of a repairable system and analysis is developed for predicting the improvement in reliability for repairable redundant systems and for determining the optimum maintenance and repair times for equipment.

The testing of redundant systems is difficult because of their complexity, and under certain circumstances the redundancy can mask design faults. Testing methods using complex test equipment are described, as well as the testing of the experimental controller.

A review is included of other fault-tolerant systems. Although the work on large computers is not directly applicable to small controllers. many of the techniques can be used.

#### - i -

#### Acknowledgements

I should like to express my gratitude to the following people. To Dr Clive Preece, my Supervisor, for his help, encouragement, friendship, and British Gas To the assistance in the preparation of this Thesis. Corporation for the provision of a Research Scholarship and equipment. То his help, encouragement, and the acquisition of Dr Ken Jenkins for equipment, and also for the close links between the Engineering Research Station and the Department of Engineering. I would like to thank Mr Robert Halse for his help and discussion. To Dr David Smith for his interest and valuable discussion about this research. To the Electrical Technicians for jobs too numerous to mention and to Motorola for providing much useful Finally I would like to thank Gillian for her reliability information. love and encouragement in the preparation of this Thesis.

. :

. r

| co | N٦ | ٢E | N | тs |

|----|----|----|---|----|

|    |    |    |   |    |

|       |   |             |         |                                        | Page  |

|-------|---|-------------|---------|----------------------------------------|-------|

|       |   | LIST OF FIG | JRES    |                                        | ix    |

|       |   | LIST OF TAB | LES     |                                        | хi    |

|       |   | LIST OF SYN | BOLS    |                                        | × i i |

|       |   | CHAPTER 1   | The Nee | ed for a Reliable Controller           | 1     |

|       |   | 1.1         | NATIONA | L GAS NETWORK                          | 1     |

|       |   | 1.2         | PNEUMA  | TIC GOVERNORS                          | 2     |

|       |   | 1.3         |         | ONS OF PNEUMATIC GOVERNORS             | 4     |

|       |   | CHAPTER 2   | A Revie | w of Other Fault-tolerant Controllers  | 7     |

|       |   | 2.1         | SMALL C | ONTROLLERS                             | 7     |

|       |   |             | 2.1.1   | TMR controllers                        | 7     |

|       |   |             | 2.1.2   | Fail-safe controller                   | 8     |

|       |   |             | 2.1.3   | Built in test equipment                | 9     |

|       |   | 2.2         | LARGE C | OMPUTERS                               | 9     |

|       | • |             | 2.2.1   | Space shuttle and avionics             | 9     |

|       |   |             | 2.2.2   | Commercial computers                   | 11    |

|       |   |             | 2.2.3   | Telephone exchange computers           | 12    |

|       |   |             | 2.2.4   | Safety monitoring computer             | 12    |

|       |   |             | 2.2.5   | PDP11 computer                         | 13    |

|       |   |             | 2.2.6   | Railway applications                   | 13    |

|       | • |             | 2.2.7   | Fault-tolerant software                | 14    |

|       |   | 2.3         | SUMMAF  | ΥY .                                   | 14    |

| 4 - 4 | • | CHAPTER 3   | Failure | of Components                          | 17    |

|       |   | 3.1         | FAILURE | DISTRIBUTION AND MECHANISMS            | 17    |

|       |   | 3.2         | FAILURE | RATE MEASUREMENT AND ACCELERATION      | 18    |

|       | · |             | 3.2.1   | Accelerated testing                    | 19    |

|       | • | 3.3         | FAILURE | RATE PREDICTION                        | 21    |

|       |   |             | 3.3.1   | CNET                                   | 23    |

| ^     |   |             | 3.3.2   | National centre of systems reliability | 24    |

|       |   |             |         |                                        |       |

|     | 3.3.3  | RADC field data                                     | 25 |

|-----|--------|-----------------------------------------------------|----|

|     | 3.3.4  | European space agency                               | 25 |

|     | 3.3.5  | Manufacturers testing                               | 25 |

|     | 3.3.6  | Simple models                                       | 26 |

|     | 3.3.7  | GIDEP computer data base                            | 26 |

|     | 3.3.8  | EuReData                                            | 27 |

|     | 3.3.9  | MIL-217 data base                                   | 27 |

| 3.4 | COMPAR | RISON OF FAILURE RATE DATA                          | 27 |

|     | 3.4.1  | Resistors                                           | 28 |

|     | 3.4.2  | Capacitors                                          | 28 |

| •   | 3.4.3  | Soldered joints                                     | 28 |

|     | 3.4.4  | Wire-wrap connections                               | 28 |

|     | 3.4.5  | Edge connectors                                     | 29 |

|     | 3.4.6  | Integrated circuits                                 | 29 |

|     | 3.4.7  | TTL integrated circuits                             | 32 |

|     | 3.4.8  | 6800 microprocessor                                 | 32 |

|     | 3.4.9  | 8080 microprocessor                                 | 33 |

|     | 3.4.10 | EPROM                                               | 34 |

|     | 3.4.11 | Bipolar ROMs                                        | 34 |

|     | 3.4.12 | Dynamic RAM                                         | 34 |

|     | 3.4.13 | Static RAMs                                         | 34 |

|     | 3.4.14 | Comparison with other field data                    | 35 |

|     | 3.4.15 | Recommendations                                     | 36 |

| 3.5 |        | RISON OF DIFFERENT DEVICE TECHNOLOGIES AND SULATION | 37 |

|     | 3.5.1  | CMOS versus TTL                                     | 38 |

|     | 3.5.2  | Hermetic versus non-hermetic encapsulation          | 39 |

|     | 3.5.3  | Recommendations                                     | 43 |

| 3.6 | SCREEN | NING AND METHODS OF IMPROVING FAILURE RATES         | 44 |

|     | 361    | Derating and cooling                                | 46 |

| 3.7       | SOFTWARE AND TRANSIENT ERRORS                                             | 47 |

|-----------|---------------------------------------------------------------------------|----|

| 3.8       | SUMMARY                                                                   | 50 |

| CHAPTER 4 | Prediction of Reliability Improvement due to<br>Fault-tolerant techniques | 52 |

| 4.1       | METHODS OF EXPRESSING RELIABILITY                                         | 52 |

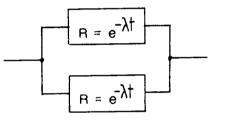

| 4.2       | EFFECT OF REDUNDANCY ON RELIABILITY                                       | 54 |

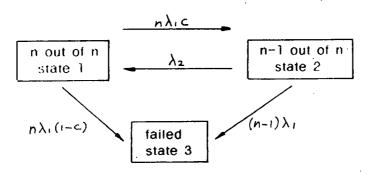

| 4.3       | EFFECT OF MAINTENANCE ON A SYSTEM                                         | 55 |

|           | 4.3.1 Redundant systems                                                   | 56 |

| 4.4       | METHODS OF EXPRESSING IMPROVEMENT                                         | 59 |

| 4.5       | SUMMARY                                                                   | 60 |

| CHAPTER 5 | Techniques for Improving a System's Fault-tolerance                       | 62 |

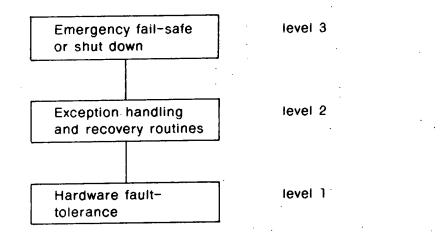

| 5.1       | LEVELS OF FAULT-TOLERANCE                                                 | 62 |

| 5.2       | DESIGN TOOLS                                                              | 63 |

|           | 5.2.1 FMECA                                                               | 63 |

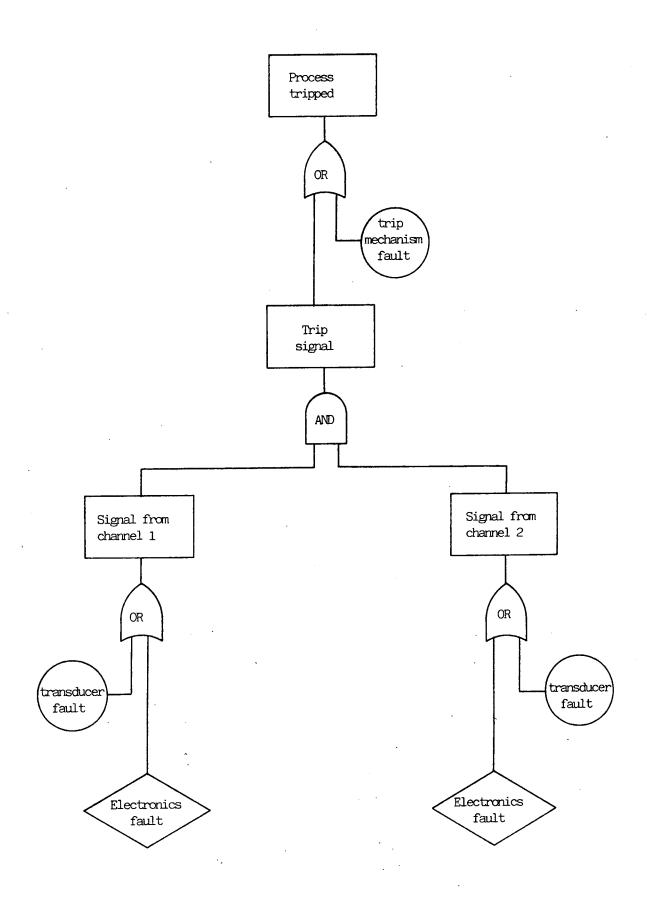

|           | 5.2.2 FTA                                                                 | 64 |

| 5.3       | HARDWARE                                                                  | 64 |

| •         | 5.3.1 Watchdog timer                                                      | 64 |

|           | 5.3.2 Snake                                                               | 65 |

|           | 5.3.3 Power supply levels                                                 | 66 |

|           | 5.3.4 Output verification                                                 | 66 |

|           | 5.3.5 Component redundancy                                                | 66 |

|           | 5.3.6 Memory protection                                                   | 67 |

|           | 5.3.7 Temperature                                                         | 67 |

| 5.4       | SOFTWARE                                                                  | 67 |

|           | 5.4.1 Exception handling                                                  | 68 |

| 5.5       | SELF-TESTING                                                              | 69 |

| 5.6       | SUMMARY                                                                   | 70 |

| CHAPTER 6 | EFFECT OF SYSTEM ARCHITECTURE ON RELIABILITY<br>AND COST                  | 72 |

| 6.1       | CHOICE OF MICROPROCESSOR                                                  | 72 |

| '         | 6.1.1 Single chip microprocessors                                         | 72 |

- v -

•

•

|       |           |          | ·                                    |      |

|-------|-----------|----------|--------------------------------------|------|

|       |           | 6.1.2 ·  | Eight-bit microprocessors            | 72   |

|       |           | 6.1.3    | Sixteen-bit microprocessors          | 73   |

|       | 6.2       | MAJORITY | VOTING                               | 74   |

|       |           | 6.2.1    | Hardware                             | 74   |

|       |           | 6.2.2    | Software                             | 75   |

|       | 6.3       | THE USE  | OF REDUNDANCY AND INCREASED COST     | 75   |

|       | CHAPTER 7 | Backgro  | und to Design of Governor Controller | 78   |

|       | 7.1       | SPECIFIC | ATION                                | 78   |

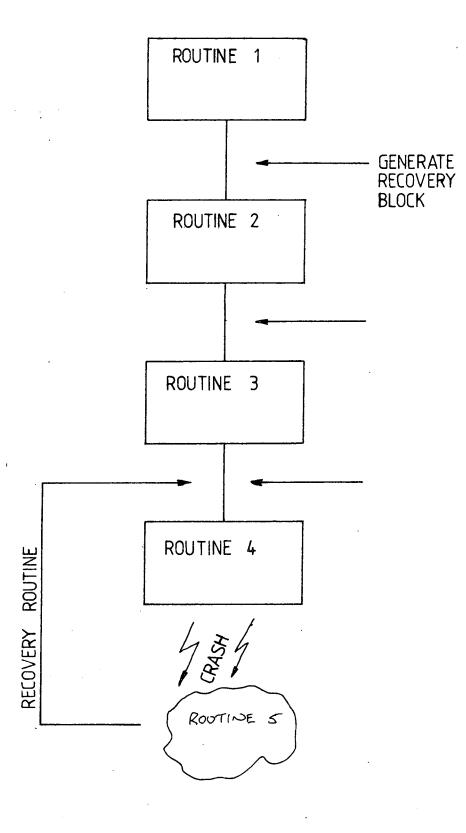

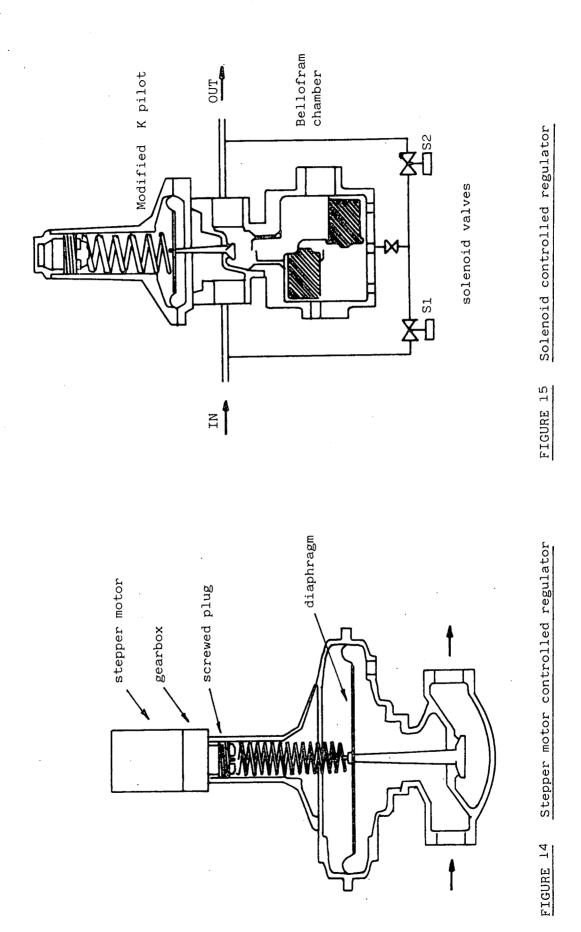

|       | 7.2       | MECHAN   | ICAL VALVE                           | 79   |

|       | 7.3       | NON FAL  | ILT-TOLERANT CONTROLLER              | 82   |

|       | 7.4       | METHOD   | S OF INTRODUCING FAULT-TOLERANCE     | 83   |

| · .   | CHAPTER 8 | Descript | tion of Experimental Controller      | 86   |

|       | 8.1       | CONSTRU  | JCTION                               | 86   |

|       | 8.2       | TMR MIC  | ROPROCESSOR BOARD                    | 86   |

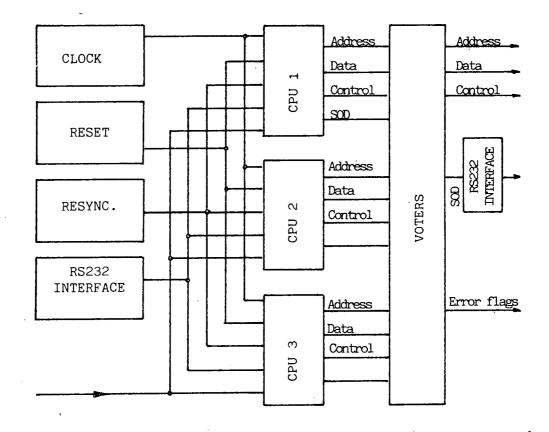

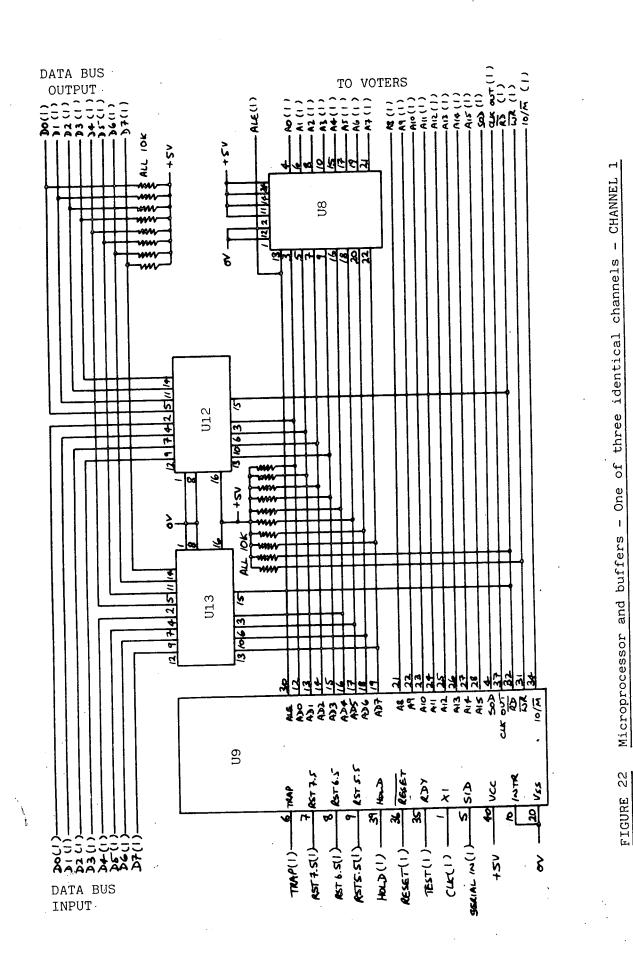

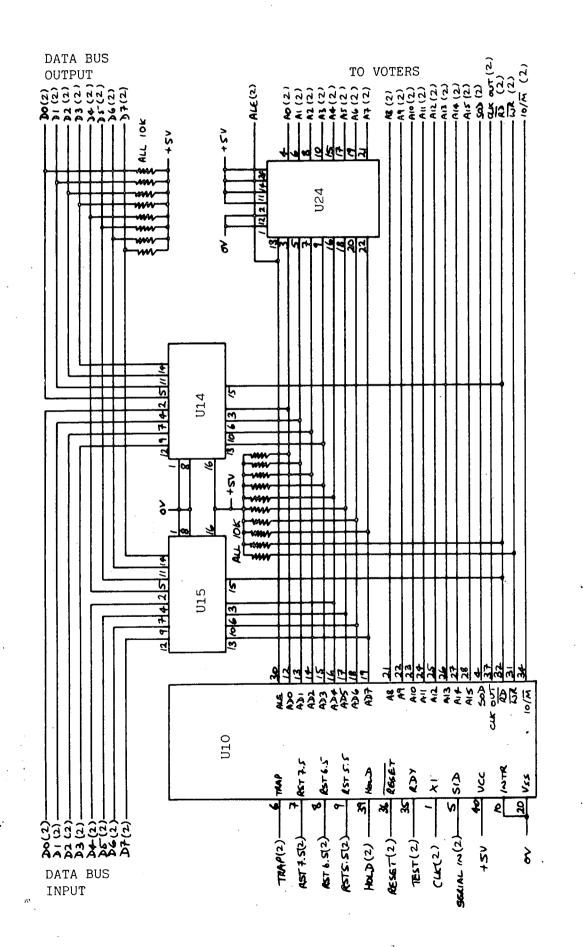

|       |           | 8.2.1    | Microprocessor block                 | 87   |

|       |           | 8.2.2    | Voters                               | 87   |

|       |           | 8.2.3    | Self synchronising clock             | 88   |

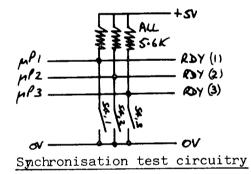

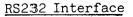

|       |           | 8.2.4    | Synchronisation hardware             | 89   |

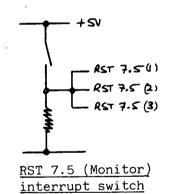

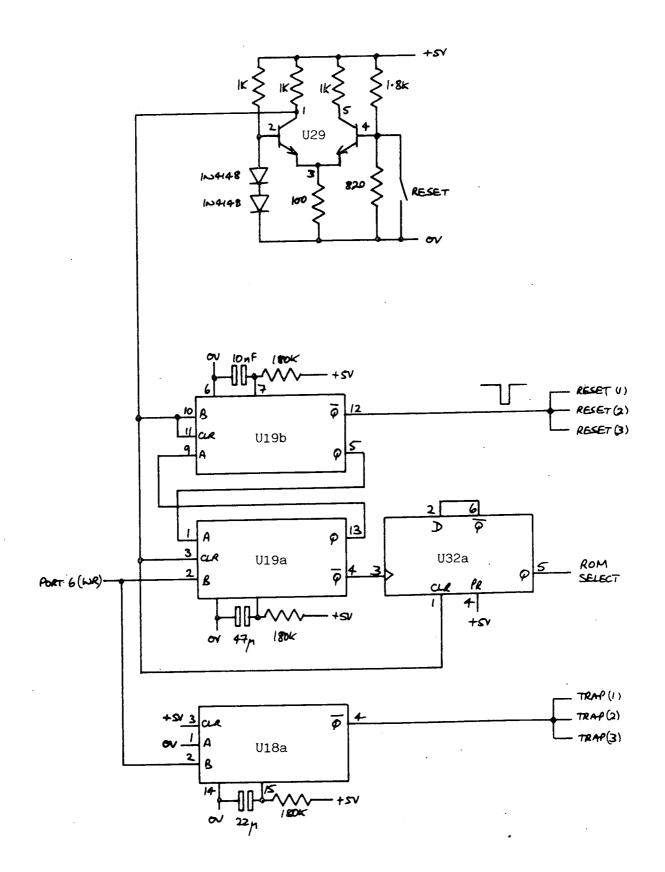

|       |           | 8.2.5    | Reset circuitry and watchdog timers  | 92   |

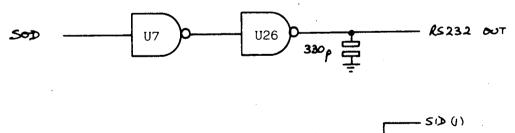

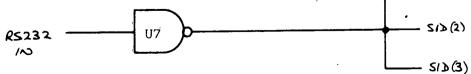

|       |           | 8.2.6    | RS232 interface                      | . 94 |

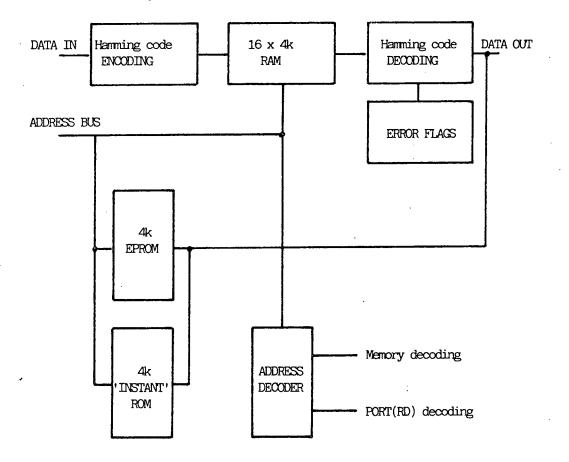

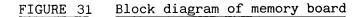

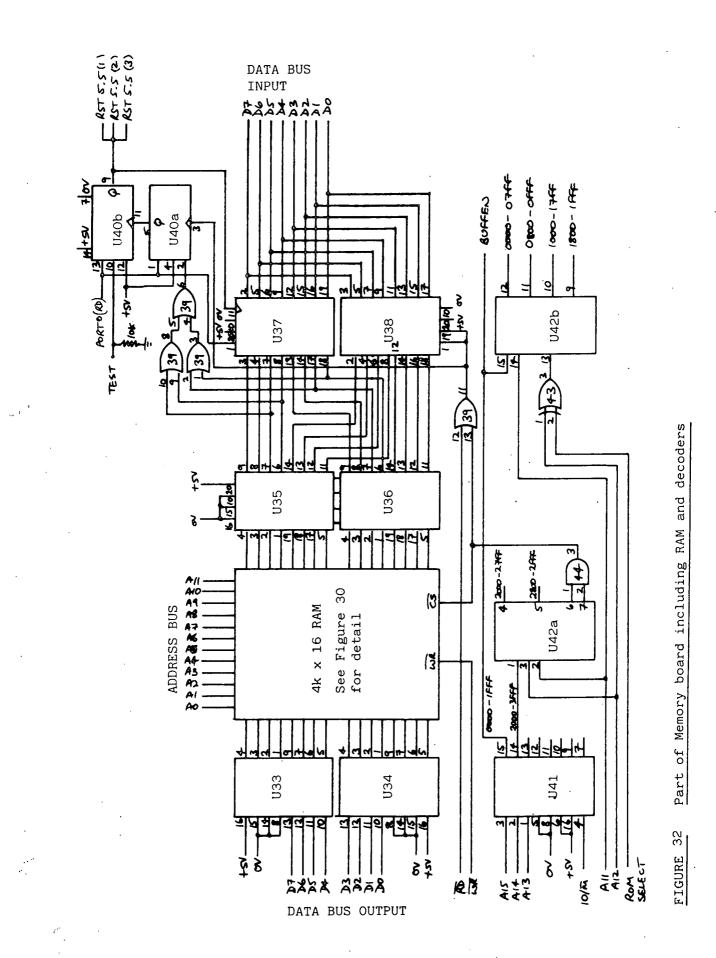

| :     | 8.3       | MEMORY   | BOARD                                | 94   |

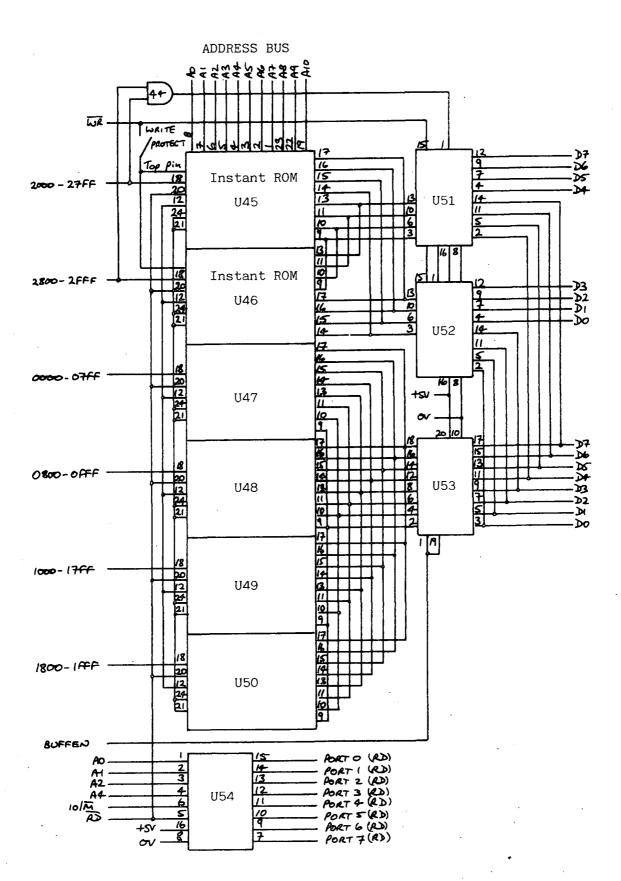

| · · · |           | 8.3.1    | Decoding                             | 96   |

|       |           | 8.3.2    | Circuit description                  | 96   |

|       |           | 8.3.3    | Address decoding and "spare" EPROMs  | 97   |

| • • • |           | 8.3.4    | Memory matrix                        | 98   |

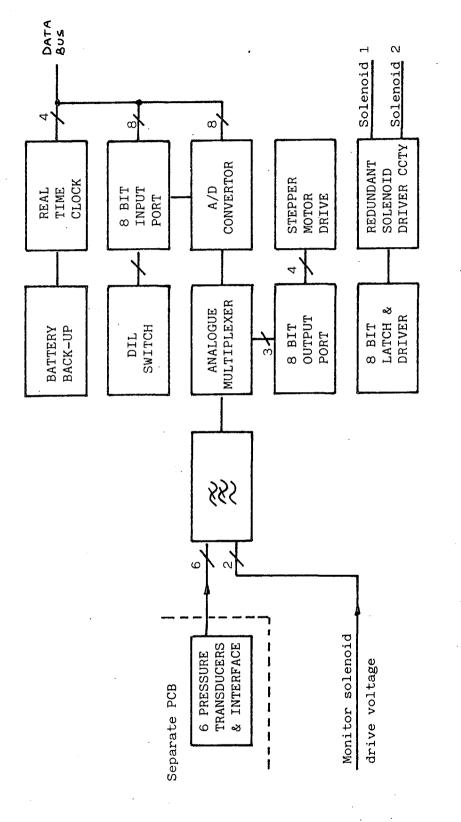

|       | 8.4       | INPUT/O  | UTPUT BOARD                          | - 98 |

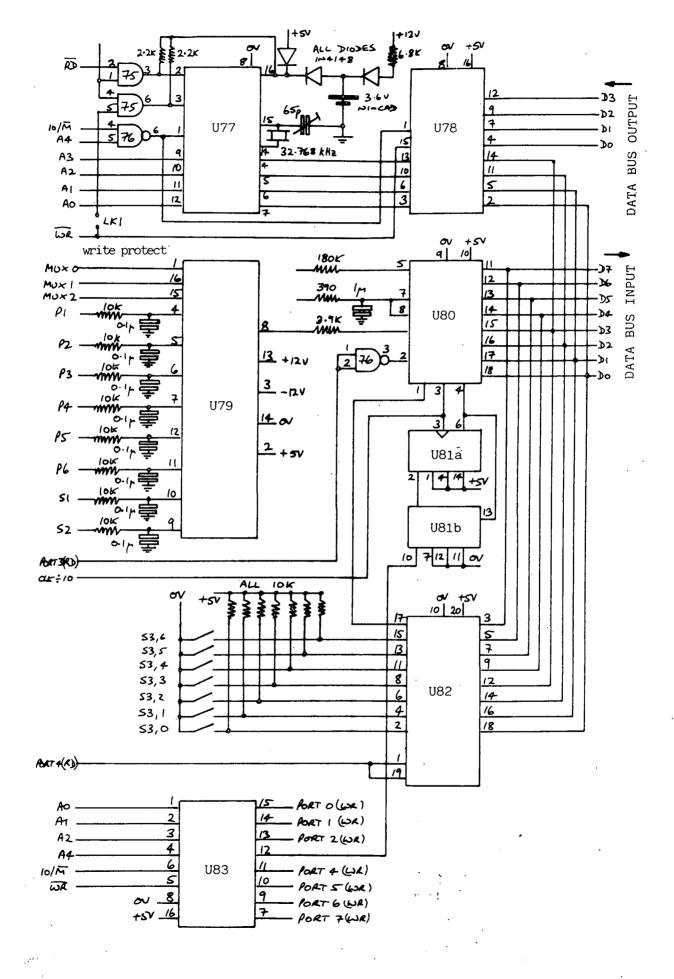

|       |           | 8.4.1    | Real time clock                      | 99   |

|       |           | 8.4.2    | Multiplexer and A/D converter        | 99   |

|       |           | 8.4.3    | Stepper motor driver                 | 100  |

|       |           | 8.4.4    | Solenoid drive circuitry             | 100  |

|       | ۱         |          |                                      |      |

|       |           |          |                                      |      |

.

|     |           |           | - vii -                       | · .     |       |

|-----|-----------|-----------|-------------------------------|---------|-------|

|     |           |           |                               |         |       |

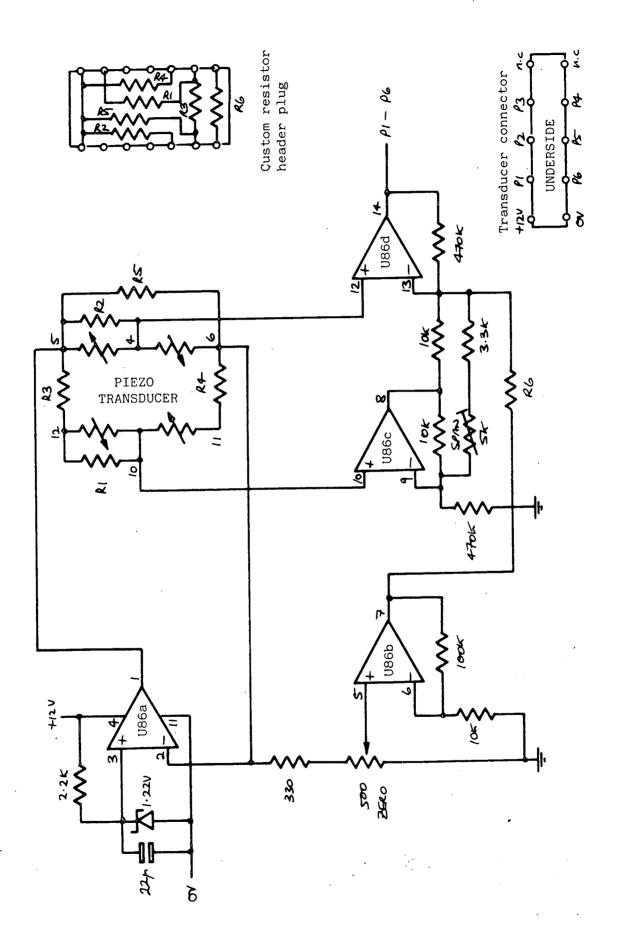

|     |           | 8.4.5     | Pressure transducers          |         | 101   |

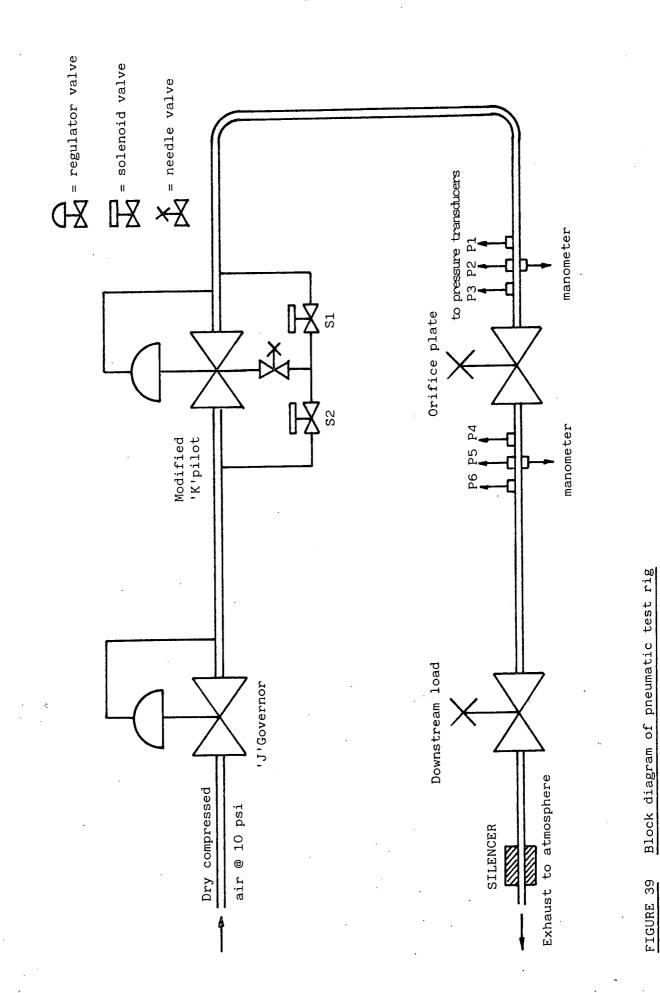

|     | 8.5       | PNEUMA    | TIC TEST RIG                  |         | 102   |

|     | 8.6       | ESTIMAT   | ED RELIABILITY                |         | 104   |

|     |           | 8.6.1     | Revised failure rate predicti | on      | 106   |

|     | CHAPTER 9 | Governo   | or Controller Software        |         | 107   |

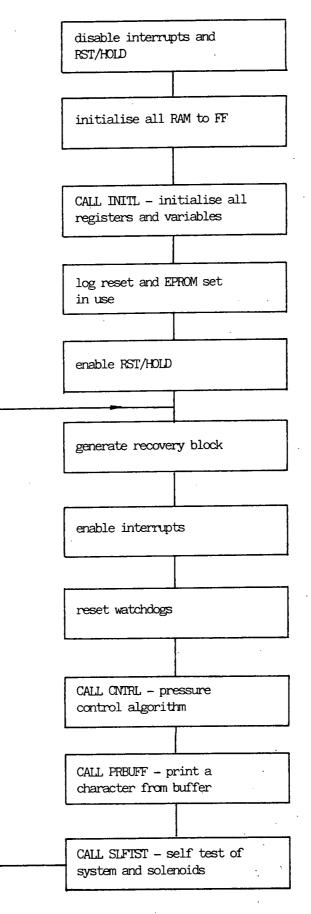

|     |           | 9.1.1     | MAIN                          |         | 107   |

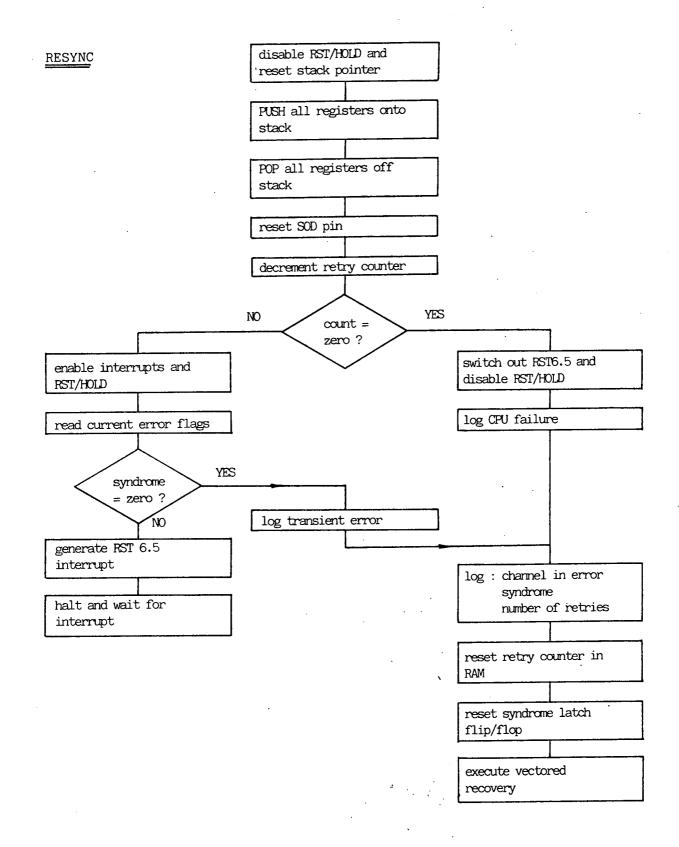

|     |           | 9.1.2     | RESYNC                        |         | 108   |

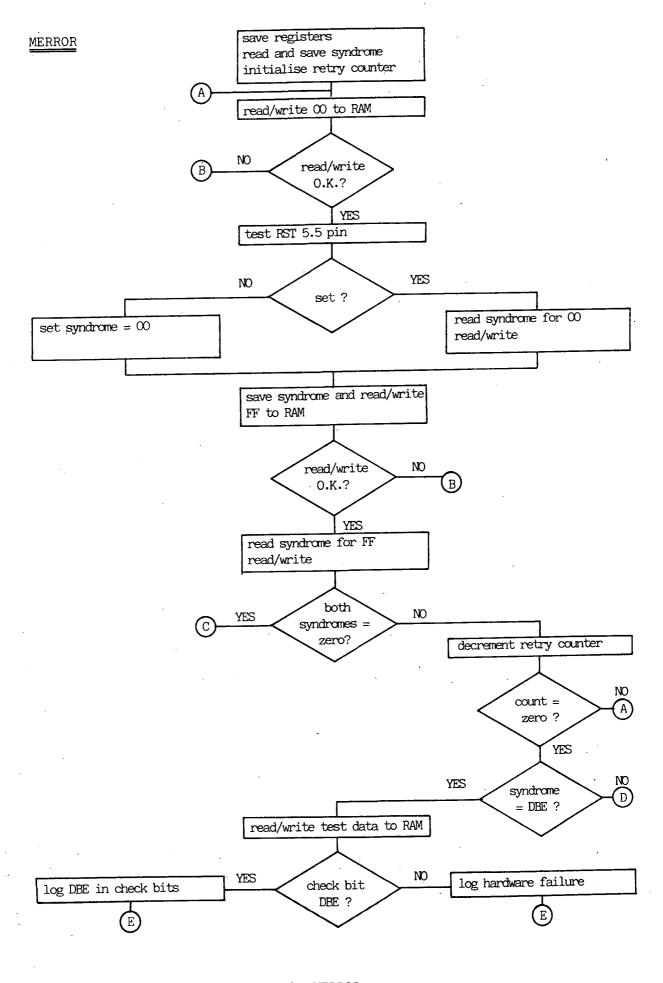

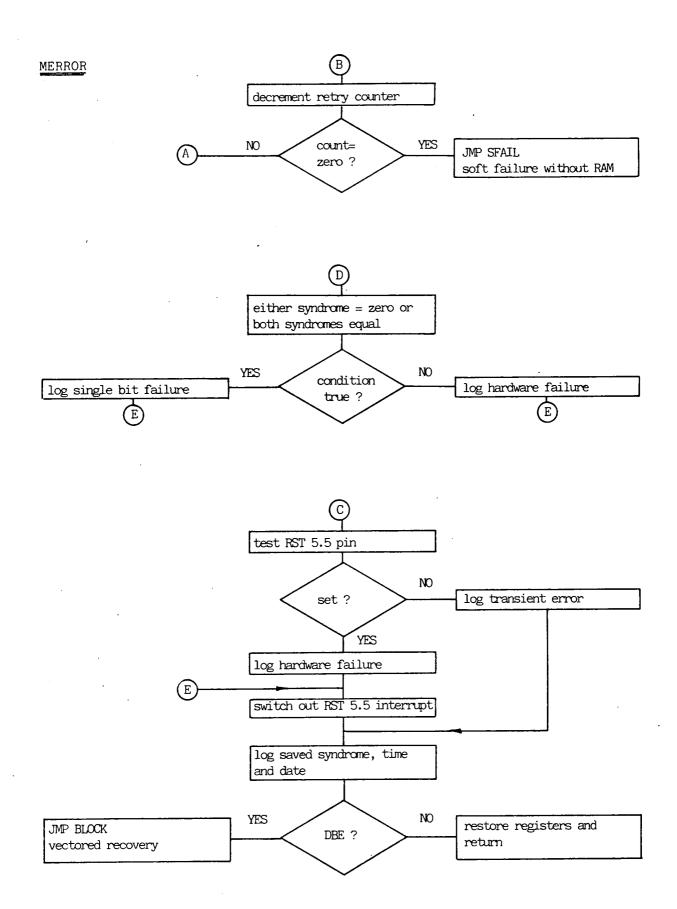

|     |           | 9.1.3     | MERROR                        | •       | 109   |

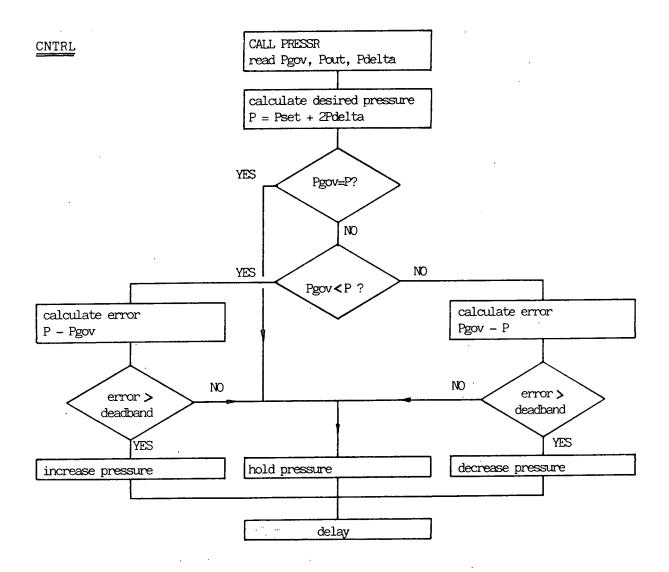

|     |           | 9.1.4     | CNTRL                         | · · · · | 110   |

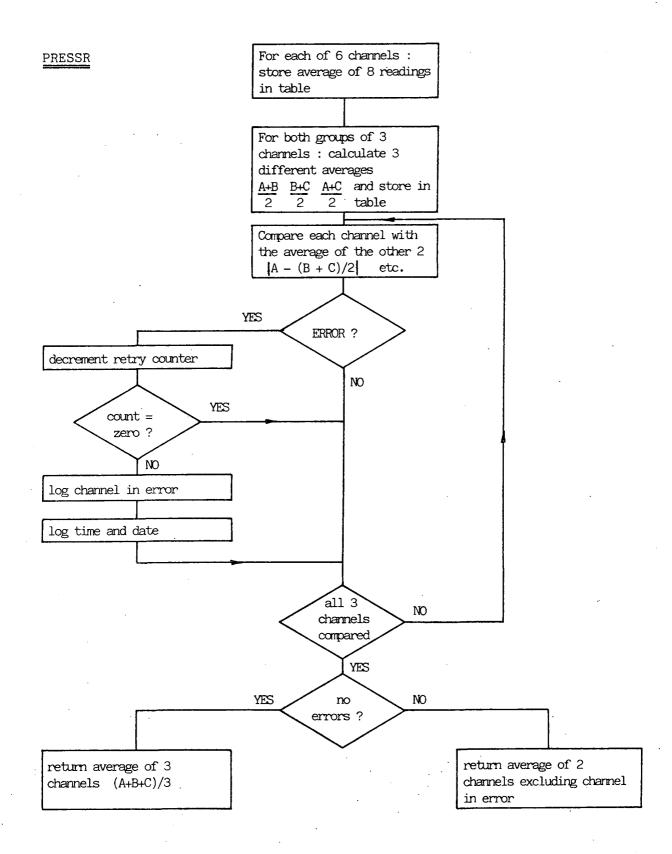

|     |           | 9.1.5     | PRESSR                        |         | 111   |

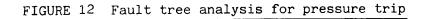

|     | ·         | 9.1.6     | RBKGEN                        |         | 111   |

|     |           | 9.1.7     | BLOCK                         |         | 111   |

| •   |           | 9.1.8     | SLFTST                        | *       | 112   |

|     |           | 9.1.9     | SFAIL                         |         | 112   |

|     |           | 9.1.10    | WTRAP                         |         | - 112 |

|     |           | 9.1.11    | SNAKE                         |         | 113   |

|     |           | 9.1.12    | DFAULT                        |         | 113   |

|     |           | 9.1.13    | INITL                         | •       | 113   |

|     |           | 9,1.14    | COUT                          |         | 113   |

|     |           | 9.1.15    | COUTBF                        | :       | 114   |

|     |           | 9.1.16    | PRBUFF                        |         | 114   |

|     |           | 9.1.17    | MSGE                          |         | 114   |

|     |           | 9.1.18    | NMOUT                         |         | 114   |

| · . |           | 9.1.19    | TIMLOG                        |         | 114   |

|     | CHAPTER 1 | 0 Testing | of Fault-tolerant Systems     |         | 115   |

|     | 10.1      | SYSTEM    | DEBUGGING                     |         | 115   |

|     | ·         | 10.1.1    | In-circuit emulation          |         | 115   |

|     |           | 10.1.2    | Logic analysis                |         | 115   |

|     | 10.2      | FAULT I   | NJECTION AND RECOVERY         |         | 117   |

|     | 10.3      | OPERAT    | IONAL TESTING                 |         |       |

| r - |           |           | ,                             | · ·     |       |

Ð

*.* •

| 10.4       | TESTING    | OF THE GOVERNOR CONTROLLER               | 118 |

|------------|------------|------------------------------------------|-----|

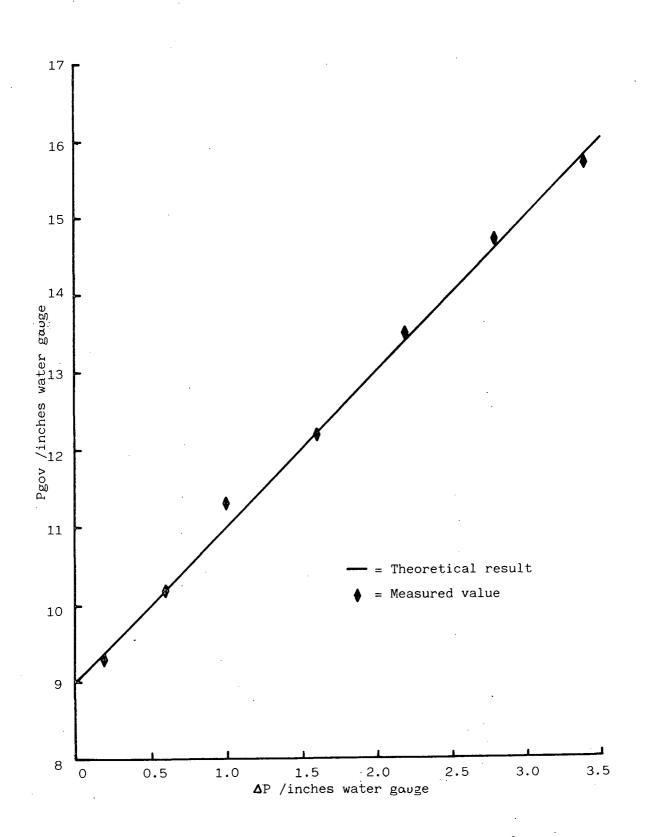

|            | 10.4.1     | Pressure control                         | 118 |

|            | 10.4.2     | Fault injection                          | 119 |

|            | 10.4.3     | Voting errors                            | 119 |

|            | 10.4.4     | RAM errors                               | 120 |

|            | 10.4.5     | Watchdogs                                | 120 |

|            | 10.4.6     | Snake                                    | 121 |

|            | 10.4.7     | Solenoid failure                         | 121 |

|            | 10.4.8     | Pressure transducers                     | 121 |

|            | 10.4.9     | Interference testing                     | 121 |

| DISCUSSION | N          |                                          | 123 |

| LIST OF RE | FERENCES   | 3                                        | 129 |

| FIGURES    |            | · · ·                                    | 136 |

| TABLES     |            |                                          | 174 |

| APPENDIX   |            |                                          | 185 |

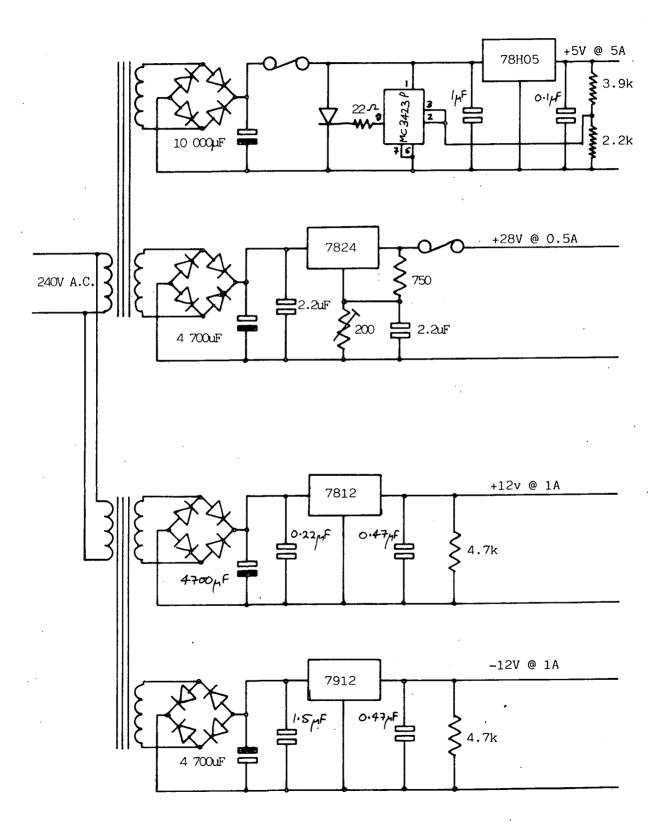

| 1.         | Circuit d  | liagram of power supply                  | 185 |

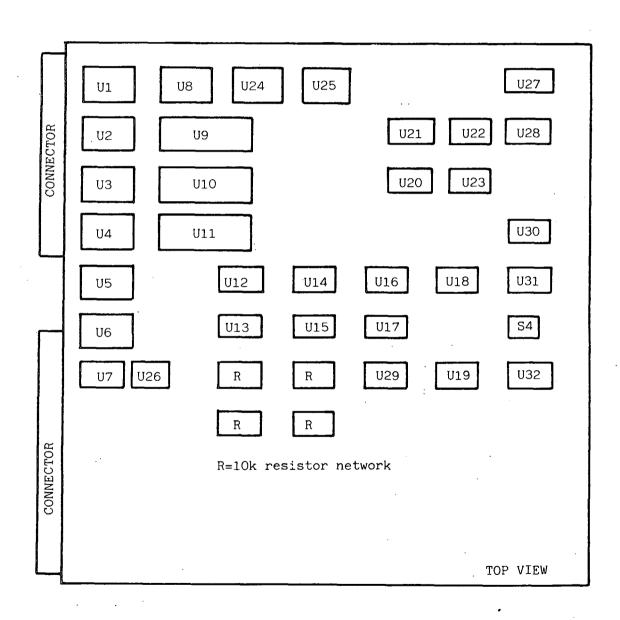

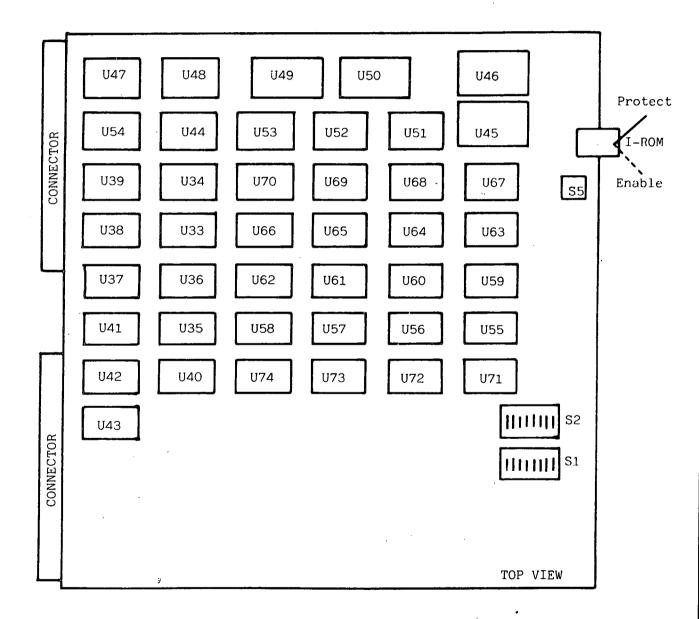

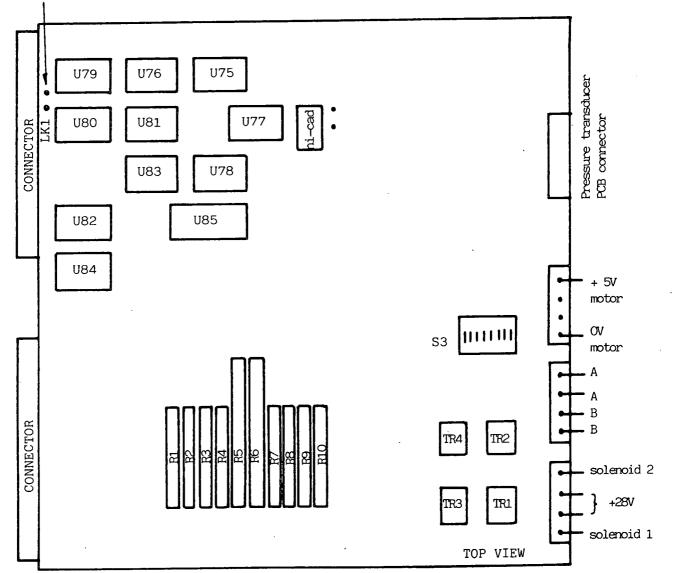

| 2.         | Circuit b  | oard layout                              | 186 |

| 3.1        | Error fla  | gs low pass filter calculation           | 190 |

| 3.2        | FPLA pro   | ogramming table                          | 191 |

| 4.         | Calculati  | ion of delay before latching error flags | 192 |

| 5.         | Encodin    | g ROM data                               | 194 |

| 6.         | Decodin    | g ROM data                               | 195 |

| 7.         | Operatio   | n of the real time clock                 | 196 |

| 8.         | Design (   | of redundant solenoid driver circuitry   | 197 |

| 9.         | List of ir | ntegrated circuits                       | 201 |

| 10         | Governo    | r controller software listings           | 202 |

viii-

۱

# LIST OF FIGURES

| Figu | ire .                                                                                                                                     | Page |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1    | Cross section of a Donkin FIG280 regulator                                                                                                | 136  |

| 2    | Governor and distribution network                                                                                                         | 137  |

| 3    | Twin stream governor                                                                                                                      | 137  |

| 4    | The bath-tub curve                                                                                                                        | 138  |

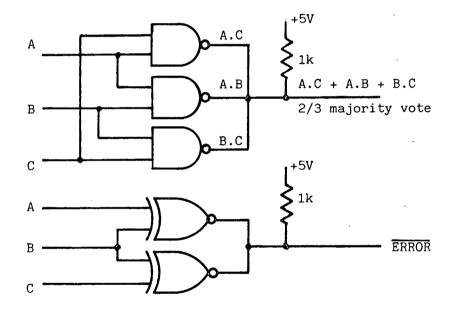

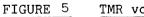

| 5    | TMR voter and error detection in open collector TTL logic                                                                                 | 138  |

| 6    | TMR ring structure                                                                                                                        | 138  |

| 7    | Graph of acceleration factor versus operating temperature for a reference temperature of 25°C. Plotted for different activation energies. | 139  |

| 8    | Failure rate of a 8085 microprocessor versus case ambient temperature                                                                     | 140  |

| 9    | BS9400 screening procedure                                                                                                                | 141  |

| 10   | Graph of simplex and TMR reliability versus normalised mission time.                                                                      | 142  |

| 11   | Graph of MTTFIF versus ratio $\lambda_2/\lambda_1$                                                                                        | 142  |

| 12   | Fault tree analysis for pressure trip                                                                                                     | 143  |

| 13   | Software recovery using recovery blocks                                                                                                   | 144  |

| 14   | Stepper motor controlled regulator                                                                                                        | 145  |

| 15   | Solenoid controlled regulator                                                                                                             | 145  |

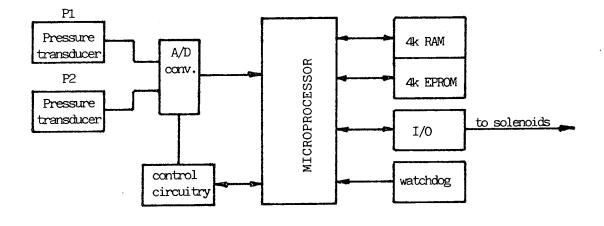

| 16   | Block diagram of non fault-tolerant controller                                                                                            | 146  |

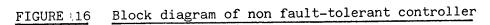

| 17   | Op-code fetch timing showing synchronisation problem                                                                                      | 146  |

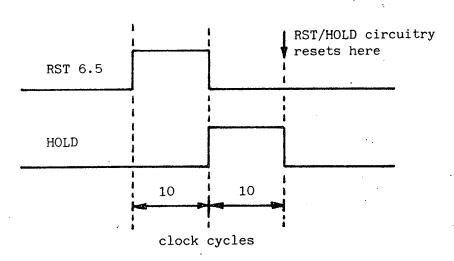

| 18   | RST/HOLD timing                                                                                                                           | 146  |

| 19   | Photograph of Governor Controller                                                                                                         | 147  |

| 20   | Photograph of pneumatic test rig                                                                                                          | 147  |

| 21   | Block diagram of microprocessor board                                                                                                     | 148  |

| 22   | Microprocessor and buffers - CHANNEL 1                                                                                                    | 149  |

| 23   | Microprocessor and buffers - CHANNEL 2                                                                                                    | 150  |

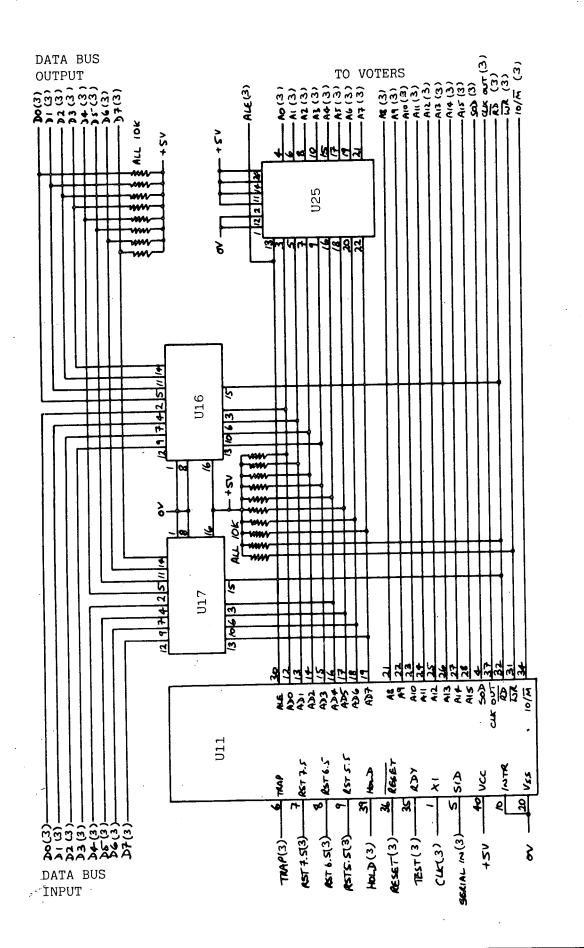

| 24   | Microprocessor and buffers - CHANNEL 3                                                                                                    | 151  |

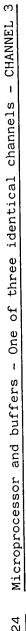

| 25   | Voting circuitry                                                                                                                          | 152  |

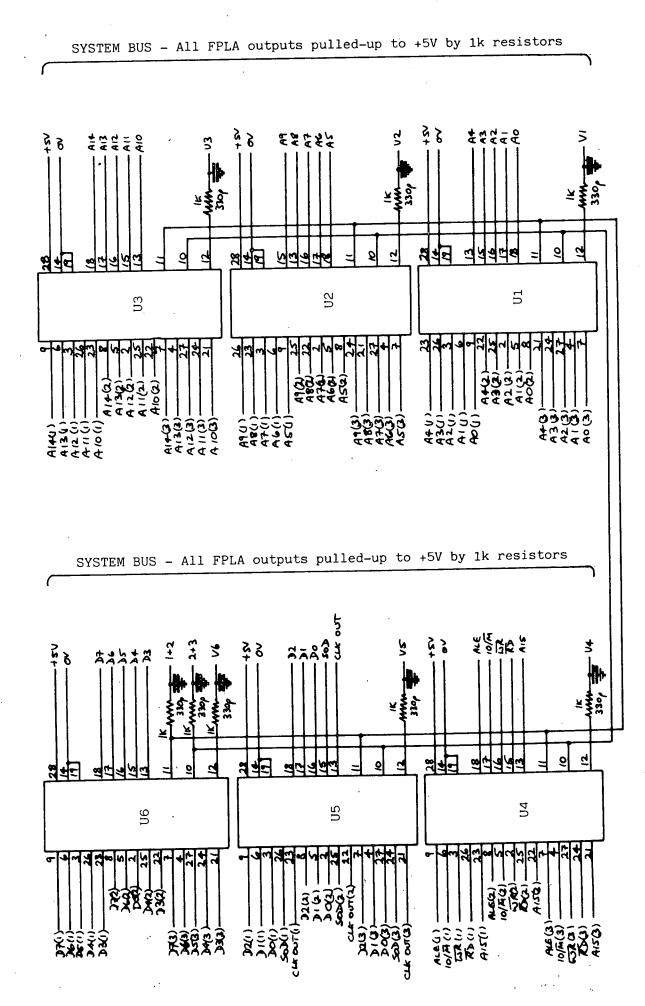

| 26   | FPLA error signal showing the effect of filtering                                                                                         | 153  |

ĥ

| , · |    |                                                                     |     |

|-----|----|---------------------------------------------------------------------|-----|

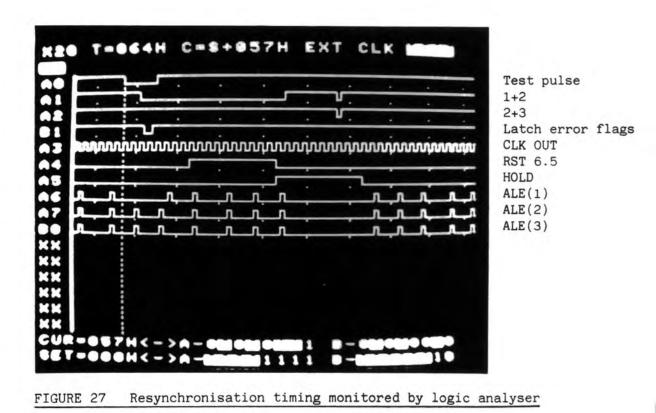

|     | 27 | Resynchronisation timing monitored by logic analyser                | 153 |

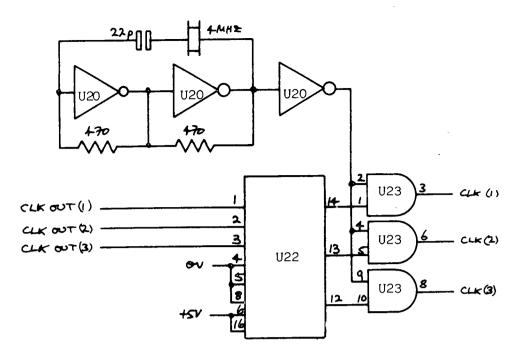

|     | 28 | Clock, Test, and RS232 interface                                    | 154 |

| `   | 29 | Resynchronisation circuitry                                         | 155 |

|     | 30 | Watchdogs and reset circuitry                                       | 156 |

|     | 31 | Block diagram of memory board                                       | 157 |

|     | 32 | Part of memory board including RAM and decoders                     | 158 |

|     | 33 | Detail of RAM storage circuitry including test circuitry            | 159 |

|     | 34 | Instant ROM, EPROM, and PORT(RD) decoder circuit diagram            | 160 |

|     | 35 | Block diagram of input/output board                                 | 161 |

|     | 36 | Input/output board                                                  | 162 |

|     | 37 | Stepper motor and redundant solenoid drive circuitry                | 163 |

|     | 38 | Pressure transducer and conditioning circuitry                      | 164 |

|     | 39 | Block diagram of pneumatic test rig                                 | 165 |

|     | 40 | Flow chart of module MAIN                                           | 166 |

|     | 41 | Flow chart of module RESYNC                                         | 167 |

|     | 42 | Flow chart of module MERROR                                         | 168 |

|     | 43 | Flow chart of module MERROR (continued)                             | 169 |

|     | 44 | Flow chart of module CNTRL                                          | 170 |

|     | 45 | Flow chart of module PRESSR                                         | 171 |

|     | 46 | Graph of governor outlet pressure versus orifice plate differential | 172 |

|     | 47 | Error messages                                                      | 173 |

\*

# LIST OF TABLES

|   | Tabl | <u>e</u>                                                         | Page |

|---|------|------------------------------------------------------------------|------|

|   | 1    | Failure mechanisms and activation energies in MOS semiconductors | 174  |

|   | 2    | A comparison of resistor failure rates                           | 174  |

| • | 3    | A comparison of capacitor failure rates                          | 175  |

|   | 4    | A comparison of soldered joints failure rates                    | 175  |

|   | 5    | A comparison of wire-wrap joint failure rates                    | 175  |

|   | 6    | A comparison of edge connector failure rates                     | 176  |

|   | 7    | Activation energies used in failure rate prediction              | 176  |

|   | 8    | A comparison of TTL integrated circuit failure rates             | 177  |

|   | 9    | A comparison of the failure rates for a 6800 microprocessor      | 177  |

|   | 10   | A comparison of 6800 microprocessor adjusted failure rates       | 178  |

|   | 11   | A comparison of the failure rates for a 8080 microprocessor      | 178  |

|   | 12   | A comparison of 8080 microprocessor adjusted failure rates       | 179  |

|   | 13   | A comparison of the failure rates of a 2716 EPROM                | 179  |

|   | 14   | A comparison of the failure rates of a 1k Bipolar ROM            | 180  |

|   | 15   | A comparison of the failure rates of a 16k Dynamic RAM           | 180  |

|   | 16   | A comparison of the failure rates of a 1k Static RAM             | 181  |

|   | 17   | The relation between cost, screening level, and Quality factor   | 181  |

|   | 18   | Recommended maximum junction temperatures for semiconductors     | 182  |

|   | 19   | Signals carried by back-plane bus                                | 183  |

|   | 20   | Correction bits for SEC/DED Hamming code                         | 184  |

|   | 21   | Error position as indicated by error flags                       | 184  |

|   |      |                                                                  |      |

$\Delta$

# List of Symbols

|   | ASCII                  | American Standard Code for Information Interchange                                                                      |

|---|------------------------|-------------------------------------------------------------------------------------------------------------------------|

|   | CMOS                   | Complementary Metal Oxide Semiconductor                                                                                 |

|   | DAG                    | Demand Activated Governing                                                                                              |

|   | DBE                    | Double Bit Error                                                                                                        |

| · | dil                    | aual in line                                                                                                            |

|   | ECL                    | Emitter coupled logic                                                                                                   |

|   | EEC                    | European Economic Community                                                                                             |

|   | EMP                    | Electromagnetic Pulse                                                                                                   |

|   | EPROM<br>FMEA<br>FMECA | Erasable Programmable Read Only Memory<br>Fault Acode and Effect Analysis<br>Fault Mode and Effect Criticality Analysis |

|   | FPLA                   | Field Programmable Logic Array                                                                                          |

|   | FTA                    | Fault Tree Analysis                                                                                                     |

|   | f/M hrs<br>ICE<br>À    | failures per million hours<br>In Circuit Enulation<br>failure rate                                                      |

|   | LSI                    | Large Scale Integration                                                                                                 |

|   | LSTTL                  | Low Power Shottky Transistor Transistor Logic                                                                           |

|   | MOS                    | Metal Oxide Semiconductor                                                                                               |

| • | MTBF                   | Mean Time Between Failures                                                                                              |

|   | MTFF                   | Mean Time to First Failure                                                                                              |

|   | MTTF                   | Mean Time To Failure                                                                                                    |

|   | MTTFIF                 | Mean Time To Failure Improvement Factor                                                                                 |

|   | MTTR                   | Mean Time To Repair                                                                                                     |

|   | NASA                   | North American Space Administration                                                                                     |

|   | POR                    | Power On Reset                                                                                                          |

|   | PROM                   | Programmable Read Only Memory                                                                                           |

|   | psi                    | pounds per square inch                                                                                                  |

|   | RAM                    | Random Access Memory                                                                                                    |

|   | rh                     | relative humidity                                                                                                       |

|   |                        |                                                                                                                         |

đ.,

ROM Read Only Memory

RTC Real Time Clock

SEC/DED Single Bit Error Correction / Double Bit Error Detection

SSI Small Scale Integration

STTL Shottky Transistor Transistor Logic

THB Temperature Humidity Bias

TMR Triple Modular Redundancy

TTL Transistor Transistor Logic

UART Universal Asynchronous Receiver Transmitter

VDU Visual Display Unit

VLSI Very Large Scale Integration

"wg inches water guage

#### CHAPTER 1

# THE NEED FOR A RELIABLE CONTROLLER

#### 1.1 NATIONAL GAS NETWORK

in the days before the extraction of natural gas, gas was produced, stored, transmitted, and used locally. Gas was transmitted at low pressure and there was no national network which made the control problem much easier.

The changeover to natural gas involved the installation of a national network. Gas comes ashore from several gas fields at high pressure and is transmitted throughout the country at high pressure, typically at 1000 psi in four foot diameter pipes. Compressor stations are used at regular intervals to overcome pressure drops in the system. Because of the extremely large volume of gas being controlled at high pressure and the absolute need for reliable control, considerable expenditure on fault tolerant main frame and mini-computers for control purposes can be justified.

Gas is progressively reduced in pressure as it is transmitted to the consumer. Transmission pressures range from 1000psi to 100psi and control of gas at the bottom end of this range is performed by pneumatics. In order to make full use of the gas network, the technique of line-pack has been developed, where the pipework itself is used to store large quantities of gas in order to smooth out variations in demand. To optimise the efficiency of techniques such as line-pack, it is necessary to replace controllers. These electronic digital controllers with pneumatic controllers must be extremely reliable because of the requirement for safe operation of the network, and failure to supply gas could involve British Gas in litigation resulting in the payment of considerable compensation. achieve the levels of reliability required Fault tolerant controllers can

and many of the techniques described and demonstrated in the following chapters could be used. Although the cost of the controller must be considered more carefully at low pressures, sufficient savings can be made by the more efficient operation of the network to justify such controllers.

tinally reaches the "distribution" network at relatively low Gas pressures where there are several thousand governor stations. The quantity of gas handled by each governor is much less than at higher pressures and all control is performed in pneumatics. A large governor station might feed two thousand consumers. The cost of electronic control at this level the controller must still be very reliable which critical. however is requires fault tolerant techniques to be used. It is this type of "small digital controller", that has been studied in depth at Durham and a The controller developed is more powerful prototype controller developed. than that required for simple pressure/flow control of a single regulator and could be expanded to control line-pack as described above.

As well as experimenting with hybrid electronic/mechanical governors. British Gas are making increasing use of microprocessor equipment. Because of the requirement for high reliability when controlling gas, it is essential to consider the reliability of every piece of equipment and introduce fault tolerant techniques if necessary.

## 1.2 PNEUMATIC GOVERNORS

Since the aim of this research was to develop a "small digital controller" to be used as part of an electromechanical governor, it is necessary to study the characteristics of pneumatic governors so that the replacement is no worse than its predecessor in performance and cost.

The terms regulator and governor are virtually synonymous, but the term governor will be used to describe a system having an inlet and a controlled outlet. The term regulator will be used to describe the

- 2 -

individual regulator valves which comprise the system.

Pneumatic regulators have been used by British Gas for many years. They have many advantages, of which the major ones are listed below :

- (i) Tried and trusted For a mechanical device they are very reliable. This is partly due to their mature technology and the vast quantity produced.

- (ii) Inexpensive A typical regulator costs a few hundred pounds.

- (iii) They are self powered and need no mains supply.

- (iv) They can withstand some unusual operating conditions and transient surges.

- (v)

- Mechanically they are very rugged and will operate over a wide temperature range as long as they are prevented from freezing up.

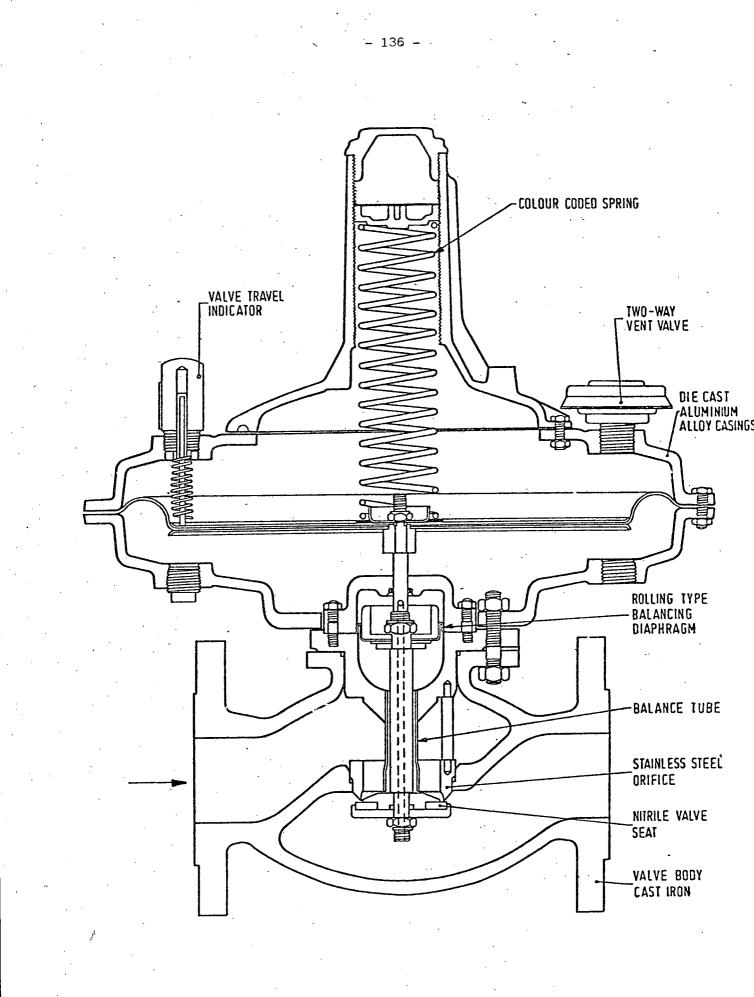

A typical regulator valve is shown in figure(1). The valve which controls the flow of gas is mounted within the lower cast iron body. The valve orifice is made from stainless steel to minimise wear and corrosion and the valve seat is made from nitrile rubber to ensure low leakage when The valve is attached to a long stem which passes up into the shut. diaphragm chamber and is attached to the centre of the diaphragm. Movement of the diaphragm causes the valve to open and shut. The diaphragm equilibrium position is reached by balancing the force of the spring on the top of the diaphragm with the gas pressure below. Downstream gas pressure is fed to the pressure tapping in the bottom diaphragm bowl which is shown If the downstream gas pressure rises, this to the right of figure(1). causes the diaphragm to move up which closes the valve and reduces the The regulator is thus seen to behave as a negative downstream pressure. feedback closed loop controller of pressure. The outlet pressure of the regulator is set by the main spring whose compression can be varied by adjusting the top screwed plug. The valve shown is an "open at rest" type and rupturing of the diaphragm will cause the valve to fail fully open.

#### 1.3 LIMITATIONS OF PNEUMATIC GOVERNORS

3.

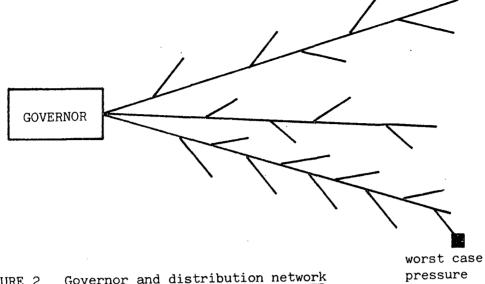

A schematic diagram of a governor feeding a distribution network is shown in figure(2). There will be some point in the network where the largest pressure drop exists between that point and the governor. This point is labelled the worst case pressure point. To complicate matters further, this point moves around as the loading on the network changes. There is a statutory minimum pressure (about 5 inches wg) at which consumers must be supplied, which means that the governor outlet pressure must always be high enough to give this minimum pressure at the worst case pressure point. All other consumers will receive gas at pressures above the statutory minimum.

It is desirable to keep the outlet pressure of the governor as low as possible whilst still satisfying the above conditions because of the problem of leakage. Old distribution pipework is subject to relatively low levels of nonhazardans leakage which is proportional to the network over-pressure. Under non worst case conditions and periods of low demand, there will be considerable over-pressure unless the governor is readjusted. It has been estimated by Murphyl231 that casedenable savings in the value of lost gas could be made for a 2"wg reduction in nationwide system pressure.

reduce network over-pressure by at least 2"wg.

As well as resistive pressure drops in the network there is a variable pressure drop across a simple pneumatic regulator. The outlet pressure of a typical regulator drops by 15 per cent as the flow through it is varied from zero to full rated – this is called "droop". Consequently the regulator set point must be set higher than required to compensate for droop at high flows. A microprocessor controlled valve could reduce the droop to zero.

It is necessary to set the governor outlet pressure higher than that

- 4 -

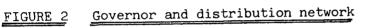

required in a "twin stream" governor. In large governor stations where it is imperative to supply gas without failure, it is common to use a twin stream regulator configuration as shown in figure(3). Siam shuts are similar to regulator valves, but are designed to close rapidly, cutting off Typical pressure the gas flow, when their set pressure is reached. settings are shown in figure(3). The minimum acceptable pressure at the governor outlet is 12"wg, so the standby regulator is set to give this. Normally the standby regulator is held off and the outlet pressure is controlled at 14"wg by the active stream regulator. If the outlet pressure rises above 18"wg, the active stream is cut off by the slam shut set at 18"wg and the standby stream takes over. If the pressure rises further to 20"wg, the standby stream is cut off by the slam shut set to 20"wg and gas It is difficult to set accurately flow through the governor is cut off. both regulators and slam shuts, so it is necessary to have their settings several inches wg apart so that they do not inter act with each other. lf all the valves and slam shuts were controlled by a microprocessor, then it would be possible to have their set points closer together.

To compensate for resistive pressure drops in the system, it is desirable to reduce the governor pressure under conditions of low flow and to increase the pressure under conditions of high flow. Such control is called "demand activated governing" (DAG). A pneumatic governor has been developed to perform this control function, but is very complex and requires many regulator valves and pneumatic components. If a multi-feed network is fed by several DAG controllers, then the controllers may interract and make the system unstable. To prevent this it is necessary for the controllers to communicate with each other so that interaction is controlled.

The previous discussion has shown that pneumatic regulators are satisfactory in their single form, but as soon as several are connected together to form a governor, penalties must be paid by way of complexity,

- 5 -

increased network leakage and inefficient control of the network. Most of the disadvantages of pneumatic governors can be overcome by using a pneumatic/electronic hybrid governor and such tasks as telemetry, health monitoring and complex control algorithms are made much easier to implement. It is however essential that the electronic controller is extremely reliable, especially in circumstances where the controller is controlling several valves. It is necessary to use fault tolerant techniques to achieve such a high level of reliability.

#### CHAPTER 2

#### A REVIEW OF OTHER FAULT-TOLERANT CONTROLLERS

#### 2.1 SMALL CONTROLLERS

The application of redundancy to small controllers is often more cost sensitive than large computers. Redundancy can be used to achieve non stop processing, tail safe operation, and a reduction in the mean time to repair (MTTR) by the use of built in diagnostics.

#### 2.1.1 TMR controllers

Platteter[7] describes a TMR design using three 8085 microprocessors which is similar to the experimental controller described in chapter eight. Platteter recommends the use of TMR for the protection against untestable Three different manufacturers' 8085s are used. errors in microprocessors. each having a different independent design. He proposes that it is better to accept that complex VLSI circuits such as microprocessors will contain untestable faults, and it is better to protect against this using TMR techniques, than to eliminate all manufacturing faults. The voting is performed at bus level in STTL integrated circuits which will be less reliable than voting in FPLAs. A very unsatisfactory approach is taken Either resynchronisation "just happens" or it towards resynchronisation. is aided by PUSHing all registers onto the stack and then POPing them off. He reports that sometimes the system would not resynchronise and it was necessary to perform a reset. The reasons for the system not synchronising and how this can be overcome is described in chapter eight.

8085 Higuchi et al [22] describe а TMR system using three This is microprocessors which is resynchronised at regular intervals. unecessary since it is better only to resynchronise when a voting error is Resynchronisation is performed by PUSHing all registers onto the detected. This will not always resynchronise the stack and then POPing them off.

program counter and sometimes one processor will be found to lock one clock cycle behind the other two as described in chapter eight. These difficulties are not reported. An alternative TMR configuration is proposed by Higuchi which uses software voting and the three processors execute tasks at staggered intervals and compare their results when all processors have executed the task. The software will be more complex and voting will not be transparent to the user, but the execution of tasks at different times should reduce the effect of transient errors.

Ryland [20] describes the use of microprocessors in reliable railway 6800 The interlocking system uses three signalling equipment. microprocessors in a TMR configuration. The processors are loosely synchronised and a processor will attempt to shut down any processor with If the assassination attempt fails, it which it disagrees (assassination). will shut itself down (suicide). Fault reporting and the repair of a faulty channel is performed on-line. Two separate data links are provided to the equipment and data is transmitted at 10k baud in Manchester code The software was written in assembler with Hamming code protection. because the designer felt that it was easier to achieve reliability because no arithmetic was used and the hardware interface was simple.

Davies et al [21] discuss ring communication structures for a small system. Three 8748 single chip microprocessors are connected in a TMR ring structure and the synchronisation is performed in software and is accomplished by handshaking between the processors or the insertion of a fixed delay before voting. The outputs from the three microprocessors must be combined which is nearly as complex as voting in hardware, but they propose that software voting offers greater versatility and is not prone to component failure.

#### 2.1.2 Fail safe controller

A life support system controller is described by Lim [4]. The design

- 8 -

is deliberately not fault-tolerant because of the increased cost. but is designed to detect hardware and software faults and to cause the system to fail safe. An alarm is given on failure of the controller so that human operation will ensure continued operation of the life support system.

#### 2.1.3 Built in test equipment

Foose [17] describes an industrial microprocessor controller which was designed to reduce the MTTR. The design aim was 80% automatic testability for 10% extra cost. The controller is divided into separate modules, each performing a single function, and modules are designed to test themselves. By reducing the MTTR the availability of the controller is increased and maintenance costs reduced. Failure diagnosis can also be performed by unskilled operators:

#### 2.2 LARGE COMPUTERS

The majority of research so far has been concentrated on large faulttolerant computers which are used in the space, avionics, and nuclear industries.

### 2.2.1 Space shuttle and avionics

The space shuttle is probably one of the best (and most expensive) References[12,13] describe the examples of a fault-tolerant system. digital processing subsystem. NASA decided to use standard proven avionics computers which nowadays are rather outdated and to implement the redundancy in software. Five identical IBM avionics 32 bit computers are used each having 250k bytes of memory. The computers share two 16M byte The computer contains built in test tape drives for mass storage. equipment and can detect 98% of errors. The computers are interconnected to themselves and to the sensors and actuators by serial buses. The loose highest reliability configuration consists of four computers in

- 9 -

background tasks. computer executing fifth synchronism with the Synchronism is achieved by hardware and software and two computers out of The inertial the four can fail without a catastrophic system failure. guidance platform is triplicated and connected to different buses. The inertial information undergoes selection filtering which compares the information channels and rejects any that are above a predetermined trip With all channels functional, mid-value selection is used which is level. common for inertial systems and failure of channels results in a degraded Failure of a channel must not cause a large transient selection algorithm. disturbance at the output of the selection filter, since a fault lasting only one second is enough under certain conditions to crash the shuttle.

The cycle time of the control process is 40ms in which time selection filtering and control of all the aerodynamic surfaces and rockets is performed. The cycle time of 40ms is necessary for the stability of the shuttle.

Ahern et al [14] describe a software voter/monitor for selection filtering of inertial guidance information. It is necessary to reject faulty channels and then to perform the vote. Mid-value selection is again chosen as the best algorithm and the requirement to smoothe the switch-over from one selection algorithm to another is stressed to avoid transient disturbances.

Modern military aircraft are controlled by the fly-by-wire technique. A digital flight computer reads in inertial and pilot information and controls electromechanical actuators which are connected to the control surfaces. Mechanical and hydraulic linkages are replaced, but it is necessary to use redundancy techniques to achieve high reliability in the controller. An added advantage in military aircraft is the increased survivability of the plane if it is damaged. For obvious reasons nothing has been published about modern use of microprocessors in digital flight controllers, but it is known that several different types of microprocessor including the Texas 9900 and Motorola 6800 are used in redundant configurations in the Tornado. Deets et al [15], in discussing the design and flight experience of a fly-by-wire control system, describe the first aircraft to use the fly-by-wire technique. An Apollo space computer was installed in a modified F8 fighter. The 16 bit computer had a 36k word memory, 12µs instruction cycle and performed the control algorithm in 30ms. The initial tests were successful and were conducted with a parallel back up hydraulic system.

Black et al [5] discuss the development of a spaceborne memory, which uses a memory error correction code, having the same number of bits as the SEC/DED Hamming code, but which is able to correct double bit errors (DBE). The position of stuck single bit errors is logged so that if a double bit error occurs, the stuck single bit error can be "erased" since its position is known, and a DBE tolerated. In order to achieve the high reliability required in space applications using semiconductor random access memory (RAM) the design was required to tolerate double bit errors.

#### 2.2.2 Commercial computers

Commercial computers are now being built with redundant circuitry. especially for memory protection. The aim is to increase the mean time to failure (MTTF) by redundant circuitry and to reduce the MTTR by built in test equipment. Hence the availability can be increased and maintenance Toschi et al[6], in discussing a fault-tolerant computer costs reduced. memory, describe the advantages gained by adding single bit error correction to memory and the tolerance of transient errors. Troublesome and failed memory devices are masked by redundancy and are replaced at Swarz [18] describes the design intervals. maintenance periodic methodology behind the VAX computer with special emphasis on the ability of the computer to tolerate memory, disk, and other errors. The computer is designed to minimise the MTTR by the use of a LSI 11 microprocessor

- 11 -

dedicated to diagnosing faults in the VAX computer. In this way the ... availability is improved and the maintenance costs reduced.

#### 2.2.3 Telephone exchange computers

Modern PCM telephone exchange computers must have a very high typically less than two hours down-time in forty vears. availability. Fantini et al [2] describe an exchange computer based on the Z8000 16 bit microprocessor which has a fault coverage of 0.98. A duplicate processor is used to detect errors by comparison with the main processor. The power supply, clock, and bus are continuously monitored for errors and RAM and ROM checking is performed off-line. The aim of the design is to detect and Most faults were found to be transient, but the system isolate faults. prompt repair of permanent faults to achieve a high relies on the availability.

Ceru et al [10] describe a similar exchange computer. The 16 bit processor is constructed from discrete TTL and LSTTL and consists of two processors operating in synchronism. The detection of an error causes both processors to check themselves and each other, and the first one to finish the checking resumes control of the exchange. Faults are logged and the second processor is resynchronised if possible.

#### 2.2.4 Safety monitoring computer

Harbert [3] describes a system using three 8086 16 bit microprocessors in a fire/gas detection and automatic shut-down controller. The input boards, microprocessor, memory, and output boards are triplicated and the processors operate asynchronously. Magnetic bubble storage is used since this gives improved reliability over spinning memory devices. Several hundred detectors are monitored by the system and their status displayed on colour VDUs, which give a clear display of information. The system controls emergency shut-down and extinguishing equipment.

#### 2.2.5 PDP 11 computer

Canepa et al [19], in discussing the architecture of multiprocessing systems, describe a system consisting of three LSI 11 computers connected a versatile triplex configuration. Hardware modification is minimal in except for the construction of the voters which use 250 SSI integrated Voting is performed at bus level which makes the redundancy circuits. transparent to the software, allowing standard software to be executed. The processors can be configured to operate singly, with one processor talking to the other two, or in a TMR configuration where the processors The system has been built to examine the effect of run in synchronism. By monitoring the three processor system transient faults on computers. and injecting faults into one channel, they hope to gain information about the frequency, duration and location of transient faults in a computer.

#### 2.2.6 Railway applications

[16], discussing reliable train control Forsythe et al in applications, describe a system using three INS8900 16 bit microprocessors which share a common bus. Each processor has its own memory store and both processors and memory are buffered to improve the fault isolation. The three processors share common RAM and EPROM and voting is performed in software to reduce the hardware costs. The operation of the controller is In the first three sectors, each processor divided into four sectors. executes a task and then swaps tasks with another processor at the end of the sector. In this way the three tasks are executed three times on three different microprocessors. In fourth sector the results of the the executed computations are compared and recovery is if required. Input/output is performed in the fourth sector only if the error checking is satisfactory. In spite of the high level of redundancy, the system was found to lock-up as a result of certain interference tests and the watchdog timer was found to reset the system and restore correct operation.

#### 2.2.7 Fault-tolerant software

Much of the fault-tolerance on large computers is implemented in References[8,9,11] describe the implementation of "recovery software. blocks" on a large machine in a high level language. A recovery block is defined as a section of code in which recovery is possible. Calculations undergo a series of acceptance tests. If the acceptance test is not passed Before executing an acceptance test. an alternative calculation is tried. variables are stored in a "recovery cache" so that the variables can be calculation the alternative and restored to their initial state if acceptance test fails. Ghani et al [11] describe the "recovery cache" hardware as implemented on a PDP 11 computer.

### 2.3 SUMMARY

Many of the fault-tolerant features reported in small controllers are used in the experimental controller. The designs of Platteter [7] and Higuchi et al [22] are similar to the governor controller which overcomes many of the shortcomings in their designs, such as the failure to Ryland [20] proposes a different TMR structure and reports resynchronise. The governor controller software that software was written in assembler. likewise written in assembler. Davies et al [21] discuss an was alternative TMR structure where the voting is performed in software. This structure is very suitable for single chip microprocessors, but was not used in the governor controller for the reasons given in chapters six and The controller described by Lim [4] is designed to fail safe as is seven. the governor controller. Foose [17] reports that built in testability can be incorporated at little extra cost and Ryland [20] mentions the on-line governor controller performs on-line fault reporting faults. The of reporting which allows the availability to be increased and maintenance costs reduced.

- 14 -

of small outside the definition large computers are Although is included for controllers, a discussion of fault-tolerant features the sake of completeness and many of their fault-tolerant features can be adapted for use on small microprocessor controllers. Much of their faulttolerance is implemented in software and is more complicated than that required for a small controller. The space shuttle uses serial buses for the interconnection of units since this is more reliable than using large The space shuttle and fly-by-wire aircraft use redundant parallel buses. inertial select the best used to software is and inertial sensors Mid-value selection is commonly used as it is a fast information. The governor controller, in a similar fashion, algorithm to implement. pressure redundant pressure trasnsducers and selects the best uses Time is not critical, so a more suitable information using software. averaging algorithm is used, rather than the faster mid-value selection.

References [5.6:18] describe the use of single bit error correction in semiconductor memory. Black et al [5] discuss a code which will correct double bit errors, but which uses the same number of bits as the more normal Hamming code. The experimental controller cannot correct double bit errors, but allows recovery from them, as well as transparently correcting single bit errors.

[2,10] describe similar telephone exchange computers References consisting of a main processor and a standby spare. This architecture could have been used in the governor controller, but a TMR structure was used in preference. Fantini et al [2] report that most faults experienced References [3,16] describe 16 bit TMR were of a transient nature. The governor controllers where the voting is performed in software. performs the voting in hardware which is transparent to the controller Canepa et al [19] describe a TMR system . using three PDP11 software. computers, where the voting is likewise performed in hardware. The complexity of hardware voting in large computers is highlighted by the size of the required voting circuitry.

Recovery blocks, as described in references [8,9,11], can usefully be implemented on small controllers. The governor controller uses a special type of recovery block, more properly called a recovery vector, which allows vectored recovery to be executed following the detection of a hardware or software error.

### CHAPTER 3

#### FAILURE OF COMPONENTS

## 3.1 FAILURE DISTRIBUTION AND MECHANISMS

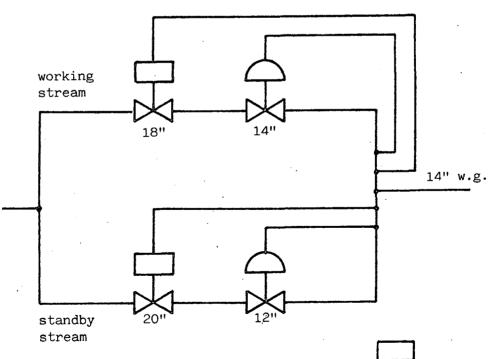

The failure rate of most types of electrical devices follows the classical "bath-tub" curve of figure(4). Phase one; infant mortality, represents the early life failures of a device and is usually associated with one or more manufacturing defects. After several hundred hours, the failure rate approaches some constant low value, phase two, where it remains for anything from several years to several hundred years and failures occur randomly. Wearout failures, phase three, occur at the end of the useful life of a device and are characterised by a rapidly rising failure rate with time as the device wears out both physically and A common wearout mechanism in integrated circuits is electrically. corrosion due to moisture trapped inside the device package. Under normal operating conditions, failure due to wearout is rarely experienced with integrated circuits, unless they are operated for a very long period of time - references[34.27].

The constant failure rate region, phase two, represents failures due to random events such as electrical surges. Most failure rate data sources assume a constant failure rate and present their results in the form of n unit time, typically n failures/10<sup>6</sup> hours. This is failures per satisfactory as long as the wearout region is not encountered during the assumption is likely for integrated lifetime of the equipment. This circuits and resistors, but components such as electrolytic capacitors may The wearout phase of an electrolytic capacitor results from be different. the electrolyte drying up, which might occur after only a few years. However the quoted "constant" failure rate might suggest a MTTF of several hundred years. Thus it is essential to distinguish between the useful life of a component and MTTF if wearout is encountered.

An example of the misleading result that this confusion might produce can be given by considering the human life span. The mortality rate for humans approximately follows the "bath-tub" curve, but if only the constant "failure rate" experienced during youth and middle-age is considered, then a MTTF of two thousand years is predicted as opposed to a normal lifespan of about seventy five years.

The majority of components used in "small digital controllers" are integrated circuits, resistors, and small decoupling capacitors. It is therefore valid under favourable operating conditions to consider the failure rate of such components constant and to assume that their useful life is equivalent to the MTTF.

Failure mechanisms in MOS integrated circuits are given in table(1) and are discussed in more detail in references[27,35]. Most potential failures caused by these mechanisms can be detected early by suitable screening. Consideration of these mechanisms is important since the majority of microprocessor and memory components are fabricated using the MOS technology.

#### 3.2 FAILURE RATE MEASUREMENT AND ACCELERATION

The simplest method of calculating the failure rate of devices under controlled or field testing is by the equation :

statistically it only The problem with this equation is that represents a point estimate at 50% confidence, and that if testing reveals no failures, then obviously the failure rate is not zero. А statistical solution to this problem is given by the Chi-squared distribution as discussed in references[32,49].

failure rate =

$$\frac{\chi^2 (1-c.L, 2r+2)}{2nt}$$

(3.2.1)

where:

$\chi^2$  = Chi-square function

CL= confidence level expressed as a decimal

r = number of failures

n = number of parts tested

t = total test duration

Tables of  $\chi^2$  are found in many texts on statistics[49].

Equation (3.2.1) is almost universally used, with most failure rates quoted at the 60% confidence level.

#### 3.2.1, Accelerated testing

Even "unreliable" microelectronic devices may last several thousand hours before failing which makes life-testing a very long process and screening virtually impossible. It has been shown that the failure rate of microelectronic devices exponentially increases with temperature according to the Arrhenius reaction rate equation, references[35,37,38].

tailure rate =

$$C \exp(-Ea/KT)$$

(3.2.2)

where:

Ea = activation energy in eV

$K = Boltzmanns constant (8.63 \times 10^{-5})$

T = absolute temperature

C = an appropriate constant

When conducting accelerated tests and analysing test data it is important to remember two things :

- 20 -

(i)

The failure rate is exponentially dependent on temperature so that incorrect specification of the device junction temperature will have a large effect on the failure rate.

(ii)

The correct activation energy should be chosen, appropriate to the failure mechanism under consideration.

According to the Arrhenius equation it is possible to accelerate significantly failures by testing at elevated temperatures and the acceleration factor is calculated by :

$$Fa = \exp\left[\frac{E_{A}}{K}\left(\frac{1}{T_{2}} - \frac{1}{T_{1}}\right)\right]$$

(3.2.3)

where : Fa = acceleration factor

T1 = test temperature of the junction

T2 = desired temperature of the junction

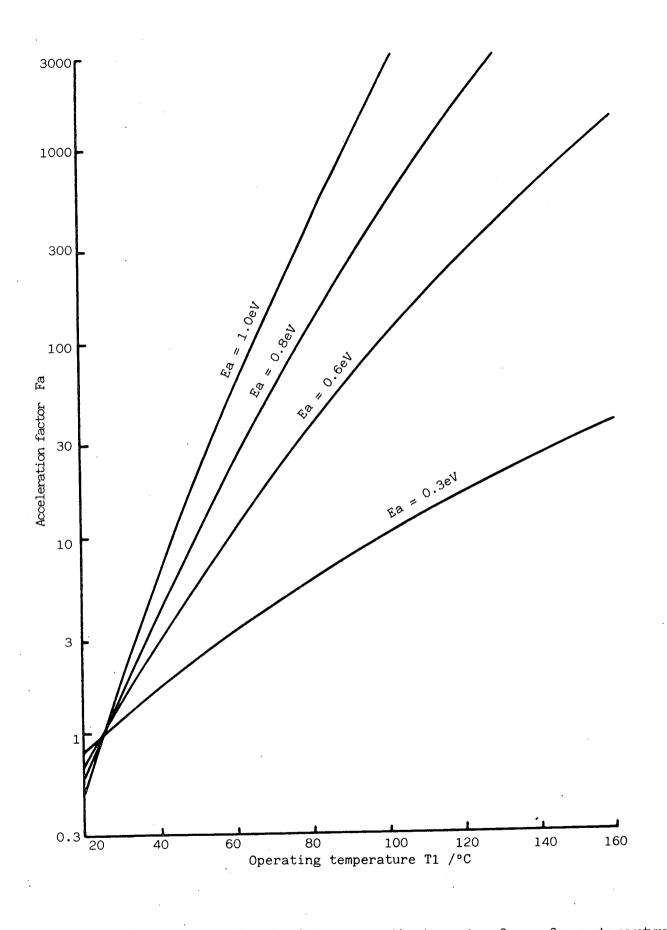

The graph of figure(7) shows the relationship between Fa and the test temperature. T1, for a desired temperature, T2, of 25°C. A family of the sensitivity of acceleration factor curves is plotted, showing to activation energy. Activation energies chosen are those corresponding to the major failure mechanisms of table(1).

When considering failures due to moisture ingression into the microcircuit package and subsequent corrosion of the metalisation and bonding wires, a similar acceleration factor may be used. It is common to test under conditions of 85° C/85%rh, references[39,43]. The acceleration factor may be calculated according to the Lawson-Harrison law, references [35,44] and is given by :

For

$$= \exp \left[\frac{E_{A}}{K}\left(\frac{1}{T_{2}}-\frac{1}{T_{i}}\right) + b(H_{i}^{2}-H_{2}^{2})\right]$$

(3.2.4)

where : Fa = acceleration factor

K = Boltzmanns constant

T1 = desired junction temperature

T2 = test junction temperature

H2 = test humidity

H1 = desired humidity

b = a constant

Reynolds[35] uses values of Ea = 0.6eV as per table(1) and b=4.4 .

# 3.3 FAILURE RATE PREDICTION

Failure rates may be predicted either by accelerated testing or a mathematical testing, and accelerated testing. field combination of The most widely used document for failure rate prediction is modelling. probably MIL-217 [37], prepared by the American Department of Defense at the Rome Air Development Centre (RADC). This document is regularly updated and has been published as MIL-217 A.B.C and recently D. The first to MIL-217B. microelectronic devices was the tailure rate of predict Components covered are those mainly used in defence applications, but this connectors. integrated circuits. capacitors. most resistors. covers switches etc. and field data is mainly gathered from defence applications. A mathematical failure rate is developed for each type of component of the form :

#### where :

$\lambda$  = failure rate

$\lambda_b$  = base failure rate

$\Pi_{\varphi}$  = quality factor

$\prod_{E}$  = environmental factor

$\prod_A$  = application factor - voltage stress, power rating etc.

The factors  $\lambda_{\rm b}$ .  $\Pi_{\varphi}$  ,  $\Pi_{\rm E}$  ,  $\Pi_{\rm A}$  etc. are tabulated in MIL-217 covering many operating conditions and grades of component.

The failure rate of components depends on their quality and the MIL-217 series attempts to allocate  $\prod_{p}$  or quality factors according to the grade of manufacture and subsequent screening.

An environment factor.  $\prod_{E}$ , is applied to take account of the operating environment of the component. Experience has shown that failure rates depend on the operating environment, as might be expected. For instance a missile launch is more hostile than an aircraft in flight which in turn is more hostile than a ground based environment. For the purpose of evaluation of industrial equipment, the environment chosen as being appropriate is "ground fixed", Gf.

Finally the application factor.  $\prod_A$  , is taken into account. This factor takes many forms, but is mainly used to reflect the electrical stress under which the component is operating. Any derating of the voltage, current, or power handled by the component will result in an improved value of  $\prod_A$ .

The failure rate model for MOS and bipolar devices is of particular interest since this covers TTL logic and most microprocessor and memory devices excluding ROMs. The model used is :

$\lambda = \Pi_{\varphi} \Pi_{L} \left[ \left( \prod_{T} \Pi_{V} + \left( \left( 2 + C_{3} \right) \right) \Pi_{E} \right] \right] \qquad \text{failures/10}^{6} \text{ hours} \qquad (3.3.2)$

where :  $\lambda$  = device tailure rate

$\prod_{\varphi}$  = quality factor - depends on grade and screening level  $\prod_{L}$  = device learning factor - unity for a mature device  $\prod_{T}$  = temperature acceleration factor - Arrhenius relation  $T_v$  = voltage stress factor - unity except for CMOS

C1 = device complexity factor - depends on transistor count

C2 = device complexity factor - depends on transistor count

C3 = package complexity factor

$TT_E$  = environment factor

Since  $\prod_{T}$  is exponentially dependent on temperature, then for high temperatures,  $\prod_{T}$  is large and the model can be simplified to the approximation :

$$\lambda = \prod_{\alpha} \prod_{\tau} \left( 1 \right)$$

(3.3.3)

The failure rate is therefore exponentially dependent on the junction temperature of the device.

#### 3.3.1 CNET

In 1972 the Comité de Coordination des Télécommunications in France decided to establish a group of people to evaluate and predict the reliability of components used in the telecommunications and computing industries. The first version of their report was published in 1976. reference(38). This report was based on MIL-217B (an earlier version of MIL-217D (37), but was biased towards telecommunication and computer equipment operating in favourable environments as opposed to defence equipment operating in hostile environments. Failure rate models are given which, are similar to MIL-217. The model given for microcircuits was considerably different, but was updated in 1982 to the following model which is more similar to the MIL-217 model.

$\lambda = \Pi_{\varphi} \Pi_{L} \left[ C_{1} \Pi_{T} \Pi_{t} \Pi_{v} + C_{2} \Pi_{\theta} \Pi_{\varepsilon} \Pi_{\varepsilon} \Pi_{s} \right]$

$\lambda$  = device failure rate

$\prod_{P}$  = quality factor - depends on grade and screening level

TTL = reliability growth factor - unity for a mature device

$TT_{t}$  = temperature acceleration factor – Arrhenius relation

$T_{T}$  = device technology factor

$TT_v$  = voltage stress factor - unity except for CMOS

C1 = device complexity factor - depends on transistor count

C2 = device complexity factor - depends on transistor count

Tre = environment factor

$T_{B}$  = humidity / temperature factor

$\Pi_s$  = transportation factor - depends on no. of journeys

# 3.3.2 National Centre of Systems Reliability

The NCSR reliability data [34] is a condensed version of their computer data bank held by the Systems Reliability Service, SRS. The data bank comprises two main parts. The first contains field data gathered from the nuclear industry where the environmental conditions are well known and controlled. The second part contains information from MIL-217C as well as data from other published sources. laboratory tests and theoretical predictions. Martin Marietta Aerospace provide much of the support for the RADC data which in turn influences the MIL-217 series. The SRS data bank contains this data, so the SRS data will not be an independent source to MIL-217.

The failure rate models are similar to MIL-217 with the exception of the microcircuit model, which is :

$F = K1 \text{ Kg} (Fe1 + Fe2 + Ft) \text{ failures/ } 10^6 \text{ hours}$  (3.3.5)

where : F = tailure rate for a hermetic device

K1 = unity for mature devices otherwise ten

Kg = reliability growth factor

Felr= transistor count complexity / environment factor

Fe2 = packaging factor - depends on no. of pins and environment

Ft = temperature accelerature factor dependent on packaging

The model only considers two grades of device, hermetic and non-hermetic. The non-hermetic device failure rate is equal to twice the hermetic failure rate as well as further adjustments incorporated into Ft.

# 3.3.3 RADC field data

As well as publishing the MIL-217 series, the RADC publishes failure rate data obtained from field experience. Klein [45] presents much field data on microcircuits which is shown to agree approximately with MIL-217C.

#### 3.3.4 European Space Agency

The ESA has its own data bank and requires companies wishing to tender for projects to perform a reliability prediction, using the failure rate data generated and supplied by themselves. This has the great advantage that all companies are forced to use the same failure rate data and a valid comparison between proposed designs can be made.

3.3.5 Manufacturers testing

Most microcircuit manufacturers publish the results of accelerated testing on their devices, references[27,40]. Devices are subjected to thermal and physical shock tests as well as dynamic testing at elevated temperatures. A large number of devices are tested for typically several thousand hours, and the number of failures observed are fitted to a Chi-squared distribution. The failure rate is typically quoted at the 60% confidence level and the failure rates are further modified according to

the Arrhenius acceleration factor, to give a failure rate appropriate to the likely conditions of usage. There is some discrepancy between different manufacturer's predictions, since they make use of different activation energies as applied to the Arrhenius acceleration equation. Tests are also performed to verify the suitability of device packages as regards shock and humidity as reported by Motorola [40].

# 3.3.6 Simple models

A simple model for microcircuits is quoted by the RRE which is useful when very tew parameters are known :

(3.3.6)

where :

$\lambda_{B} = 5$  digital bipolar

$\lambda_{B} = 8$  digital MOS

$\lambda_{B} = 12$  linear bipolar

$Kd = \frac{die area in square inches}{0.015}$

$$KI = 1 + \frac{N - 12}{24}$$

N = number of package leads

For this model to apply, the ambient temperature must not exceed  $55^{\circ}$ C, the junction temperature must not be greater than  $40^{\circ}$ C above ambient, and plastic encapsulation must not be used. If plastic encapsulation is used, then it is recommended that the failure rate is doubled.

# 3.3.7 GIDEP computer data base

The Government Industry Data Exchange Programme is an American based association which was established in 1959 and provides access to four data banks, which are :

(i) Engineering data bank

(ii) Reliability-maintainability data bank

(iii) Failure experience data bank

(iv) Metrology data bank

The reliability-maintainability data bank is of particular interest as regards reliability prediction.

# 3.3.8 EuReData

The European Reliability Data Bank Association was established in 1974 on a voluntary basis and was formally constituted in 1979. The organisation is non profit making and is supported by the EEC. Its main aims are to promote data exchange between organisations and to set up standard methods for obtaining and using reliability data.

#### 3.3.9 MIL-217 Data base

The failure rate models and factors contained in the MIL-217 series ideally lend themselves to computerisation, since mathematical formulae are given for all the failure rate factors.  $\Pi_{T}, \Pi_{P}$  etc. The Predictor package [81] includes the computerisation of MIL-217. The CNET data, likewise, is suitable, however data such as NCSR [34] is not suitable since no formulae are given for the failure rate factors, but only tables of figures.

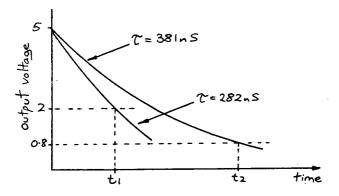

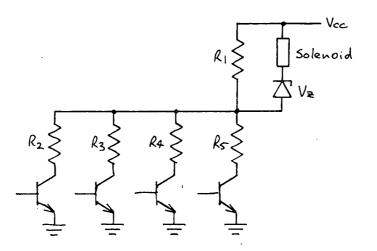

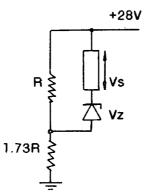

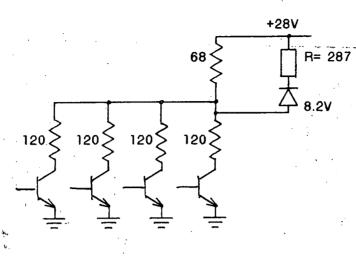

## 3.4 COMPARISON OF FAILURE RATE DATA