## **Durham E-Theses**

# $Amorphous\ silicon/langmuir-blodgett\ film\ mis\ devices$

Lloyd, J.P.

#### How to cite:

Lloyd, J.P. (1984) Amorphous silicon/langmuir-blodgett film mis devices, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/7122/

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

# AMORPHOUS SILICON/LANGMUIR-BLODGETT FILM MIS DEVICES

bу

J. P. LLOYD, B.Sc.

The copyright of this thesis rests with the author.

No quotation from it should be published without his prior written consent and information derived from it should be acknowledged.

A Thesis submitted for the Degree of Doctor of Philosophy in the University of Durham

March, 1984

19811 120

#### DECLARATION

I hereby declare that the work reported in this thesis has not previously been submitted for any degree, and is not being currently submitted in candidature for any other degree.

Signed J. P. Wayd

The work reported in this thesis was carried out by the candidate

Signed

Directors of Studies

Candidate

#### ABSTRACT

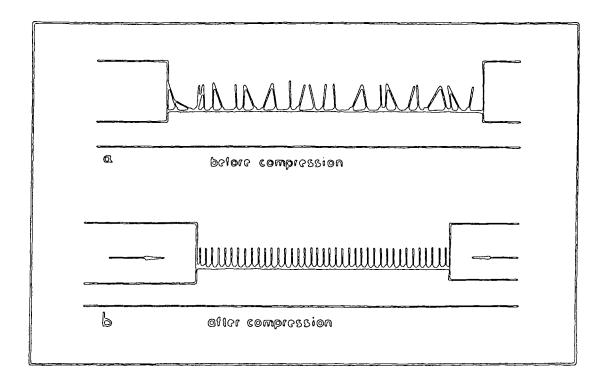

Metal-insulator-semiconductor (MIS) structures based on glow discharge produced, hydrogenated amorphous silicon (α-Si:H), and incorporating Langmuir-Blodgett (LB) film insulating layers, have been investigated. Two distinct types of MIS diode have been considered: tunnelling diodes (insulator thickness <5 nm) and non-tunnelling diodes (insulator thickness > 10 nm). A preliminary study of insulated-gate field-effect-transistors (igfet's) has also been undertaken.

Simple Schottky barrier (MS) structures, which are effectively a first step towards tunnelling MIS devices, have been made and characterised : results showed that these were 'state-of-the-art' devices. A preparation procedure has been developed which facilitates the successful deposition of LB film materials onto a-Si:H. Tunnelling MIS diodes containing diacetylene polymer LB insulating films have been fabricated, and capacitance measurements showed that the films were of reasonable quality. The current-voltage characteristics of these diodes were rather non-ideal and, it is thought, were dominated by the effects of two distinct levels of surface states. The appearance of peaks in the illuminated conductancevoltage curves supports this interpretation. Solar cells with an MIS structure can show an enhanced efficiency compared with MS (Schottky) cells. By using varying numbers of LB monolayers, the effects of increasing insulator thickness on a-Si:H solar cell parameters have been ascertained. Though the results closely parallel those of other researchers, the presence of a surface 'oxide' layer of  $\sim 4~\mathrm{nm}$ thickness (as a result of the pre-LB film deposition etch) prevented optimisation of the cell efficiency. Further work is necessary in order to capitalise on the effect which has been demonstrated e.g. the development of a more suitable etch treatment, the use of different LB film materials.

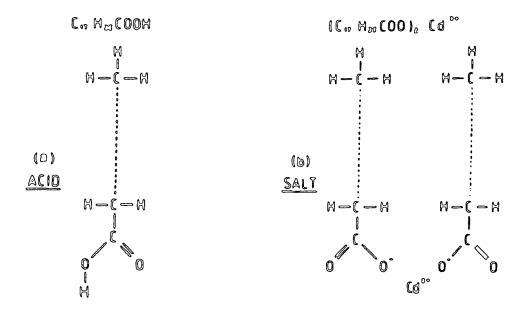

Non-tunnelling MIS diodes were made using cadmium stearate/stearic acid LB films. The capacitance-voltage curves were very similar to those which have been reported for conventional MIS devices on single crystal semiconductors. The LB films, although of slightly poorer structural quality than is possible on single crystal substrates, were nonetheless reproducible. An unusual ln J v  $v^{\frac{1}{2}}$  current-voltage dependence was found, which, it is suggested, was due to image-force effects. Large hysteresis was observed in the device characteristics due to polarisation or ionic motion. The characteristics were also influenced by the presence, in the upper half of the  $\alpha$ -Si:H mobility gap, of a band of surface or bulk states. These simple structures could possibly be used as gas detectors, since the penetration of a gas into the LB film may well result in measureable changes in the device parameters.

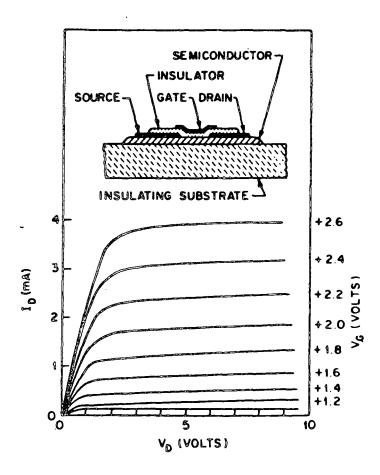

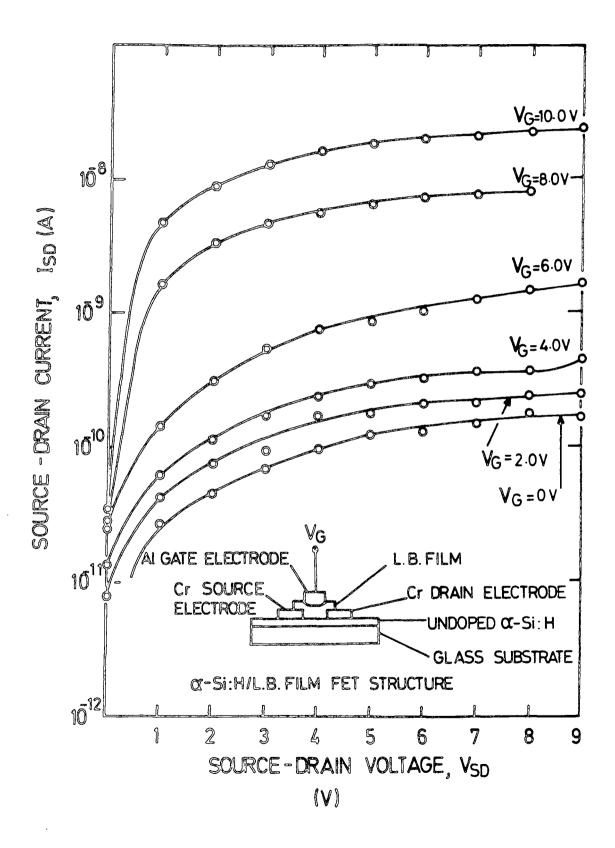

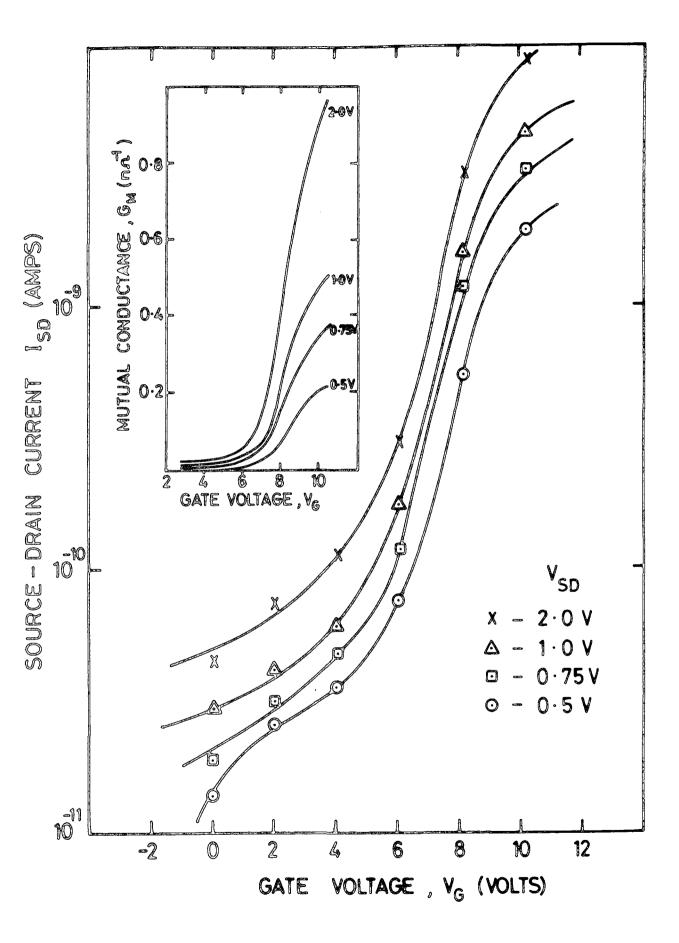

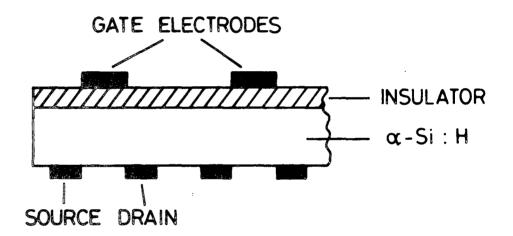

For the first time, an igfet based upon the  $\alpha$ -Si:H/LB film system has been produced. The device showed a change in source-drain current of almost three orders of magnitude for a gate voltage change of 10V. This compares well with the early results of other workers using more conventional insulators. It is thought that the device performance was limited by the poor semiconducting properties of the surface region of the  $\alpha$ -Si:H, and that an alternative FET configuration would lead to improvements. Possible applications include the switching of large area liquid crystal displays (using FET arrays) or, more tentatively, the exploitation of the 'molecular tailoring' qualities of LB films to produce specific biological and chemical FET sensors.

#### ACKNOWLEDGEMENTS

I would like to take this opportunity to thank the many friends and colleagues in the Department of Applied Physics and Electronics who have helped me during the course of this work. In particular I am grateful to Professor Gareth Roberts and Dr. Mike Petty for the time and effort they have given to encouraging and directing me in my research. I would also like to thank Dr. Graham Russell for taking the RHEED micrographs and for many helpful discussions, and Dr. Derek Skinner of Plessey Research (Caswell) Ltd. for his expert assistance with the Auger Electron Spectroscopy. The other members of the LB film group have made my time with them both interesting and enjoyable, and their helpfulness has been much appreciated, as has that of the Department technical staff headed by Mr. F. Spence. My thanks also go to Mrs. P. Morrell for her patience and proficiency in typing this thesis, and to Mr. N. Thompson for preparing the diagrams.

I gratefully acknowledge the financial support given to me by the SERC. I am also indebted to Plessey Research (Caswell) Ltd. for additional support, for the provision of samples and for the use of some of their facilities. Professor W. E. Spear and Dr. P. G. LeComber of the University of Dundee and Dr.R.Street of the Xerox Corporation provided the rest of my samples, for which I am very grateful.

I would like to thank my wife, Fran, for her patience, understanding and support throughout this work. I am greatly indebted to Peter Scott and Charles Newby for their invaluable encouragement, especially during the writing of this thesis. Finally I would like to thank my parents for their constant support, sacrifice and encouragement over the years.

### C O N T E N T S

|           | ·                                                                                                                                                                                                        | Page           |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| ABSTRACT  |                                                                                                                                                                                                          | (i)            |

| ACKNOWLE  | OGEMENTS                                                                                                                                                                                                 | (ii)           |

| CHAPTER 1 | : INTRODUCTION                                                                                                                                                                                           | 1              |

| CHAPTER 2 | : INTRODUCTION TO AMORPHOUS SILICON                                                                                                                                                                      |                |

| 2.1       | Introduction                                                                                                                                                                                             | 4              |

| 2.2       | Preparation of Amorphous Silicon                                                                                                                                                                         | 7              |

| 2.3       | The Structure of Amorphous Silicon                                                                                                                                                                       | 11             |

|           | 2.3.1 Methods of Structure Determination 2.3.2 Models of Structure 2.3.3 The Structure of $\alpha$ -Si                                                                                                   | 11<br>12<br>13 |

| 2.4       | The Electronic Structure of Amorphous Silicon                                                                                                                                                            | 15             |

|           | <ul> <li>2.4.1 Methods of Measuring the Gap Density of States</li> <li>2.4.2 Models of the Gap Density of States in Amorphous Semiconductors</li> <li>2.4.3 The Gap Density of States in α-Si</li> </ul> | 15<br>17<br>18 |

| 2.5       | The Electrical Properties of Amorphous Silicon                                                                                                                                                           | 21             |

| 2.6       | The Optical Properties of Amorphous Silicon                                                                                                                                                              | 25             |

| 2.7       | Applications of Amorphous Silicon                                                                                                                                                                        | 28             |

| CHAPTER 3 | : SCHOTTKY BARRIER AND TUNNELLING MIS THEORY                                                                                                                                                             |                |

| 3.1       | Introduction                                                                                                                                                                                             | 32             |

| 3.2       | The Theory of Schottky Barriers on Single<br>Crystal Semiconductors                                                                                                                                      | 32             |

|           | <ul><li>3.2.1 Barrier Parameters</li><li>3.2.2 Current Transport Mechanisms</li><li>3.2.3 Practical Diode Characteristics</li></ul>                                                                      | 32<br>35<br>39 |

|           |                                                                                                                                                                                                                                                                                                                      | Page                                   |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 3.3       | Schottky Barriers on Hydrogenated Amorphous<br>Silicon                                                                                                                                                                                                                                                               | 45                                     |

|           | 3.3.1 Current-Voltage Characteristics 3.3.2 Capacitance Characteristics 3.3.3 A Review of Theoretical Models                                                                                                                                                                                                         | 45<br>46<br>48                         |

| 3.4       | Conduction Processes in Insulating Films                                                                                                                                                                                                                                                                             | 53                                     |

| 3.5       | Theory of Tunnelling MIS Diodes                                                                                                                                                                                                                                                                                      | 58                                     |

| 3.6       | Solar Cells                                                                                                                                                                                                                                                                                                          | 63                                     |

|           | 3.6.1 Schottky Barrier Devices 3.6.2 MIS Solar Cells                                                                                                                                                                                                                                                                 | 63<br>65                               |

| CHAPTER 4 | : THICK INSULATOR MIS THEORY                                                                                                                                                                                                                                                                                         |                                        |

| 4.1       | Introduction                                                                                                                                                                                                                                                                                                         | 68                                     |

| 4.2       | The Ideal MIS Diode                                                                                                                                                                                                                                                                                                  | 68                                     |

| 4.3       | Causes of Deviation from Ideality                                                                                                                                                                                                                                                                                    | 74                                     |

|           | <ul> <li>4.3.1 Work Function Differences</li> <li>4.3.2 Surface States</li> <li>4.3.3 Surface Charge and Insulator Space Charge</li> <li>4.3.4 Temperature Changes</li> <li>4.3.5 Illumination</li> <li>4.3.6 Substrate Resistance</li> <li>4.3.7 Surface Leakage</li> <li>4.3.8 Amorphous Semiconductors</li> </ul> | 75<br>75<br>80<br>82<br>83<br>83<br>84 |

| 4.4       | Measurement of Surface State Density                                                                                                                                                                                                                                                                                 | 86                                     |

|           | 4.4.1 Capacitance Techniques 4.4.2 The Conductance Technique                                                                                                                                                                                                                                                         | 87<br>89                               |

| 4.5       | Field Effect Transistor Principles                                                                                                                                                                                                                                                                                   | 91                                     |

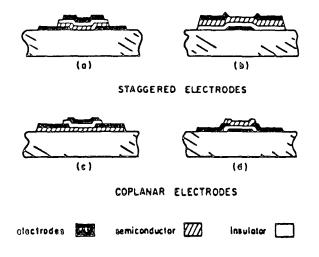

| 4.6       | Thin Film Transistors                                                                                                                                                                                                                                                                                                | 95                                     |

| CHAPTER 5 | : LANGMUIR-BLODGETT FILM TECHNOLOGY                                                                                                                                                                                                                                                                                  |                                        |

| 5.1       | Introduction                                                                                                                                                                                                                                                                                                         | 98                                     |

| 5.2       | Historical Background                                                                                                                                                                                                                                                                                                | 98                                     |

| 5.3       | Principles of Langmuir-Blodgett Film Deposition                                                                                                                                                                                                                                                                      | 99                                     |

| 5.4       | Deposition Equipment and Instrumentation                                                                                                                                                                                                                                                                             | 101                                    |

|           |                                                    | Page       |

|-----------|----------------------------------------------------|------------|

| 5.5       | Deposition Conditions                              | 102        |

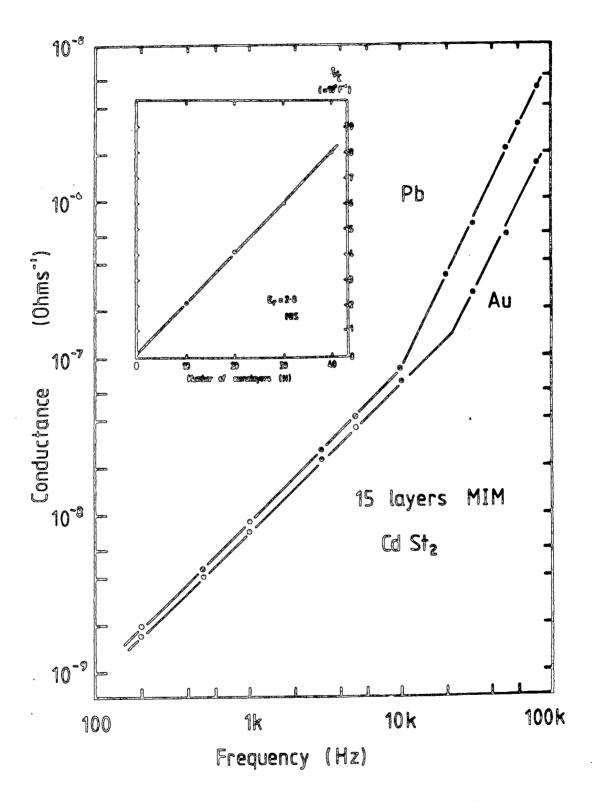

| 5.6       | Review of Electrical Properties                    | 103        |

|           | 5.6.1 D.C. Conduction                              | 103        |

|           | 5.6.2 A.C. Conductance                             | 106        |

|           | 5.6.3 A.C. Capacitance                             | 107        |

| 5.7       | LB Film Applications                               | 108        |

| CHAPTER 6 | S : EXPERIMENTAL TECHNIQUES AND DEVICE FABRICATION |            |

| 6.1       | Introduction                                       | 112        |

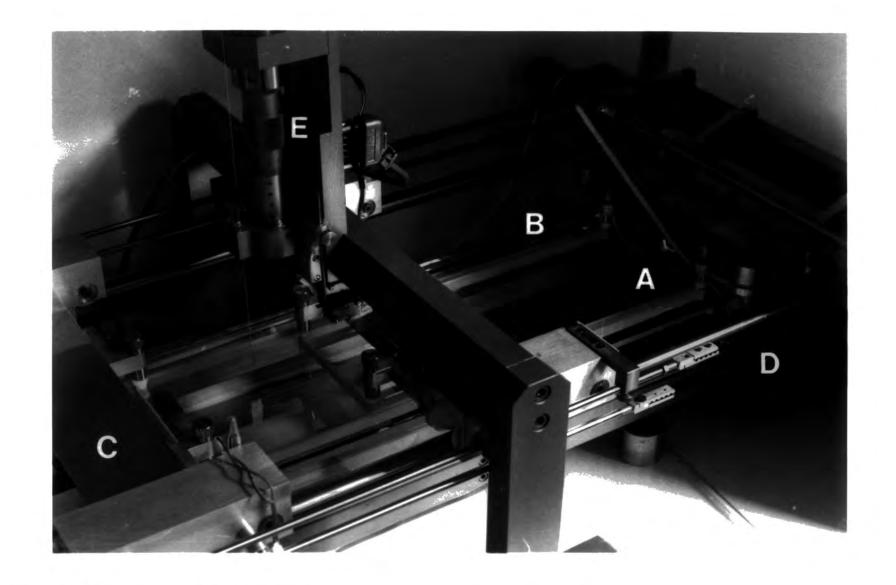

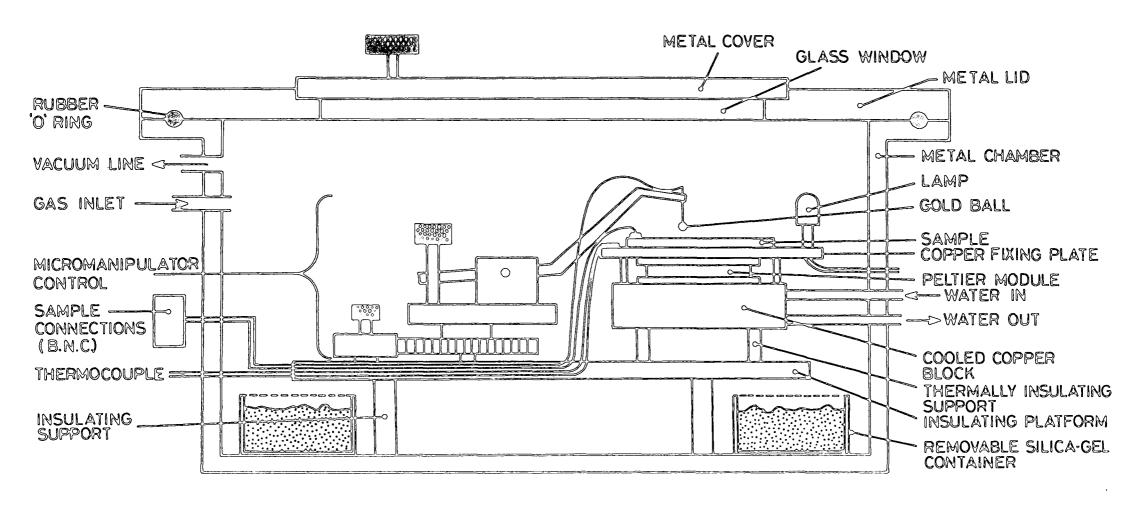

| 6.2       | Sample Chambers                                    | 112        |

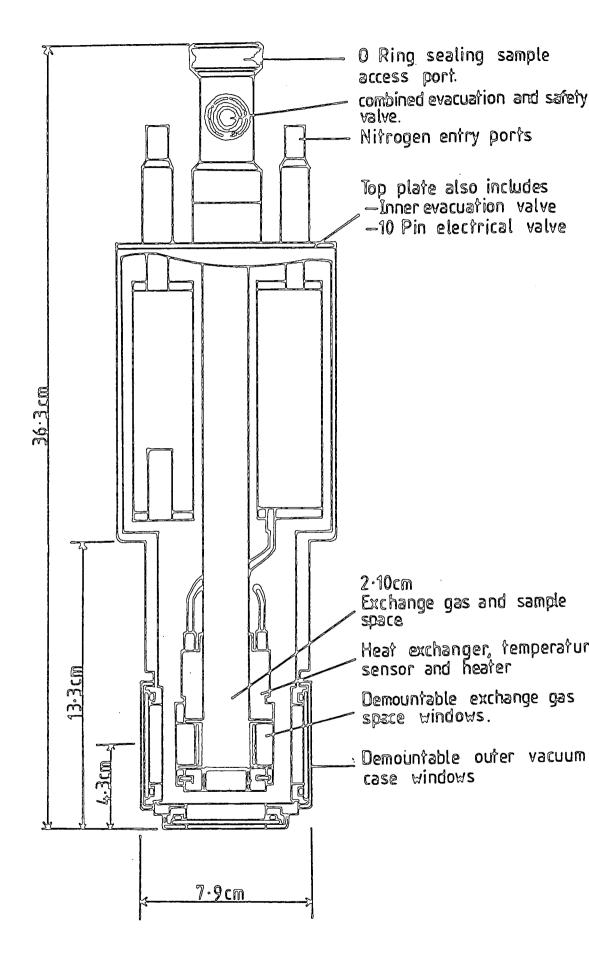

|           | 6.2.1 Custom Built Sample Chamber                  | 113        |

|           | 6.2.2 Exchange Gas Cryostat                        | 114        |

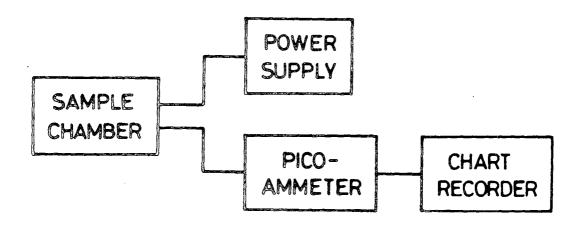

| 6.3       | D.C. Conductivity Measurements                     | 115        |

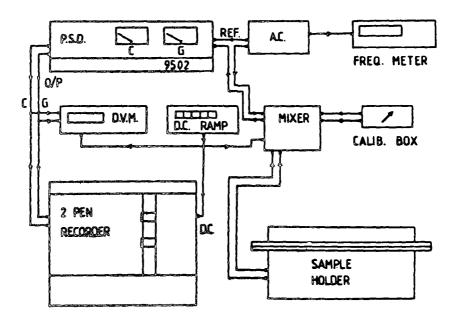

| 6.4       | Admittance Measurements                            | 115        |

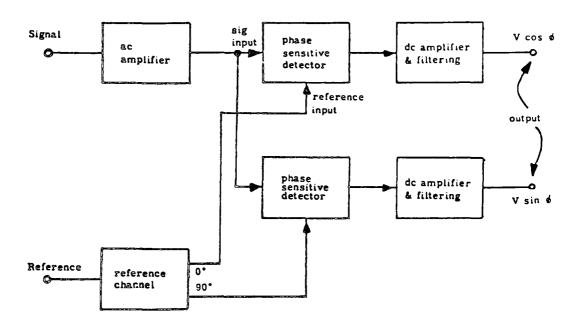

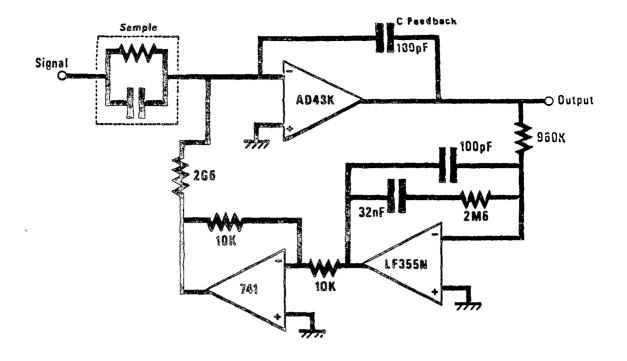

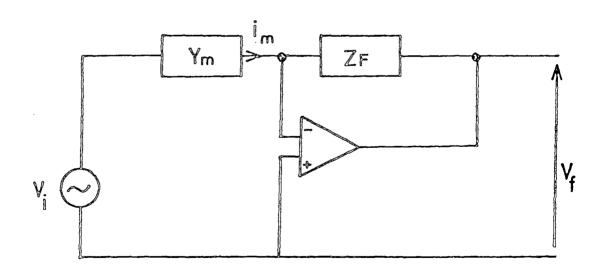

|           | 6.4.1 Phase Sensitive Detection System             | 115        |

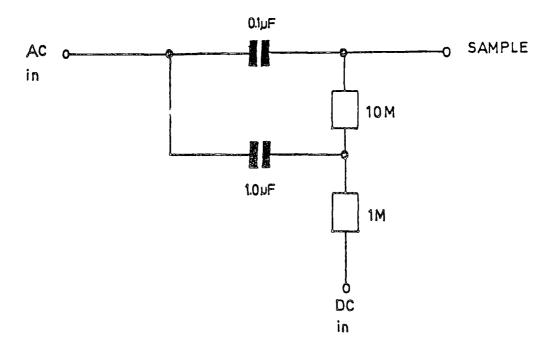

|           | 6.4.2 Input Circuitry and Signal Sources           | 117        |

|           | 6.4.3 Calibration Procedures                       | 120        |

|           | 6.4.4 Other Instrumentation                        | 120        |

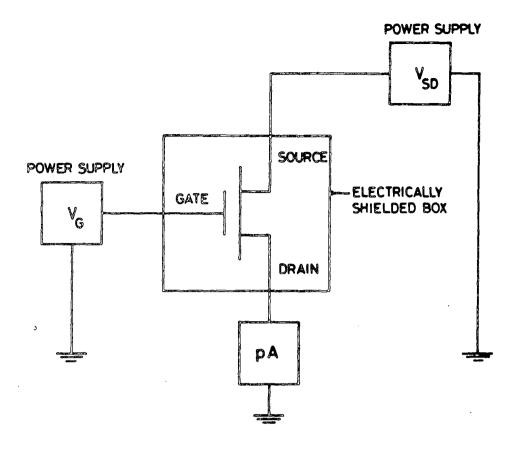

| 6.5       | Field Effect Transistor Measurements               | 121        |

| 6.6       | Auger Electron Spectroscopy                        | 121        |

| 6.7       | Reflection High Energy Electron Diffraction        |            |

| 6.8       | Device Fabrication                                 | 124        |

|           | 6.8.1 Substrate Preparation                        | 125        |

|           | 6.8.2 Substrate Treatment                          | 125        |

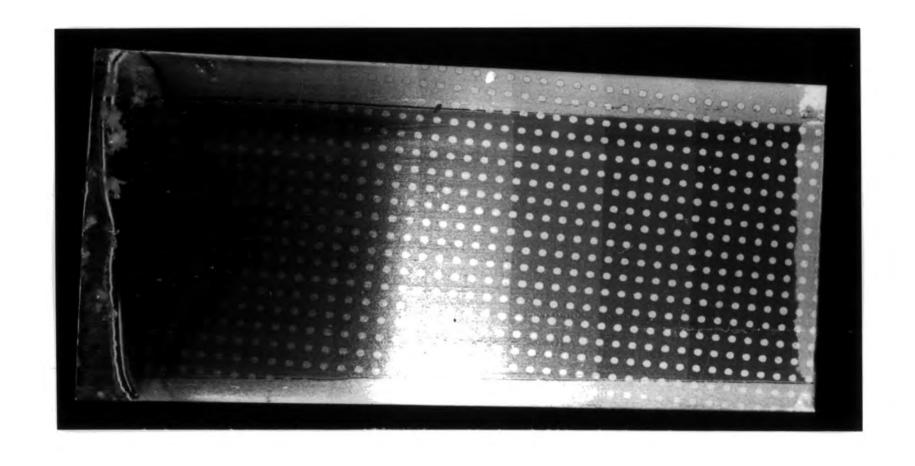

|           | 6.8.3 LB Film Quality                              | 131        |

|           | 6.8.4 Top Contact Evaporation                      | 133        |

| CHAPTER 7 | : SCHOTTKY BARRIER RESULTS                         |            |

| 7.1       | Introduction                                       | 136        |

| 7.2       | Schottky Barrier Contact Metals                    | 136        |

| 7.3       |                                                    | 137        |

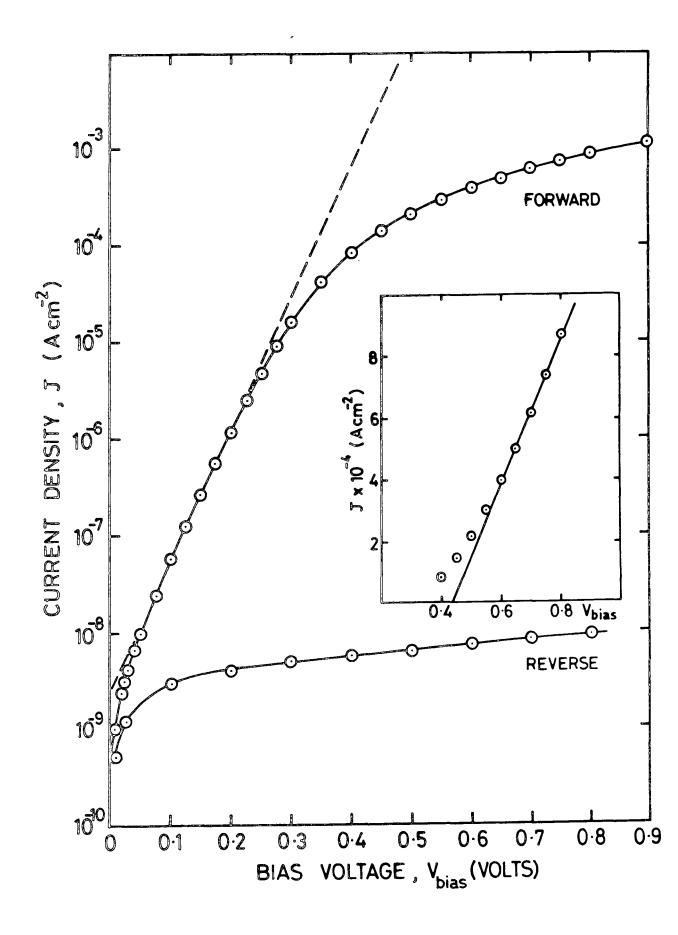

| 1.3       | Current-Voltage Characteristics                    |            |

|           | 7.3.1 Forward bias                                 | 138        |

| •         | 7.3.2 Reverse bias                                 | 141        |

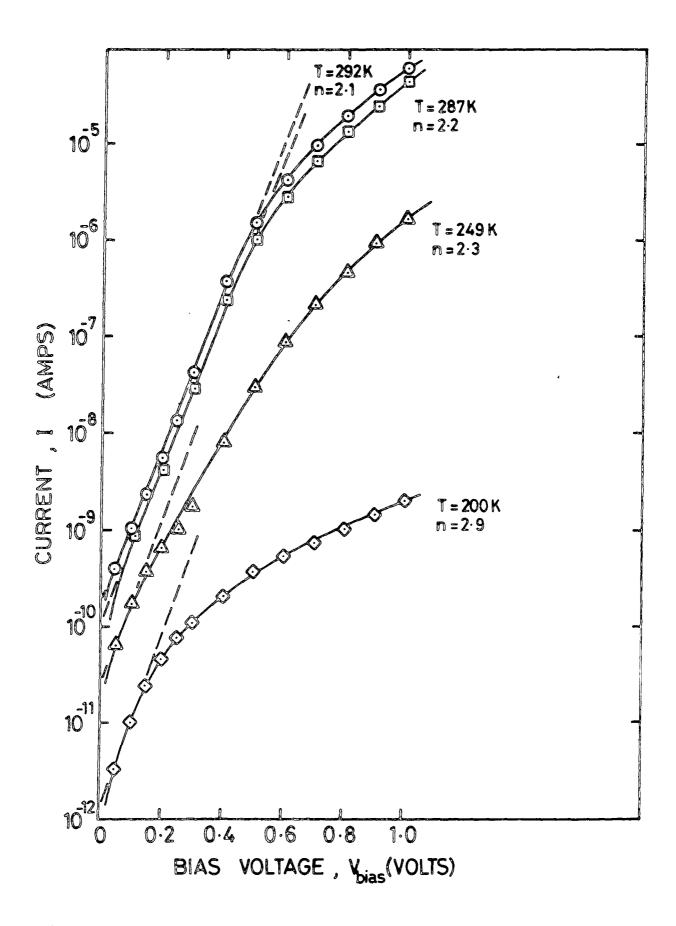

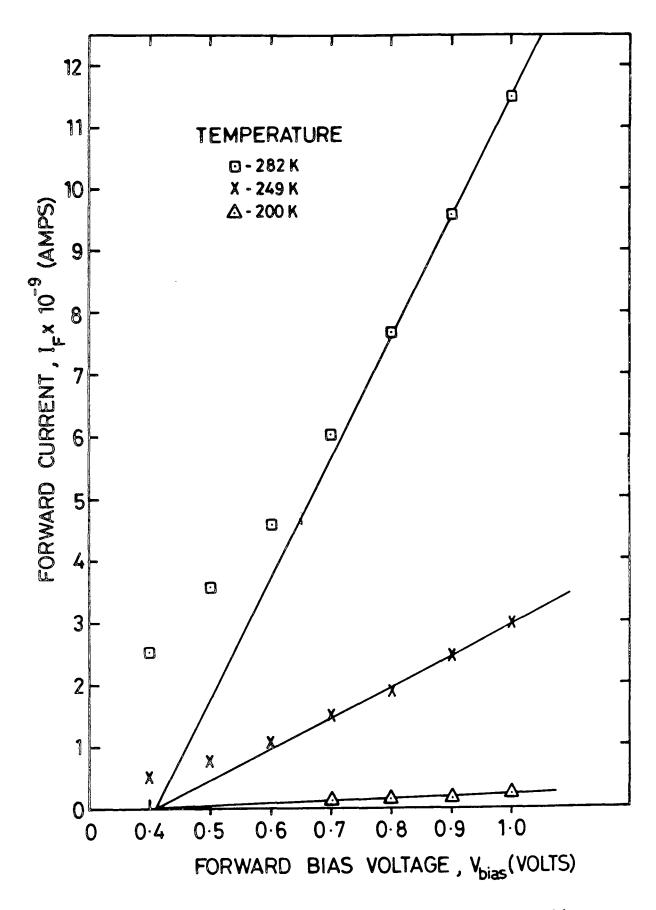

|           | 7.3.3 Temperature Dependence of Forward J-V        | 1/1        |

|           | Characteristics 7 3 4 Device Reproducibility       | 141<br>144 |

|           | , s a device Kebroducidilliv                       | 144        |

|                     |                                                                                                | Page              |

|---------------------|------------------------------------------------------------------------------------------------|-------------------|

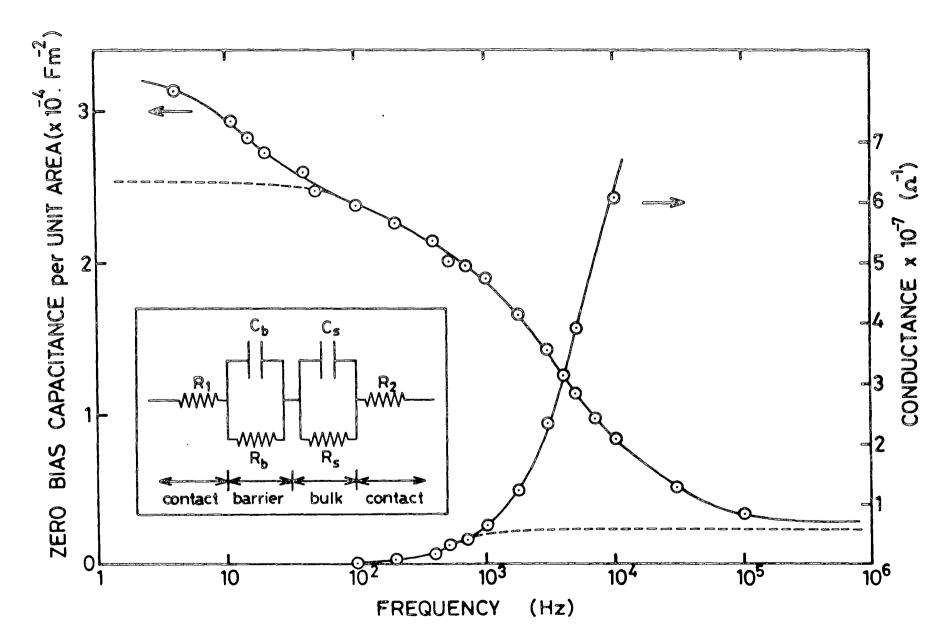

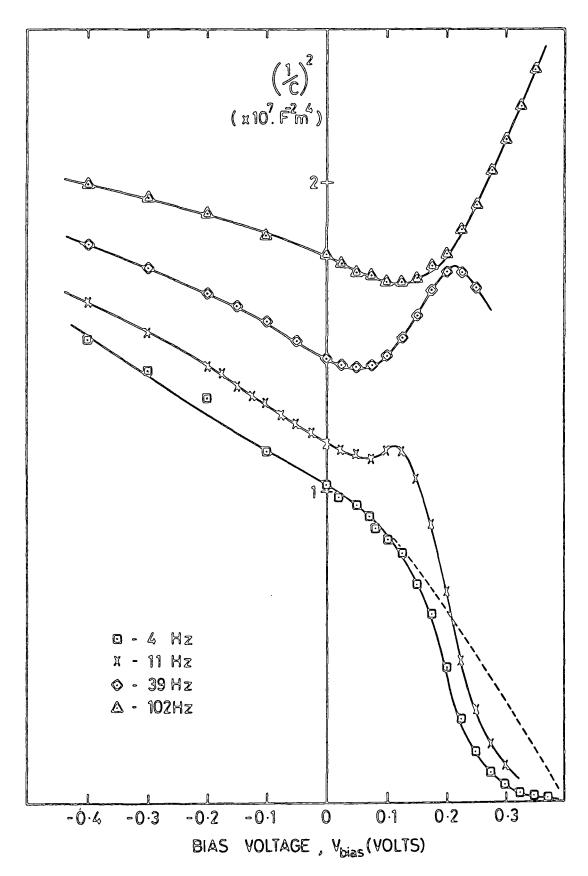

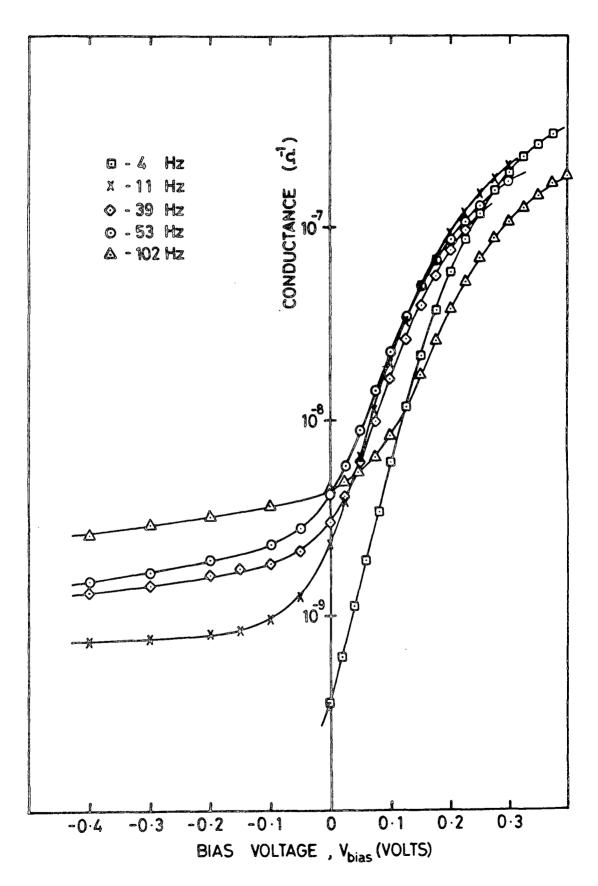

| 7.4 Capacita        | nce and Conductance Measurements                                                               | 145               |

| 7.4.2 T<br>7.4.3 D  | requency Effects<br>he Effect of Bias Voltage<br>iodes Made on α-Si:H from Different<br>ources | 145<br>150<br>155 |

| _                   | for Etched Semiconductor Substrates                                                            | 156               |

|                     | and Conclusions                                                                                | 158               |

| CHAPTER 8 : THIN I  | NSULATOR MIS RESULTS                                                                           |                   |

| 8.1 Introduc        | tion                                                                                           | 159               |

| 8.2 Practica        | l Details                                                                                      | 159               |

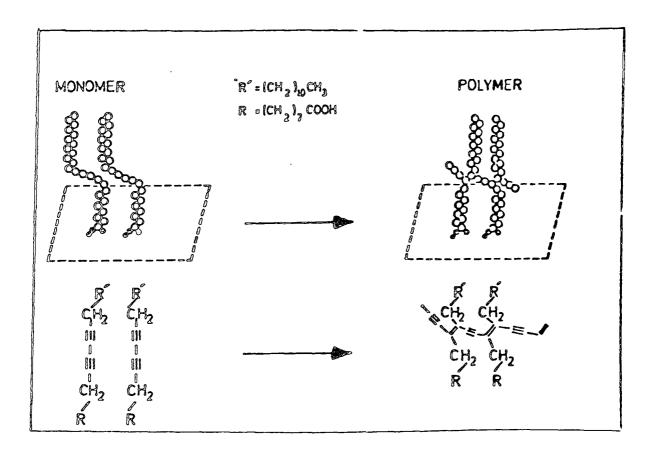

| 8.2.1 L             | B Film Materials                                                                               | 159               |

| 8.2.2 De            | evice Reproducibility                                                                          | 161               |

| 8.3 Capacita        | nce Measurements                                                                               | 161               |

|                     | apacitance-Voltage Data                                                                        | 162               |

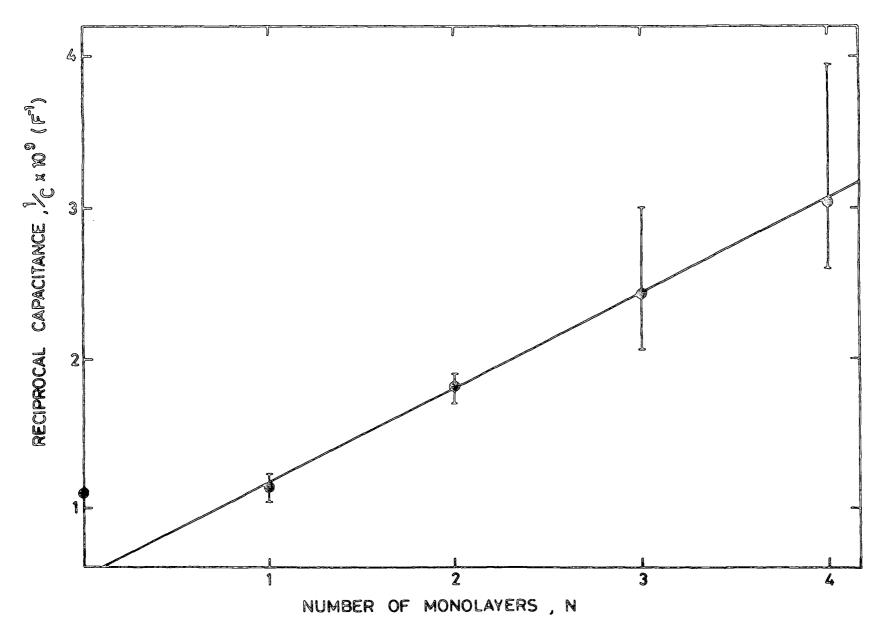

|                     | eciprocal Capacitance v LB Film<br>nickness                                                    | 164               |

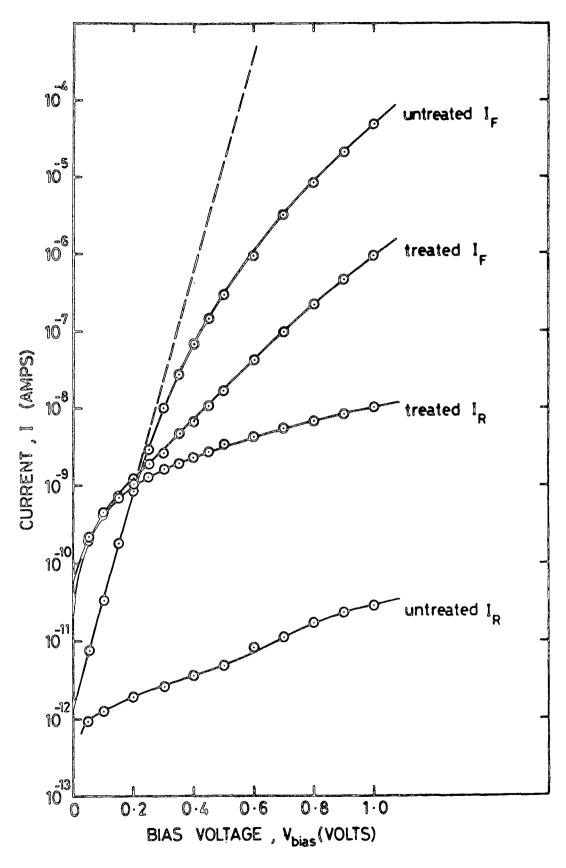

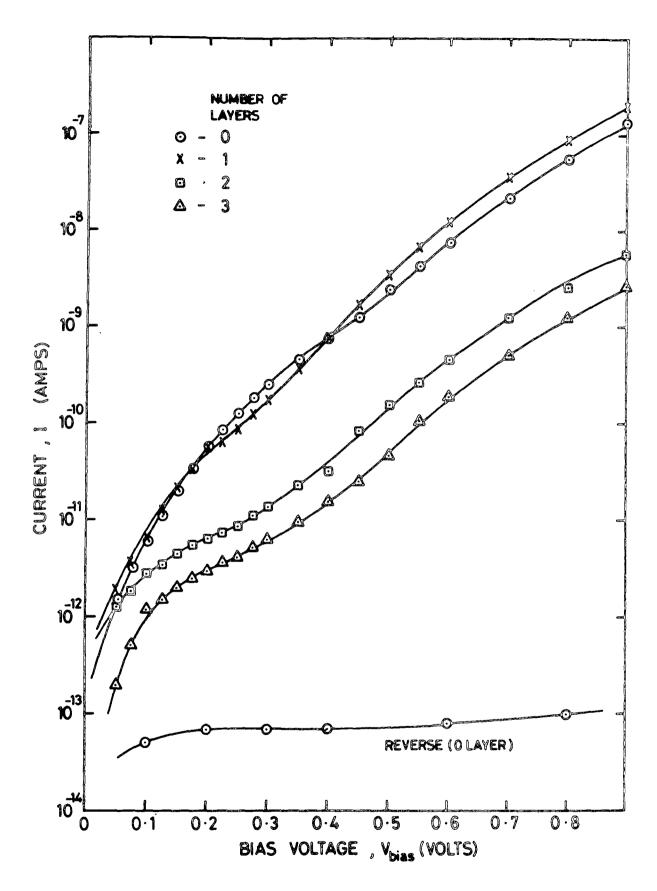

| 8.4 Current-N       | Voltage Measurements                                                                           | 166               |

|                     | orward Bias<br>everse Bias                                                                     | 166<br>167        |

| 8.4.3 Pc            | ossible Mechanisms to Explain Forward ias I-V Curves                                           | 168               |

|                     | ummary                                                                                         | 173               |

| 8.5 Light Inc       | duced Effects                                                                                  | 174               |

|                     | apacitance-Voltage Data<br>onductance-Voltage Data                                             | 174<br>175        |

|                     | -                                                                                              |                   |

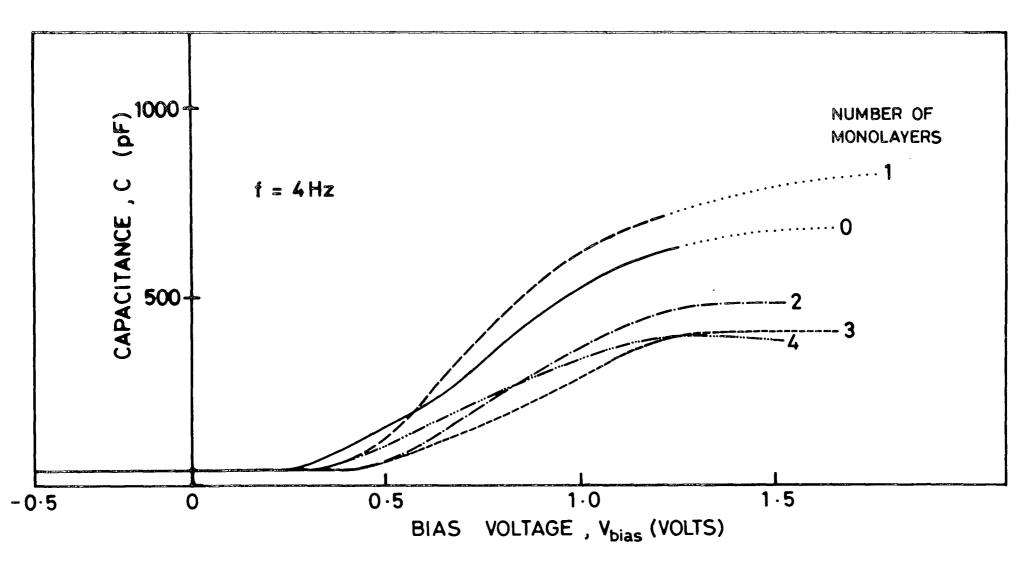

| 8.6 Solar Cel       | 1 Measurements                                                                                 | 177               |

| 8.7 Summary a       | and Conclusions                                                                                | 179               |

| CHAPTER 9 : THICK I | NSULATOR MIS RESULTS                                                                           |                   |

| 9.1 Introduct       | ion                                                                                            | 182               |

| 9.2 Admittano       | ce Characteristics                                                                             | 183               |

| 9.2.1 Ca            | pacitance-Voltage and Conductance-Voltage                                                      |                   |

|                     | erves                                                                                          | 183               |

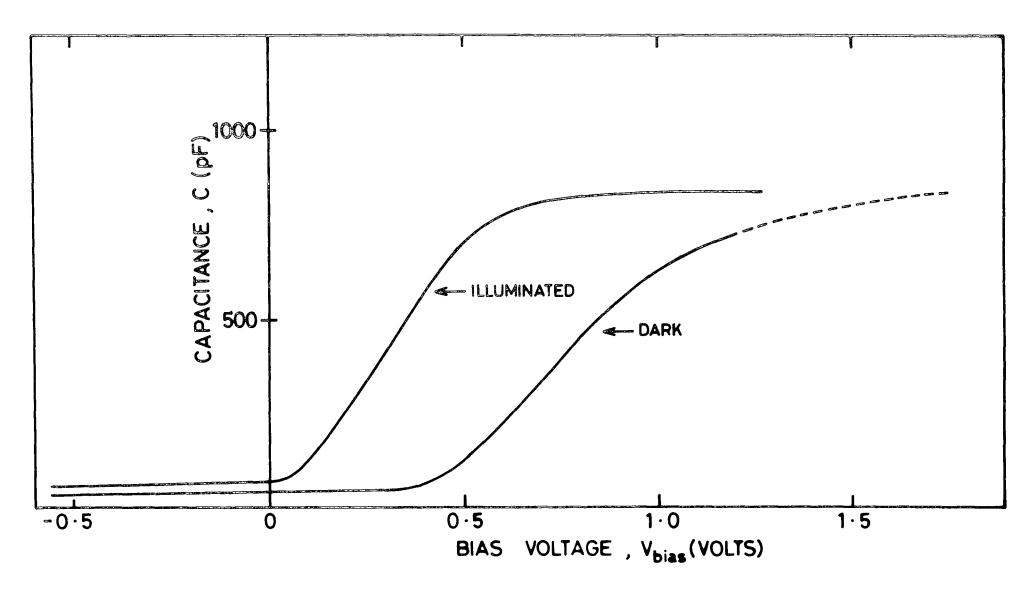

|                     | e Effects of Illumination steresis Effects                                                     | 185<br>186        |

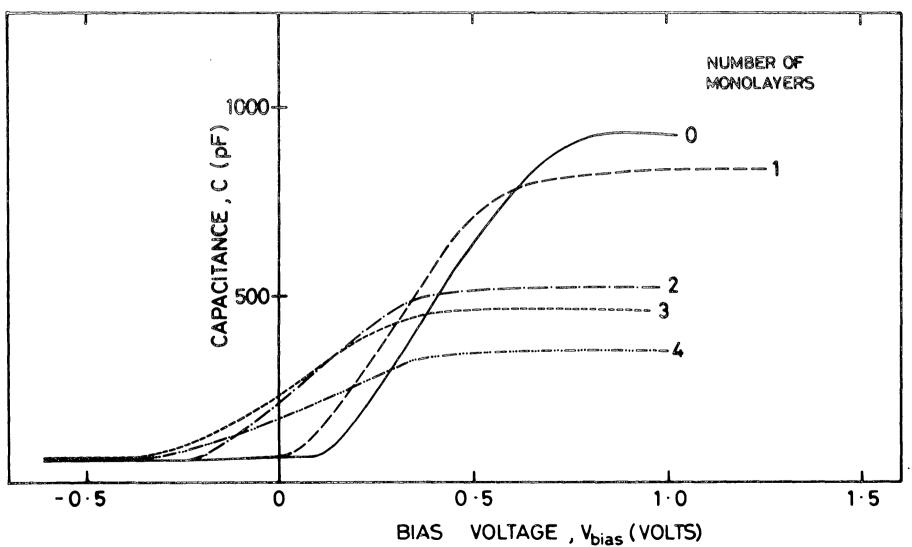

| _                   | anges in Insulator Thickness                                                                   | 189               |

| 9.2.5 Ch            | anges in Insulator Material                                                                    | 196               |

|                                                                                         | Page       |

|-----------------------------------------------------------------------------------------|------------|

| 9.2.6 Changes in the Measuring Frequency 9.2.7 Application of the Conductance Technique | 198<br>202 |

| 9.3 D.C. Conductivity Data                                                              | 203        |

| 9.4 Field Effect Transistor Results                                                     | 206        |

| 9.5 Summary and Conclusions                                                             | 208        |

| CHAPTER 10 : CONCLUSIONS AND SUGGESTIONS FOR FURTHER WORK                               | 211        |

| FIGURE CAPTIONS                                                                         | 214        |

| REFERENCES                                                                              | 225        |

#### CHAPTER 1

#### INTRODUCTION

The development and application of new materials often leads to scientific progress and social change. This can be seen quite clearly in the rapid rise of single crystal silicon technology to its present highly advanced state, and the consequent changes in society brought about by the increasing use of semiconductor devices in computers, T.V's etc. Other single crystal semiconductors e.g. InP, GaAs are currently being investigated in the search for faster devices and improved performance. In certain applications however, rather different factors must be considered, for example, the ability to make thin semiconducting films over large areas, or the need for a very cheap device. To some extent these considerations may be more important than the speed of operation or the performance, and a trade-off must be made. These different criteria call for the use of different materials and indeed, there is one group of materials, namely the non-crystalline semiconductors, whose properties may be well suited to such needs.

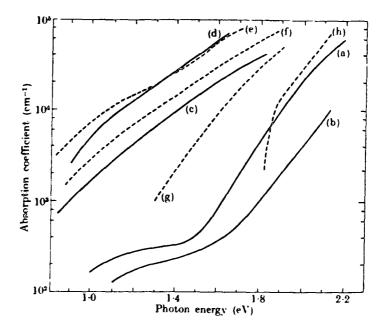

Although amorphous and glassy semiconductors have been studied for some time, it is only in the last twenty years that their potential impact on the electronics world has become apparent. In particular the discovery that amorphous silicon ( $\alpha$ -Si:H) produced by the glow discharge technique could be doped n- or p-type has generated enormous interest. This material may be deposited in thin film form, on a variety of substrates and over large areas. Coupled with its excellent photoconductivity and high absorption coefficient for visible light, these properties mean that solar cells based on  $\alpha$ -Si:H could become a viable, low cost, alternative to single crystal Si cells. The semiconducting properties of  $\alpha$ -Si:H, though poorer than those of single crystal Si, are outstanding for a disordered material and open up other

applications such as thin film integrated electronic devices, transistors, optoelectronic imaging sensors and xeroxography. In short,  $\alpha$ -Si:H has become almost the prototype amorphous semiconductor.

The Langmuir-Blodgett (LB) technique is another recently developed technology, although its origins can be traced back 200 years. LB films are produced from compressed organic monolayers by repeatedly passing the substrate through the monolayer (usually on a water surface) and building up a multilayer structure. The deposition method is a low temperature process and films of accurately defined thickness can be put down over large areas. A variety of different molecules may be used, enabling one to alter the thickness of each individual monolayer and the overall properties of the film. Research is being conducted into the exploitation of LB films on single crystal semiconductors where they usually form the insulating layer in some sort of MIS device. It is noticeable, however, that the large area and thin film capability of the Langmuir-Blodgett technique matches—quite closely some of the advantageous characteristics of  $\alpha$ -Si:H. Therefore it was considered that an investigation of MIS devices based on  $\alpha$ -Si:H and incorporating LB films could be both very interesting and fruitful.

This thesis deals basically with two types of device: tunnelling MIS devices, and those with a non-tunnellable insulator. The former type may be used in solar cell applications. In this context the LB technique provides a unique method of studying the effects of insulator thickness in a controllable way using built-up multilayers. The study of non-tunnellable MIS structures leads the way to the production of an  $\alpha$ -Si:H FET. One reason for the interest in such FET's is that they could be used for the direct switching of liquid crystal elements in large area displays. Once again the properties of LB films would appear to match the requirements very well. The structure of the thesis is as follows. Since  $\alpha$ -Si:H is a relatively new material, chapter 2 is devoted to a broad review of its production, properties

and applications. Chapters 3 and 4 cover the basic theory of Schottky barrier and tunnelling MIS devices, and of non-tunnelling (thick insulator) MIS structures. LB film technology is introduced in chapter 5, which includes the historical background, experimental procedures, a summary of the electrical properties of the films and an outline of possible applica-In chapter 6 the various experimental arrangements used during the course of this study are described and the techniques of device fabrication are listed. Also included are the results of some important, preliminary experiments carried out at various stages in the fabrication procedure. Chapters 7, 8 and 9 contain the bulk of the experimental data. The first of these deals with the characterisation of Schottky barrier diodes on These diodes form an effective 'first step' towards the tunnelling MIS devices which are discussed in chapter 8, and help to establish a standard by which the MIS devices can be judged. In chapter 8, detailed measurements on these novel tunnelling LB film/ $\alpha$ -Si:H structures are reported and their solar cell properties are investigated. Chapter 9 is concerned with the non-tunnelling devices. A series of experiments is described which has led to the fabrication of the first α-Si:H/LB film FET. chapter of the thesis summarises the conclusions and gives suggestions for further work.

#### CHAPTER 2

#### INTRODUCTION TO AMORPHOUS SILICON

#### 2.1 Introduction

In a crystalline semiconductor the electron wavefunctions may be defined using Bloch functions which incorporate the periodicity of the lattice. The energy bands are clearly defined using the relations between energy and wavevector (E-k relations). In an amorphous semiconductor this periodicity is absent : k, the electron wavevector is no longer a good quantum number and Bloch's theorem is rendered invalid. However, solutions to the Schrodinger equation must still exist and hence the concept of a density of states is still valid (1). Photoemission studies on crystalline materials have shown that the conduction and valence band densities of states are determined largely by the short range order i.e. the local bonding arrangements. Since short range order is preserved in amorphous materials the gross features of their electronic structure should be similar to that of their crystalline counterpart. The main differences occur at the band-edges, where, instead of a sharp 'cut-off' of states, the distribution tails into the forbidden gap. Two different types of state are known to exist. States which are well within the bands are extended in nature i.e. the wavefunctions extend throughout the whole semiconductor (although they are not Bloch functions). Nearer the band-edges, as the density of states reduces (i.e. in the 'tail' region), the states become localised i.e. each wavefunction has a large amplitude at a particular point which decays approximately exponentially with distance. The mobility of the carriers in these states is very low (since conduction must take place by a hopping mechanism) and vanishes completely at absolute The transition from extended to localised states is an abrupt one, occurring at a definite energy which is known as the mobility edge because of the sudden change in carrier mobility.

Another cause of states in the gap of amorphous semiconductors is the presence of structural defects. It is thought that a defect-free amorphous semiconductor, i.e. one in which all bonds are satisfied and in which there are no inhomogeneities, has an electronic structure which exhibits limited band tailing such that there is a range of energies with a zero density of allowed energy levels (a 'pseudo-bandgap'). Real amorphous materials often contain very high defect densities e.g. vacancies, voids, impurities, dangling bonds etc. which lead to a finite density of states throughout the forbidden gap. If the density of states is large enough the Fermi level may become 'pinned' i.e. the position of the Fermi level is fixed relative to the conduction and valence bands, and is insensitive to substitutional doping or to the injection of excess carriers.

This chapter is concerned with hydrogenated amorphous silicon  $(\alpha-Si:H)$  which is a rather unusual amorphous  $(\alpha)$ -semiconductor. general, most α-semiconductors may be assigned to one of two classes on the basis of their observed properties. Glassy α-semiconductors are commonly prepared by quenching molten material, although they can be deposited from the vapour phase. They are typified by the chalcogenides which are compounds containing a large proportion of one or more group VI elements. These wide bandgap (∿2eV) semiconductors display an activated conductivity with an activation energy equal to roughly half the optical Their absorption varies according to the spectral Urbach rule bandgap. i.e. the logarithm of the absorption coefficient is proportional to the photon energy. ESR measurements show a very low density of unpaired spins and it is very difficult to change the conductivity of chalcogenides by doping. Non-glassy a-semiconductors cannot be prepared from the melt. They are made in thin-film form by vacuum evaporation, sputtering, glow discharge decomposition of a gas or electrolytic deposition (1). This

group is best represented by pure, evaporated  $\alpha$ -Si or  $\alpha$ -Ge. These have a tetrahedral 'diamond' structure locally and esr measurements detect a high density of unpaired spins. Their conductivity follows the Mott variable-range hopping law (ln  $\sigma \propto T^{-\frac{1}{4}}$ ) rather than the classical activation energy equation ( $\sigma = \sigma_0 \exp(-E/kT)$ ). These films are also insensitive to substitutional doping.

Films of hydrogenated  $\alpha$ -Si and  $\alpha$ -Ge produced by the glow discharge technique or by reactive sputtering in hydrogen are notable exceptions to the above classification, having markedly different properties from the other non-glassy semiconductors. For instance, α-Si:H displays a quite well defined optical absorption edge at ~ 1.7eV. ESR measurements record a low density of unpaired spins and the conductivity at room temperature is observed to be activated rather than following a hopping law. In short, although α-Si:H is a non-glassy semiconductor, its behaviour is remeniscent of a chalcogenide. There is however one important difference :  $\alpha$ -Si:H can be substitutionally doped to change its conductivity. Both p-type and n-type samples can be produced and the conductivity can be varied over a range of ten orders of magnitude. This unique (for an α-semiconductor) controllability of conductivity by doping, together with the relative ease with which large area thin film deposition can be achieved, has opened up the possibility of using  $\alpha$ -Si:H in many different device structures. a result α-Si:H is currently the object of a great deal of scientific and commercial interest.

The remainder of this chapter provides a more detailed introduction to amorphous silicon. The notation  $\alpha$ -Si is used as a general term to include all different forms of amorphous silicon. When a specific form is being considered this is clearly stated e.g. evaporated  $\alpha$ -Si, hydrogenated  $\alpha$ -Si ( $\alpha$ -Si:H) etc. The emphasis is on glow discharge produced  $\alpha$ -Si:H, which

was the material used in this investigation, although other types of  $\alpha$ -Si are included for comparison. Sections 2.2 and 2.3 deal with the preparation and structure of  $\alpha$ -Si films. Because of the importance of the electronic structure of  $\alpha$ -Si, section 2.4 discusses methods of measuring the gap density of states as well as the current models of the band structure. The electrical and otpical properties are summarised in sections 2.5 and 2.6 respectively, and the chapter closes with a review of the potential applications of  $\alpha$ -Si:H.

#### 2.2 Preparation of Amorphous Silicon

Pure amorphous silicon has traditionally been produced by radio frequency (r.f.) sputtering, vacuum evaporation and electrolytic deposition, although the latter method is not commonly used. R.F. sputtering is usually performed in an argon atmosphere using a prefabricated, polycrystalline or compressed powder target (2). Deposition rates of a few microns per hour can be attained with an Ar pressure of  $\sim 10^{-3}$  torr. The inclusion of a small amount of Ar in the films (typically 1%) is unavoidable and forms the major impurity in a good system. Vacuum evaporation can produce  $\alpha$ -Si films up to 20  $\mu$ m thick with properties similar to sputtered material, given ideal conditions (1). These are ultra-high vacuum ( $\sim 10^{-10}$  torr), pure source materials, a large source-substrate separation, ultra-clean, smooth substrates held at high temperatures (250-300°C) and a slow evaporation rate.

Films of hydrogenated  $\alpha$ -Si are generally made directly, although the post-deposition hydrogenation of pure  $\alpha$ -Si samples is possible. The most popular methods are the glow discharge technique and r.f. sputtering in a hydrogen atmosphere: these will be described in detail. Other techniques are described only briefly.

#### The Glow Discharge Technique

Hydrogenated amorphous silicon was first produced using the glow discharge (g.d.) decomposition of silane, SiH<sub>4</sub> by Sterling et al<sup>(3,4)</sup> in 1965. Subsequently, intensive investigations were carried out by Spear's group at Dundee<sup>(5,6)</sup>. The plasma provides a convenient means of transferring energy to the gaseous molecules. The electrons contained in the plasma have sufficient energy (1-10eV) to break molecular bonds by collision, creating new species such as atoms, ions and free radicals. These species may then recombine to form more stable compounds. A glow discharge may thus be used to facilitate chemical reactions at low ambient temperatures.

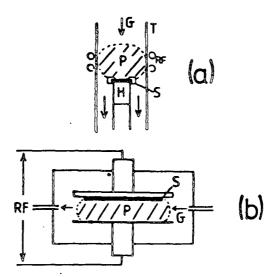

The earliest apparatus used inductive coupling of the r.f. power to maintain the discharge  $^{(3,4)}$  (see Fig. 2.1(a)). Silane gas flowed through the quartz chamber, over the substrate, mounted on a heated block. The system was operated at a power of 10-20W in the frequency range 0.5-100 MHz. The deposition rate ranged between 100 and 1000 % min  $^{-1}$ . The electronic properties of films deposited in this fashion depend critically on a large number of variables e.g. substrate temperature  $(T_d)$ , gas flow rate and pressure, r.f. power level, the floating potentials on various internal surfaces and the system geometry. The uniformity of the films is a problem owing to the small size of the discharge chamber, typically 5-7 cm internal diameter. Unfortunately this is difficult to overcome since the arrangement is not easily scaled up.

Large area specimens with a higher degree of uniformity may be deposited using a capacitively coupled r.f. discharge  $^{(5-7)}$ . A schematic diagram of such a system showing the internal parallel plate electrodes is given in Fig. 2.1(b). The variables governing deposition are as listed for the inductively coupled system. Pure silane is passed through the system while the substrate is held at a constant temperature  $T_d$ . Flow rates, which can be between 10 and 30 standard cm<sup>3</sup> per minute are monitored electronically and

Fig. 2.1 Schematic diagram of gas phase deposition of an amorphous semiconductor using (a) inductive coupling of the r.f. and (b) capacitive coupling P is the plasma, S, the substrate and G is the gas flow direction.

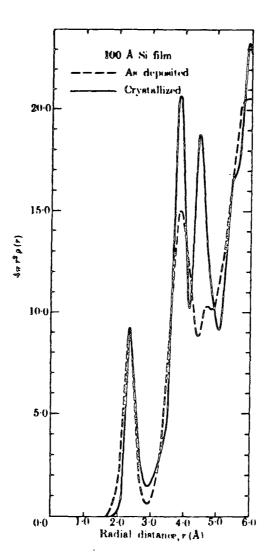

Fig. 2.2 Radial distribution function of amorphous (evaporated) and crystalline silicon as determined from analysis of electron diffraction data (29).

the gas is pumped away at the lower end of the chamber, maintaining a pressure of a few torr. Decomposition takes place inside the reaction vessel and  $\alpha$ -Si:H is deposited on the internal surfaces. Operating frequencies are typically a few MHz with power levels of 10-20W, resulting in a growth rate of about 500  $\mathrm{Amin}^{-1}$ . For a given system with set operating conditions the main variable which determines the film properties is the deposition temperature. Recently, very large area (60 cm diameter)  $\alpha$ -Si:H films have been produced with a low frequency (380 kHz) discharge (8). However, this material seems to have rather poor electronic properties at present.

Thin films of  $\alpha$ -Si:H have also been made in a d.c. glow discharge of SiH<sub>4</sub> (9); the substrate can be made either the cathode or the anode. In the case of an insulating substrate this method may still be used by placing a cathodic screen near the substrate.

The doping of  $\alpha$ -Si:H was first reported by Chittick et al<sup>(4)</sup> although the first detailed experiments were carried out by Spear and LeComber<sup>(10)</sup>. To produce a doped layer, the correct dopant in gaseous form is mixed with the silane before passing into the reaction chamber. Phosphine (PH<sub>3</sub>) or diborane (B<sub>2</sub>H<sub>6</sub>), for n- and p-type films respectively is admitted to a small known volume and its pressure is measured. It is then expanded into an evacuated cylinder and mixed with silane to attain a standard pressure. In this way a few volume parts per million can be added to the silane with a fair degree of accuracy. Any combination of n-type, p-type or undoped layers can be deposited simply by controlling the gas flow through the reaction vessel. The use of such toxic gases necessitates nitrogen 'purging' facilities to clean the apparatus.

Whichever experimental arrangement is chosen, the plasma in a glow discharge is always in close proximity to the substrate. The reactions taking place at this surface are very complex since they involve many

different chemical species e.g. silicon-hydrogen fragments, electrons.

The production of reproducible films requires close experimental control over these reactions and is not easily achieved. As a consequence, different laboratories may produce films which are ostensibly the same and yet exhibit markedly different properties.

#### R.F. Sputtering

Reactive sputtering in hydrogen is a modification of the conventional inert gas sputtering technique. Hydrogen is added to the inert gas, the proportion being up to 20%. A target of pure Si is held at a large negative d.c. potential relative to the low pressure plasma of gas. Ions are accelerated to the target ejecting (usually) neutral atoms, some of which diffuse to the substrate. Paul et al (11) first showed the effect of hydrogen inclusion in sputtered  $\alpha$ -Si:H films. The equipment used is very similar to a capacitively-coupled plasma decomposition system, the main differences being the much lower pressure (  $\sim$  5 x 10<sup>-3</sup> torr) and the higher d.c. potential (1-2 kV compared with  $\sim$  100V). Both the hydrogen partial pressure and the argon pressure are important variables in determining the film properties, and the bias may also be important. Doping from the gas phase has also been achieved in sputtered films (11).

#### Other Methods

Several other techniques are currently at an early stage of development. Chemical vapour deposition (c.v.d) of silane has been successfully used and doping of such films has been reported  $^{(12)}$ . These films are thought to contain less hydrogen than g.d.  $\alpha$ -Si:H because of the high deposition temperature  $(650^{\circ}\text{C})$ . Thus post-deposition hydrogenation by annealing at  $\sim 400^{\circ}\text{C}$  in a hydrogen plasma may be necessary  $^{(13)}$ . Miller et al have described  $\alpha$ -Si:H formation by reactive evaporation  $^{(14)}$  where atomic hydrogen is added to the silicon during the deposition process. More recently Caesar et al  $^{(15, 16)}$

have used ion beam deposition: the advantage claimed for this technique is that deposition occurs in a field free region, resulting in minimum heating, radiation and plasma damage to the growing film. Preliminary results suggest that this method may offer a greater control of the intrinsic defects and hence of the electronic properties of the films.

#### 2.3 The Structure of Amorphous Silicon

#### 2.3.1 Methods of Structure Determination

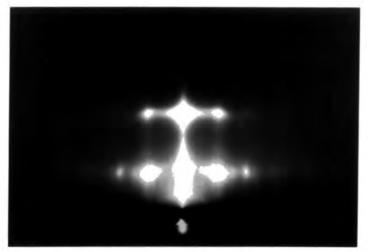

Diffraction Techniques. As with crystalline materials the major tools for structural assessment are X-ray, neutron, and electron diffraction. The practical and theoretical aspects of these techniques, as applied to the amorphous state, are discussed extensively in refs. (17-19). Because amorphous solids lack any periodicity and are generally isotropic on a macroscopic scale their diffraction patterns consist of broad rings or 'haloes'. From the measured angular intensity distribution of scattered radiation a one-dimensional description of the atomic arrangement, known as the radial distribution function (RDF) can be calaculated. A plot of the RDF against r, the distance from an arbitrary atomic centre, displays peaks situated at r values corresponding to the average separation of nearest neighbours, next-nearest neighbours etc. The width of a peak gives the fluctuation in the interatomic spacing and the area under a peak is related to the co-ordination number.

#### Other Methods

Extended X-Ray Absorption Fine Structure (EXAFS) measurements may be used to complement diffraction studies (20, 21). The sample is bombarded with X-rays photoejecting electrons from deep states. These electrons are backscattered by surrounding atoms and they interfere with the outgoing wave, thus modulating the absorption coefficient. An RDF can be obtained from the energy dependence of the absorption coefficient. The technique

is especially useful for investigating alloys, since each element can be examined independently using its own characteristic absorption edge and fine structure. EXAFS is substantially more sensitive to elements present in low concentrations than diffraction techniques.

The vibrational modes of bonded atoms can be investigated using infrared (IR) radiation. Two methods are currently in use: infra-red spectroscopy (22), which involves absorption and reflection measurements, and Raman spectroscopy, which measures the scattering of IR photons in the creation or destruction of optical phonons. Local molecular groupings in amorphous materials can be identified by comparing results with those obtained on crystalline specimens (or with theoretical calculations) since each grouping has characteristic frequencies of vibration corresponding to the stretching and bending of the bonds.

#### 2.3.2 Models of Structure

Models of amorphous solids are based on the concept of an 'ideal' amorphous material i.e. one which is free of impurities, voids, inhomogeneities and where all bonds are satisfied. Calculations of their RDF, density, local bonding arrangements and vibrational properties can be compared with experimental data. Two approaches are possible. The crystallite theory views a material in terms of regions, where the atomic order approaches that of the crystalline state (crystallites), interconnected by regions with a lesser degree of order. However, with small crystallites about 50% of the volume consists of these connecting regions, which must therefore be as important as the crystallites (23). In the limit (i.e. as the crystallite size is reduced) the model becomes indistinguishable from the continuous random network (CRN) model, where the atoms are arranged according to certain constraints. The major constraint of the CRN is that every atom has its chemical bonding requirements satisfied: nearest

neighbour bond lengths are set to approximately their crystalline value (-1%) and bond angles are allowed to fluctuate within given limits.

#### 2.3.3 The Structure of $\alpha$ -Si

Both X-ray  $^{(24-27)}$  and electron diffraction  $^{(28-30)}$  have shown that in pure  $\alpha$ -Si the short range order of the diamond cubic lattice is more or less preserved. Fig. 2.2 shows a comparison of the experimentally determined RDF's of amorphous and crystalline Si. The correlation between the first and second peaks of the two sets of data indicates that each atom has four nearest neighbours, arranged tetrahedrally, with bond lengths within a few percent of their crystalline value. There are twelve next-nearest neighbours at an average separation of  $\sqrt{8/3}$  of the crystalline bond length, but with an r.m.s. distortion of  $^{\frac{1}{2}}$ 10% from the normal tetrahedral angle (109° 28'). Beyond this any structure is lost, as evidenced by the missing third peak.

Polk  $^{(31)}$  constructed a 440-atom, 'ball and stick' model to simulate the structure of amorphous silicon (and  $\alpha$ -Ge). The continuous random network is shown in Fig. 2.3. It allows the relative orientation of neighbouring triads of bonds (known as the dihedral angle) to take up any value. The statistical distribution of dihedral angles gives the network its random character. This model has been refined  $^{(32-34)}$  and seems to provide the best fit to experimental data, although different models have been proposed  $^{(35, 36)}$ .

The densities of pure  $\alpha$ -Si films are usually between 3 and 15% lower than that of Si single crystals. Calculations based on CRN models predict only a 1-3% density difference. The discrepancy is generally attributed to the presence of voids in the structure and small angle electron and X-ray scattering experiments seem to confirm this (28, 29, 36). The large density of defects (  $\sim$  10 $^{20}$  cm $^{-3}$ ) with unpaired spins is shown by the relatively large electron spin resonance (esr) signal. A substantial fraction of these

Fig. 2.3 The 440-atom continuous random network built by Polk (31 ) to simulate the structure of  $\alpha\text{-Ge}$ .

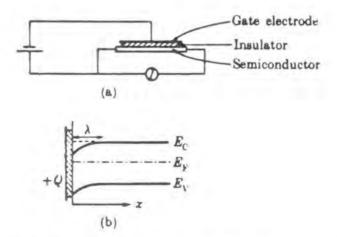

Fig. 2.4 (a) Experimental arrangement for field-effect measurements.

(b) Variation of potential with distance  $\hat{x}$  below the surface of the semiconductor. A charge +Q on the gate electrode induces -Q which, in the absence of surface states, is distributed throughout a space charge region  $\lambda$  either in gap states or in the bands.

defect states may reside on the internal void surfaces (37). The electronic states associated with these defects dominate the properties of such films (see sections 2.4 and 2.5).

Amorphous silicon films which incorporate hydrogen ( $\alpha$ -Si:H) exhibit markedly different properties from pure  $\alpha$ -Si. Undoubtedly, the hydrogen molecules neutralise the defects i.e. they satisfy dangling bonds, as shown by the substantially reduced esr signal. The electronic states associated with these defects are thus removed and no longer control the film properties. However, the amount of H<sub>2</sub> incorporated into the films (from 5 to 50 atomic percent) is many times larger than that required for defect passivation. Because of this  $\alpha$ -Si:H should be treated more as an alloy material, of composition  $\alpha$ -Si<sub>(1-x)</sub>H<sub>x</sub>.

X-ray and electron diffraction results  $^{(27,\ 30)}$  indicate that  $\alpha\text{-Si:H}$  has the same basic structure as pure  $\alpha\text{-Si}$  with a slightly higher degree of local order (i.e. some structure is evident to the third nearest neighbour). Various groups have investigated the incorporation of H using infrared and Raman spectroscopy. Some have identified the presence of hydrogen in the forms SiH, SiH<sub>2</sub>, SiH<sub>3</sub>  $^{(38)}$ ; others have not detected the SiH mode  $^{(39)}$ . More recently Lucovsky  $^{(40)}$  has interpreted infrared data in terms of SiH, SiH<sub>2</sub> and  $(\text{SiH}_2)_n$  groupings, where the latter chain has the same vibrational spectrum as SiH<sub>3</sub>. The exact role of hydrogen in  $\alpha\text{-Si:H}$  is still not clear. Moustakas et al  $^{(41)}$  have suggested that, after defect passivation, hydrogen incorporation increases the gap density of states around the mobility edge. This question is also the subject of a review by Knights and Lucovsky  $^{(42)}$ .

Hydrogenated  $\alpha$ -Si can be doped using trivalent or pentavalent impurities. It was originally thought unlikely that these dopants could be forced into four-fold co-ordination in  $\alpha$ -Si:H, because of the flexibility inherent in a CRN structure (1). However, measurements on P doped  $\alpha$ -Si:H (10, 43) and

EXAFS studies of As doped films (44) give direct evidence of substitutional doping. With low dopant concentrations the doping efficiency is typically 20% for As and 30-40% for P. The structure is not significantly altered, except by high doping levels.

### 2.4 The Electronic Structure of Amorphous Silicon

#### 2.4.1 Methods of Measuring the Gap Density of States

#### (a) The Field Effect Technique

This method probes the gap density of states (DOS) by displacing the state distribution with respect to the Fermi level. A typical specimen geometry is shown in Fig. 2.4(a). The conductivity of the surface layer of the semiconductor between source and drain is monitored by measuring the current for a fixed source-drain voltage. An electric field is applied normal to the sample by means of the gate electrode. The insulating layer must be of high quality and able to withstand high fields (up to  $10^8~\mathrm{Vm}^{-1}$ ) with a minimum leakage current. The field induces excess charge at the semiconductor surface. Some of the charge is trapped in surface states at the semiconductor/insulator interface and some resides in bulk states (both band states and localised states) within the space charge region (see Fig. 2.4 (b)). The conductivity is modified by this excess charge and the changes can be related to the density of states at the Fermi level. The analysis is complex and several approaches are possible (45-50) The main difficulty lies in distinguishing between charge in the surface states and charge in the bulk states. In principle, a surface state density  $\sim 10^{13}~{\rm cm}^2~{\rm eV}^{-1}$  would screen the specimen from the external field, making measurements of the bulk DOS impossible.

#### (b) Steady-State Admittance Measurements

Capacitance-voltage (C-V) measurements are closely related to the field effect technique, and have been widely used on crystalline materials with metal-insulator-semiconductor (MIS) devices, Schottky barriers or

p-n junction structures (51). For small biases the resistance of the depletion region is much greater than that of the bulk and so the depletion width may be obtained directly from the measured capacitance, assuming uniform doping. The capacitance can also be related to the charge density in the depletion region and thus to the density of states. The frequency must be low enough to allow the localised states to follow the oscillating capacitance measurement voltage. Unfortunately, the presence of surface states can lead to spurious results, especially at low frequencies.

Capacitance v frequency (or temperature) measurements have the advantage that a regime may be chosen where surface state effects are minimised (usually high frequency, low temperature). Even so, the separation of bulk and surface contributions is not always simple and the technique is limited to measuring the DOS over a relatively small portion of the gap near  $\mathbf{E}_{\mathbf{p}}$ .

Admittance data may be obtained from tunnellable and non-tunnellable MIS devices. The extraction of a gap DOS is dependent on forming an equivalent circuit for the device. The application of this technique to amorphous semiconductors has been hindered by the poor theoretical understanding of such devices, making modelling difficult. Determining the exact role of surface states complicates matters further, allowing only estimates of the DOS to be made.

#### (c) 'Bulk' Measurements

Traditional 'bulk' measurements e.g. transport data, optical effects, spin resonance are often viewed as giving a more representative value of the bulk DOS, even though interface effects can cause serious errors in films less than a few microns thick. Transport data such as conductivity, drift mobility, space charge limited currents etc. can be used to identify certain transport mechanisms and can shed light on the DOS (see section 2.5).

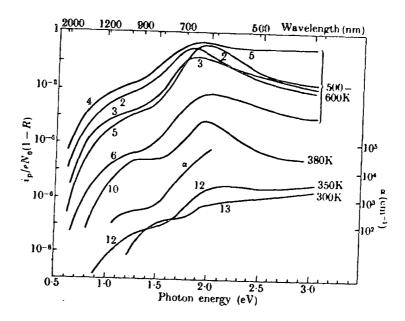

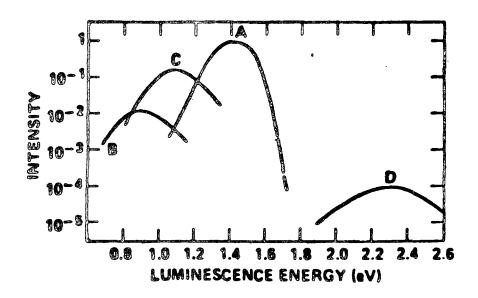

Optical properties like absorption, luminescence and photoconductivity can also yield information on features in the DOS, linking them with particular transitions or recombination mechanisms (see 2.6). Electron spin resonance (esr) is limited in that it can only detect states which have unpaired spins. Nonetheless, it can be used to determine an upper limit to the DOS, though it cannot identify where (in energy terms) those states lie.

#### (d) Non-Equilibrium Techniques

The most powerful of the transient techniques is Deep Level Transient Spectroscopy (D.L.T.S.) (52). This relies on the band bending at a potential barrier to provide a depletion region. By creating a non-equilibrium state e.g. applying a voltage pulse, and monitoring the current or capacitance, information regarding the state density and energy location can be obtained. Surface and bulk states can be distinguished relatively easily and spatial variations in the DOS can be investigated (profiling). The data analysis for an amorphous semiconductor is rather involved, and care must be taken in modelling the device response. The technique can only be used for semiconductors on which a barrier can be produced, which often limits it to fairly conducting samples. Other non-equilibrium techniques involve measuring thermally stimulated currents (TSC) and thermally stimulated capacitance (TSCAP).

#### 2.4.2 Models of the Gap Density of States in Amorphous Semiconductors

An early and influential model of the gap DOS in amorphous semiconducting alloys was proposed by Cohen, Fritsche and Ovshinsky in 1969<sup>(53)</sup> (the CFO model). They supposed that the tails of localised states from the conduction and valence bands (due to the non-crystallinity) would overlap, as shown in Fig. 2.5(a). States from the conduction band would be neutral when empty, while those from the valence band would be neutral when filled. The overlapping of the two tails would create centres of

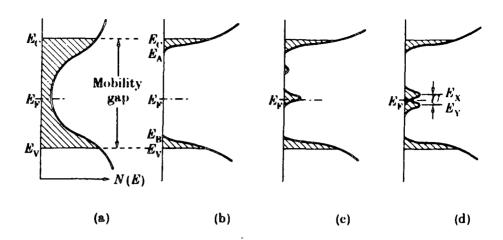

Fig. 2.5 Various forms proposed for the density of states in amorphous semi-conductors. Localised states are shown shaded. (a) the CFO model (53), (b) a real gap in the density of states, as appropriate to an 'ideal' (defect free) material (c) the same as (b) but with a partially compensated band of defect levels (55), (d) the same as (b) but with overlapping bands of donor ( $E_v$ ) and acceptor ( $E_x$ ) levels arising from the same defect.

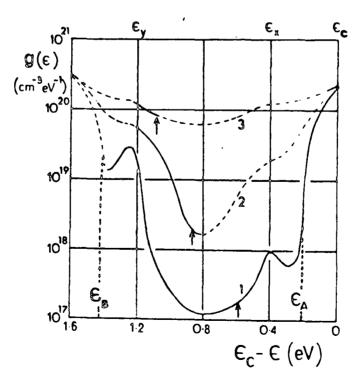

Fig. 2.6 Density of states g( $\epsilon$ ) in amorphous silicon determined by the field effect technique (61). Curve 1: glow discharge  $\alpha$ -Si:H deposited at 550K, Curve 2: glow discharge  $\alpha$ -Si:H deposited at 350K. Curve 3: evaporated or sputtered  $\alpha$ -Si.

unpaired spin because the states would be charged, and this would pin the Ferm level ( $\rm E_{\rm F}$ ) at this position, a phenomenon commonly observed in  $\alpha$ -materials. At a given energy in the conduction and valence band these authors defined a'mobility edge' corresponding to the transition from localised to extended states, first suggested by Mott (54). The range of energies between these two mobility edges is called the mobility gap. The density of states required to pin the Fermi level in this model is high and should be observable both optically and using esr measurements. Since many amorphous semiconductors and insulators are transparent in the visible or infrared and do not exhibit an esr signal equivalent to such a high DOS this model is not commonly applicable. More recently, theoretical calculations have indicated that the band tailing due to disorder should not be as extensive as to cause overlapping.

The generally accepted picture of the band edges in an ideal amorphous semiconductor (as previously defined) is shown in Fig. 2.5(b). A genuine band gap exists. States between  $E_{\rm C}$  and  $E_{\rm V}$  are localised with a very low carrier mobility (see section 2.5). The occurrence of defects can give rise to states in the gap, just as in a crystalline semiconductor, and various models have been proposed explaining observed properties in terms of defect states. Fig. 2.5(c) shows one such model due to Davis and Mott (55) where a band of acceptor levels is partially occupied by electrons from a weaker band of donors. Like the CFO model the density of states required to pin  $E_{\rm F}$  is high, and is not observed experimentally. Roberts (56, 57) has suggested a model involving two defect levels (see also (58)) which would probably be narrow bands of states, as shown in Fig. 2.5(d). Such levels could be responsible for pinning  $E_{\rm F}$  with densities which are too low to be detected optically and can be used to explain experimental data (59).

#### 2.4.3 The Gap Density of States in $\alpha$ -Si

Films of pure  $\alpha$ -Si prepared by evaporation or sputtering generally have high gap densities of states, particularly at the Fermi level,  $E_{\rm F}$ .

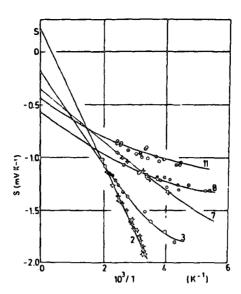

This is shown by the observation of log conductivity v  $T^{-\frac{1}{4}}$  behaviour (hopping conductivity) and also by the small value of the thermopower (60), both of which indicate transport at  $E_F$ . The estimated DOS is  $> 10^{19} \text{ cm}^{-3} \text{ eV}^{-1}$  and  $E_F$  is invariably pinned near midgap. These samples give a large esr signal equivalent to a volume density of paramagnetic centres of  $10^{19} - 10^{20} \text{ cm}^{-3}$ .

Hydrogenated  $\alpha\text{-Si}$  films show no signs of hopping conductivity and give no esr signal, indicating a much lower overall density of gap states. Glow-discharge produced  $\alpha$ -Si:H has been extensively studied by the Dundee group, using the field effect technique (47, 48, 61). Their results are summarised in Fig. 2.6. Films deposited onto substrates held at higher temperatures (  $\sim$  500K) have the best electrical characteristics. The DOS generally increases with decreasing deposition temperature  $^{(61)}$ . The main features of the DOS (see curve 1) are a broad minimum (of about  $10^{17} \, \mathrm{cm}^{-3} \, \mathrm{eV}^{-1}$ ) near the centre of the mobility gap bounded by two peaks at  $E_x$  and  $E_y$ , and a rapidly rising density at  $\mathbf{E}_{\mathbf{A}}$  corresponding to the tailing of the conduction band. Various authors  $^{(62, 63)}$  suggested that some of these features may be artefacts of the analysis used by Spear and LeComber (47), although Grunewald et al (64) derived similar features (within a factor of 2 or 3) using a different analysis. Surface states are also a problem : if the DOS at the surface is different from that in the bulk then errors will be introduced in N(E) (65). Field effect data can therefore only give an upper limit to the gap DOS and features of the state distribution must be verified by independent experiments.

A high degree of correlation has been found between the field effect DOS and data from other experiments. The low DOS in midgap is clearly demonstrated by the ability to move  $E_F$  easily by doping (10, 66). Evidence for the existence of the peak at  $E_y$  comes from photoconductivity results, which exhibit features at hv = 1.1 - 1.2 eV, corresponding to an  $E_y$   $E_c$

transition  $^{(67)}$ . Capacitance measurements confirm this high DOS at  $E_y^{(68)}$ , as does the increasing difficulty experienced in moving  $E_F$  through the region of  $E_y$  by doping  $^{(10, 66)}$ . Furthermore, the transport of excess holes has been shown to be controlled through the trapping and thermal release of carriers by states situated at  $E_y^{(69)}$ . The peak at  $E_x$  is more difficult to detect, because of its lower density. However, it has been identified by Beyer et al  $^{(70)}$ , and by Kablitzer et al  $^{(66)}$ , who estimated the DOS by measuring the number of implanted ions required to move  $E_F$  a given distance. Anderson and Spear have also implied its existence from photoconductivity measurements  $^{(71)}$ , as have Fuhs and Milleville from studies of thermally stimulated conductivity  $^{(72)}$ . Finally the rapid rise in N(E) at the conduction band tail is demonstrated by the difficulty of moving  $E_F$  by doping  $^{(10,66)}$  and the onset of the tail states has been located at about 0.2eV below  $E_C$  by electron drift mobility measurements  $^{(5)}$ .

More recently, Lang et al $^{(73)}$  have investigated the gap DOS using DLTS, TSCAP and TSC techniques. They report a much lower midgap density of states of the order of  $10^{15}$  cm $^{-3}$  eV $^{-1}$ . Their DOS distribution is substantially different to the field effect results, with a deep minimum between 0.3 and 0.6 eV from the conduction band and a broad shoulder of states extending from the valence band to midgap. Some optical and transport data have been re-interpreted to provide support for this model. A similar distribution has been reported by some workers using C-V measurements on thick insulator MIS structures  $^{(74-76)}$ .

Space charge limited current (SCLC) measurements, first observed in  $\alpha$ -Si:H by Ashok et al<sup>(77)</sup>, may provide independent verification of the DOS distribution, since this type of conduction depends on the <u>bulk</u> distribution of localised states. Results published by den Boer<sup>(78)</sup> quote the density of states at midgap to be between 1-4 x  $10^{16}$  cm<sup>-3</sup> eV<sup>-1</sup>,

halfway between the field effect DOS and the DLTS DOS. The distribution of states over a small energy range (0.2eV) resembles the field effect DOS. Bhattacharya et al  $^{(79)}$ have measured N(E $_{\rm F}$ ) by SCLC and field effect experiments. They obtain a value of 7.9 x  $10^{16}$  cm $^{-3}$  eV $^{-1}$  from both methods. Mackenzie et al  $^{(80)}$  have found similar densities of states and have shown that the distribution of these states over quite a wide range of energies is not dissimilar to the earlier field effect data of Spear and LeComber  $^{(47)}$ .

The origin of the two DOS peaks is still the subject of speculation. An early suggestion  $^{(10)}$  associated these states with a defect similar to the divacancy in crystalline silicon, which produces states at comparable energies within the bandgap  $^{(81)}$ . However, the inequality in the densities of the two levels observed in  $\alpha$ -Si:H shows that this interpretation is too simple. It would seem that a whole range of possible defects must be considered  $^{(82)}$ .

#### 2.5 The Electrical Properties of Amorphous Silicon

The electrical properties of evaporated films of  $\alpha$ -Si are dependent on the exact preparation conditions. In particular these films may take up large quantities of oxygen during evaporation. Increasing oxygen concentrations lead to decreasing defect densities and conductivity (83). The variation in conductivity with temperature is approximately  $\sigma \propto T^{-\frac{1}{4}}$  which suggests hopping near the Fermi level as the normal conduction mechanism. Experiments by Knotek (84) on  $\alpha$ -Si films of varying thickness deposited under the ultra-high vacuum provide conclusive evidence for variable range hopping, and he estimates the density of states of  $E_F$  to be  $\sim 3 \times 10^{19}$  cm<sup>-3</sup> eV<sup>-1</sup>. This density is consistent with a pinned Fermi level as observed,

Glow discharge and sputtered  $\alpha$ -Si:H films are generally much more resistive than evaporated  $\alpha$ -Si films deposited at similar temperatures. The deposition temperature,  $T_d$ , is the main variable governing the

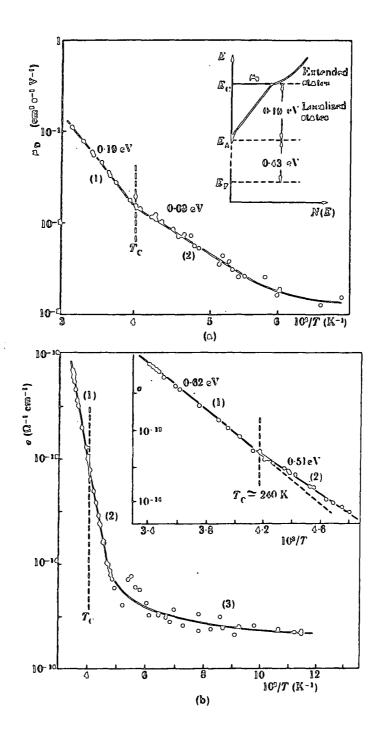

properties of these films. As shown in Fig. 2.7 an increase in  $T_{\rm d}$  from 300K to 640K changes the room temperature conductivity of g.d.  $\alpha$ -Si:H by over five orders of magnitude. The minimum at  $T_d \sim 250 \text{K}$  suggests a change in the conduction mechanism. According to Spear, at high T, transport is due to electrons moving above the mobility edge and at low T, to holes hopping through localised states near the valence band (5). Measurements of drift mobility and conductivity seen to confirm this. Fig. 2.8 shows data taken by LeComber and Spear for an undoped g.d. α-Si:H sample deposited at  $T_d = 500K$ . They have identified three distinct temperature regimes and have associated each with a particular conduction mechanism as follows (85). (Subsequent measurements on samples prepared at different values of  $T_d$  are in agreement.) For T > 250K the conduction is an activated process with an activation energy (from the slope of the  $\mu_d$  graph) of  $\sim$  0.19eV. Electrons drift through the extended states but interact with the localised states by trapping and thermal release. Hence the measured drift mobility  $\mu_d$  is trap controlled, with a room temperature value of  ${\rm ^{\circ}}$  0.1 cm  $^{2}$  sec  $^{-1}$  V  $^{-1}$  . From this, the deduced mobility near the bottom of the extended states,  $\mu_{\alpha}$ is about  $10 \text{ cm}^2 \text{sec}^{-1} \text{V}^{-1}$ . Moore (86) has reported very similar results. As the temperature is decreased the probability of an electron being thermally released from a localised state drops, and at a given temperature the hopping of electrons between localised states will become the dominant transport mechanism. For T < 250K the drift mobility is of the order of  $10^{-2}~{\rm cm}^2~{\rm sec}^{-1}~{\rm V}^{-1}$ , which is consistent with phonon assisted hopping. A clear change in the slope is seen at T = 250K, and the hopping activation is  $\sim 0.09 \, \text{eV}$ . Moore has not found this large change in slope, which casts some doubt on the interpretation (86). However, the conductivity data clearly exhibit these two regimes (see Fig. 2.8(b)). At T = 250K the slope changes from 0.62eV to 0.51eV, a difference of 0.11eV. Thus the change in slopes in  $\boldsymbol{\mu}_{\boldsymbol{d}}$  and  $\boldsymbol{\sigma}$  are approximately the same, as predicted by theory (1). Estimates of the conductivity based on the previous value of

Fig. 2.7 Variation of (a) room temperature conductivity  $\sigma$  (b) activation energy of conductivity (c) pre-exponential factor  $\sigma_0$  for glow discharge  $\alpha$ -Si:H with deposition temperature  $T_d$ . Points on the left of this figure refer to evaporated films for which  $T_d$  has no real significance (after ref (6)).

Fig. 2.8 Temperature dependence of (a) electron drift mobility  $\mu_D$  (b) conductivity  $\sigma$  in a glow discharge  $\alpha\text{-Si:H}$  film deposited at 500K (85).

$\mu_{o}$  and  $(E_{c} - E_{F}) = 0.62 \text{eV}$  from the slope of  $\sigma$  v  $\frac{1}{T}$  (for T > 250K) concur with experimental measurements. The conductivity v  $\frac{1}{T}$  graph also suggests the existence of a third region. For T < 170K the hopping energy decreases still further. This is thought to be indicative of variable range hopping (87) between localised states near the Fermi level.

The drift mobility of holes is considerably less than that of electrons, with a room temperature value of between 5 and 6 x 10<sup>-4</sup> cm<sup>2</sup> sec<sup>-1</sup> V<sup>-1</sup> (69,86). The mobility is still trap-controlled and the  $\mu_{\rm d}$  v  $^1\!\!/_{\rm T}$  graph has a break point at 250K, with corresponding activation energies of 0.35eV (above) and 0.26eV (below).

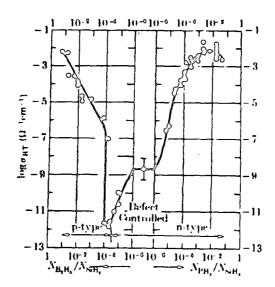

The position of the Fermi level in films described so far is defect controlled. High temperature  $\alpha\text{-Si:H}$  i.e.  $T_d \sim 500\text{-}600\text{K}$  is invariably n-type, with  $E_c$  -  $E_F$  approximately 0.6eV. Doping(as described in Section 2.2) enables the movement of  $E_F$  to within about 0.2eV of either mobility edge (10). The introduction of phosphine (PH3) as a dopant gas in concentrations of only a few p.p.m. increases the conductivity (n-type) by over two orders of magnitude (see Fig. 2.9). The rate of increase in the conductivity falls off with increasing dopant concentration as  $E_F$  moves into a higher density of gap states. The introduction of diborane ( $B_2H_6$ ) during preparation leads, with small concentrations, to a reduction in conductivity corresponding to the shifting of  $E_F$  to midgap. Conduction becomes p-type as the dopant concentration is increased further.

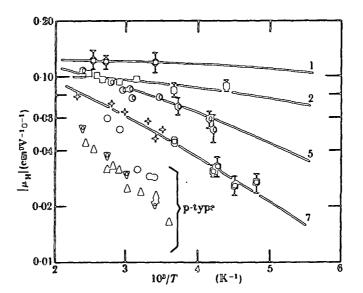

Doped samples have been used in the study of the Hall effect and the thermopower. LeComber et al (88) have measured the Hall mobility as a function of temperature in both n and p-type specimens. They discovered an interesting sign reversal in the Hall voltage: p-type samples showed a Hall voltage in the direction normally associated with electrons and n-type specimens gave a p-type Hall voltage. The former sign reversal may be explained. Theoretical treatments in terms of small polaron conduction (89)

Fig. 2.9 Room temperature conductivity of n- and p-type  $\alpha$ -Si:H plotted as a function of the gaseous composition from which the films were deposited (10).

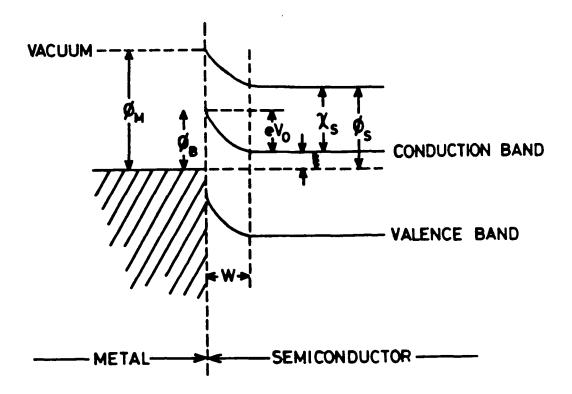

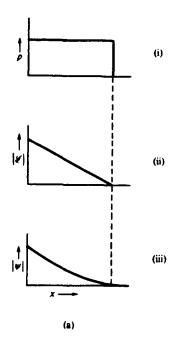

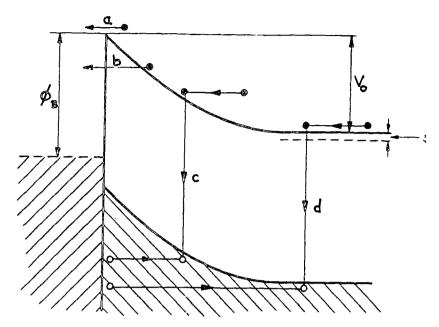

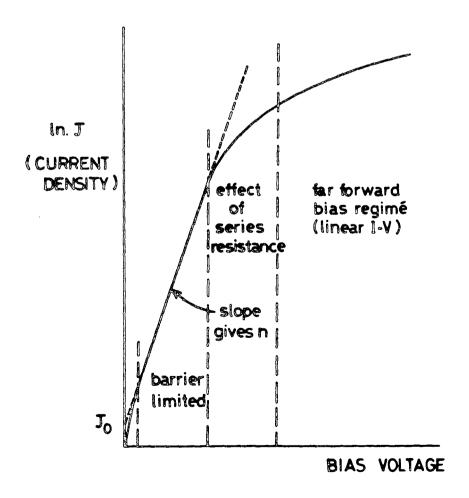

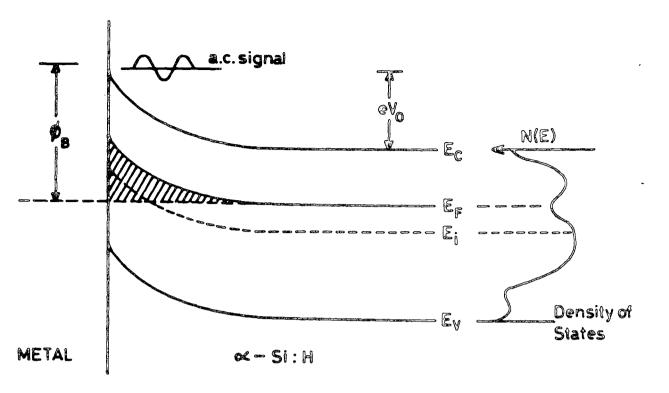

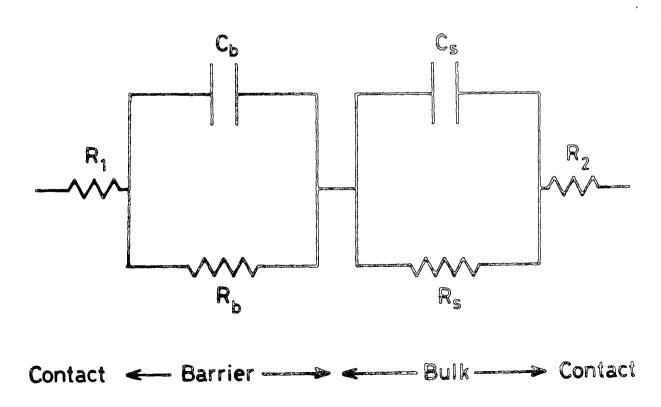

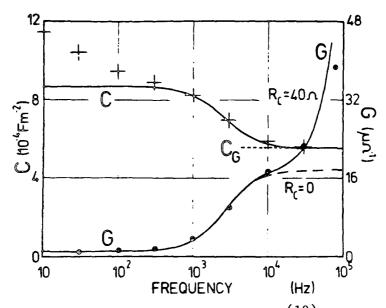

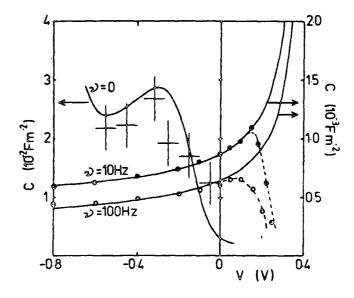

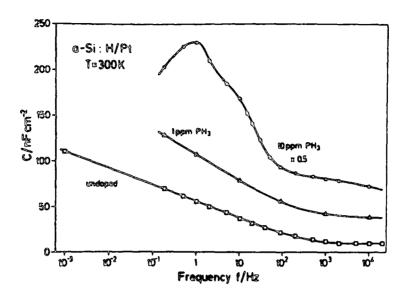

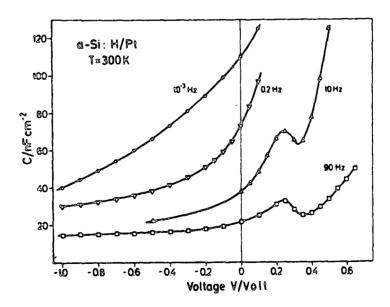

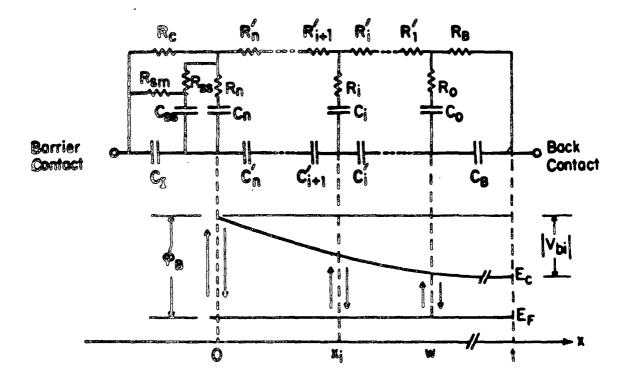

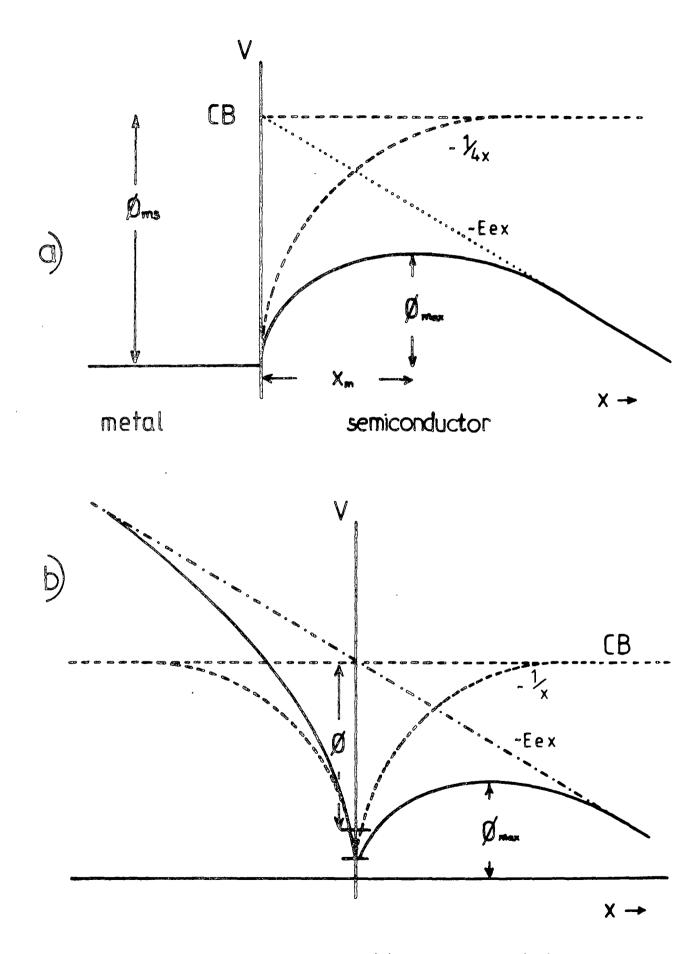

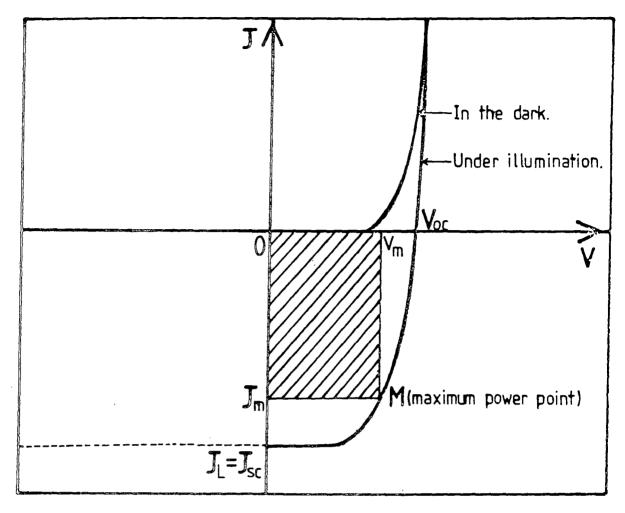

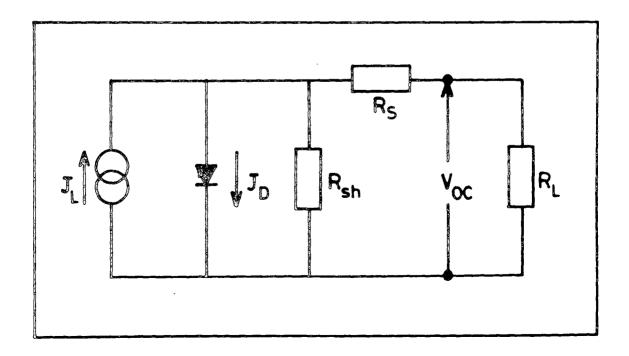

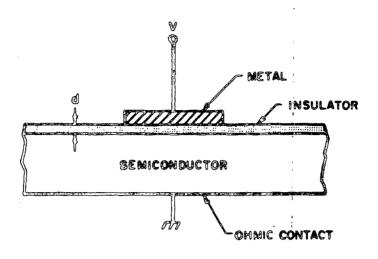

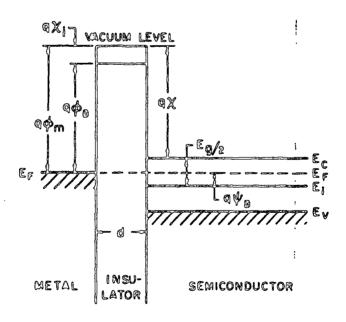

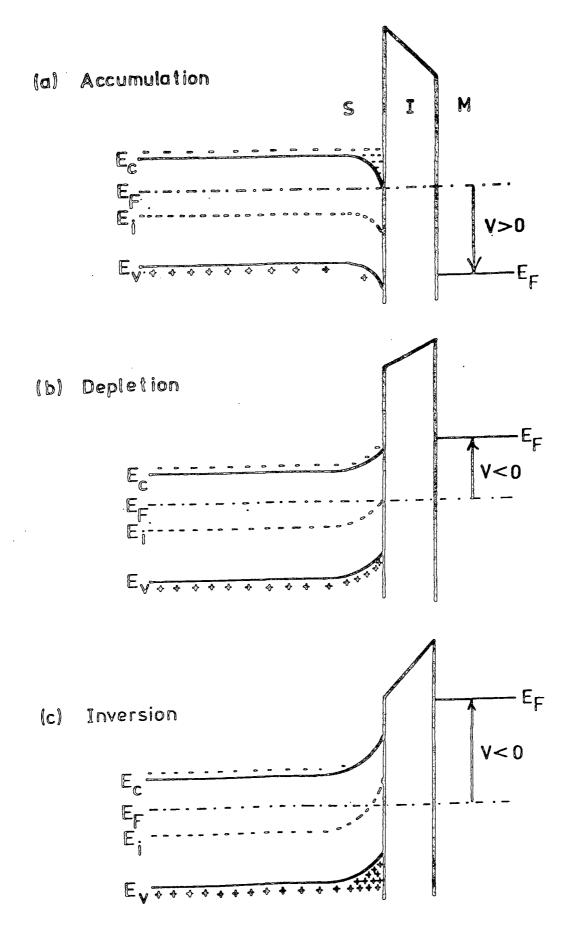

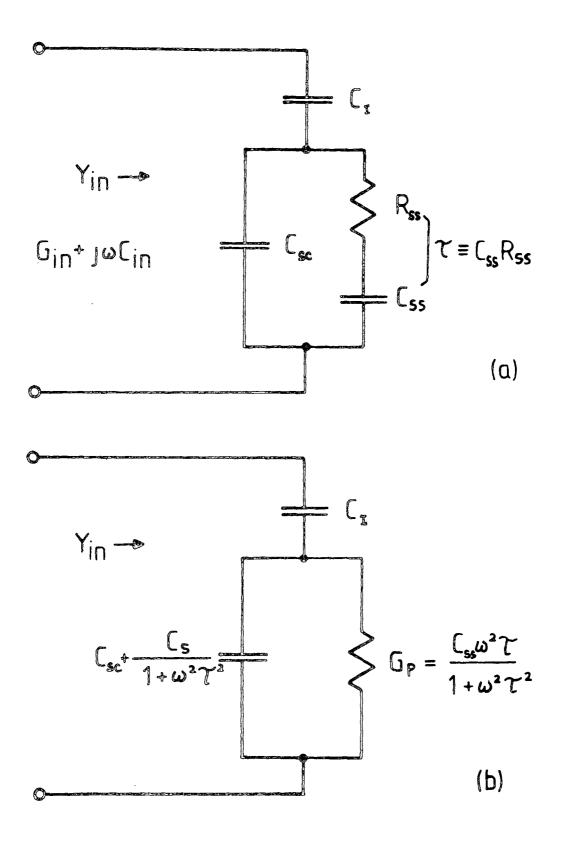

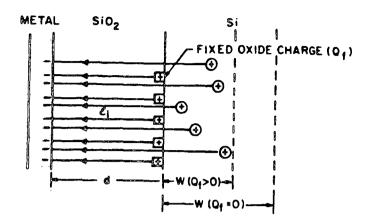

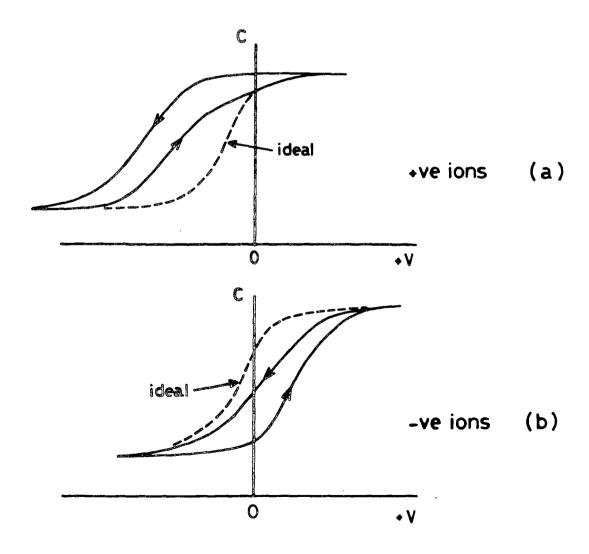

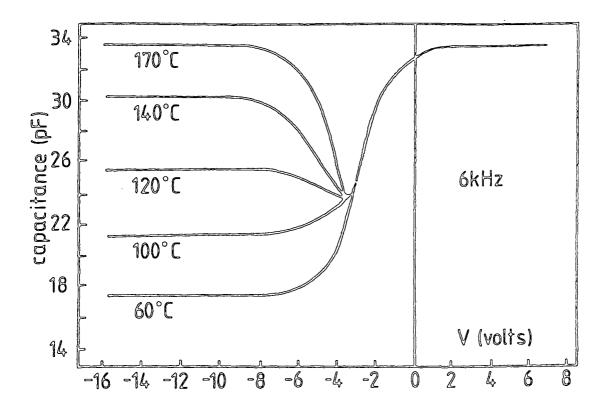

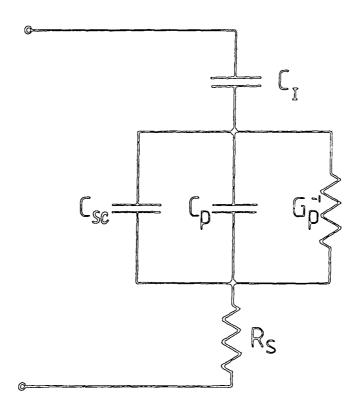

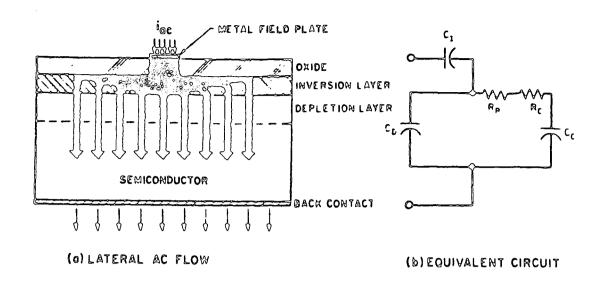

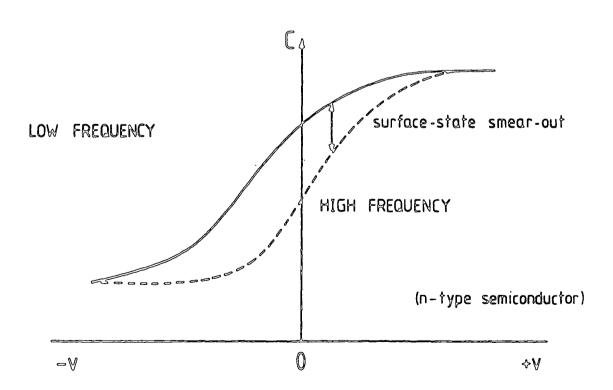

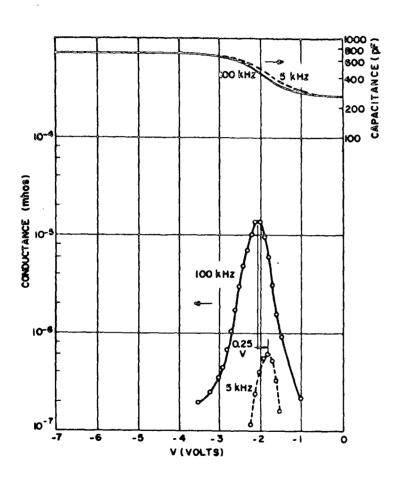

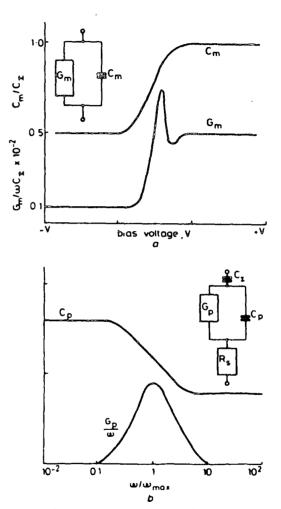

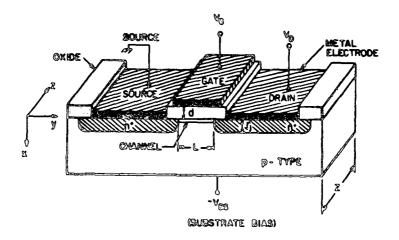

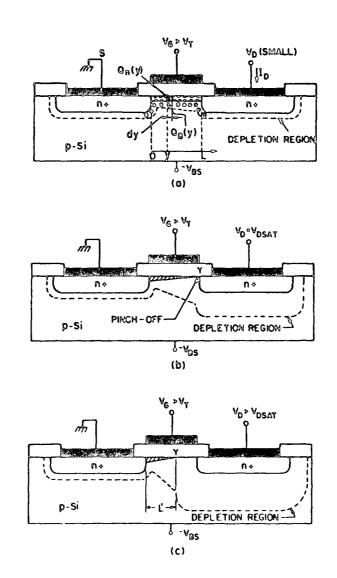

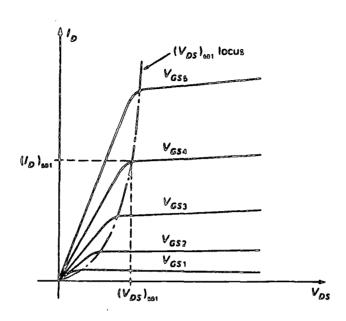

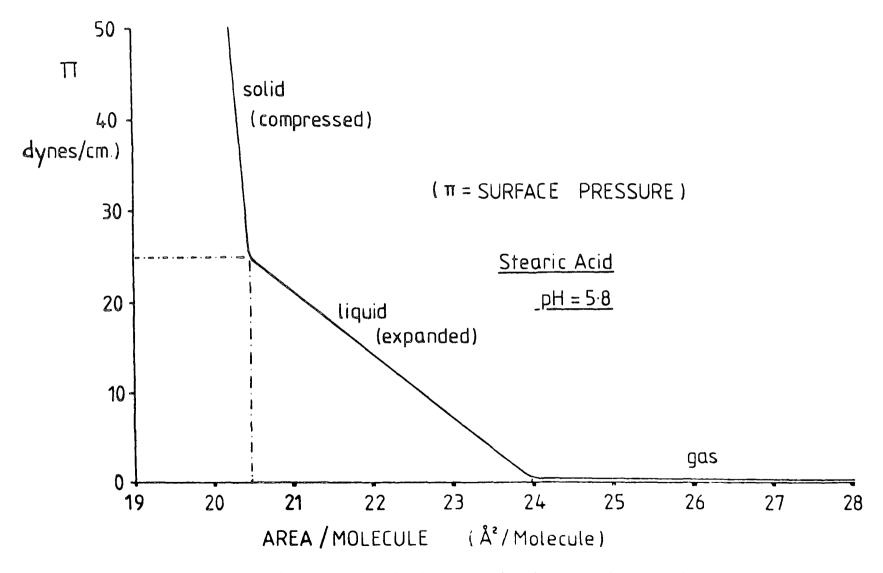

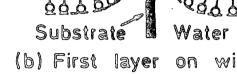

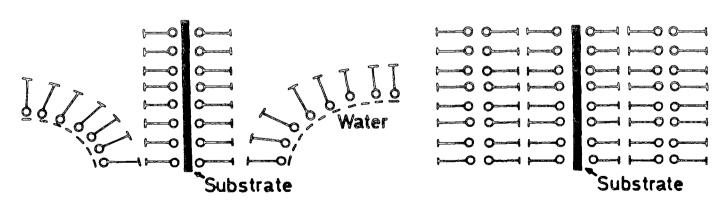

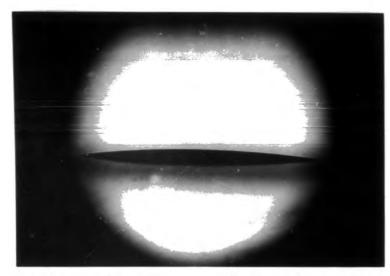

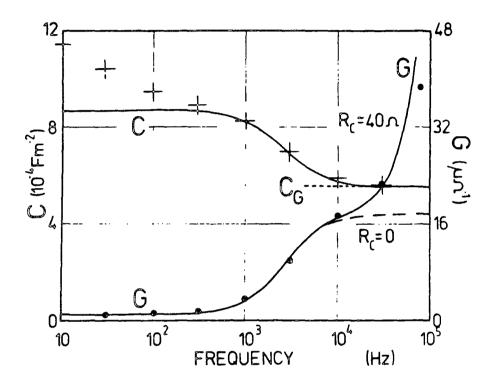

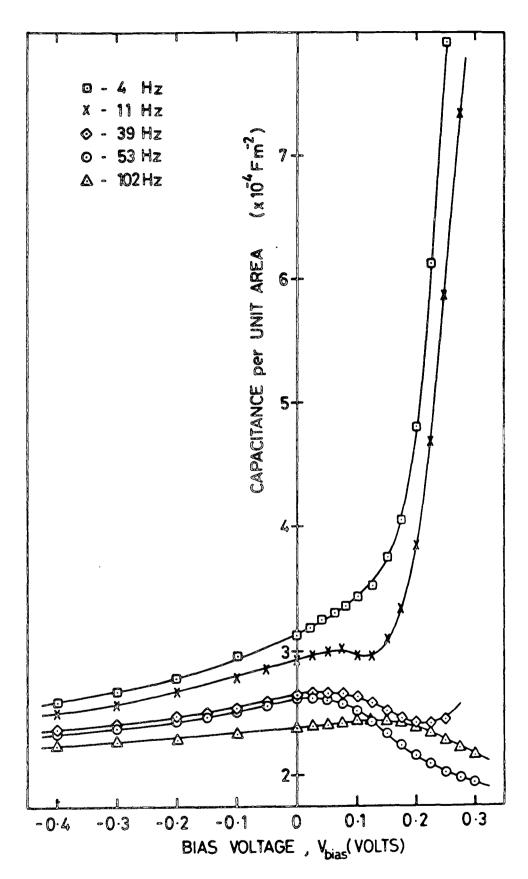

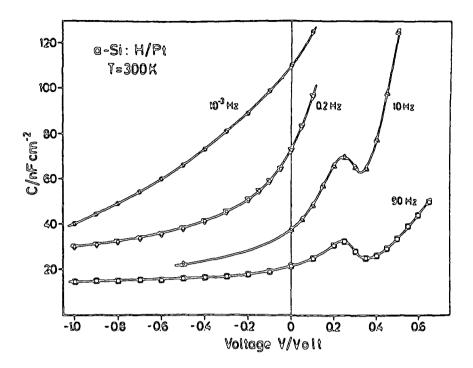

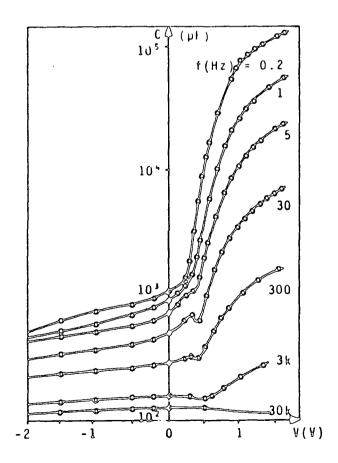

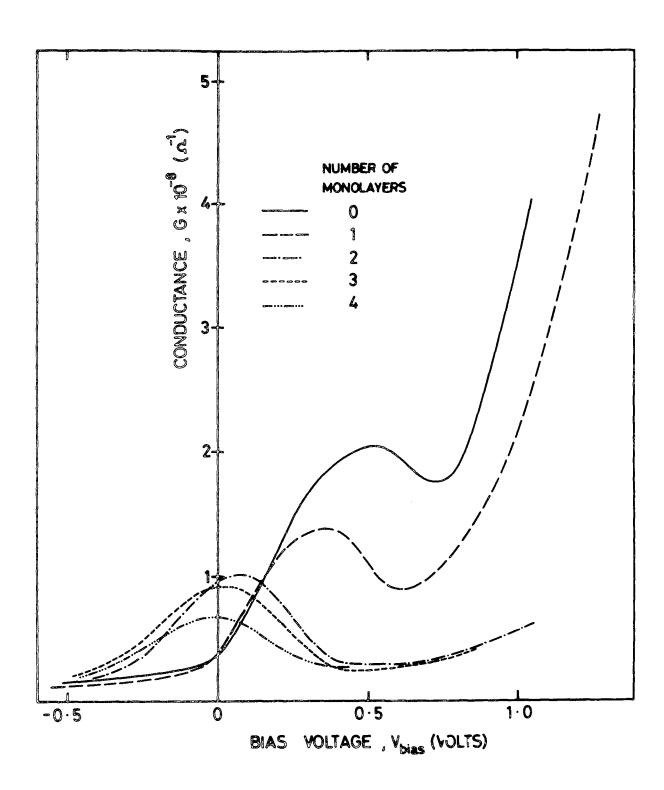

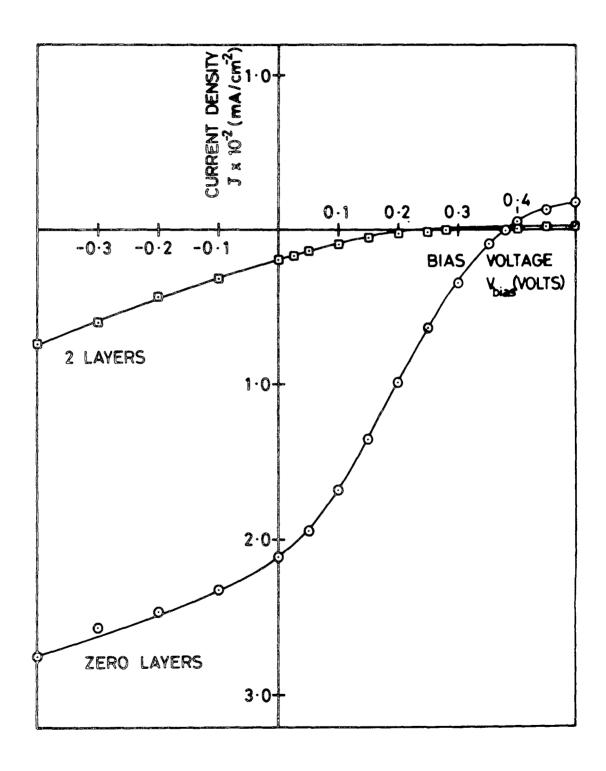

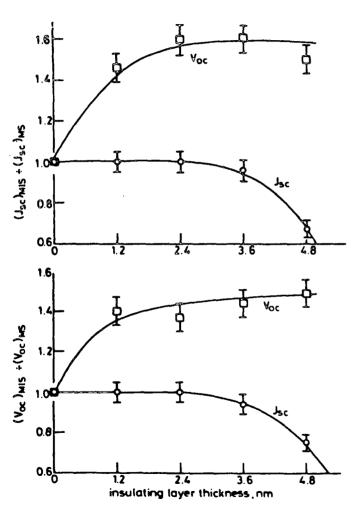

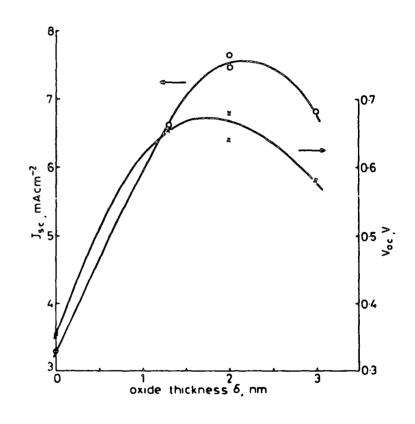

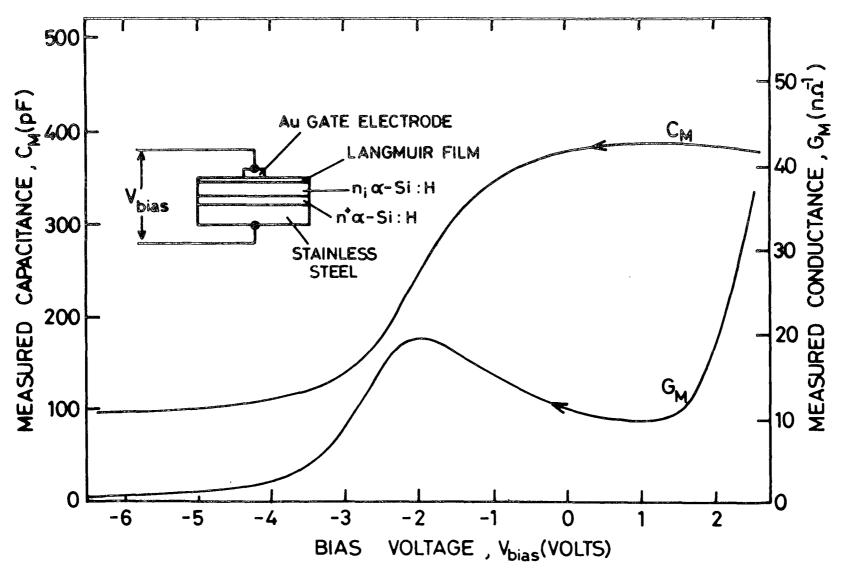

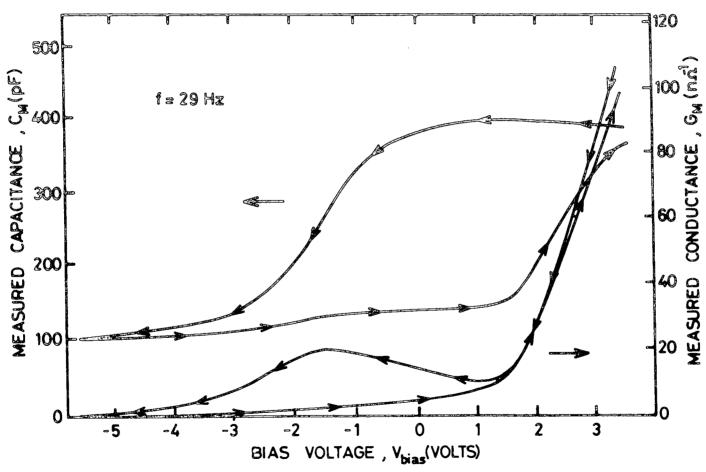

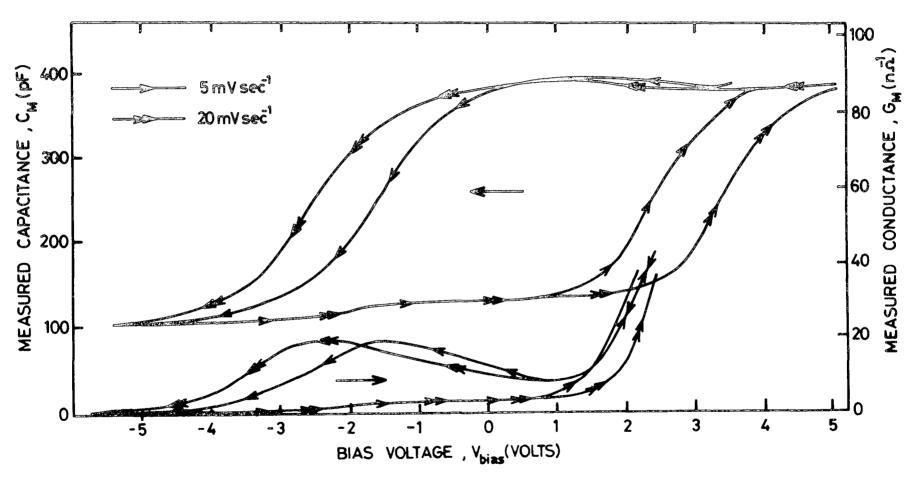

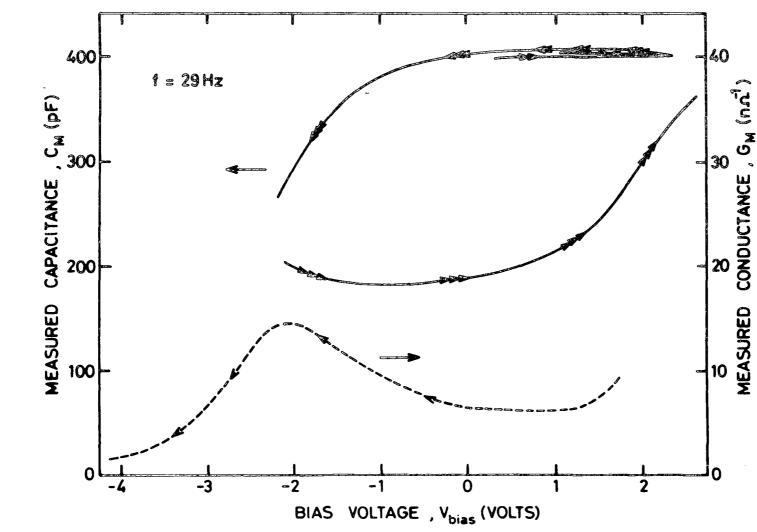

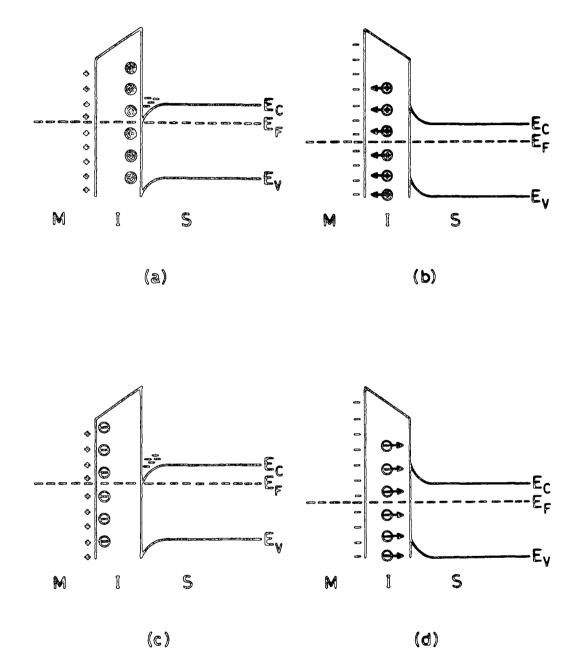

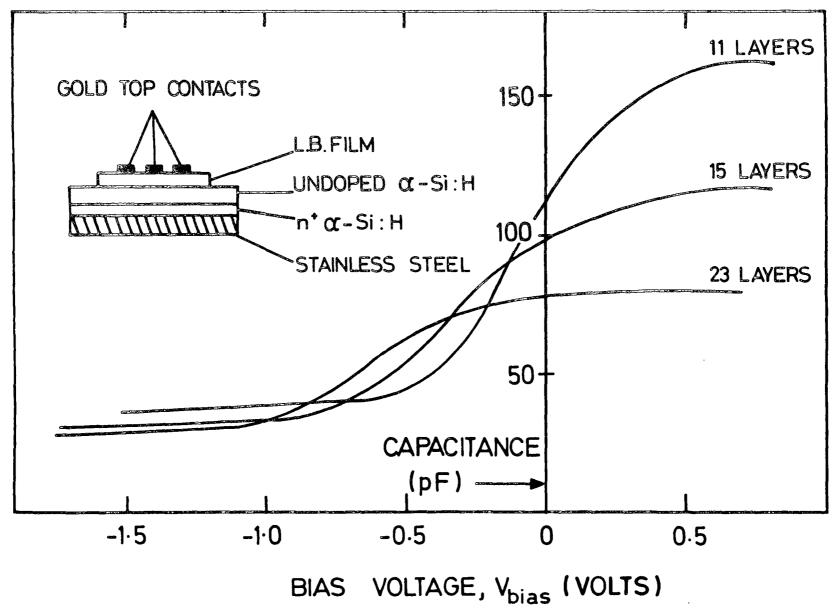

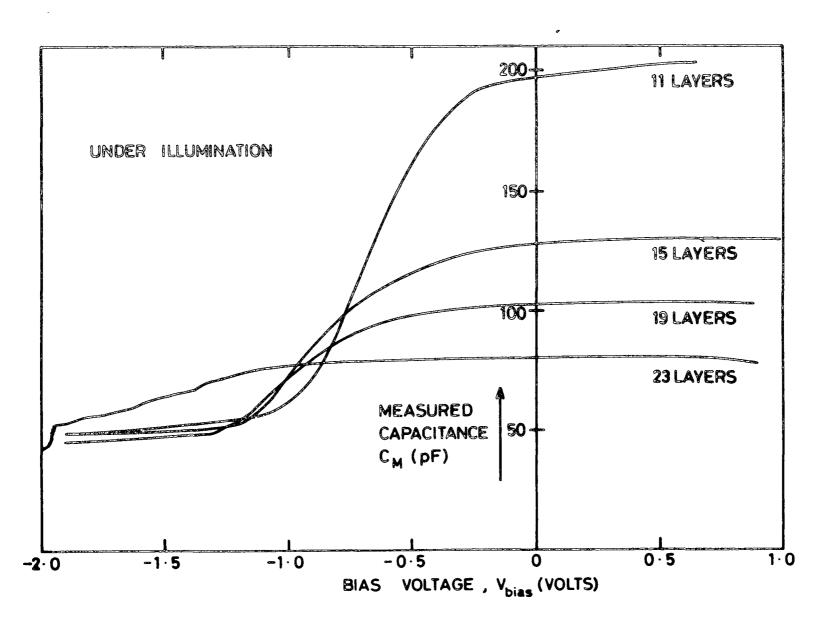

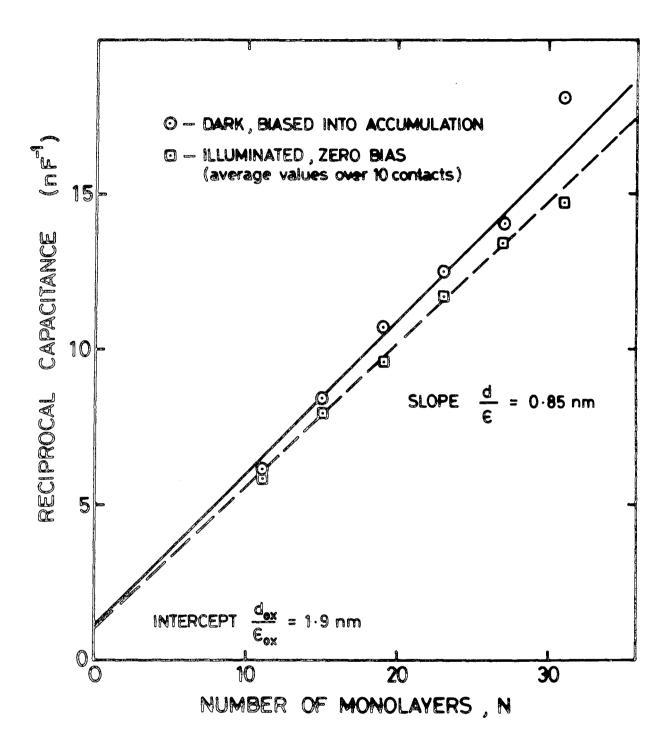

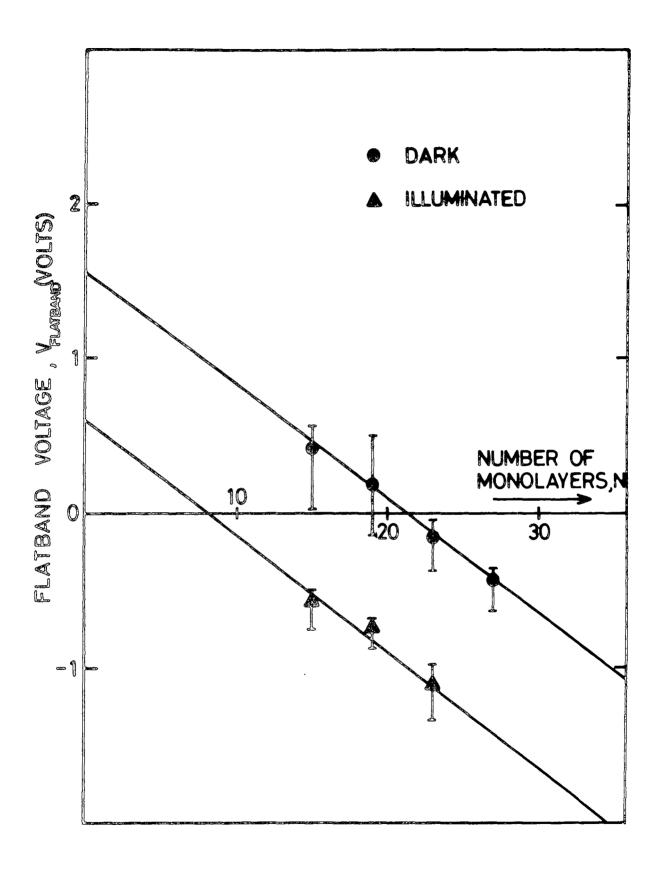

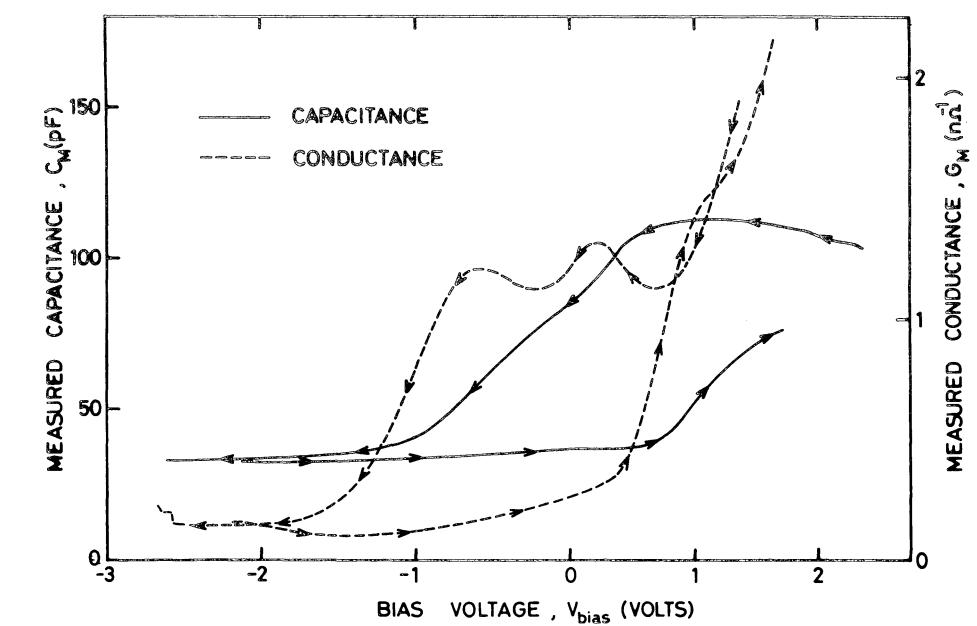

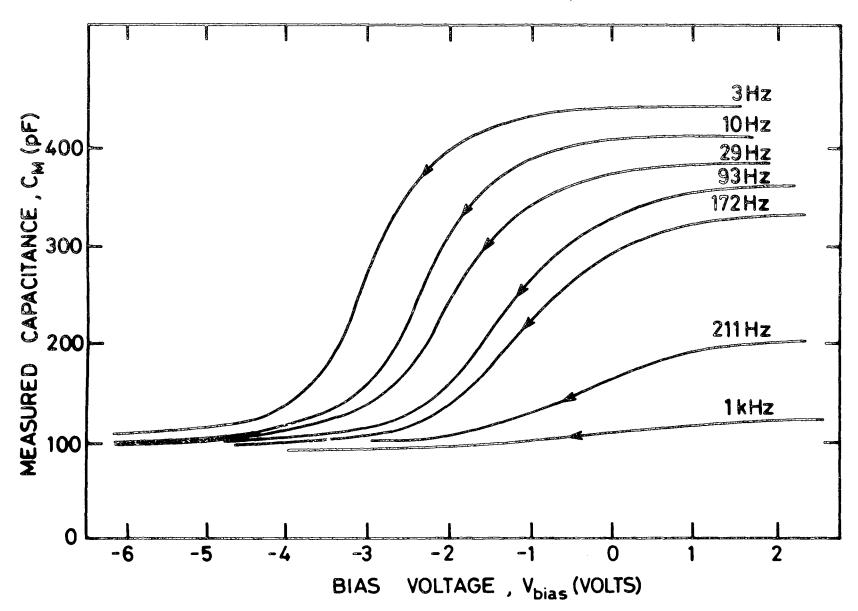

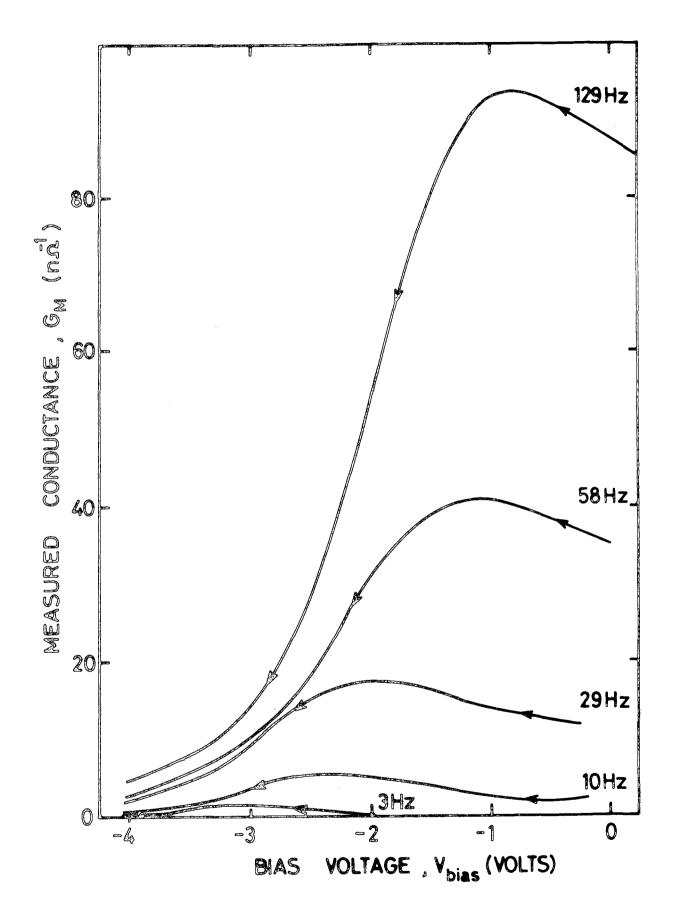

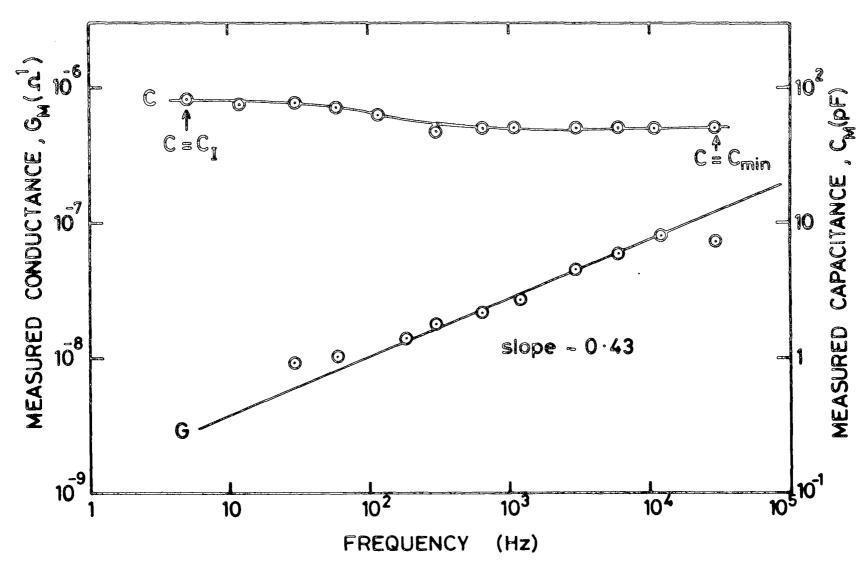

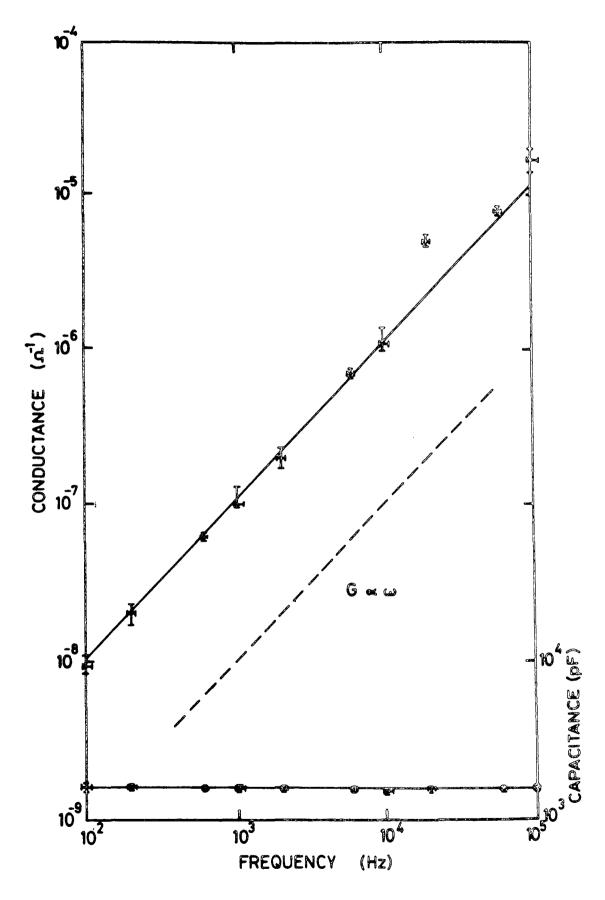

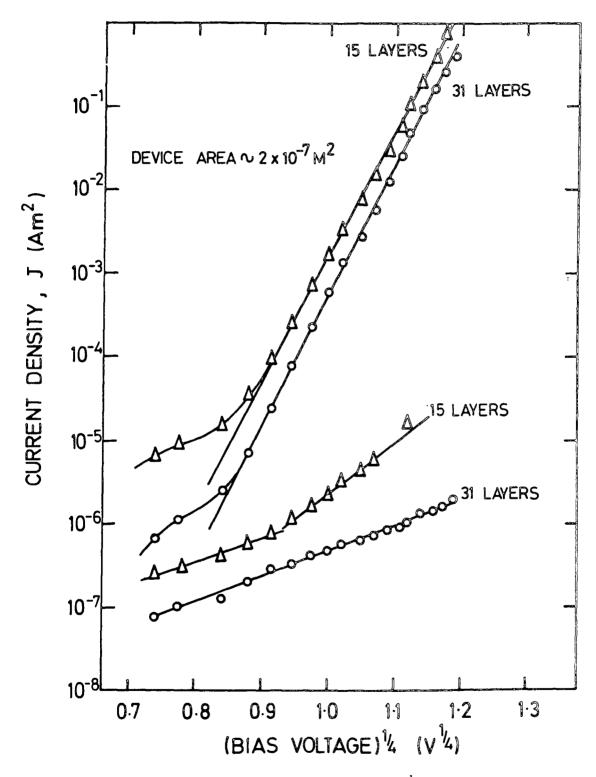

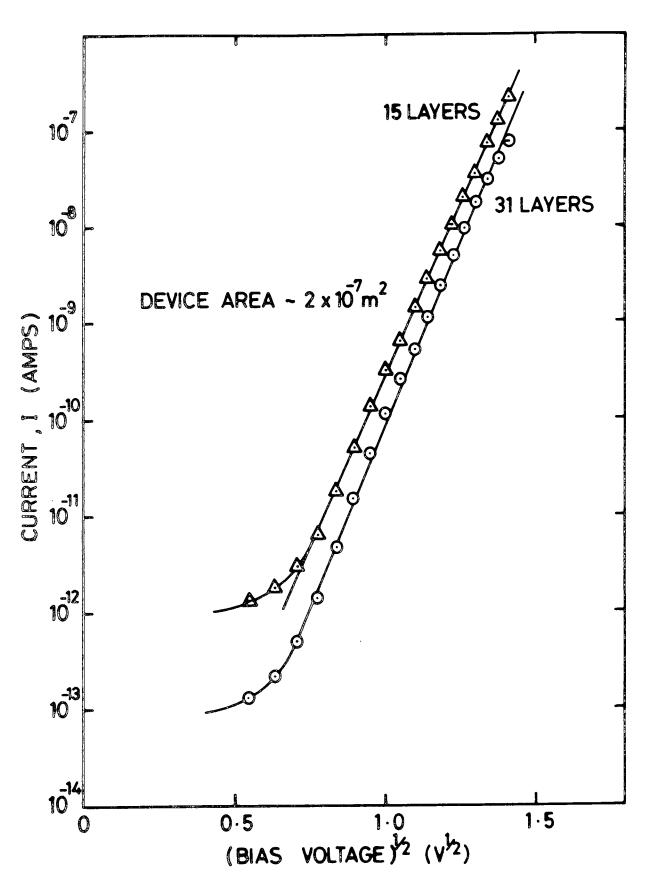

Fig. 2.10 Temperature dependence of Hall mobility for four n-type samples (1, 2, 5 and 7) and three p-type samples of glow discharge  $\alpha$ -Si:H. The samples were prepared from silane containing the following p.p.m. of  $^{\rm B}_2{}^{\rm H}_6$  (for the p-type films) and of PH $_3$  (for the n-type films): (), 2.3 x 10 $^4$ ;  $\nabla \Delta$ , 5 x 10 $^4$ ; 1, 98; 2, 304; 5, 2 x 10 $^3$ ; 7, 3 x 10 $^4$ . The solid curves are theoretical (88).