## **Durham E-Theses**

## Influence of cases on the electrical properties of mis devices

Evans, N. J.

#### How to cite:

Evans, N. J. (1986) Influence of cases on the electrical properties of mis devices, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/6866/

#### Use policy

$The full-text\ may\ be\ used\ and/or\ reproduced,\ and\ given\ to\ third\ parties\ in\ any\ format\ or\ medium,\ without\ prior\ permission\ or\ charge,\ for\ personal\ research\ or\ study,\ educational,\ or\ not-for-profit\ purposes\ provided\ that:$

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders. Please consult the full Durham E-Theses policy for further details.

> Academic Support Office, The Palatine Centre, Durham University, Stockton Road, Durham, DH1 3LE e-mail: e-theses.admin@durham.ac.uk Tel: +44 0191 334 6107 http://etheses.dur.ac.uk

INFLUENCE OF GASES ON THE ELECTRICAL

PROPERTIES OF MIS DEVICES

N. J. Evans, B.Sc.

Ph.D. Thesis, University of Durham

August 1986

#### Abstract

This thesis studies the effects of gas ambients on the electrical properties of the insulator-semiconductor interface of a MIS capacitor. A microcomputer-controlled instrumentation system has been developed to extract this information from measurement of the a.c. admittance of MOS or MIS devices. The system incorporates several novel developments in circuitry and software which enable these admittance data to be automatically collected and processed in the frequency domain by remote recalibration of the instrumentation. This advancement permits interface state density information to be calculated more quickly and accurately than has been previously possible using manually-operated equipment.

The system has been used to investigate the influence of gases on the density of interface states in a MIS capacitor, in particular the palladium/silicon dioxide/silicon structure which is sensitive to hydrogen gas. A distinct change in the distribution of surface state density across the silicon bandgap has been observed upon exposure to a hydrogen ambient. An alternative insulating layer, an organic Langmuir-Blodgett film multilayer of  $\omega$ -tricosenoic acid, has been characterised and examined, and increased sensitivity of this structure to hydrogen gas has been

> The copyright of this thesis rests with the author. No quotation from it should be published without his prior written consent and information derived from it should be acknowledged.

#### ACKNOWLEDGEMENTS

I gratefully acknowledge the help and guidance given to me during the course of this work by the staff and students of the Department of Applied Physics at the University of Durham. In particular, I should like to thank my supervisors, Dr. M.C. Petty and Professor G.G. Roberts, for all their advice and encouragement, and Drs. T.M. Ginnai, J.P. Lloyd and Mr. B. Holcroft for useful discussions. I am also grateful for the contribution of the departmental technicians, who constructed the new experimental equipment to such a high standard.

I am indebted to Thorn EMI Central Research Laboratories for their assistance in the production of this thesis, and to Ms Jean Phillips for typing the final document. My friends and colleagues in the Sensors Department have all been very helpful, especially Dr. J.F. Ross and Mr. I. Robins who have both taught a "mere physicist" a bit of chemistry.

The financial support for this project has been provided by the SERC and ICI plc, and I am also thankful to RSRE, Malvern and GEC plc for the silicon wafers used in the research; Dr. A. Barraud kindly supplied the samples of  $\omega$ -tricosenoic acid.

Finally I wish to express my gratitude to my fiance, Sarah, and my parents for all their support and encouragement (and patience!) throughout my studies.

#### CONTENTS

|           |              |          |                                     | rag |

|-----------|--------------|----------|-------------------------------------|-----|

| Chapter 1 | INTR         | ODUCTIO  | N                                   | 1   |

| Chapter 2 | PHYS         | ICS OF 1 | METAL-INSULATOR-SEMICONDUCTOR       |     |

|           | (MI S        | ) STRUC  | TURES .                             |     |

|           | 2.0          | Introd   | luction                             | 3   |

|           | 2.1          | The Io   | leal MIS Capacitor                  | 3   |

|           |              | 2.1.1    | Basic principles                    | 4   |

|           |              | 2.1.2    | Electrical properties               | 7   |

|           |              | 2.1.3    | Characteristics of non-ideal        |     |

|           | ~            | • 7      | devices                             | 9   |

|           | 2.2          | Insula   | ator Charge and Semiconductor       |     |

|           |              | Surfac   | ce States                           | 10  |

|           |              | 2.2.1    | Nature of the Silicon-Silicon       |     |

|           |              |          | Dioxide System                      | 11  |

|           |              | 2.2.2    | Electrical effects of charges       |     |

|           |              |          | in the insulator                    | 14  |

|           |              | 2.2.3    | Electrical behaviour of interface   |     |

|           |              |          | traps                               | 17  |

|           | 2.3          | Summar   | У                                   | 21  |

| Chapter 3 | CHAR         | ACTERISA | TION OF MIS DEVICES                 |     |

|           | 3.0          | Introd   | uction                              | 23  |

|           | 3.1          | Electr   | ical Characterisation of MIS        |     |

|           |              | Struct   | ures                                | 23  |

| ·         |              | 3.1.1    | Flat-band voltage calculation       | 24  |

|           | ú <b>.</b> . | 3.1.2    | Determination of insulator charge   | 24  |

|           |              | 3.1.3    | Calculation of doping concentration | 26  |

|           |              | 3.1.4    | Insulator permittivity              | 27  |

|           |              | 3.1.5    | Experimental equipment              | 29  |

|           | 3.2          | Surfac   | e State Density Evaluation          | 30  |

|           |              | 3.2.1    | Capacitance-voltage methods         | 30  |

|           |              | 3.2.2    | The a.c. conductance technique      | 33  |

|           | 3.3          | Summar   | У                                   | 37  |

|           |              |          |                                     |     |

۰.

Page

| Chapter | 4 | DEVELOPMENT | OF  | AUTOMATED | ADMITTANCE |

|---------|---|-------------|-----|-----------|------------|

|         |   | MEASUREMENT | SYS | STEM      | ·          |

| 4.0 | Introduction                                |    |  |  |

|-----|---------------------------------------------|----|--|--|

| 4.1 | Manual measurement of a.c. admittance       |    |  |  |

| 4.2 | Development of automated a.c. admittance    |    |  |  |

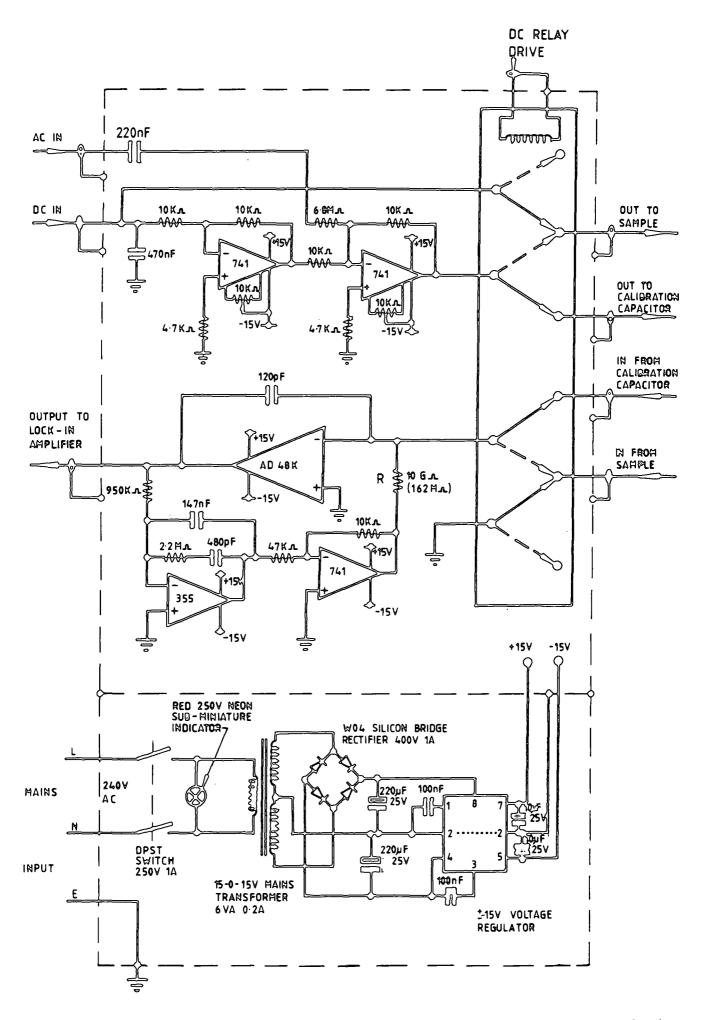

|     | instrumentation                             | 40 |  |  |

|     | 4.2.1 Lock-In Amplifier                     | 41 |  |  |

|     | 4.2.2 Voltage Calibrator                    | 43 |  |  |

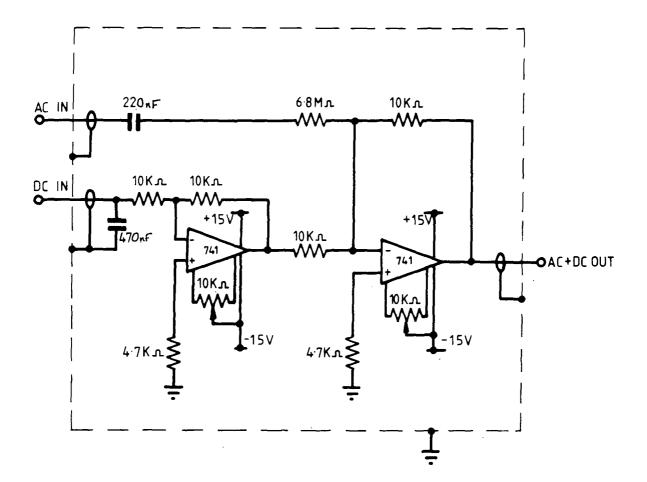

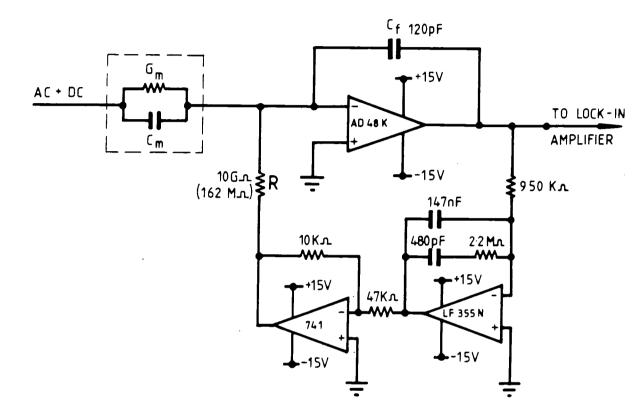

|     | 4.2.3 a.c./d.c. mixing circuit              | 43 |  |  |

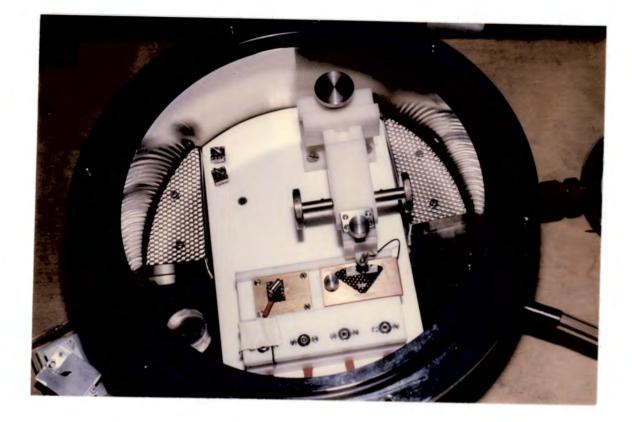

|     | 4.2.4 Relay actuator and signal multiplexer | 46 |  |  |

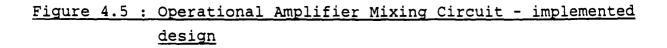

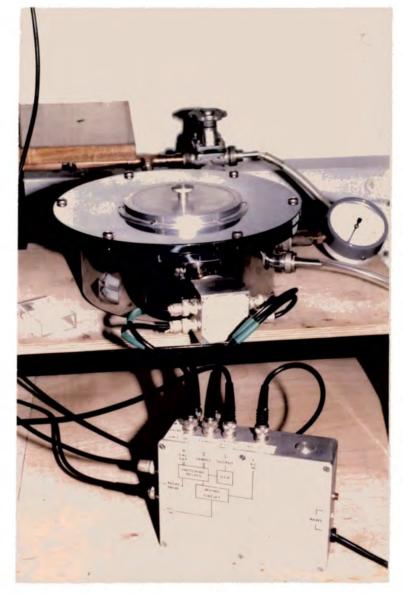

| ب.  | 4.2.5 Sample chamber                        | 47 |  |  |

|     | 4.2.6 . Yirtual earth amplifier circuit     | 49 |  |  |

|     | 4.2.7 Practical circuit considerations      | 52 |  |  |

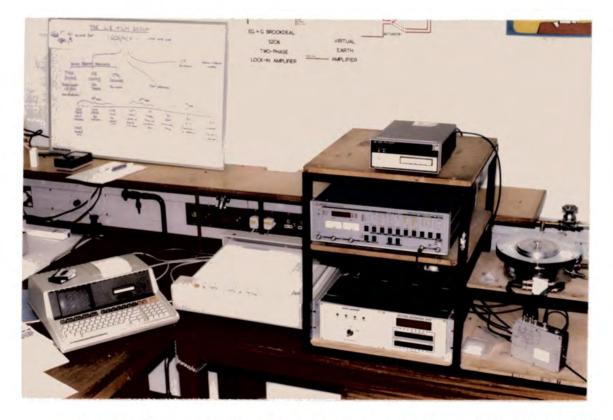

|     | 4.2.8 The microcomputer controller          | 53 |  |  |

| 4.3 | Summary                                     | 53 |  |  |

Chapter 5 SYSTEM PERFORMANCE AND EXPERIMENTAL RESULTS

۰,

| 5.0 | Introduction                       |                                                    |    |

|-----|------------------------------------|----------------------------------------------------|----|

| 5.1 | Operational Procedure and Software |                                                    |    |

|     | 5.1.1                              | PSD calibration routine                            | 56 |

|     | 5.1.2                              | Data acquisition                                   | 56 |

|     | 5.1.3                              | Analysis of data and N ss                          |    |

|     |                                    | determination                                      | 57 |

|     | 5.1.4                              | Software                                           | 58 |

| 5.2 | Perfor                             | mance Assessment and Results with                  |    |

|     | real M                             | IOS device                                         | 63 |

| ֥ - | 5.2.1                              | Accuracy of measurement                            | 63 |

|     | 5.2.2                              | Characterisation of "standard"                     |    |

|     |                                    | MOS device                                         | 66 |

|     | 5.2.3                              | Checking results with manual system                | 68 |

|     | 5.2.4                              | Critical Appraisal of N $_{ m ss}$ - $\psi_{ m s}$ |    |

|     |                                    | determination method                               | 69 |

| 5.3 | Summar                             | у                                                  | 71 |

Page

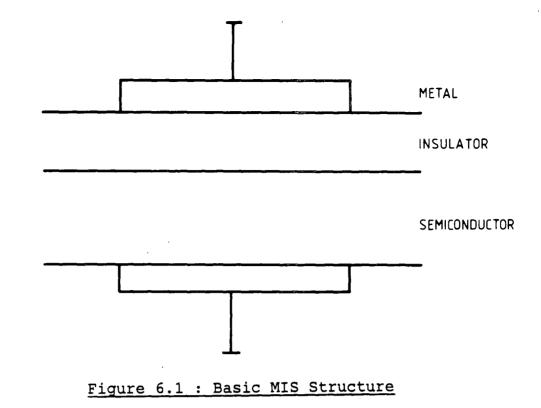

#### Chapter 6 GAS EFFECTS ON PALLADIUM-GATE MOS STRUCTURES

|           | 6.0  | Introduction                                |    |

|-----------|------|---------------------------------------------|----|

|           | 6.1  | Hydrogen Interactions with Pd-gate MOS      |    |

|           |      | devices                                     | 74 |

|           |      | 6.1.1 Work function changes                 | 74 |

|           |      | 6.1.2 Changes in surface state distribution | 75 |

|           | 6.2  | Experimental Details                        | 76 |

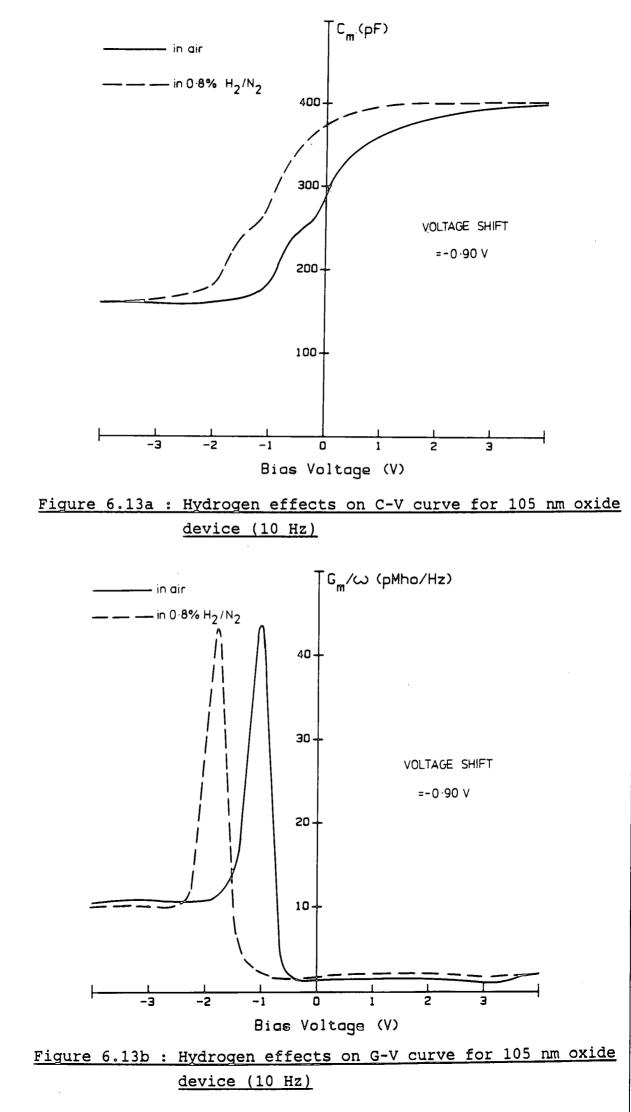

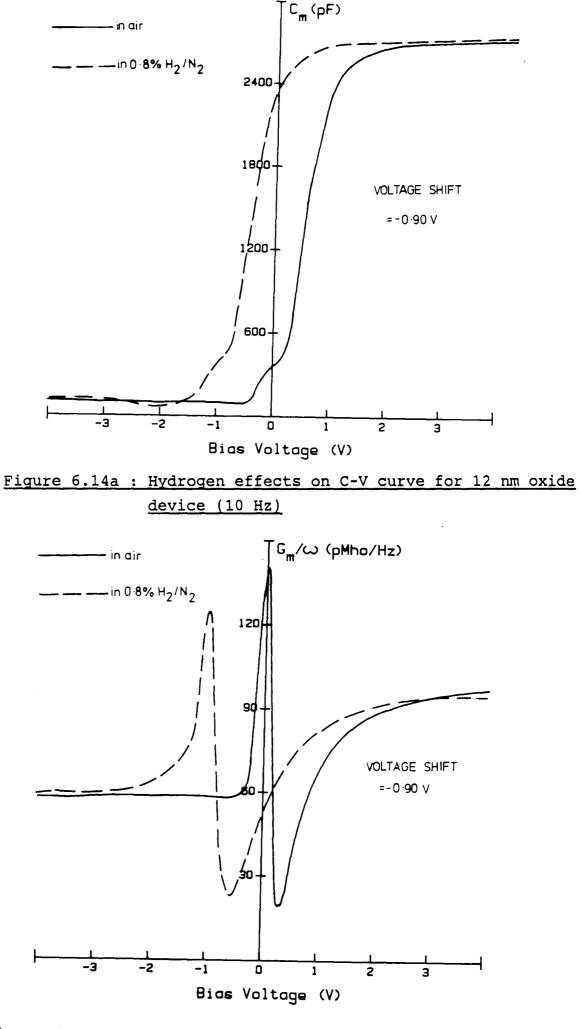

|           | 6.3  | Results and Discussion                      | 77 |

|           |      | 6.3.1 Device characterisation               | 77 |

|           |      | 6.3.2 Influence of hydrogen on MOS devices  | 79 |

|           | لىر  | 6.3.3 Effects of annealing                  | 80 |

|           |      | 6.3.4 Discussion of hydrogen results        | 81 |

|           | 6.4  | Summary and Suggestions for further work    | 82 |

| Chapter 7 | LANG | AUIR-BLODGETT (LB) FILM DEVICES             |    |

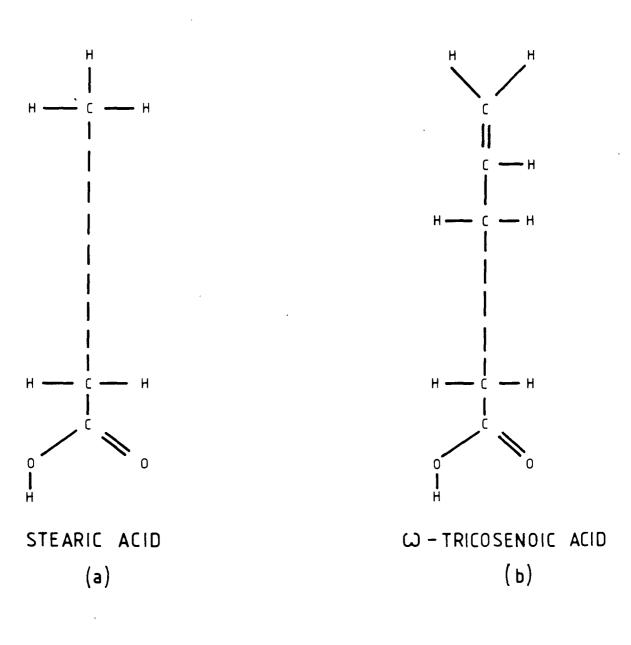

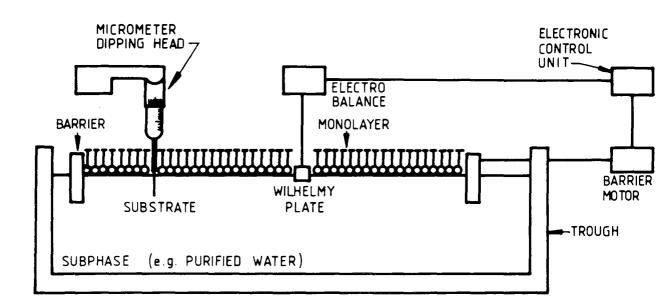

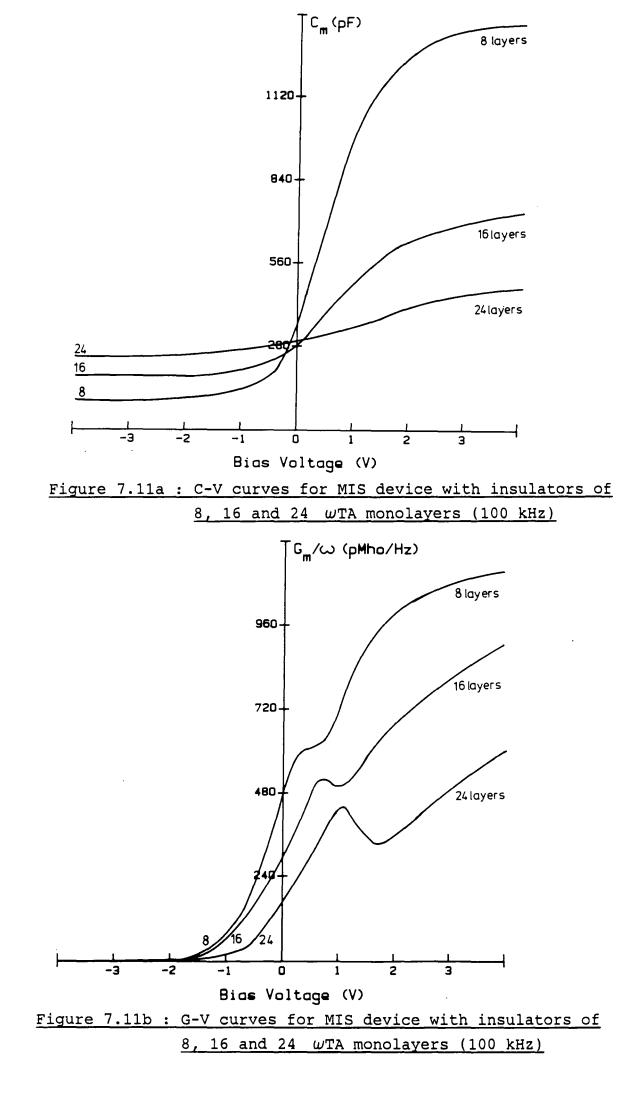

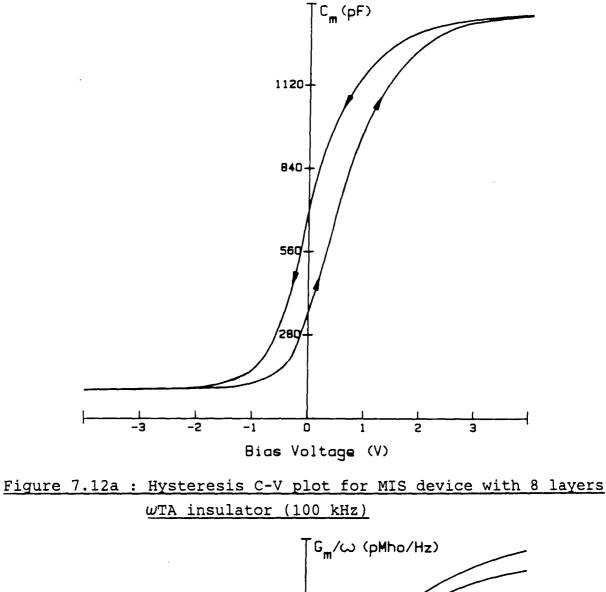

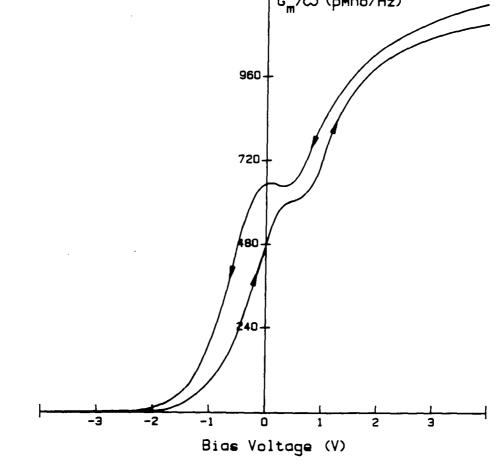

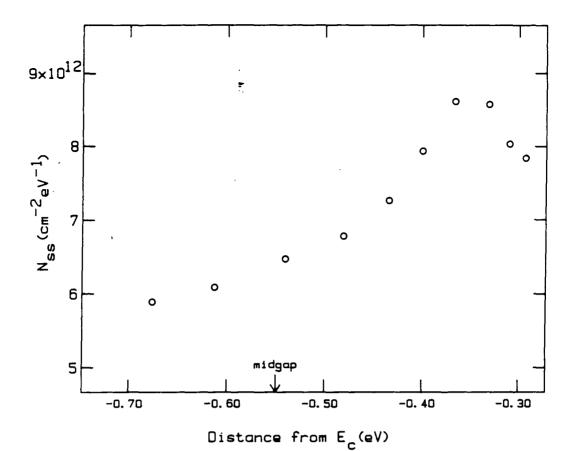

#### 7.0 85 Introduction 7.1 86 Langmuir-Blodgett Film Deposition 7.1.1 LB Film Materials 86 87 7.1.2 Langmuir trough instrumentation 7.1.3 Film deposition procedure 88 90 7.1.4 Automated LB film deposition 7.2 Experimental Details 91 7.3 93 Results and Discussion 93 7.3.1 Preliminary studies 7.3.2 Electrical characterisation of 94 ωTA LB film insulators ÷., . 7.3.3 Effects of WTA insulators on MIS 96 device properties 97 7.3.4 Influence of WTA LB films on silicon surface states 7.3.5 Aging effects on interface state density 98 7.3.6 Effects of hydrogen gas on wTA LB 99 film devices 100 7.4 Summary

#### Chapter 8 CHARGE INCORPORATION IN LB MULTILAYES

|          | 8.0    | Introduction                                 |                                       |     |  |

|----------|--------|----------------------------------------------|---------------------------------------|-----|--|

|          | 8.1    | Sample preparation and preliminary experimen |                                       |     |  |

|          | 8.2    | Discus                                       | Discussion of Experimental Results    |     |  |

|          |        | 8.2.1                                        | General observations                  | 103 |  |

|          |        | 8.2.2                                        | Moisture effects                      | 104 |  |

|          |        | 8.2.3                                        | Influence of subphase pH              | 105 |  |

|          |        | 8.2.4                                        | Effects of counterions in the         | 106 |  |

|          |        |                                              | subphase                              |     |  |

|          |        | 8.2.5                                        | Calculation of charge density         | 106 |  |

| 8.3 Theo |        |                                              | eoretical model and calculation of    |     |  |

|          |        | trapped charge                               |                                       |     |  |

|          |        | 8.3.1                                        | Modified theory for double dielectric | 107 |  |

|          |        |                                              | structure                             |     |  |

|          |        | 8.3.2                                        | Calculations and Results              | 110 |  |

|          | 8.4    | Summary                                      | y and Suggestions for further work    | 112 |  |

|          |        |                                              |                                       |     |  |

| 9        | CONCLU | JSIONS                                       |                                       | 113 |  |

|          |        |                                              |                                       |     |  |

REFERENCES

. چه

Chapter

۰.

APPENDICES

Appendix A : Program Listings

Appendix B1: Silicon Pd-MOS Device Preparation

Appendix B2: LB Film Device Preparation

Appendix C : Computer-controlled Langmuir Trough

116

#### CHAPTER 1 : INTRODUCTION

There is currently a great deal of interest in the development of a wide range of transducers for accurate measurement of physical properties in order to effectively interface electronic equipment to the real world. One structure which is well-suited for this purpose is the metal-insulator-semiconductor (MIS) capacitor, as its electrical properties may be altered by external influences Impurities or defects either inherent in the on the device. semiconductor material or introduced during device processing may create trapping levels at the insulator-semiconductor boundary which interact with mobile carriers in the semiconductor, thus changing the admittance characteristics of the device. We have been particularly interested in the effects of different gases on these interface (or surface) states with a view to developing a sensitive gas detection system.

The electrical nature of these MIS devices is described in chapter 2 by first considering the properties of an ideal device and by expanding this theory to allow for additional charges in the structure introduced by impurities in the insulator and at the semiconductor surface. In chapter 3, the methods used to determine the electrical characteristics of the MIS capacitor are considered, and the measurements necessary for evaluating the surface state density  $(N_{cc})$  distribution are discussed. The most accurate is the conductance technique of Nicollian and Goetzberger, in which the a.c. admittance properties of the device are recorded. However, the standard approach is time-consuming in practice because of the large amount of data which must be collected and the need to calibrate the instrumentation at each measurement frequency. In this work, an instrumentation system has been developed to reduce the time and effort involved in surface state evaluation. These savings have been accomplished by using a microcomputer to automatically recalibrate the equipment, take admittance readings and interpret these data for  $N_{ss}$  calculation. In addition, a number of improvements in the electronic signal-processing circuitry have been incorporated into

-1-

the design. Details of the instrumentation and hardware developments are given in chapter 4 whilst the operational procedure and software are discussed in chapter 5 along with an assessment of the system performance.

The degree to which the electrical characteristics of MIS devices are influenced by the ambient surrounding the device is a subject of great controversy. One area which has received particular attention is the well-recognised hydrogen response of palladiumgate silicon dioxide/silicon structures. Some workers have indicated that surface states are affected by the presence of hydrogen gas, but others believe that this is not so. The instrumentation system developed in this work has been used to measure the electrical properties of Pd/SiO<sub>2</sub>/Si capacitors in order to resolve this argument, and a distinct change in surface state density has been observed upon exposure to a hydrogen atmosphere; these experiments are reported in chapter 6. In an attempt to increase the magnitude of this response, MIS structures incorporating a Langmuir-Blodgett (LB) film insulator have been investigated. The electrical characteristics of the LB film material,  $\omega$ -tricosenoic acid, have been measured, and the effect of external influences (such as moisture, film preparation and storage conditions) on the device properties have been examined. Increased sensitivity to hydrogen gas has been indicated, and the results obtained with these organic multilayer structures are detailed in chapters 7 and 8.

- 2 -

#### 2.0 Introduction

The metal-insulator-semiconductor (MIS) capacitor is perhaps the most important structure used for studying the electrical properties of semiconductor devices. By far the most investigated and best understood system is the silicon - silicon dioxide combination, and this chapter will consider in the main the properties of this MOS (metal-oxide-semiconductor) structure, although the concepts presented here are equally applicable to devices of other insulator and semiconductor materials.

Most oxidised silicon surfaces and many other similar systems contain a number of trapping levels close to the oxide-semiconductor interface (surface states) which will influence the electrical behaviour of MIS devices. Although the density of surface states for thermally-oxidised silicon can be as low as  $10^9 \text{ cm}^{-2} \text{eV}^{-1}$  with careful preparation <sup>(1)</sup>, some four or five orders of magnitude lower than that of "bare" silicon surfaces, these may still have a significant effect upon the electrical properties of a practical device.

In order to understand the characteristics of practical MIS devices, we shall first consider the "ideal" MOS capacitor and then examine the nature and behaviour of "real" structures.

#### 2.1 The ideal MOS Capacitor

For the purpose of conciseness, the theoretical discussions presented below will be limited to consideration of n-type semiconductors only; all samples examined in the experiments reported in this thesis were based on n-type silicon. However, the theory is very similar for p-type semiconductors, and the reader is referred to some of the many texts on semiconductor physics for further information (1, 2). Throughout this chapter, unit area is assumed when discussing charge, capacitance and density of states.

- 3 -

#### 2.1.1 Basic Principles

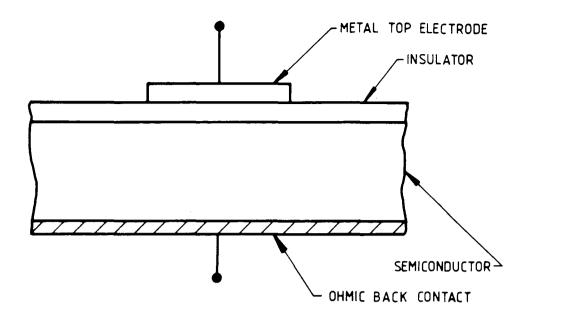

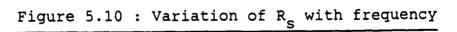

The cross-section of a MIS capacitor is shown in figure 2.1 and consists of a semiconductor substrate on top of which lies an insulating layer. A metal electrode is deposited onto the insulator, and the metal-insulator-semiconductor structure is completed by making an ohmic back contact to the semiconductor. In the case of a silicon MOS device, the insulator is a layer of thermally oxidised silicon grown on a silicon single crystal. This structure was first used to investigate silicon surfaces by Terman<sup>(3)</sup>, and other researchers<sup>(4, 5)</sup>.

To be termed "ideal", a MOS capacitor must possess the following properties:

- The semiconductor substrate is uniformly doped and has no defect levels

- 2) The oxide is free of space charges

- The oxide is an insulator of infinite electrical resistance

- 4) There is no energy difference between the metal and the semiconductor work functions at zero applied bias.

This last condition may be described mathematically for n-type semiconductors by

$$\phi_{\rm ms} = \phi_{\rm m} - (\chi + (E_{\rm c} - E_{\rm v})/2q - \psi_{\rm B}) = 0$$

(2.1)

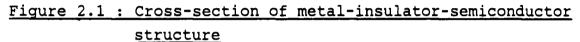

and the corresponding energy-band diagram is depicted in figure 2.2; q is the electronic charge,  $\phi_m$  the metal work function,  $\chi$  the semiconductor electron affinity and  $\psi_B$  the potential difference between Fermi level E<sub>F</sub> and intrinsic Fermi level E<sub>i</sub>. E<sub>c</sub> and E<sub>v</sub> represent the edges of the conduction and valence bands respectively. With no applied voltage, the energy bands are flat and the metal and semiconductor Fermi levels are aligned - this is called the flat-band condition.

- 4 -

### Figure 2.2 : Energy band diagram for n-type ideal MIS device with zero applied bias

When a d.c. bias voltage is applied to the device, electrons in the metal will flow towards or away from (depending on the polarity) the metal-insulator junction, causing a net charge  $Q_m$ at this interface. Consequently, there will be a build-up of oppositely-charged carriers near the semiconductor-insulator interface which will result in the bending of energy bands in the semiconductor. The total semiconductor space charge  $Q_{sc}$  will equal the charge  $Q_m$  on the metal electrode. The amount of band bending is measured with respect to the energy of the intrinsic Fermi level  $E_i$  in the bulk of the semiconductor, and is represented by the electrostatic potential at the semiconductor surface,  $\psi_s$ .

Electron and hole concentrations at this point are given by:

$$n = n_{o} \exp(q \psi_{o} / kT)$$

(2.2a)

and

$$p = p \exp(-q\psi_c/kT)$$

(2.2b)

where  $n_0$  and  $p_0$  are the densities of electrons and holes in the semiconductor bulk, k is the Boltzmann constant, and T the absolute temperature.

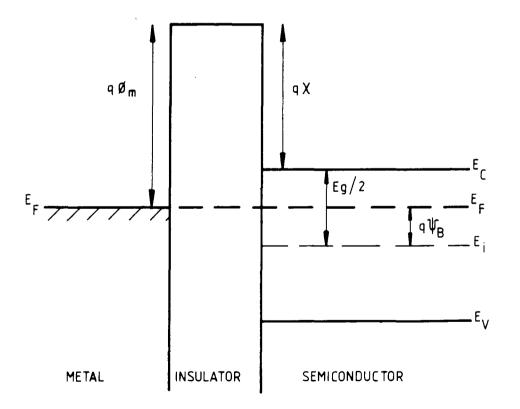

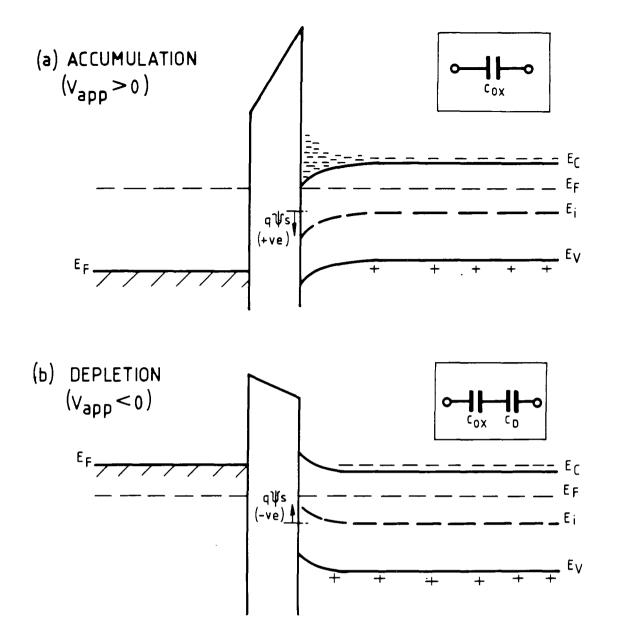

Varying degrees of band bending may be achieved by changing the voltage V applied to the MOS structure. Conventionally V is defined as the potential between the metal top electrode and the semiconductor back contact (i.e. V is positive if the metal field plate is more positive than the semiconductor). The possible ranges of surface potential for n-type semiconductors are illustrated in figure 2.3. These are:

#### Accumulation (Fig. 2.3a)

$\psi$  > 0 : enhanced electron concentration at the interface  ${}^{\rm s}$

Flat-band (shown in Fig. 2.2)

$\psi_s = 0$ : electron and hole concentrations equal to intrinsic values

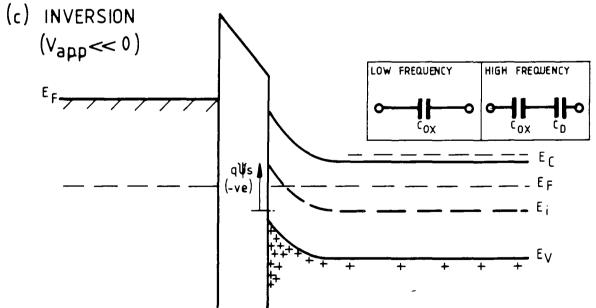

Figure 2.3 : Energy band diagrams for n-type ideal MIS device with applied bias (Insets show equivalent electrical circuits)

Depletion (Fig. 2.3b)

$0 > \psi_{s} > 2\psi_{B}$ : depleted electron concentration at the interface

Inversion (Fig. 2.3c)

$$\psi_{s} < 2\psi_{B}$$

: enhanced hole (minority-carrier) concentra-

tion at the interface

It is clear from the above that the carrier concentration in the semiconductor\_space-charge region will change as the energy bands are influenced by applied bias. The total charge per unit surface area may be determined by integration of the one-dimensional Poisson equation or invoking Gauss' law. For electrons, this procedure yields the relationship (2, 6)

$$Q_{sc} = \pm \frac{\varepsilon_s}{\lambda_D} - \frac{2kT}{q} - G\left(\psi_s, \frac{p_o}{n_o}\right)$$

(2.3)

(positive for  $\psi_s < 0$ , negative for  $\psi_s > 0$ ).  $\varepsilon_s$  is the semiconductor dielectric permittivity, and the abbreviations  $\lambda_D$  (the extrinsic Debye length) and G ( $\psi_s$ ,  $p_o/n_o$ ) are given by

$$\lambda_{\rm D} = \left(\frac{2kT\varepsilon_{\rm s}}{N_{\rm d}q^2}\right)^{\frac{1}{2}}$$

(2.4a)

and

$$G\left(\frac{\psi_{s}}{s}, \frac{P_{o}}{n_{o}}\right) = \pm \left\{ \exp\left(\frac{q\psi_{s}}{kT}\right) - \frac{q\psi_{s}}{kT} - 1 + \frac{P_{o}}{n_{o}} \left[ \exp\left(-\frac{q\psi_{s}}{kT}\right) + \frac{q\psi_{s}}{kT} - 1 \right] \right\}^{\frac{1}{2}} \quad (2.4b)$$

$\mathrm{N}_{\mathrm{d}}$  is the semiconductor doping concentration.

The differential capacitance of the space-charge region is defined as (2, 7)

$$C_{\rm D} = \frac{\partial Q_{\rm sc}}{\partial \psi_{\rm s}} = \frac{\varepsilon_{\rm s}}{\lambda_{\rm D}} \frac{1 - \exp(q\psi_{\rm s}/kT) + \frac{P_{\rm o}}{n_{\rm o}} \left[\exp(-q\psi_{\rm s}/kT) - 1\right]}{G\left(\frac{\psi_{\rm s}}{r_{\rm o}}, \frac{P_{\rm o}}{n_{\rm o}}\right)}$$

(2.5)

This relationship satisfactorily describes the depletion and weak inversion conditions, under which all experiments reported below were performed. (A more general treatment of the space charge capacitance, which is also valid for accumulation and strong inversion, has been presented in an article by Brown and Gray (8), to which the reader is referred; however, this work will not be reproduced here).

#### 2.1.2 Electrical Properties

÷.,

The simple MOS device discussed in the previous section may be considered as a series connection of the oxide capacitance,  $C_{ox}$ , and the space charge capacitance,  $C_{D}$ . The total capacitance of the structure is thus:

$$C = \frac{C C C}{C_{ox} + C_{D}}$$

(2.6) or  $\frac{1}{C} = \frac{1}{C_{ox}} + \frac{1}{C_{D}}$  (2.6a)

and any applied voltage will appear partly across each region, according to the relation

$$V_{app} = V_{ox} + \psi_{s}$$

(2.7)

${\tt V}_{\rm ox}$  is the voltage across the oxide layer, and is given by

$$V_{\text{ox}} = \frac{Q_{\text{sc}}}{C_{\text{ox}}}$$

(2.8)

where  $Q_{sc}$  is the semiconductor space charge as defined in equation 2.3.

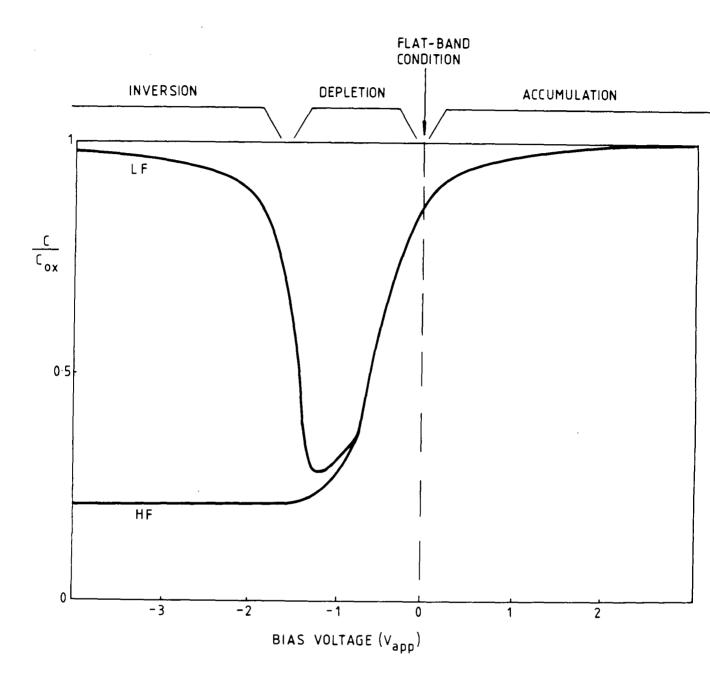

The relationship between MOS capacitance and bias voltage is best illustrated by considering the insets of figure 2.3 and the typical capacitance-voltage (C-V) curve <sup>(7)</sup> shown in figure 2.4. This is obtained by applying a d.c. bias perturbed by a small a.c. signal to the sample and measuring the device capacitance <sup>(7, 1, 2)</sup>. The four bias regions described above (section 2.1.1) may be distinguished. In <u>accumulation</u>, the total capacitance is close to the oxide capacitance since the space charge capacitance of the semiconductor is large (i.e. charge is concentrated close to the oxide/semiconductor interface). At the <u>flat-band</u> condition,  $V_{app} = 0$ , the space charge is more spread out into the semiconductor and adds a series capacitance, obtained by expanding the exponential terms in equation 2.5, of

$$C_{D(fb)} = \frac{\sqrt{2\varepsilon_s}}{\lambda_D}$$

(2.9)

which reduces the total capacitance of the structure. This space charge region grows wider as the majority carriers are depleted, and there is a further decrease in MOS capacitance. In the <u>depletion</u> regime, equation 2.5 becomes

$$C_{D(dep)} = \left[\frac{qN_d\varepsilon_s}{2(\Psi_s - kT/q)}\right]^{\frac{1}{2}}$$

(2.10)

In the <u>inversion</u> region, the enhanced minority carrier concentration at the interface influences the total device capacitance, but its effect-is dependent upon the frequency of the applied signal. At low frequencies (typically below IHz) the minority carriers are able to respond to the applied a.c. ripple and consequently the total capacitance rises to close to the oxide capacitance. (Again, charge is concentrated close to the interface, effectively "short-circuiting" the space charge region). However, at high frequencies (typically >10 kHz) these carriers cannot follow the a.c. excitation; they are in equilibrium with the d.c. bias. The differential space charge capacitance  $C_{D(inv)}$  saturates in the inversion region at the value given by equation (2.10) and the total capacitance remains low.

The shape of the C-V characteristics varies for different semiconductor doping densities and insulator thicknesses. Goetzberger<sup>(9)</sup> has published sets of C-V plots, surface potential versus applied voltage data and flat band capacitance values, all calculated with respect to these two parameters, for the ideal metal-SiO<sub>2</sub>-Si system. These curves may be applied to other insulators by simply rescaling to allow for the different dielectric permittivity<sup>(2)</sup>.

#### 2.1.3 Characteristics of non-ideal devices

In a real MIS capacitor, the C-V curves will be altered from the idealized case considered above due to work function differences between the metal and semiconductor, dipole layers in the device structure, charges in the insulator and trapping states at the insulator/semiconductor interface.

Where there is a non-zero work function difference between metal and silicon (i.e. in equation 2.1,  $\phi_{ms} \neq 0$ ) the Fermi levels in figure 2.2 will not be aligned and the energy bands will be bent even without any applied bias <sup>(5)</sup>. This "built-in" voltage changes the surface potential relationship to applied bias; equation 2.7 becomes

$V_{app} = V_{ox} + \psi_{s} + \phi_{ms}$ (2.11)

The flat-band condition will be restored when the applied bias equals the barrier potential

$$V_{FB} = \phi_{ms} \sim (2.12)$$

which will offset this additional voltage. The shape of the C-V characteristic will be unaltered from the ideal response (figure 2.4) but there will be a parallel shift of the curve along the voltage axis by an amount equal to  $V_{FB}$  (which is called the flat-band voltage).

- 9 -

If any dipole layers exist (10) at the metal-insulator interface, or within the insulator, then equations 2.11 and 2.12 become

$$V_{app} = V_{ox} + \psi_{s} + \phi_{ms} - \frac{\sigma t}{\varepsilon_{ox}}$$

(2.11a)

and

$$V_{FB} = \phi_{ms} - \frac{\sigma t}{\varepsilon_{ox}}$$

(2.12a)

where  $\sigma$  is the charge density,  $\epsilon_{ox}$  the absolute permittivity of the oxide, and t the distance of separation of the two sheets of charge.

Charges in the insulator will invoke a similar shift in the C-V curves, and possibly a hysteresis<sup>(7)</sup> in the measured characteristics due to mobile ions. Interfacial trapping sites distort the curve shape as well as stretching out the response with respect to the voltage axis. These effects are explained more fully in the following sections.

#### 2.2 Insulator Charge and Semiconductor Surface States

Because of its importance as a test structure to assess the performance and behaviour of semiconductor devices, the MIS capacitor has been extensively modelled and investigated by a great number of researchers; a book by Nicollian and Brews<sup>(1)</sup> deals solely with this subject, and is recommended as a comprehensive reference.

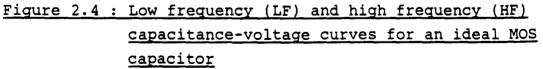

The discussion of the ideal MIS capacitor presented above does not consider any charges in the structure apart from the majority and minority carriers in the semiconductor. In a real device, however, a number of additional charges may be present <sup>(2)</sup> due to imperfections and impurities either inherent in the semiconductor crystal and/or insulating layer or introduced into these materials during device processing (Figure 2.5).

- 10 -

- FIXED SURFACE CHARGES

- + IONISED TRAPS

- O MOBILE IONS

- **X** SURFACE STATES (INTERFACE STATES)

- BULK SEMICONDUCTOR TRAPS

# Figure 2.5 : Possible states and charges in a non-ideal MIS device

\_

This section concentrates particularly on the nature of the possible states and charges in the insulator and at the semiconductor surface of a SiO<sub>2</sub>-Si MOS capacitor, and their effect on the electrical properties of the device.

#### 2.2.1 Nature of the silicon - silicon dioxide system

Any interruption of a perfect crystal lattice by a defect or impurity will result in the creation of extra energy levels that may be situated in the "forbidden" bandgap of the material. If these levels occur in the bulk of the material they are referred to as bulk traps; at the surface or at an interface with another material they are known as surface or interface states.

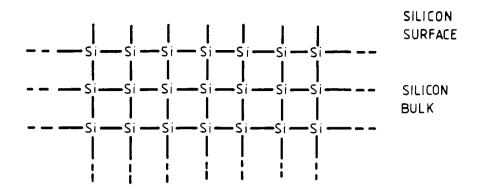

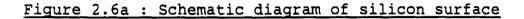

In silicon crystals, the surface states are believed to be due to a dangling bond at each atomic site at the semiconductor surface<sup>(11)</sup>, as depicted schematically in figure 2.6a. The growth of silicon dioxide reduces the number of surface states by saturating some of these dangling bonds; however, some will remain unbound as a result of the mis-match between the Si and SiO<sub>2</sub> lattices (Figure 2.6b). Two types of defects are considered <sup>(7)</sup> to be present in this interface region : fast states which can exchange charge very quickly with free carriers in the silicon and which are located within lnm of the Si-SiO<sub>2</sub> interface<sup>(12)</sup>, and very slow (effectively fixed charge) states distributed over a region of the oxide some 5 to 10nm from the interface. Many different models <sup>(1, 13, 14)</sup> have been developed in attempts to explain the origins of these two types of defect states. Although there is no experimental support for any one theory alone, the model described below seems to be supported by many researchers<sup>(15, 13,16)</sup>.

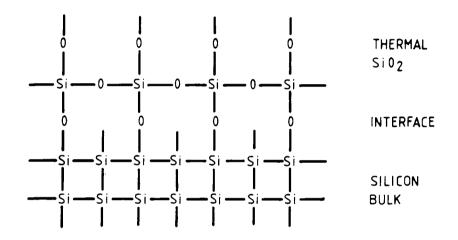

This model considers trivalent silicon defects in the siliconsilicon dioxide interface region which results in an unsatisfied bond  $^{(17)}$ . Figure 2.7 shows three possible defects. The Si site is considered to be a surface state whilst the others are hole traps; due to its interaction with the silicon surface, the Si trap is a much slower state and is believed to be the source of the fixed oxide charge.

- 11 -

Figure 2.6b : Schematic diagram of the silicon-silicon dioxide interface

Si - Si0<sub>2</sub> interface region

The theory is favoured because of its ability to account for the changes in surface state density observed after low- and high-temperature annealing in hydrogen (7, 15) and due to the results of extensive electron paramagnetic resonance (EPR) studies (16, 18, 19) of the SiO<sub>2</sub>-Si interface; the latter research has identified a number of possible defects which are suggested to be responsible for the energy levels observed within the bandgap of the devices.

The number of states present at a silicon - silicon dioxide interface is dependent upon the crystal orientation, since this will determine the number of unsatisfied bonds at the silicon surface prior to oxidation <sup>(1)</sup>. For example, there are almost twice as many available bonds per unit area in the <111> plane than in the <100> plane<sup>(7)</sup>; and hence the interface state density and oxide charge will be a minimum in devices of <100> orientation.

In addition to the intrinsic properties discussed above, a number of external factors will influence the density of states within the SiO<sub>2</sub>-Si structure. Dislocations and miscrosplits in the silicon surface, either present in the crystal or introduced during processing (e.g. in diffusion, ion-implanation or wafer-sawing steps), will increase the number of defects <sup>(7)</sup> in the interface region. It is also believed that increased oxide charge is a result of damange produced by strain or radiation effects <sup>(1)</sup>, or possibly by the introduction of metal impurities which diffuse into the oxide (e.g. during top electrode evaporation). The situation is further complicated by the presence of mobile ions (e.g. Na<sup>+</sup>,K<sup>+</sup>) in the oxide layer <sup>(20, 21)</sup>; these are mainly responsible for the instabilities observed <sup>(22)</sup> in the C-V measurements of SiO<sub>2</sub>-Si devices and may also add to the number of surface states <sup>(23, 24)<sup>2</sup></sup> and fixed surface charges<sup>(2)</sup> in the structure if they drift to the SiO<sub>2</sub>-Si interface.

The conditions under which the oxide is grown on the silicon surface are critical to the purity of the oxide and to the properties of the interface region. The oxidation processes in ambients of dry oxygen, wet oxygen and steam are described in detail elsewhere<sup>(1)</sup>, but the essential steps in each process are the sawe. After oxygen has been introduced into the oxide already grown, it must diffuse

- 12 -

through this layer in order to react with silicon at the interface to form  $SiO_2^{(25)}$ .

Oxidation in a dry oxygen atmosphere produces the purest oxide, but at low temperatures ( $<1000^{\circ}$ C) the interface state density is high since the reaction rate is slower - consequently, many unsaturated silicon bonds are produced and there is excess oxygen in the oxide. Lower interface state densities may be obtained by high-temperature oxidation ( $>1000^{\circ}$ C) as the faster reaction time will produce SiO<sub>2</sub> predominately. In both cases, a low temperature annealing process is desirable to further reduce interface and oxide charge<sup>(1)</sup>.

Steam oxidation is a faster process and produces oxides with a greatly reduced number of interface states <sup>(26)</sup>. As well as leaching out impurities from the oxide and silicon surface, it is believed that water vapour chemically reacts with unsaturated silicon bonds at elevated temperatures. This may be described in terms of the trivalent silicon model discussed above by considering the following reaction:

$$-Si + H_2 0 - Si - OH + H$$

(2.13)

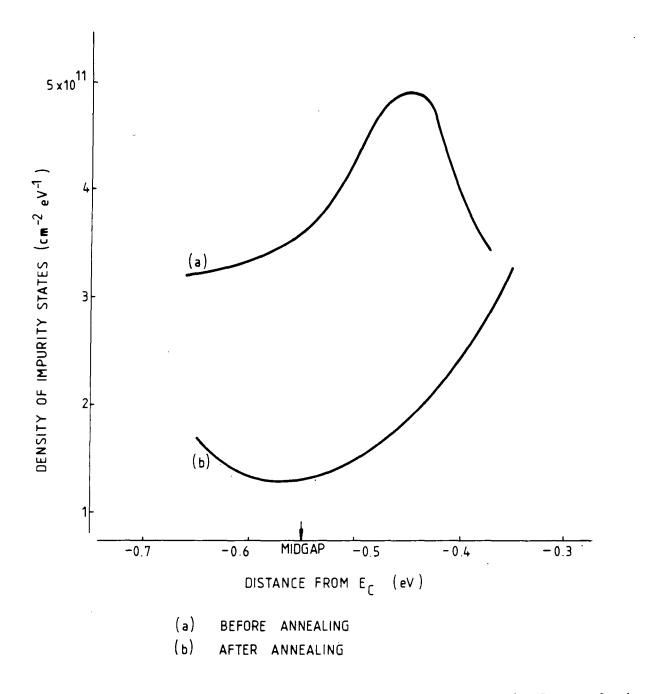

This reaction will decrease the number of dangling bonds by the formation of silanol groups. Oxides grown in this way exhibit a surface state distribution which is of reduced magnitude and U-shaped across the semiconductor bandgap (27). Figure 2.8 illustrates the effect of annealing on surface state density distribution (28).

The density of interface states produced by either of the oxidation processes mentioned above may be further improved by annealing in the presence of hydrogen; for an oxide grown in dry oxygen this will also result in the characteristic U-shaped distribution mentioned above (1,29). Again considering the trivalent silicon model, a similar chemical reaction to (2.13)

- 13 -

may be envisaged when heating in a hydrogen atmosphere:

$$- Si + H_2 - Si - H + H$$

(2.14)

In this case the unsatisfied Si bond is effectively neutralised by capturing a hydrogen atom. The oxide charge always decreases during an annealing process regardless of the temperature. However, the interface state density will only be reduced if the annealing temperature is below about  $500^{\circ}$ C; above this temperature the hydrogen bond of the above reaction is split and an increase of surface state density occurs.

The shape of the interface state density curve is attributed to the different types of defect found at different energy levels in the bandgap. The density of states at the band edges is due to bond distortion and strain near the silicon surface  $^{(11)}$  and these are not affected by a post-oxidation anneal. The mid-gap surface state density, however, is affected by this process; dangling bond defects are responsible for states in this region  $^{(30)}$ , and these may be significantly reduced in number by hydrogen annealing, hence producing the characteristic U-shaped distribution.

So far, the discussion has been limited to the possible origins and types of defects found within the metal-insulator-semiconductor system. In the next two sections, the effects of these impurities on the electrical properties of the structure will be considered. The first part (section 2.2.2) will describe the effects of insulator charge and the second (section 2.2.3) the influence of states at the insulator-semiconductor interface.

#### 2.2.2 Electrical effects of charges in the insulator

Impurities in the insulating layer are due to insulator trapped charge, mobile ionic charge and fixed surface charge as demonstrated in figure 2.5. These parameters will change the electrical behaviour of a metal-insulator-semiconductor device; the specific case of a metal  $-Si0_2-S_i$  structure is discussed below.

- 14 -

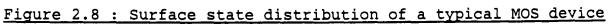

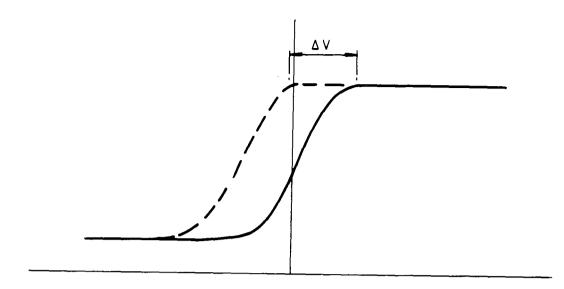

Charge trapped in the Si0 insulating oxide layer is a result of  $\frac{1}{2}$ defects present in the oxide. These defects may result in energy levels in the Si bandgap which can trap electrons or holes injected into the oxide (e.g. from the gate electrode, from the semiconductor or from electron-hole excitation), as detailed elsewhere<sup>(31)</sup>. As the charge held in these trapping centres will be constant provided that no carrier injection takes place, the only effect on the electrical characteristics of the MOS capacitor will be a lateral voltage shift (Figure 2.9a). If charge injection does occur, however (e.g. as a result of illuminating the sample, or by biasing the device into strong accumulation or inversion), then a hysteresis <sup>(20)</sup> in the measured response will be observed; i.e. the C-V characteristcis recorded with a positive voltage ramp will be shifted with respect to the curve obtained with a negative voltage ramp, as the amount of trapped charge will be different (Figure 2.9b).

The presence of mobile ions (23, 32, 33) in the oxide will also cause a hysteresis in the measured C-V curves (21). This instability is due to alkali ions  $(Na^+, K^+)$  which are usually trapped at the SiO<sub>2</sub>-Si interface but which may drift freely at elevated temperatures or under the influence of an applied electric field. Other ions (e.g. H<sup>+</sup> protons (34)) may also cause drifting effects. The change in charge distribution within the oxide again produces a shift in the flat-band voltage (22).

Fixed surface charge is generally positive and is located in a region of the oxide less than  $25^{\circ}$  from the SiO<sub>2</sub>-Si interface. This charge is affected only by the sample processing techniques and results in a permanent contribution to the flat-band voltage.

The total voltage shift of the C-V curves due to the three types of oxide charge discussed above may be written as  $^{(6)}$

$$V = -\frac{1}{\frac{1}{d_{ox} C_{ox}}} \int_{0}^{d_{ox}} x \cdot e(x) dx = -\frac{1}{x} Q_{ox} \frac{1}{d_{ox} C_{ox}} (2.15)$$

- 15 -

Figure 2.9a : Example of C-V curve showing lateral voltage shift due to flat-band voltage change (high frequency case)

### Figure 2.9b : Example of C-V curve illustrating possible hysteresis effect (high frequency case)

where  $d_{ox}$  is the oxide thickness and Q(x) represents the charge density distribution.  $Q_o$  is the total oxide charge due to trapped charge  $Q_t$ , mobile ionic charge  $Q_i$ , and fixed surface charge  $Q_f$ , such that

$$Q_{o} = Q_{t} + Q_{i} + Q_{f} = \int_{0}^{d_{ox}} e^{(x) dx}$$

(2.16)

and  $\overline{x}$  is the position of the effective charge centroid, i.e.

$$\bar{x} = \frac{1}{Q_0} \int_{0}^{d_0 x} \int_{0}^{x} x \cdot \varrho(x) dx$$

(2.17)

These equations may also be applied to multi-layer insulators, e.g. Langmuir-Blodgett films (see chapters 7 and 8).

Equation 2.11a must now be modified thus:

$$Vapp = V_{ox} + \psi_{s} + \phi_{ms} - \frac{\sigma t}{\varepsilon_{ox}} - \frac{\bar{x}Q_{o}}{\frac{d}{\sigma C_{ox}}}$$

(2.18)

and the flat-band voltage becomes:

$$V_{FB} = \phi_{ms} - \frac{\sigma t}{\varepsilon_{ox}} - \frac{\bar{x}Q_o}{\frac{d_o C}{ox ox}}$$

(2.19)

This additional term can in practice be greatly reduced by careful device processing to give lower fixed surface charge and fewer mobile ions in the oxide, and by controlling the conditions of device storage and measurement to reduce trapped charge (e.g. preventing charge injection by avoiding elevated temperatures, illumination and large bias voltages). However, as Q<sub>o</sub> may change due to the factors indicated above, flat-band voltage will be a function of device history and consequently there may be slight variations in

$V_{FR}$  over a period of time.

#### 2.2.3 Electrical behaviour of interface traps

The presence of trapping sites at or near the insulatorsemiconductor interface creates allowed energy levels with the semiconductor bandgap; these levels may exchange charge with the conduction (valence) band by capture or emission of electrons (holes). Donor-type states will exhibit positive or neutral charge when empty or filled respectively, acceptor-type states will be neutral or negatively charged under like conditions. The occupation of interface states in thermal equilibrium is determined by the Fermi-Dirac function;

$$f(E) = \left[1 + g.exp ((E-E_F - q\psi_s)/kT)\right]^{-1}$$

(2.20)

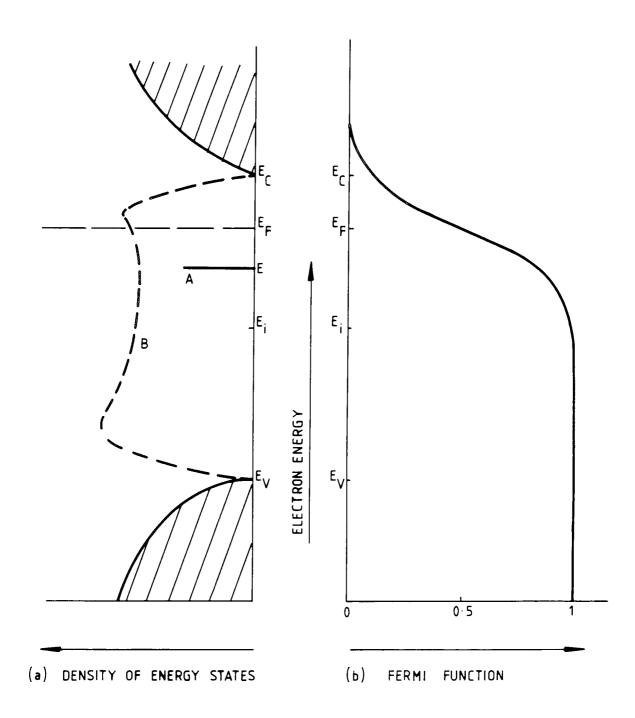

where f(E) is the probability that a state at energy level E is occupied by an electron, and g is the spin correction factor (usually 2 for donor and 1/4 for acceptor-type states). Figure 2.10 depicts the energy band diagram at the insulator/semiconductor interface region.

Changes in the occupancy of interface traps can be achieved by varying the applied bias voltage and hence the surface potential,  $\psi_s$ . Consequently, a small ( $\sim kT/q$ ) a.c. voltage applied to the device will modulate the position of the Fermi level which will cause majority carriers to be captured or emitted by interface states whose energy levels lie within a few kT/q of  $E_F$ . As this capture/emission phenomenon is not infinitely fast, there will be a time delay associated with the exchange process. This will be manifested as an energy loss at all but very low and very high signal frequencies (under which conditions all or none of the interface traps respond to the applied signal, respectively) and contributes to the ohmic losses observed in non-ideal MIS structures.

- 17 -

# Figure 2.10 : Energy band diagram at the insulator - semiconductor interface

- (a) Density of energy states across bandgap

A ≡ single level state of energy E

B ≡ continuum of states

- (b) Probability of electron occupancy across bandgap

The effects of interface charges on the C-V curve discussed in the previous sections are manifold. The capacitance will be increased by one elementary charge per state and so, therefore, will the lateral voltage shift, i.e.

$$V_{app} = V_{ox} + \psi_{s} + \phi_{ms} - \frac{\sigma t}{\varepsilon_{ox}} - \frac{\overline{x} Q_{o}}{\frac{d}{\sigma C_{ox}}} - \frac{Q_{ss}}{c_{ox}}$$

(2.21)

and

$$V_{FB} = \phi_{ms} - \frac{\sigma t}{\varepsilon_{ox}} - \frac{\bar{x}Q_{o}}{\frac{d}{\sigma c_{ox}}} - \frac{Q_{ss}}{c_{ox}}$$

(2.22)

×. ...

where Q<sub>ss</sub> is the total charge introduced by interface traps. This charge (and hence the additional capacitance term) is strongly dependent upon surface potential and so also upon applied bias; when the Fermi level is at the energy of the trap its effect will be maximised. Furthermore, the electric surface field itself is changed by the interface charge and more applied voltage is required to create the same amount of band-bending as in the ideal case. These effects are observed as a shift, a distortion and a stretchingout in the measured C-V curves.

A quantitative explanation of the electrical influences of interface traps can be obtained by considering first the admittance of a single-level state and expanding the treatment to the continuous distribution of states across the bandgap observed in real devices. Finally surface potential fluctuations will be discussed.

The admittance of the single-level state for small signal conditions may be written as (27)

$$Y_{SL}(E) = \frac{j\omega q^2}{kT} \qquad \frac{N_{SL}f_o(1-f_o)}{(1+j\omega f_o/c_n^n s_o)}$$

(2.23)

- 18 -

where  $\omega$  is the angular frequency of the applied signal,  $N_{SL}$  is the single-level state density,  $f_o$  is the value of the d.c. Fermi function,  $c_n$  is the electron capture rate, and  $n_{so}$  the electron density at the surface.

This admittance may be considered as a parallel combination of capacitance  $C_s$  and conductance  $G_p$  such that:

$$C_{s} = C_{SL} / (1 + \omega^{2} \tau_{n}^{2})$$

(2.24)

and

$$G_{p}/\omega = C_{SL} \omega \tau / (1 + \omega^{2} \tau^{2})$$

(2.25)

where the capacitance  $C_{\mbox{SL}}$  and the time constant  $\tau_n$  associated with the single-level state are given by

. م

$$C_{SL} = q^2 N_{SL} f_0 (1 - f_0) / kT$$

(2.26)

and

$$\tau_n = f_o / c_n n_{so}$$

(2.27)

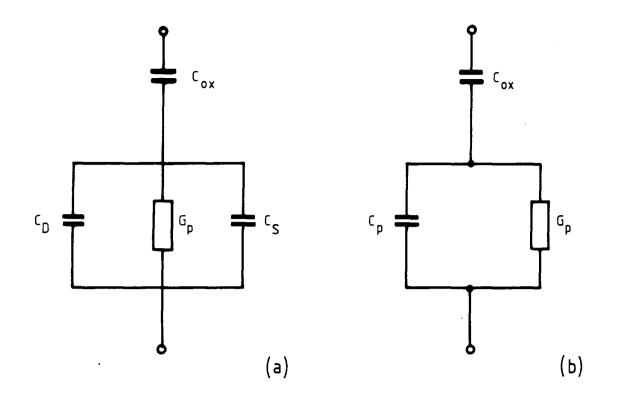

The electrical equivalent of the total system in depletion is given in figure 2.11a; the interface and space-charge region terms may be reduced to a single parallel circuit as shown in figure 2.11b, where:

$$C_{p} = C_{s} + C_{D}$$

$$(2.28)$$

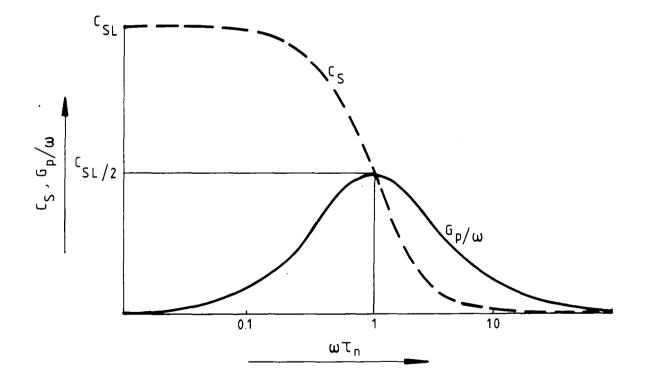

It can be seen from equation 2.25 that  $G_p/\omega$  will be a maximum when  $\omega_{\tau_n} = 1$ , and that this maximum will be

$$(G_{p}/\omega) = C_{SL}/2$$

(2.29)

A typical plot of C and G  $/\omega$  versus frequency for this singlelevel case is given in figure 2.12. Knowing the value of  $(G_p/\omega)_{max}$

Figure 2.11 : Equivalent circuits of a MIS device in depletion

Figure 2.12 : Example of  $C_s$ ,  $G_p/w$  versus frequency for single-level model

and the corresponding surface potential,  $N_{SL}$  may be calculated (from equation 2.26) for the energy level.

It is more realistic in practice to consider the case of a continuous distribution of energy states across the bandgap  $^{(35)}$ , each of which may be individually described as above. The total admittance of this arrangement,  $Y_{ss}$ , may be derived by integrating  $Y_{sL}$  over the whole range of trap energies in the bandgap:

$$Y_{ss} = \int_{E_{v}}^{E_{c}} Y_{s}(E) dE = \frac{j\omega q^{2}}{kT} \int_{V_{v}}^{E_{c}} \frac{N_{ss}f(1-f_{o})}{1+j\omega f_{o}/c_{n}} dE \qquad (2.30)$$

The result <sup>(27)</sup> may be expressed, as before, as a parallel conductance and capacitance network, where:

$$C'_{S} = q N_{ss} \arctan (\omega \tau_{m})$$

(2.31)

and

$$(G_{p}/\omega)' = q N_{ss} \ln (1 + \omega_{\tau_{m}}^{2}) / 2\omega T_{m}$$

(2.32)

$$\tau_{\rm m} = 1 / \bar{c}_{\rm n} n_{\rm so} \tag{2.33}$$

This procedure is only valid if N<sub>ss</sub> (the density of distributed interface states per electron volt) and  $\overline{c}_n$  (the average capture probability over the range of the integral) are not greatly varying functions of surface potential, i.e they may be treated as constants over a range of a few kT/q. This is generally true for most practical systems provided that the amplitude of the applied signal is small ( $\forall$ kT).

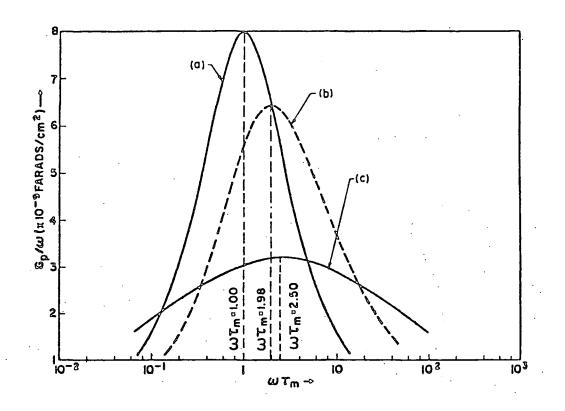

From equation 2.32 it can be calculated that the maximum Gp/ $\omega$  will occur at  $\omega \tau_m = 1.98$ .

Figure 2.13 <sup>(27)</sup> compares the normalised Gp/ $\omega$  versus  $\omega$  curves for the single-level state model (curve (a)) and the continuous model (curve (b)). In practice, however, a response similar to that shown in curve (c) is obtained, where the Gp/ $\omega$  maximum is found at  $\omega_{T}$  = 2.5. This broadening of the response is attributed <sup>(7)</sup> to fluctuations in the surface potential caused by lateral variations in the electric field due to ionized charge or localised oxide charge near the interface region and/or oxide thickness non-uniformities. Several models account for this <sup>(27, 11, 20, 36)</sup> and derive expressions for the device admittance which may only be solved by numerical techniques.

The equivalent circuits described above are valid for the device when biased in the depletion region. A more comprehensive model has been developed by Lehovec and Slobodsky <sup>(37)</sup> which describes the inversion and accumulation regions also. However, it will be seen later (Chapter 3) that by using numerical analysis techniques, the simple model discussed above is sufficient as the devices to be investigated will be biased in the depletion region only.

### 2.3 Summary

This chapter has described the electrical properties of real metal-insulator-semiconductor devices by first explaining the behaviour of an ideal MIS capacitor and then considering the effects of charges introduced by defects in the structure. The nature and origin of these charges have been related to the observed electrical characteristics. The metal-SiO<sub>2</sub>-Si system has been given specific attention because this is the structure of samples investigated in this work and also because it is the most common example of a MIS device. However, the principles discussed above may equally well be applied to many other combinations of insulator and semiconductor which are currently of interest.

- 21 -

Figure 2.13 : Calculated  $G_p/\omega$  curves versus log  $\omega \tau_m$

- (a) single-level state

- (b) continuum of states

- (c) response with surface potential fluctuations

In the next chapter, the evaluation of MIS device properties from measured electrical data and some of the methods used to extract this information will be described. In particular, experimental techniques which may be used to analyse the interface state density distribution across the semiconductor bandgap will be considered.

÷., .

× - .a

#### CHAPTER 3 : CHARACTERISATION OF MIS DEVICES

## 3.0 Introduction

The electrical behaviour of metal-insulator-semiconductor devices has been examined in chapter 2 along with the physical properties responsible for this behaviour.

In this chapter, the idea of plotting capacitance and conductance with respect to voltage and frequency will be more fully discussed, especially the use of this technique for measurement of MIS device parameters such as flat-band voltage, insulator trapped charge and doping density. Various methods to calculate interface state density distribution will be considered; in particular, the a.c. conductance technique and its application to measurement of real MIS devices are described.

# 3.1 Electrical Characterisation of MIS Structures

From the data gathered in a single capacitance-voltage scan performed on an MIS sample, a large amount of information may be extracted about the electrical properties of the device. This procedure may be repeated after a period of time or after a sample treatment operation, say, in order to determine the electrical effects of aging or of the treatment process.

The following three sections (3.1.1, 3.1.2, and 3.1.3) show how C-V plots may be used to calculate flatband voltage, insulator charge, and doping density; section 3.1.4 discusses the procedure for determing the dielectric permittivity of the insulator layer, and finally the experimental apparatus used for C-V measurement and insulator permittivity calculation is outlined (section 3.1.5). All of these analysis techniques are utilised for characterising the devices investigated later in this work. In the flat-band condition the insulator-semiconductor surface is depleted of majority carriers, and the equivalent circuit is given by a series combination of insulator and depletion capacitances as shown for the metal- $\delta i0_2$ -Si system in chapter 2 (section 2.1.2).

The oxide capacitance, C<sub>ox</sub>, may be found from the C-V plot by calculating the value of capacitance measured in strong accumulation. The depletion capacitance is given by equations 2.9 and 2.4a:

$$C_{D(fb)} = \left(\frac{\varepsilon_s A^2 q^2 N_d}{kT}\right)^{\frac{1}{2}}$$

(3.1)

The parameters  $\varepsilon_s$ , q, N<sub>d</sub>, k and T are as defined in chapter 2, but the additional A<sup>2</sup> term is introduced to relate the depletion capacitance to the device top contact area, A.

From equation 2.6, the value of measured capacitance at the flatband point is:

$$C_{fb} = \frac{C_{ox} C_{D(fb)}}{C_{ox} C_{D(fb)}}$$

(3.2)

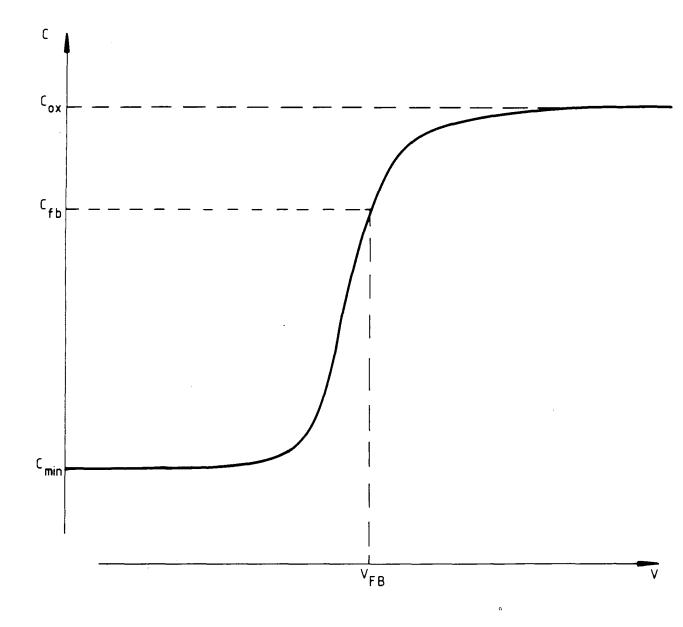

By calculating the value of  $C_{\rm fb}$  for a particular sample and determining the point on the C-V curve at which it occurs, the flat-band voltage  $V_{\rm FB}$  may be obtained (figure 3.1). This procedure may be applied to any MIS combination by inserting the appropriate electrical constants into equation 3.1.

# 3.1.2 Determination of insulator charge

The total amount of charge incorporated in a MIS device can be determined from equation 2.19 if the flat-band voltage is calculated as shown in section 3.1.1. By using a technique known as

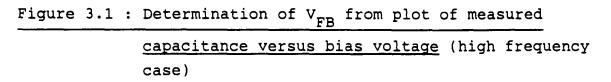

Bias-Temperature Stressing (1, 2), information about the components of the insulator charge can be obtained from the hysteresis effects on the C-V curve. The procedure is to bias the device into inversion at elevated temperature for some minutes, after which a C-V scan is performed. The sample is then held in strong accumulation (again at elevated temperature) for a similar length of time before repeating the C-V measurement. The two resulting curves are plotted as in figure 3.2 (n-type device). Curve (a) shows the C-V response after application of a negative voltage (inversion) when all mobile (positive) ionic charges have drifted to the metal-oxide interface; in this condition there is no contribution to the flat-band voltage (x = 0 in equation 2.15). Curve (b) denotes the C-V characteristics after biasing in accumuation (positive applied voltage) when all the mobile charges are at the insulatorsemiconductor interface; the flat-band voltage shift will be a maximum (as  $x = d_{ox}$  in equation 2.15):

$$\Delta V_{i} = \frac{-Q_{i}}{C_{ox}}$$

(3.3)

Hence the value of Q, may be determined.

It is generally found that curves 3.2(a) and 3.2(b) differ by no more than 0.1V as the number of mobile ions is very low for modern processing techniques <sup>(3)</sup>. However, analysing C-V curves in this way can indicate sample quality and is used as a standard process monitoring technique. Other researchers have shown how this method can be used to investigate trapping effects <sup>(4)</sup> and polarisation of the insulator <sup>(5)</sup>. In addition, any changes in insulator charge introduced by subsequent device treatment can be observed by the effect upon flat-band voltage.

The main contribution to the flat-band voltage shift from the "ideal" case is the oxide fixed charge,  $Q_f$ . If the number of ionised traps is small, and assuming that there are no dipole layers of charge in the insulator, then  $Q_f$  may be calculated from equations 2.16 and 2.19:

(a) AFTER APPLYING INVERSION (NEGATIVE) BIAS

(b) AFTER APPLYING ACCUMULATION (POSITIVE) BIAS

Figure 3.2 : Schematic plot of hysteresis effect on high frequency C-V curve due to mobile ionic charge (insets show position of charge in MIS structure)

$$V_{FB} = \phi_{ms} - \frac{Q_f}{C_{OX}}$$

(3.4)

In practice, this calculation will not be exact due to the other charges present, but although these cannot be totally ignored their effect will be small and so a reasonable approximation to  $Q_f$  can be obtained.

It should also be noted that in the above calculations no allowance is made for the effects of interface states. The interface state charge can be determined by other means (see section 3.2) and the  $Q_{ss}$  term in equation 2.22 removed, enabling  $Q_i$  and  $Q_f$  to be obtained as above.

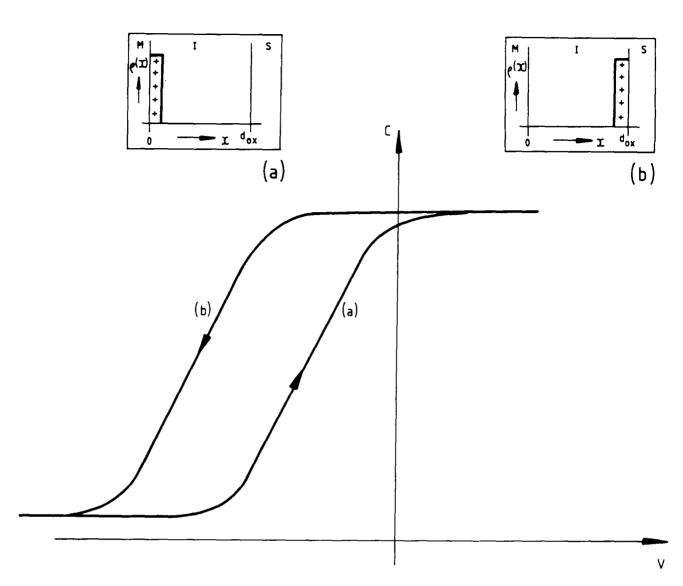

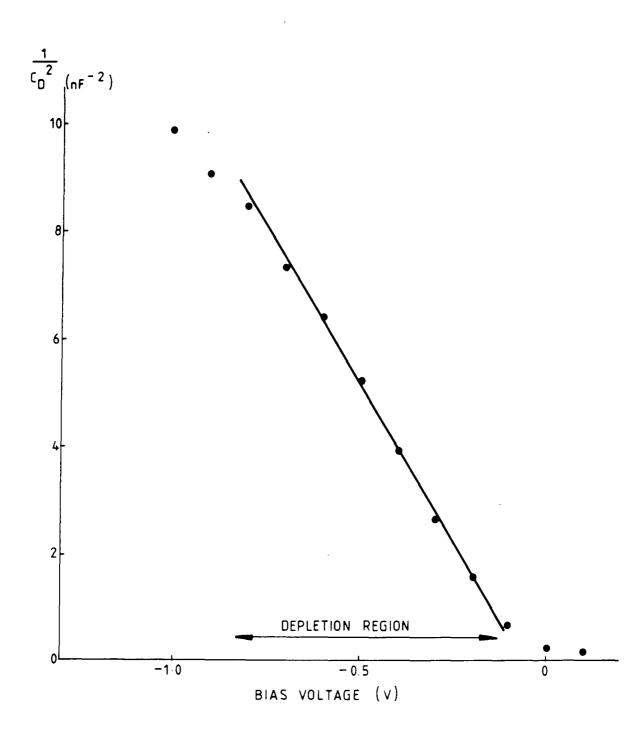

## 3.1.3 Calculation of doping concentration

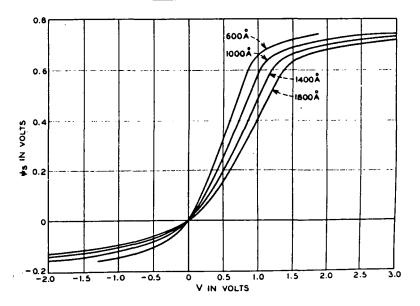

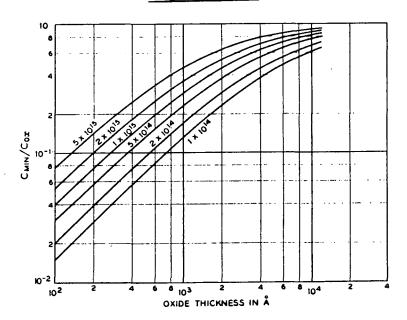

The doping impurity density within the semiconductor must be known for the region near the insulator-semiconductor interface in order to calculate the MIS device parameters. An average doping concentration can be determined from a high-frequency C-V plot <sup>(6)</sup> by measuring the minimum capacitance C which occurs in the inversion min region as described in chapter 2 (section 2.1.2). Curves have been computed which relate capacitance, surface potential, applied voltage, oxide thickness and doping concentration for the metal- $SiO_2$ -Si system <sup>(6, 7)</sup>; similar curves may be obtained for other insulator-semiconductor combinations. An example of these plots (7) is shown in figure 3.3 for p-type silicon (conversion to n-type silicon is achieved by reversing the voltage axes). If the oxide thickness is known, the doping density,  $N_d$ , can be calculated by measuring  $C_{\min}$  and  $C_{ox}$ , the oxide capacitance (see figure 3.1), and reading from a set of curves such as figure 3.3c the value of  $N_d$ which corresponds to the C /C ratio thus determined.

An alternative evaluation of N<sub>d</sub> is given by examining the high frequency C-V curve in a different way. When a bias voltage V is applied to a MIS device in depletion, equation 2.10 becomes:

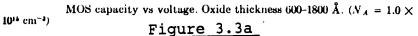

Surface potential vs voltage. Oxide thickness 600-1800 Å.  $(N_A = 1.0 \times 10^{15} \text{ cm}^{-3})$ Figure 3.3b

Figure 3.3c

$$C_{\rm D} = \left(\frac{qN_{\rm d}\varepsilon_{\rm s}^{\rm A}^{2}}{2(\psi_{\rm s}+V-kT/q)}\right)^{\frac{1}{2}}$$

(3.5)

or

$$\frac{1}{C_{\rm D}^2} = \frac{2}{qN_{\rm d}\varepsilon_{\rm s}A^2} (V+\psi_{\rm s}-kT/q)$$

(3.5a)

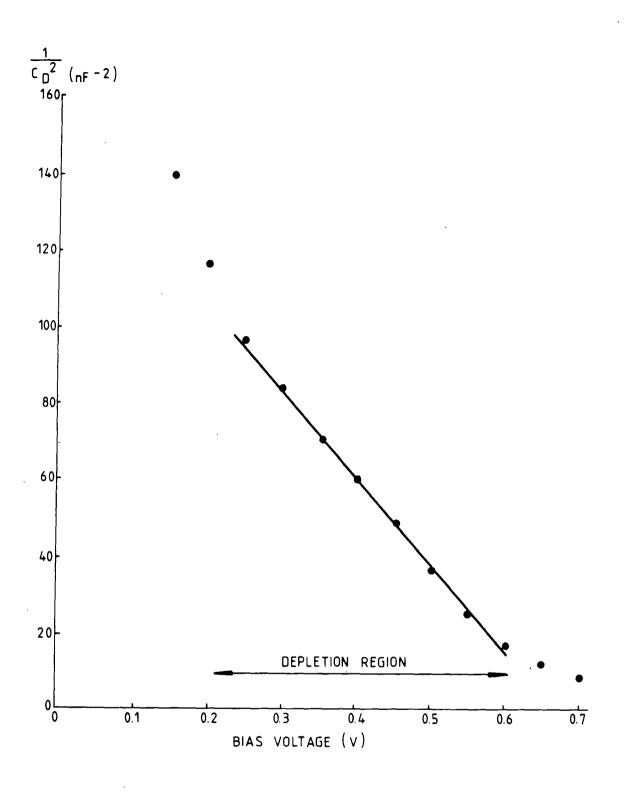

and the doping concentration may be extracted from the slope of a plot of  $1/C_D^2$  versus V. ( $C_D$  is obtained from the measured capacitance C by using equation 2.6a). This treatment can be extended to obtain impurity profiles for non-uniformly doped semiconductors and to correct for the effects of interface states <sup>(8)</sup>; however, the average value of  $N_d$  as determined above is sufficient for most practical calculations of MIS device characteristics.

## 3.1.4 Insulator permittivity

Information on the electrical properties (such as dielectric constant) of SiO<sub>2</sub> and other commonly-used insulators is readily available in textbooks and tables of constants. However, when a novel insulating material is incorporated into a MIS device, it is necessary to calculate these values experimentally, as they are often required for determination of other device parameters. The simplest structure for effecting measurements on an insulator is a metal-insulator-metal (MIM) "sandwich" which can be fabricated by depositing a film of the insulating material onto a metal and then evaporating a metal top electrode.

The electric permittivity,  $\varepsilon$ , of the insulating layer may be obtained from measurement of the MIM device capacitance, C, as

$$C = \frac{A\varepsilon}{d} = \frac{A\varepsilon}{r_{0}}\varepsilon}{\frac{1}{d}}$$

(3.6)

- 27 -

where A is the device area and d the thickness of the insulating layer. The absolute permittivity of the insulator is generally expressed as the product  $\varepsilon_r \varepsilon_o$ , where  $\varepsilon_o$  represents the permittivity of free space and  $\varepsilon_r$  is a constant for the material which is known as the relative permittivity or the dielectric constant.

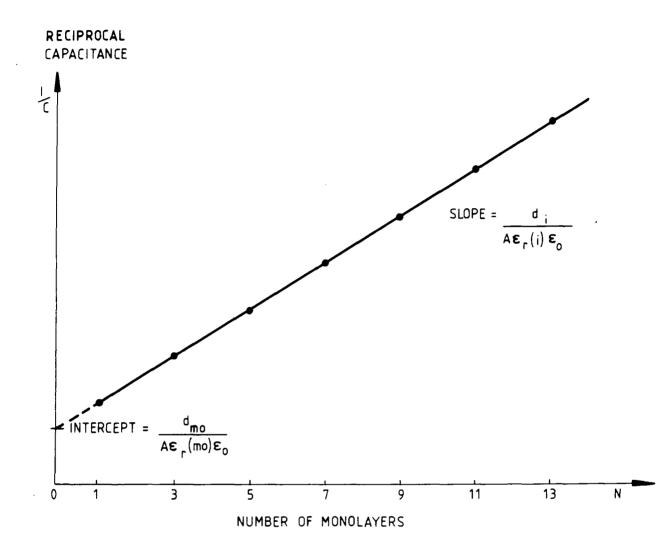

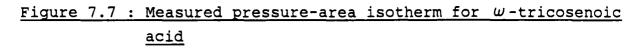

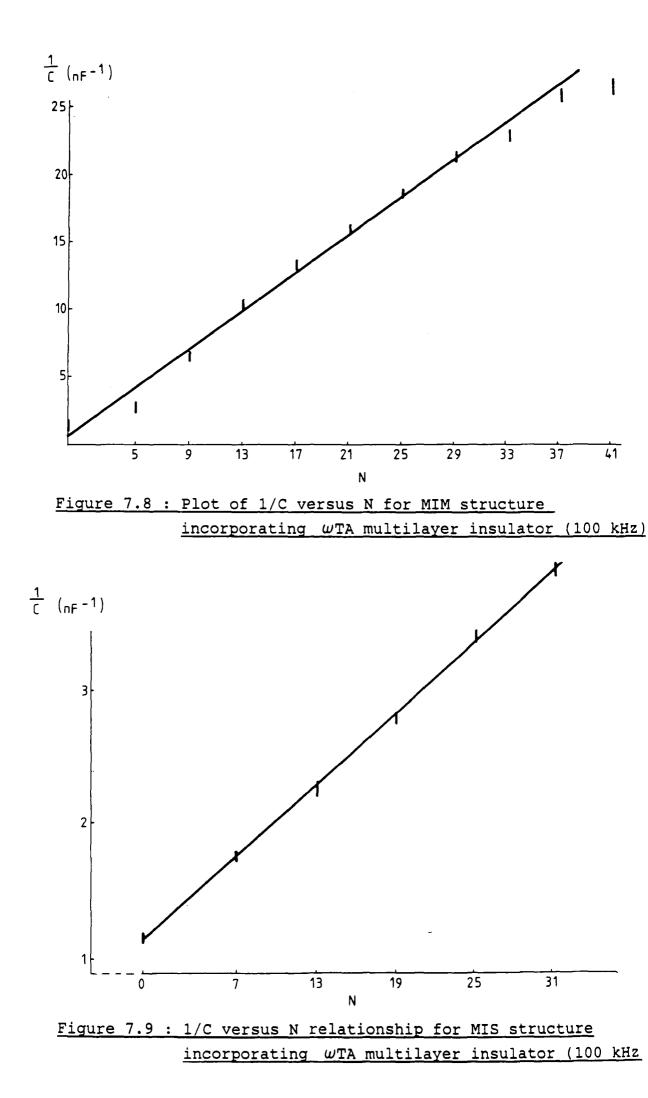

To determine the relative permittivity accurately a number of capacitance measurements should be carried out on MIM structures of different insulator thickness. Plotting C against 1/d should give a straight line of slope  $A\epsilon_{ro} \epsilon_{ro}$  passing through the origin. In the case of Langmuir-Blodgett film insulators (which are discussed in chapters 7 and 8), where the insulating layer can be built up in multiples of a monolayer thickness, equation 3.6 may be rearranged and rewritten as:

$$\frac{1}{C} = \frac{Nd_{i}}{A\varepsilon_{r}\varepsilon_{o}}$$

(3.7)

Here, N is the number of monolayer of thickness  $d_i$  deposited onto the metal electrode. A plot of 1/C against N will give  $\varepsilon_r$ (in this case the straight line slope is  $d_i/A\varepsilon_r\varepsilon_0$ ).

In some plots of 1/C versus N (or d) for MIM devices a non-zero intercept may be recorded. This is often due to oxidation of the surface of the deposited metal electrodes resulting in the formation of a region of metal oxide (e.g.  $Al_2O_3$  on Al electrodes). As a consequence, the apparent insulator thickness is increased by a constant amount which contributes an extra series capacitance; modifying equation 3.7 for this effect, we find

$$\frac{1}{C} = \frac{Nd_{i}}{A\varepsilon_{r}(i)\varepsilon_{o}} + \frac{d_{mo}}{A\varepsilon_{r}(mo)\varepsilon_{o}}$$

(3.8)

where  $\mathcal{E}_{r}(i)$  is the relative permittivity of the LB film insulator,  $\mathcal{E}_{r}(mo)$  is the value of  $\mathcal{E}_{r}$  for the metal oxide and d is the thickness of the metal oxide. It can be seen that the slope of the 1/C - N line will be unchanged, enabling  $\mathcal{E}_{r}(i)$  to be calculated as before. In addition, the thickness of the metal oxide layer may be determined from the value of the intercept with the 1/C axis if  $\epsilon_{r}(mo)$  is known (since at this point  $d_{i} = 0$ ). A typical 1/C - N characteristic for a metal - LB film - metal structure is shown to illustrate this feature (figure 3.4).

. . .

The technique for evaluating the dielectric constant of an insulating layer has so far been applied only to a MIM structure. However, should it not be possible to fabricate such a device, experiments may be carried out on a MIS structure biased into strong accumulation (under this condition, just the insulator capacitance will be measured, as there will be no depletion region), and  $\varepsilon_r$  (i) determined as above.

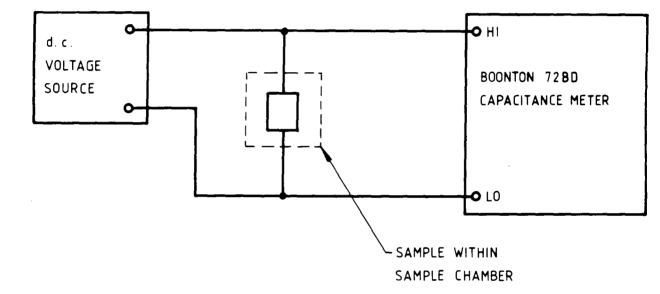

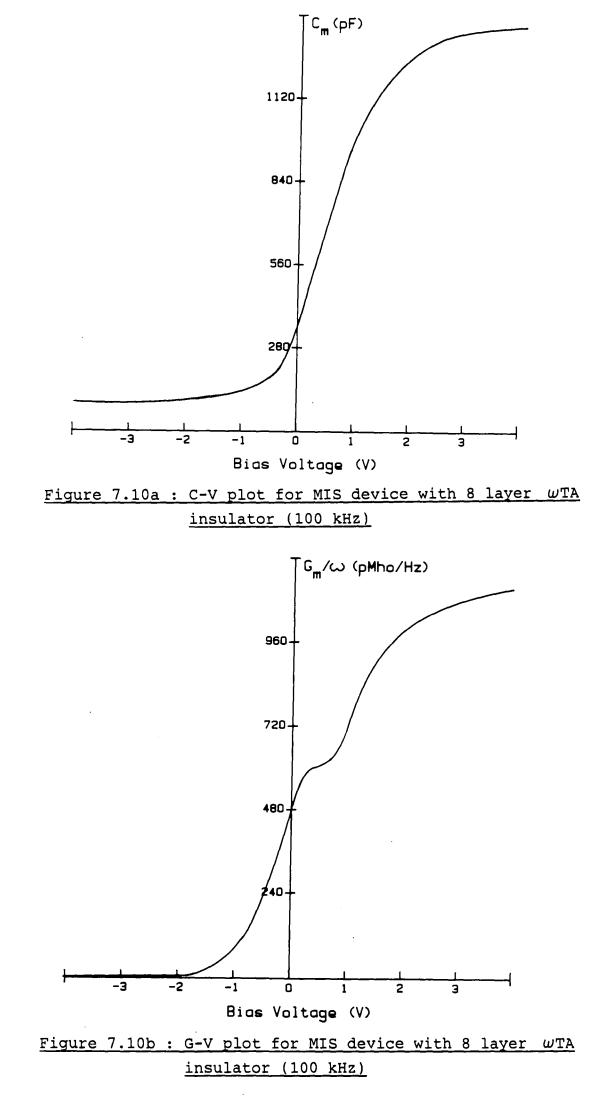

### 3.1.5 Experimental equipment

Capacitance-voltage plots are obtained by the method outlined in section 2.1.2 in which the sample is perturbed by a small a.c. signal whilst applying a d.c. voltage ramp. By using a phasesensitive detector the a.c. admittance of the device may be measured and resolved into its capacitive and conductive components, and hence the C-V and G-V characteristics determined. An automated experimental system was especially developed to facilitate the recording of these and other parameters and is fully described, along with details of the measurement technique, in the next two chapters.

The procedure for calculating the insulator permittivity is to measure the capacitance of a number of MIM devices with different thicknesses of insulator; figure 3.5 is a schematic diagram of the equipment used for this purpose. The Boonton model 72BD Capacitance Meter displays capacitances of up to 2000pF by measuring the small signal response to a low amplitude 1MHz a.c. signal which is generated internally. When using MIM samples, no d.c. bias is required for determination of insulator capacitance. However, MIS devices may also be measured with this apparatus if a d.c. voltage is applied so as to bias them into accumulation (see section 3.1.4); the voltage source (Time Electronics 9814) and

- 29 -

# Figure 3.4 : Typical 1/C versus N plot for a metal - LB film - metal structure

# Figure 3.5 : Schematic of apparatus for permittivity calculations

sample chamber are considered in chapter 4.

## 3.2 Surface State Density Evaluation

A number of different methods have been employed to calculate the interface state density distribution of a MIS device. Some of these techniques require the capacitance-voltage characteristics of the sample to be recorded and are discussed in section 3.2.1. However, as will be seen, the drawbacks associated with this C-V approach may be largely overcome by utilising the conductance technique of Nicollian and Goetzberger <sup>(9)</sup> which involves measuring the relationships between a.c. conductance, signal frequency and bias voltage. Section 3.2.2. is devoted to this method and explains how the surface state density is calculated from the experimental data.

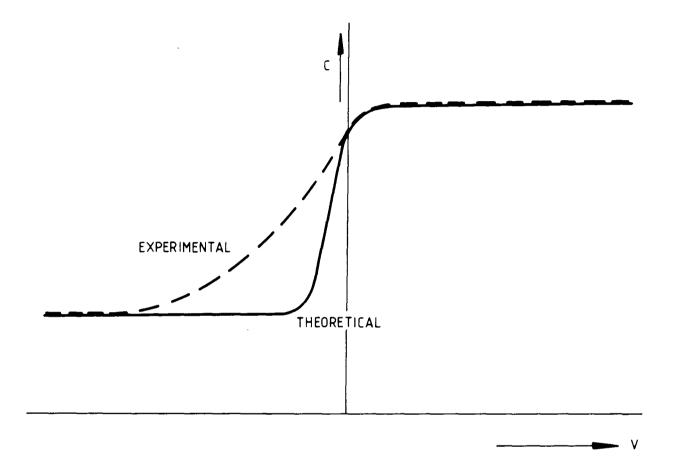

## 3.2.1. Capacitance-voltage methods

The earliest technique employed to determine surface state density was that of Terman <sup>(10)</sup>, in which a high frequency C-V curve is measured experimentally as outlined in section 3.1. Although surface states do not respond to a high frequency signal, their trapped charge results in a lateral displacement from the ideal theoretical curve (figure 3.6). At each energy position this lateral voltage shift  $\Delta V$  depends upon the surface state distribution N<sub>ce</sub> at that point, and is given by:-

$$Q_{s} = C_{ox} \Delta V$$

(3.9)

where Q<sub>s</sub> represents the total charge in the surface states. If Q<sub>s</sub> is calculated over the range of applied bias voltage so that the Q<sub>s</sub> versus surface potential ( $\psi_s$ ) relationship can be determined, then:

- 30 -

# Figure 3.6 : Comparison of typical experimental and theoretical high frequency C-V plots

$$N_{ss} = \frac{1}{q} \qquad \frac{\partial Q_s}{\partial \psi_s} \qquad eV^{-1} cm^{-2}$$

(3.10)

This equation expresses N<sub>SS</sub> as a function of energy, and with knowledge of the flat-band position (where  $\Psi_{\rm S} = 0$ ) each calculated value of surface state density can be related to a particular energy position in the bandgap. (The  $\partial Q_{\rm S} / \partial \Psi_{\rm S}$  terms must be obtained by graphical differentiation methods). One disadvantage of this method is that it is very sensitive to surface potential fluctuations, which can lead to considerable apparent surface state densities being wrongly detected. A further error can arise near theband edges, where even a frequency of IMHz is not high enough to ensure that the surface states do not respond.

Another method of interface state density analysis involves measuring the C-V curve with a low frequency (quasistatic) applied signal <sup>(11)</sup>. If the period of this signal is longer than the time constants of the surface states, then these states will contribute to the total device capacitance,  $C_{1f}(V)$ . This is measured by recording the displacement current, i, resulting from the application of a slowly-rising linear voltage ramp, <sup>(12)</sup> as given by

$$i = \frac{dQ}{dt} = \frac{dQ}{dV} \frac{dV}{dt} = {}^{C}lf \frac{dV}{dt}$$

(3.11)

For the simple MIS capacitor described in figure 2.11a,

$$\frac{1}{C} = \frac{1}{C_{ox}} + \frac{1}{C_{D} + C_{S}}$$

(3.12)

Assuming that  $C_s = qN_{ss}A$  and rearranging equation 3.12:

$$N_{ss} = \frac{1}{qA} \left( \frac{C_{1f}}{1 - C_{1f}/C_{ox}} - C_{D} \right)$$

(3.13)

$C_D$  can be calculated from equation 2.10 or derived experimentally from applying equation 3.12 to a high frequency curve (in which case  $C_S = 0$ ). Thus, equation 3.13 becomes:

$$N_{ss} = \frac{1}{qA} \left( \frac{C_{1f} C_{ox}}{C_{ox} - C_{1f}} - \frac{C_{hf} C_{ox}}{C_{ox} - C_{hf}} \right)$$

(3.14)

Unfortunately, as with the high frequency technique, surface potential fluctuations may give rise to incorrect determination of surface state density <sup>(13)</sup>, since the theoretically calculated value for  $C_{\rm D}$  in equation 3.13 will be inaccurate. It is better to compare the high- and low-frequency curves, using equation 3.14, but this is only accurate provided that the high frequency is such that  $C_{\rm S}$  is zero (i.e. that no surface states can follow the applied signal).

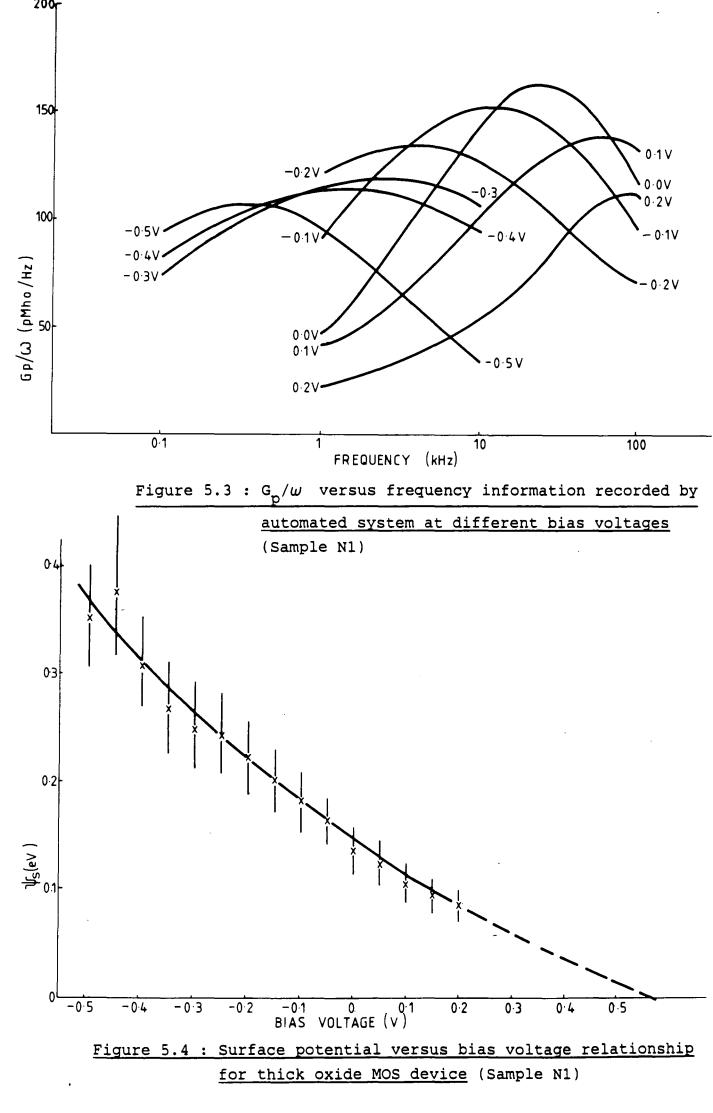

The surface potential,  $\psi_s$ , may be obtained directly from the low frequency C-V plot by integrating the curve over the range from strong accumulation towards inversion <sup>(11)</sup>:

$$\Psi_{s} = \int_{Vacc}^{V} (1 - C_{1f}/C_{ox}) dV = \Psi_{s}^{*} + \Delta$$

(3.15)

Numerical integration maybe performed to determine  $\psi_s^*$ , and the additive constant,  $\Delta$ , may be found by comparison with ideal curves or calculated from the horizontal intercept of a high frequency  $1/\ddot{c}^2$  versus V curve; from equation 3.5a, when  $1/c_p^2 = 0$ :

intercept =

$$\psi_s - \frac{kT}{q} = \psi_s^* + \Delta - \frac{kT}{q}$$

(3.16)

These, and other, capacitance techiques have been used for surface state density evaluation  $^{(14)}$ , but all suffer drawbacks of one kind or another. Some are very susceptible to errors due to surface potential fluctuation or are inaccurate because of uncertainty in the determination of the integration constant  $^{\Delta}$ , or of C<sub>ox</sub> and N<sub>d</sub>;

others fail when the C/C<sub>ox</sub> ratio becomes close to unity (in this case even an accuracy of 10% on measurement of C can give great errors in N<sub>ss</sub> and  $\Psi_s$ ). Becuase of these problems, it was found necessary to adopt a new approach to surface state density determination, and the a.c. conductance technique, described in the next section, was developed <sup>(9)</sup>.

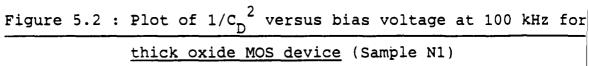

### 3.2.2 The a.c. conductance technique

By considering the loss mechanisms associated with the presence of interface states as discussed in section 2.2.3, further information about these states may be obtained. The procedure proposed by Nicollian and Goetzberger, <sup>(9)</sup> requires the determination of the complex frequency response of the small signal admittance of a MIS device from which the parallel capacitance and conductance,  $C_{p}$  and  $G_{p}$  (see figure 2.11b), are acquired and the surface state information extracted.

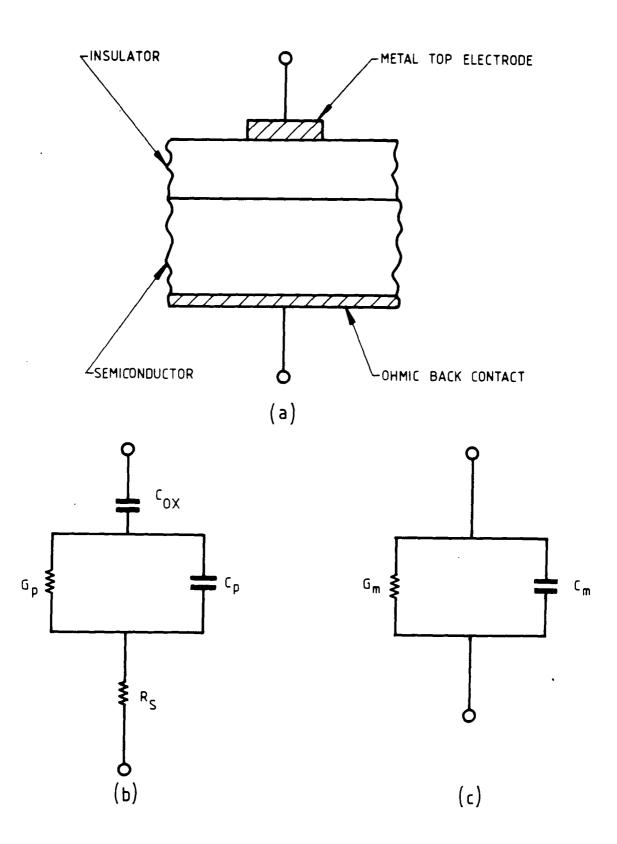

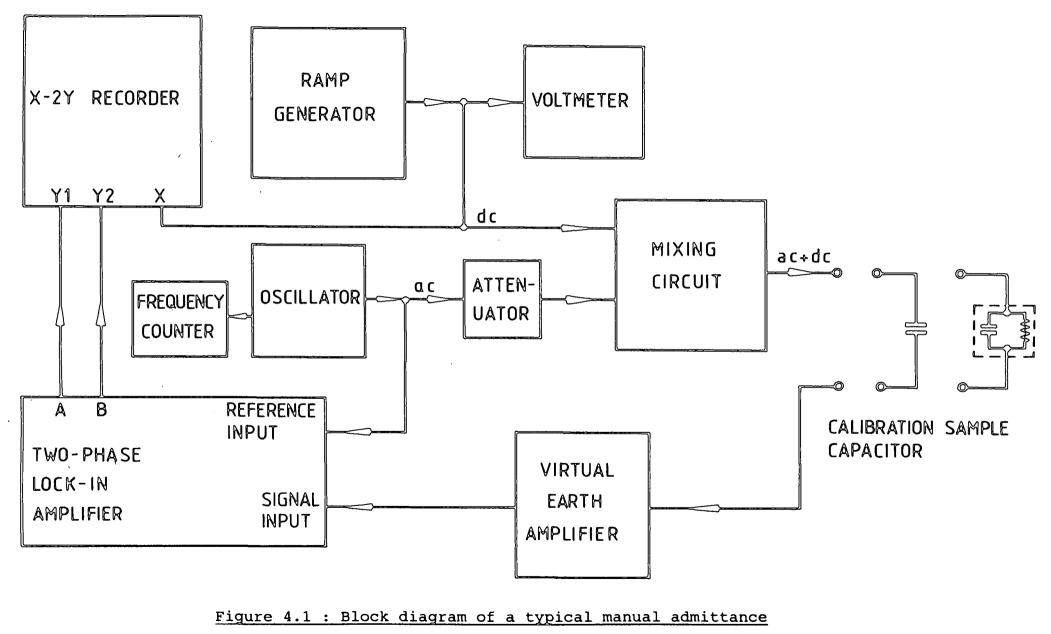

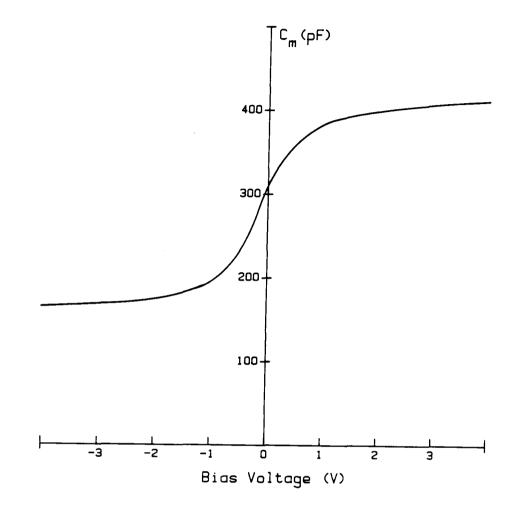

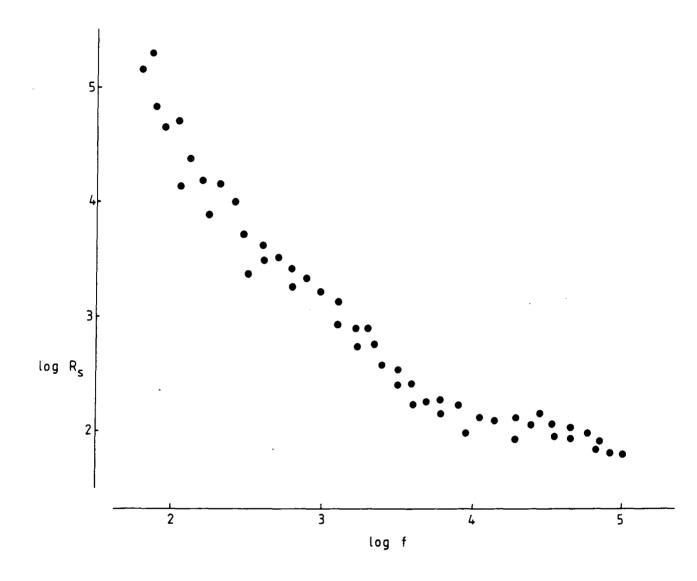

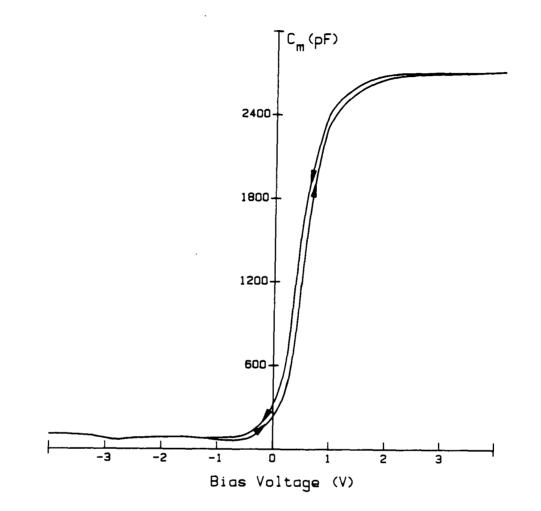

This is achieved by measuring the capacitance  $C_m$  and the conductance  $G_m$  of the sample over a wide frequency range at a large number of bias voltages. The device structure is shown in figure 3.7a and the electrical equivalent circuit in figure 3.7b:  $C_{ox..}$  is the oxide (or insulator) capacitance,  $R_s$  the series resistance of the top and back contacts, leads and bulk semiconductor, and the parallel  $G_p - C_p$  network represents the combined effects of interface traps and depletion layer capacitance. Figure 3.7c denotes the circuit as measured experimentally.

The values of R and C may be determined from measurements of C and G instrong accumulation:

$$R_{s} = G_{m} / (G_{m}^{2} + \omega^{2}C_{m}^{2})$$

(3.17)

$$C_{ox} = C_{m} \left[ 1 + (G_{m}^{2} + \omega^{2} C_{m}^{2}) \right]$$

(3.18)

Figure 3.7: Schematic cross-section of MIS device with electrical equivalent circuits

It is important to compensate for thexelements as they may otherwise obstruct correct interface state  $a_{AA}$ lysis <sup>(15)</sup>; for ideal devices the terms are bias and frequency independent, but in practice R and C must be calculated at each measurement frequency to offset any frequency-dependent effects. The importance of this compensation is not commonly appreciated, but it shall be demonstated in experiments reported later (chapter 5.2.4).

The parallel conductance and capacitance terms,  $G_p$  and  $C_p$  respectively, may now be determined from the following equations:

× .s

$$A G_{p} = \frac{\omega^{2} C_{ox}^{2} (G_{m} - \omega^{2} C_{m}^{2} R_{s} - R_{s} G_{m}^{2})}{(\omega^{2} C_{ox}^{2} R_{s} C_{m} - G_{m}^{2})^{2} + \omega^{2} (C_{ox}^{2} - C_{m}^{2} - C_{ox}^{2} R_{s} G_{m}^{2})}$$

(3.19)

$$A C_{p} = \frac{\omega^{2} C_{ox} C_{m} (C_{ox} - C_{m}) - C_{ox} G_{m}^{2}}{(\omega^{2} C_{ox} R_{s} C_{m} - G_{m})^{2} + \omega^{2} (C_{ox} - C_{m} - C_{ox} R_{s} G_{m})^{2}}$$

(3.20)

where A is the area of the top electrode, and  $R_s$  and  $C_{ox}$  are as defined in equations 3.17 and 3.18. The surface state density  $N_{ss}$ can be obtained from either  $C_p$  or  $G_p$  (see section 2.2.3).  $C_p$ is made up of two components: the surface state capacitance  $C_s$  and the depletion layer capacitance  $C_D$  (equation 2.28), and so the problem of evaluating  $C_p$  accurately is again encountered (as in the C-V techniques discussed in section 3.2.1.). However,  $G_p$  is directly related to  $N_{ss}$  (equation 2.32), and this fact enables values of surface state density to be calculated more accurately.

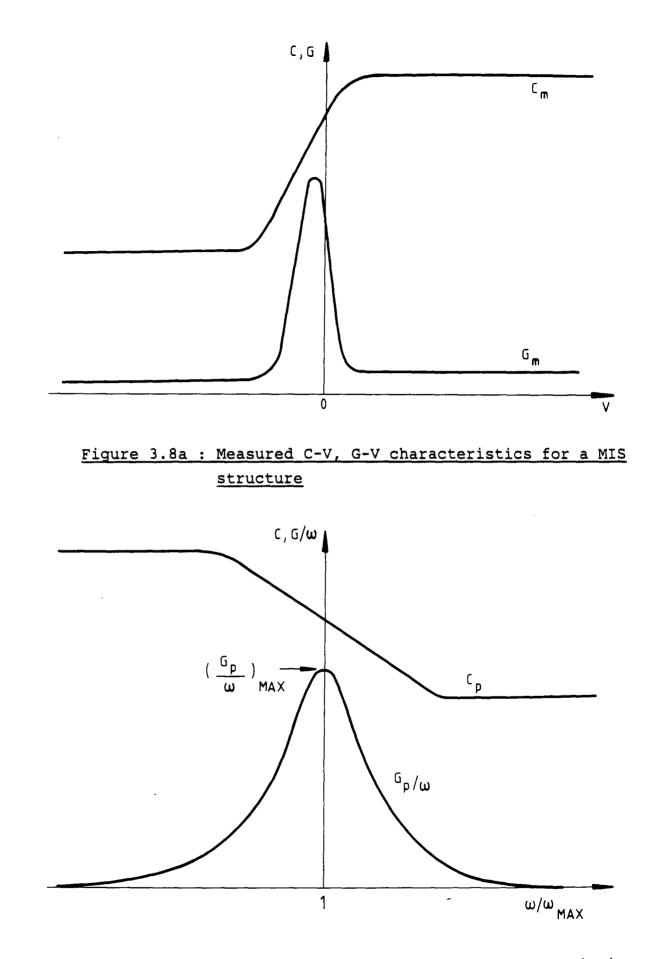

The standard experimental procedure for obtaining N<sub>SS</sub> is to plot a number of C-V/G-V curves at different signal frequencies, and from these to build up plots of normalised  $G_p/\omega$  versus  $\omega$ for different values of bias voltage (9). Figure 3.8a shows a

- 34 -

Figure 3.8b : Equivalent parallel admittance characteristics for a MIS structure

schematic curve of  $C_m$ ,  $G_m$  versus V and figure 3.8b a single  $C_p$ ,  $G_p/\omega$  versus  $\omega/\omega_{max}$  plot made up of data from a number of C-V/G-V runs (both curves plotted in arbitrary units). The surface state density can be calculated from the equation:

$$N_{ss} = \frac{1}{qA} \left( \frac{G_p}{\omega} \right)_{max} / f_N(O_g)$$

(3.21)

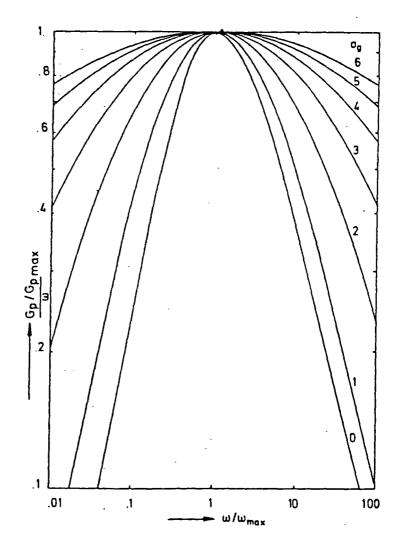

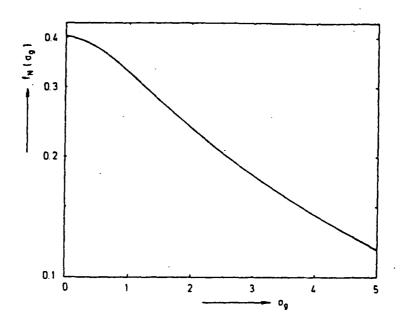

The value of  $(G_p/\omega)_{max}$  is obtained graphically from the parallel conductance plot. The statistical function  $f_N(\sigma_g)$  depends purely upon the variance  $\sigma_g$  of the normalised  $G_p/\omega$  versus  $\omega$  response. By comparing the experimental result with standard curves plotted with  $\sigma_g$  as parameter (figure 3.9a), the curve variance can be found; the corresponding value of  $f_N$  is obtained from a standard plot of this function <sup>(14)</sup> (figure 3.9b).

In order to obtain the value of surface potential  $\psi_s$  (and hence the position in the bandgap relating to each particular surface state), the complicated integration procedure <sup>(11)</sup> described in section 3.2.1 can be avoided by measuring the value of C<sub>p</sub> at the position of the G<sub>p</sub>/ $\omega$  peak. From equation 2.10, modified for surface area:

$$c_{\rm D}^{-2} = \frac{2}{q \varepsilon_{\rm s} N_{\rm d} A^2} \left( \psi_{\rm s} - \frac{kT}{q} \right)$$

(3.22)

or

$${}^{\psi}s = \frac{kT}{q} + \frac{q\varepsilon_{r}\varepsilon_{o}N_{d}A^{2}}{2C_{D}^{2}}$$

(3.22a)

However,  $C_{D} = C_{p} - C_{s}$  from equation 2.28, and since in general<sup>(14)</sup>:

- 35 -

Figure 3.9a : Normalised parallel conductance curves plotted with variance  $\sigma_{\rm q}$  as parameter

Figure 3.9b : Plot of the statistical function  $\sigma_{\underline{q}}$

$$C_{s} = qAN_{ss}$$

(3.23)

then from equation 3.22a:

$$\psi_{s} = \frac{kT}{q} + \frac{q\varepsilon_{r}\varepsilon_{o}N_{d}A^{2}}{2(c_{p}-qAN_{ss})^{2}}$$

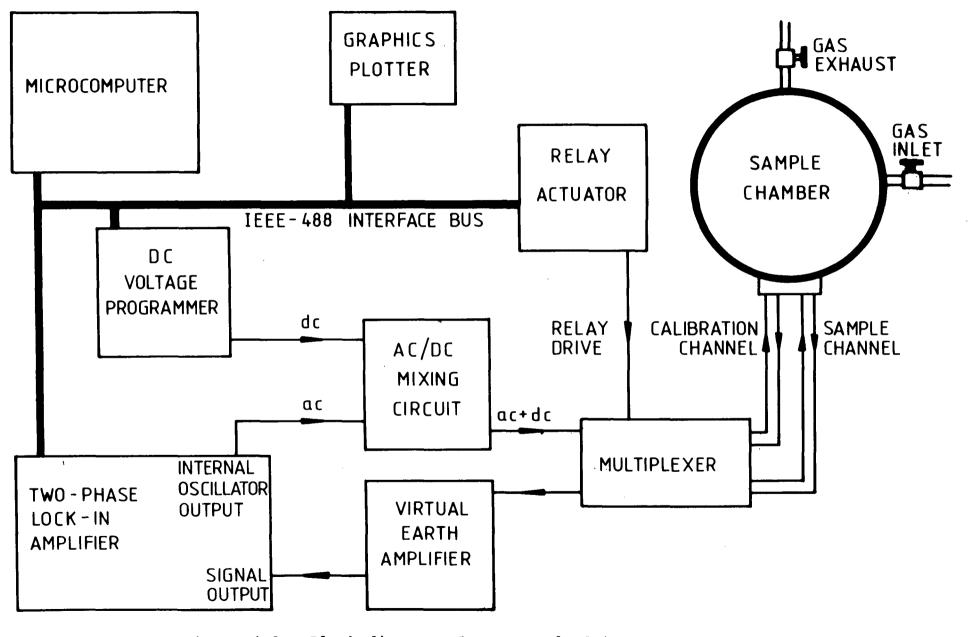

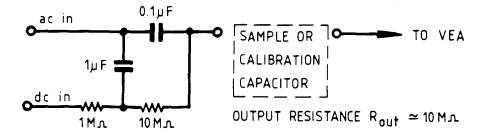

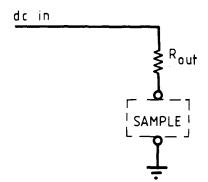

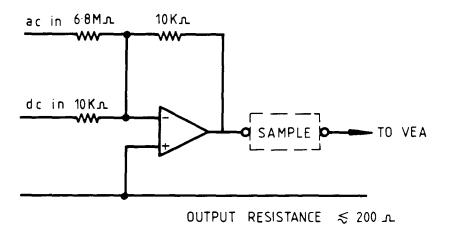

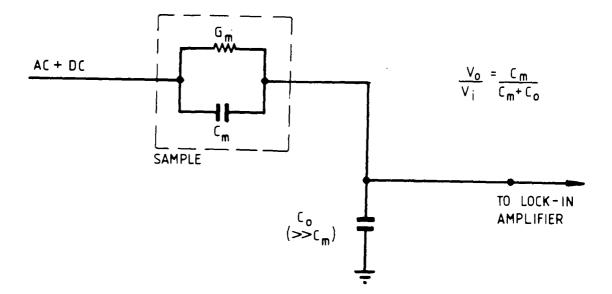

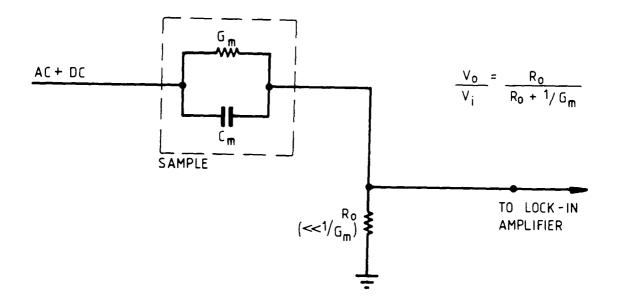

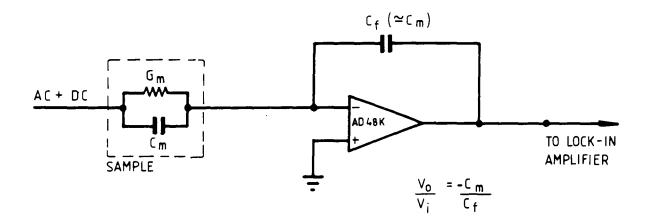

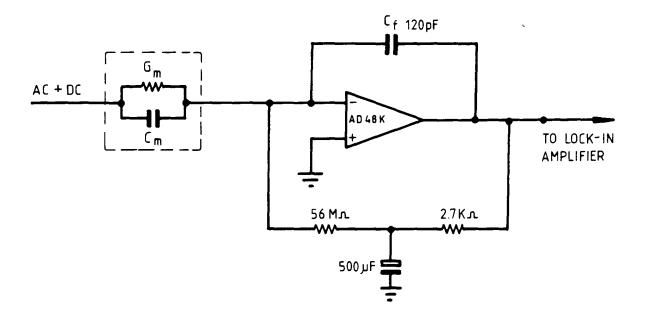

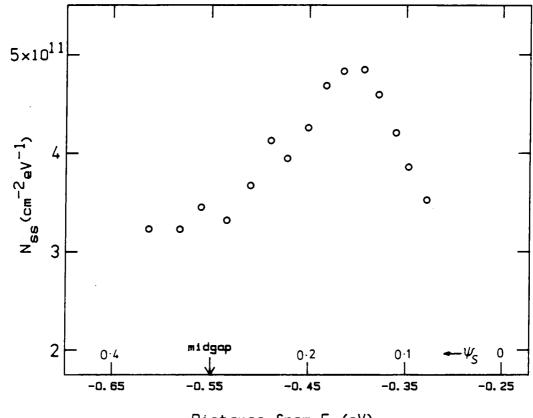

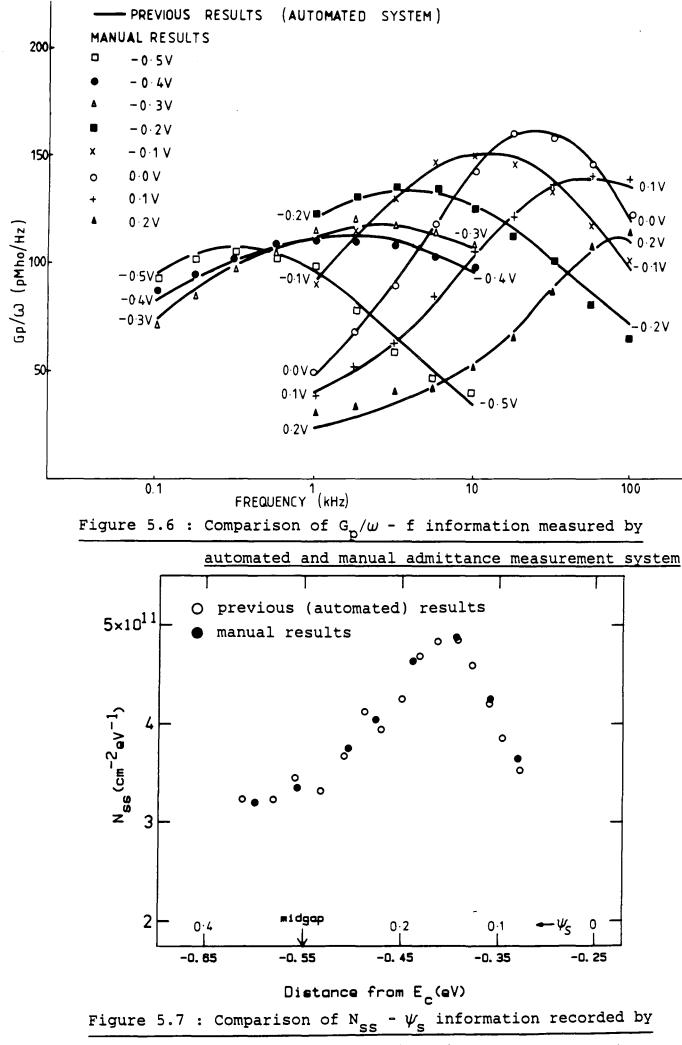

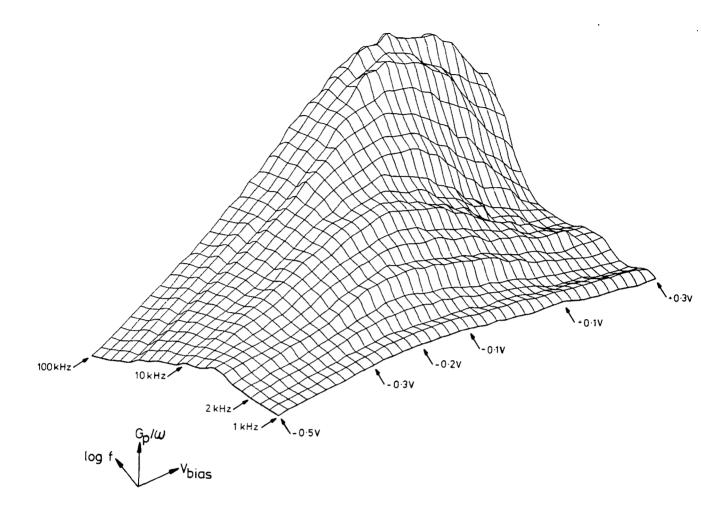

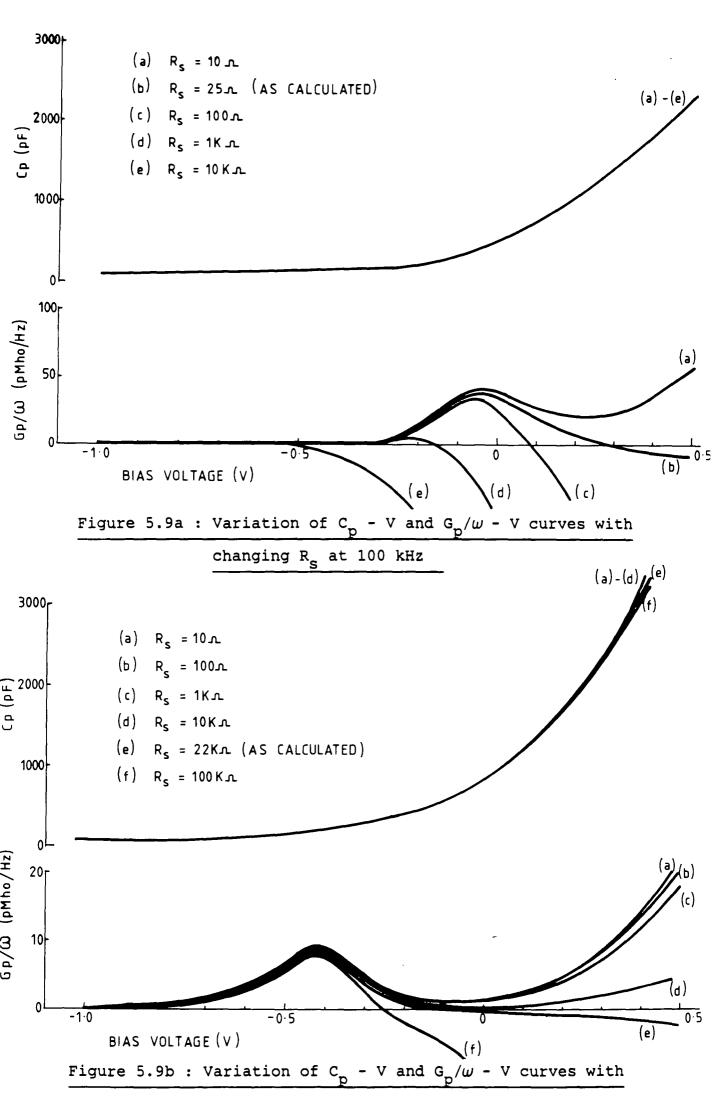

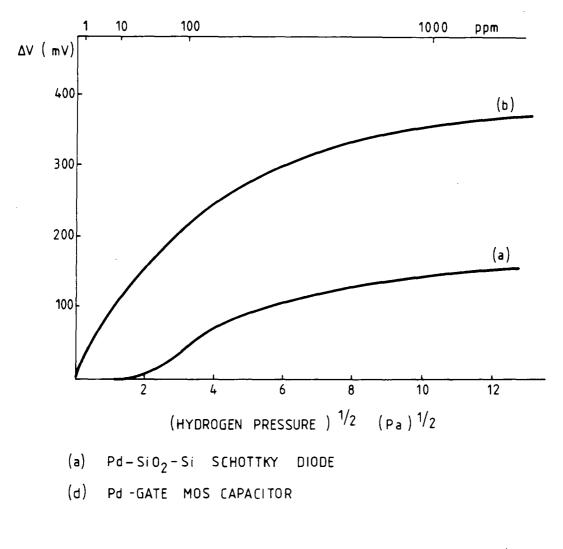

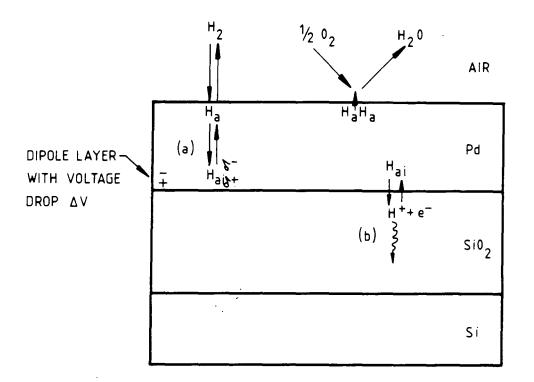

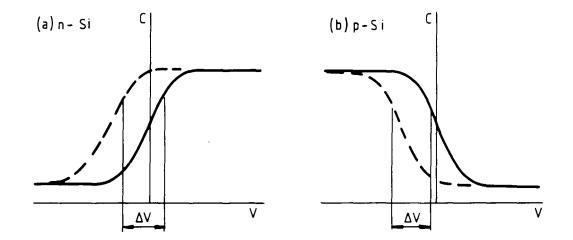

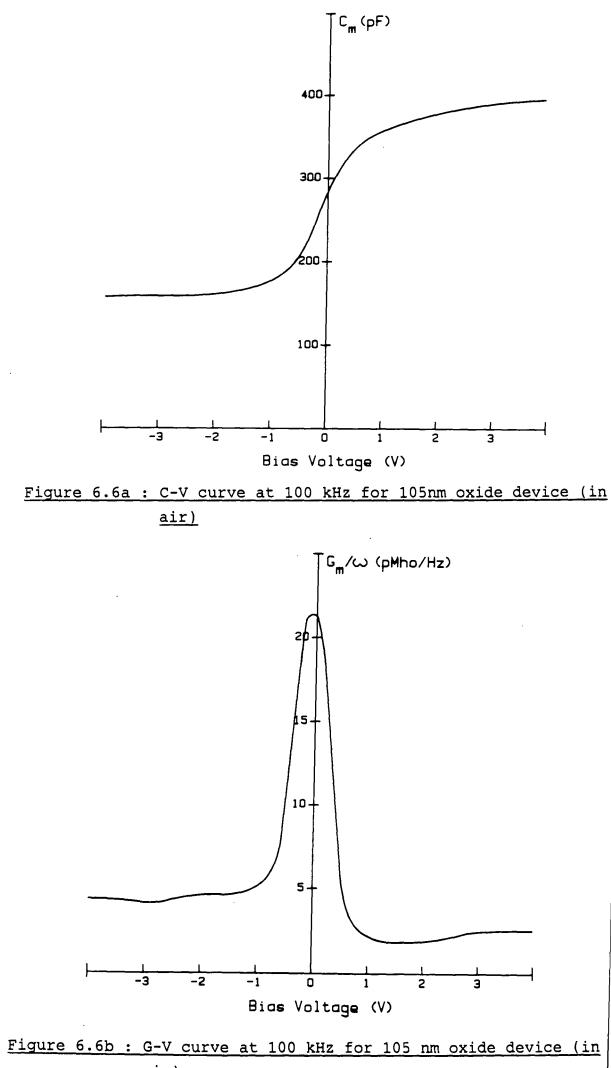

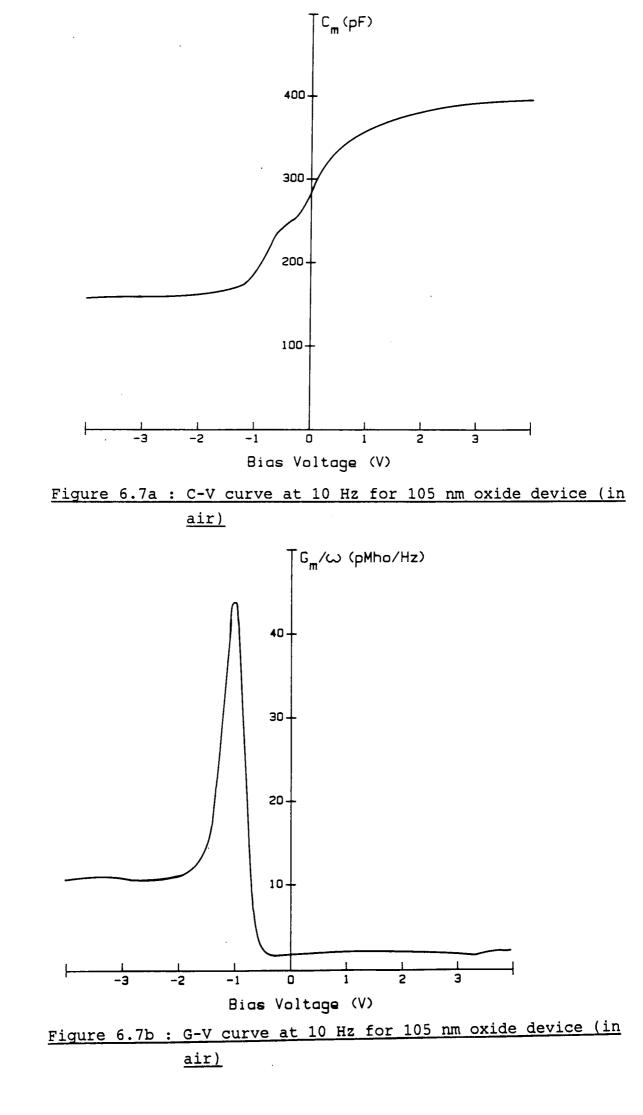

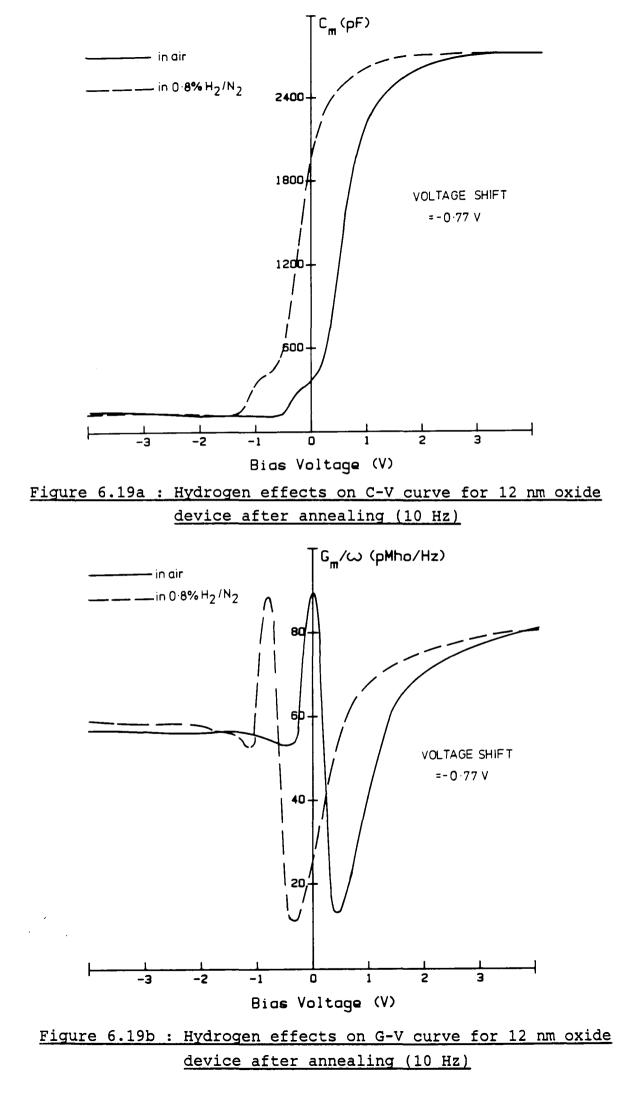

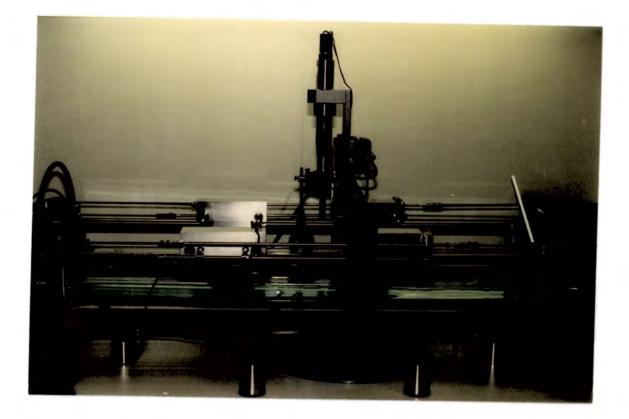

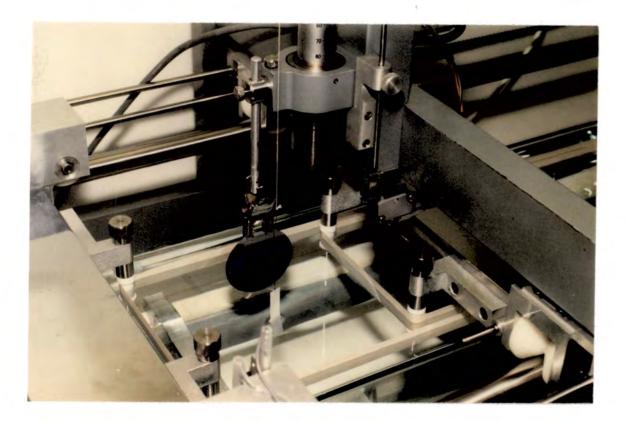

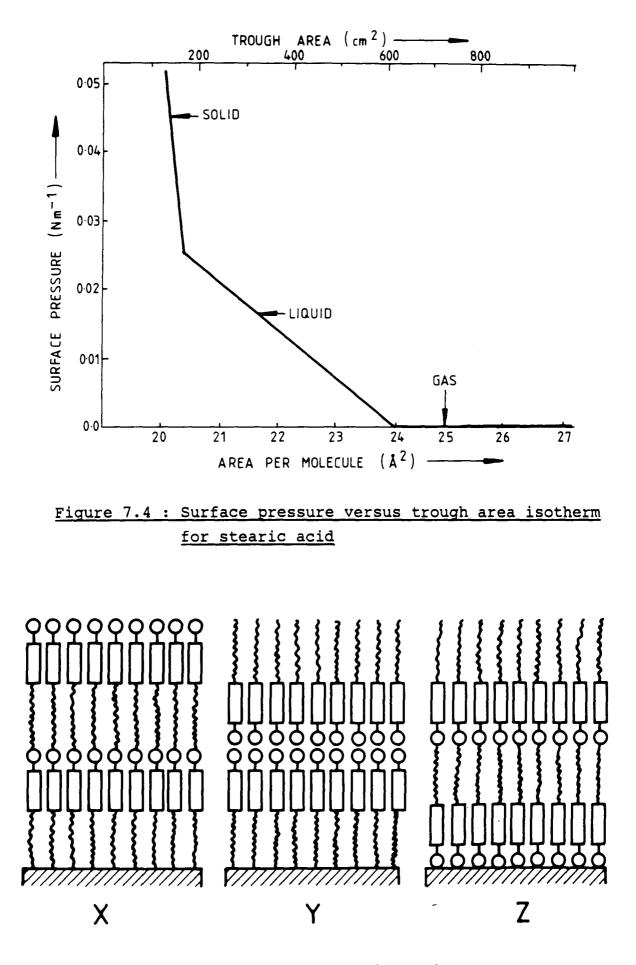

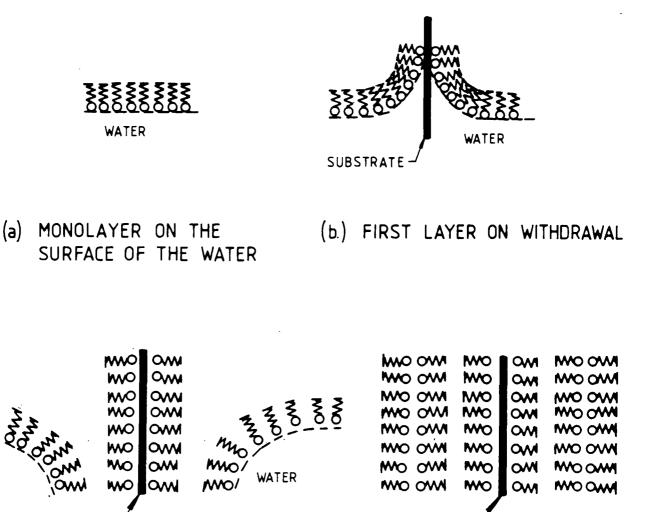

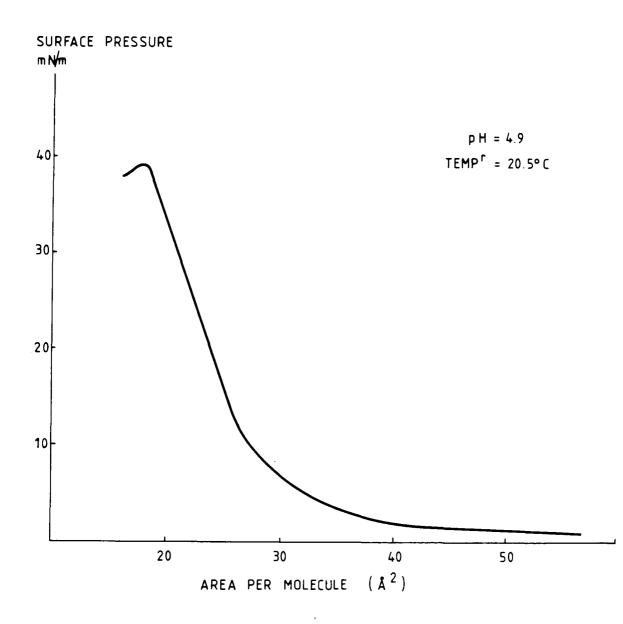

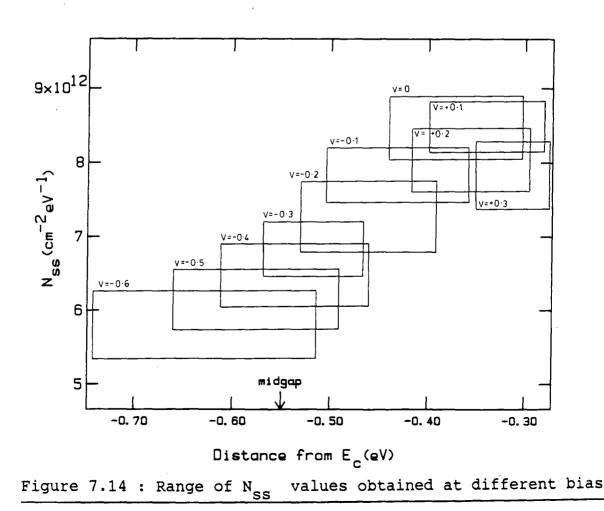

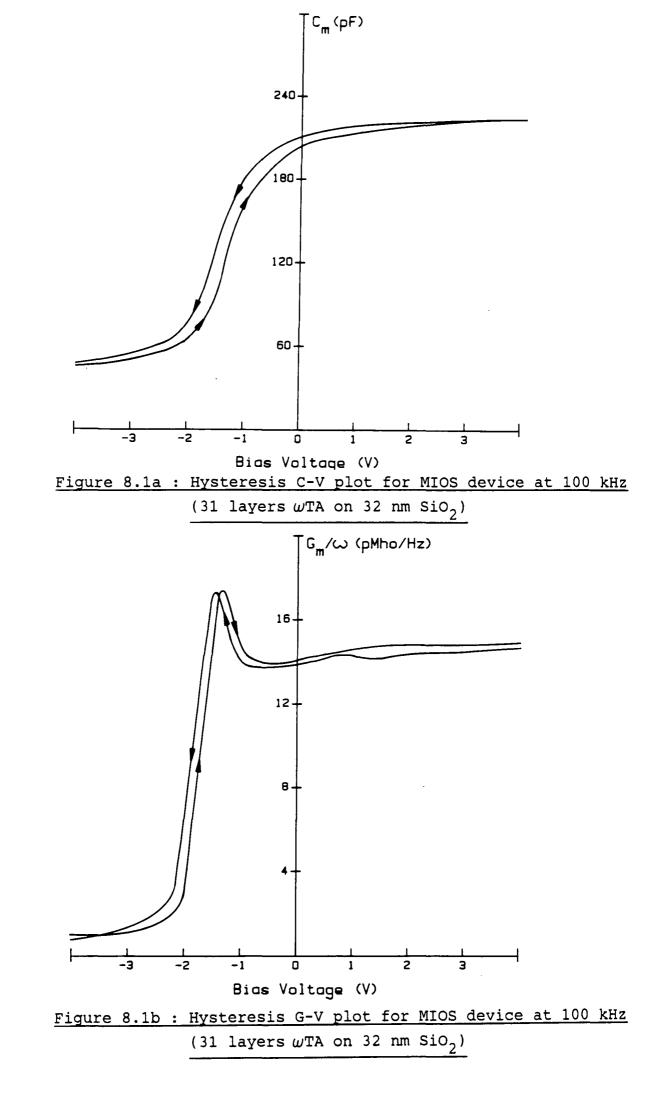

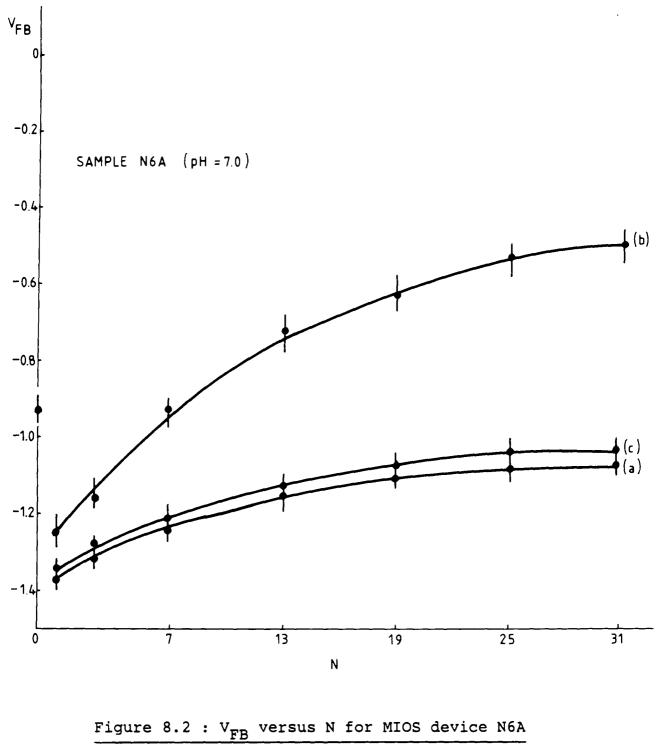

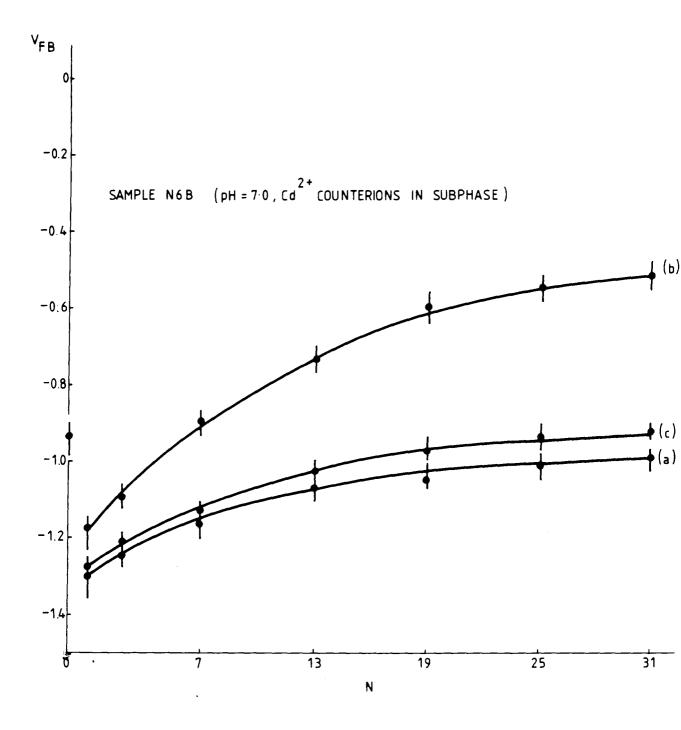

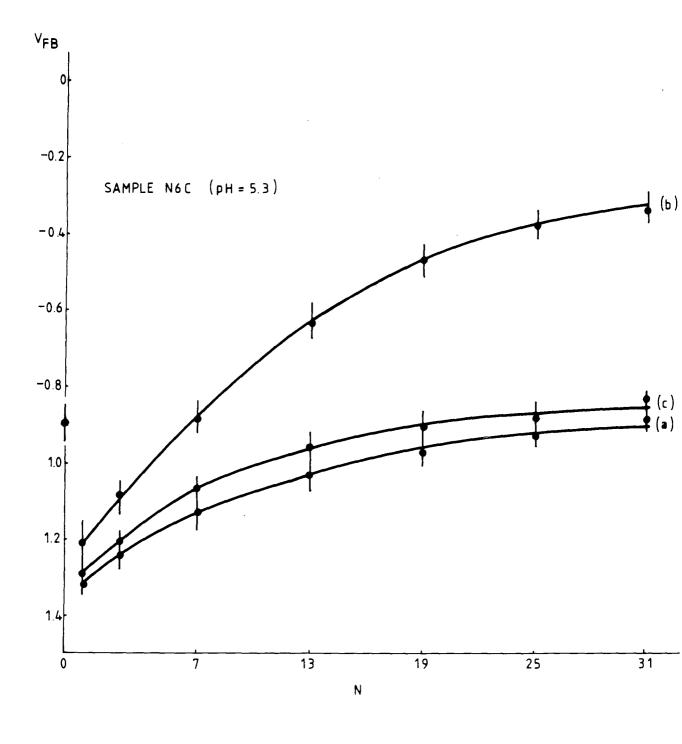

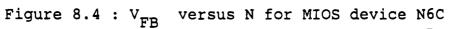

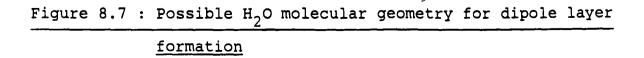

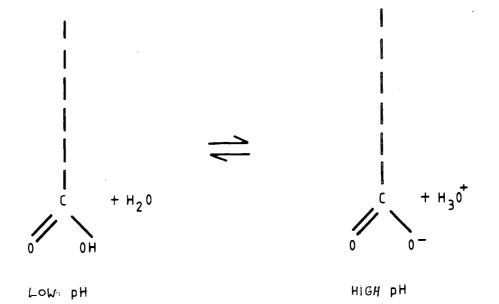

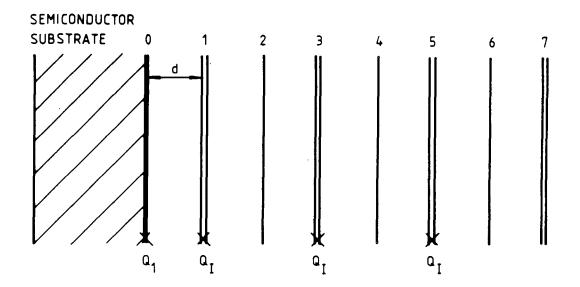

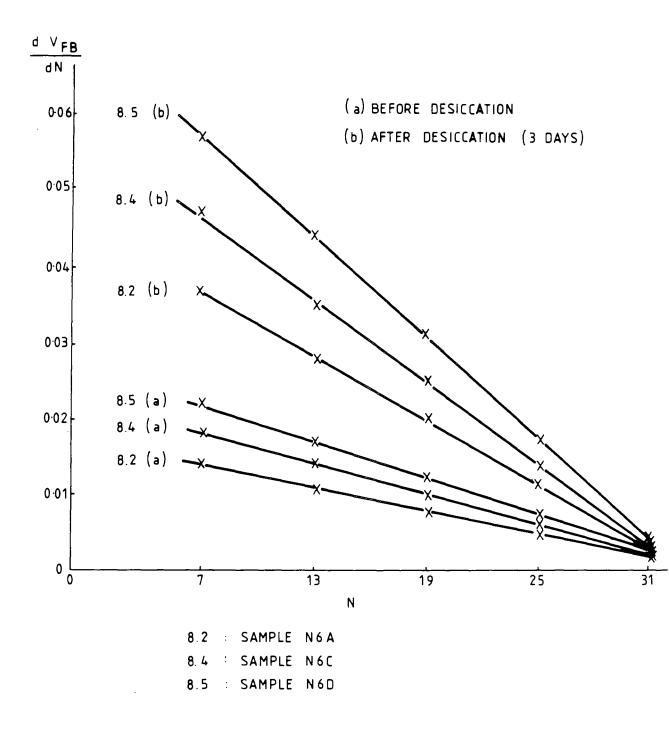

(3.24)