## **Durham E-Theses**

## Strategies for Optimising DRAM Repair

MILBOURN, JOSEPH, JOHN

#### How to cite:

MILBOURN, JOSEPH, JOHN (2010) Strategies for Optimising DRAM Repair, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/685/

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- $\bullet\,$  a link is made to the metadata record in Durham E-Theses

- $\bullet \,$  the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

# Strategies for Optimising DRAM Repair

Joseph Milbourn

A Thesis presented for the degree of Doctor of Philosophy

Centre For Electronic Systems

School of Engineering

Durham University

England

September 2010

## Strategies for Optimising DRAM Repair

#### Joseph Milbourn

Submitted for the degree of Doctor of Philosophy September 2009

#### Abstract

Dynamic Random Access Memories (DRAM) are large complex devices, prone to defects during manufacture. Yield is improved by the provision of redundant structures used to repair these defects. This redundancy is often implemented by the provision of excess memory capacity and programmable address logic allowing the replacement of faulty cells within the memory array.

As the memory capacity of DRAM devices has increased, so has the complexity of their redundant structures, introducing increasingly complex restrictions and interdependencies upon the use of this redundant capacity.

Currently redundancy analysis algorithms solving the problem of optimally allocating this redundant capacity must be manually customised for each new device. Compromises made to reduce the complexity, and human error, reduce the efficacy of these algorithms.

This thesis develops a methodology for automating the customisation of these redundancy analysis algorithms. Included are: a modelling language describing the redundant structures (including the restrictions and interdependencies placed upon their use), algorithms manipulating this model to generate redundancy analysis algorithms, and methods for translating those algorithms into executable code.

Finally these concepts are used to develop a prototype software tool capable of generating redundancy analysis algorithms customised for a specified device.

## Declaration

The work in this thesis is based on research carried out at the Centre for Electronic Systems, the School of Engineering, the Durham University, England. No part of this thesis has been submitted elsewhere for any other degree or qualification and it is all my own work unless referenced to the contrary in the text.

#### Copyright © 2010 by Joseph Milbourn.

"The copyright of this thesis rests with the author. No quotations from it should be published without the author's prior written consent and information derived from it should be acknowledged".

# Acknowledgements

This work would not have been possible without the kind support of my supervisors, Professor Alan Purvis and Dr Simon Johnson at Durham University.

I would also like to thank Dr Erik Volkerink, Verigy Chief Scientist; his colleagues Tien Pham, Andy Niemic, and Scott West of the memory test division in Cupertino, Justin Cui of the memory test division in Shanghai, and also Klaus Dieter Hilliges of the SoC test division, Germany, and Jimmy Jin of the SoC test division, Shanghai.

Finally, I would acknowledge the Engineering and Physical Sciences Research Council for funding this project, and Verigy for their sponsorship.

# Contents

|   | Abs  | stract                              | ii   |

|---|------|-------------------------------------|------|

|   | Dec  | claration                           | iii  |

|   | Ack  | knowledgements                      | iv   |

| 1 | Intr | roduction                           | 1    |

|   | 1.1  | Requirement for DRAM Redundancy     | 2    |

|   | 1.2  | Redundancy Implementation           | 2    |

|   | 1.3  | Repair Process                      | . 3  |

|   | 1.4  | Redundancy Analysis Algorithms      | . 3  |

|   | 1.5  | Industrial Background               | 5    |

|   | 1.6  | Problem                             | 6    |

|   | 1.7  | Proposed Solution                   | 6    |

|   | 1.8  | Sponsorship                         | 6    |

| 2 | Bac  | ekground                            | 8    |

|   | 2.1  | Introduction to Repairable DRAM     | . 8  |

|   | 2.2  | Structure of Repairable RAM Devices | 10   |

|   | 2.3  | Causes of Complexity                | . 11 |

|   |      | 2.3.1 Hard Wired Fusebox Bits       | 11   |

|   |      | 2.3.2 Shared Fusebox Bits           | 12   |

|   |      | 2.3.3 Shared Redundant Elements     | 14   |

|   | 2.4  | Modelling DRAM devices              | 14   |

|   | 2.5  | Repair Algorithms                   | 17   |

|   | 2.6  | Proposed Solution                   | 18   |

|   | 2.7  | Conclusions                         | 20   |

| CONTENTS | • |  |

|----------|---|--|

|          |   |  |

|          |   |  |

| 3 | $\mathbf{Mo}$ | delling DRAM Failure Maps                            | <b>23</b> |

|---|---------------|------------------------------------------------------|-----------|

|   | 3.1           | Introduction                                         | 23        |

|   | 3.2           | The Statistical Model                                | 24        |

|   | 3.3           | Implementation                                       | 27        |

|   | 3.4           | Conclusions                                          | 30        |

| 4 | $\mathbf{DR}$ | AM Redundancy Analysis                               | 32        |

|   | 4.1           | DRAM Repair Background                               | 32        |

|   | 4.2           | Introduction                                         | 36        |

|   | 4.3           | The Spare Allocation Problem                         | 37        |

|   | 4.4           | Algorithms                                           | 38        |

|   | 4.5           | Analysis                                             | 40        |

|   | 4.6           | Repair in Hierarchical Devices                       | 44        |

|   | 4.7           | Experiments                                          | 46        |

|   |               | 4.7.1 Apparatus                                      | 48        |

|   |               | 4.7.2 Results                                        | 48        |

|   | 4.8           | Conclusions                                          | 50        |

| 5 | A F           | Redundancy Model for DRAM                            | <b>52</b> |

|   | 5.1           | Background                                           | 52        |

|   | 5.2           | Introduction                                         | 55        |

|   | 5.3           | Problem                                              | 57        |

|   |               | 5.3.1 Model Concepts                                 | 58        |

|   | 5.4           | Mathematical Model                                   | 58        |

|   |               | 5.4.1 Possible Placements                            | 61        |

|   |               | 5.4.2 Constraints                                    | 62        |

|   |               | 5.4.3 Interaction Between Placements and Constraints | 65        |

|   | 5.5           | Functions of Model Elements                          | 66        |

|   |               | 5.5.1 Coverage                                       | 66        |

|   |               | 5.5.2 Equality                                       | 67        |

|   |               | 5.5.3 Compatibility                                  | 68        |

|   | 5.6           | Modelling Rules and Syntax                           | 69        |

|   |               | 5.6.1 Rules                                          | 69        |

| $\frac{\mathbf{C}}{\mathbf{C}}$ | ONT           | ENTS                                          | 1 |

|---------------------------------|---------------|-----------------------------------------------|---|

|                                 |               | 5.6.2 Syntax and Semantic Checking            | ) |

|                                 | 5.7           | Abstraction in the Graphical Model            | ) |

|                                 |               | 5.7.1 Atomic Abstract Models                  | 2 |

|                                 | 5.8           | Conclusions                                   | 2 |

| 6                               | Tex           | tual Model Language 79                        | ) |

|                                 | 6.1           | Introduction                                  | 9 |

|                                 | 6.2           | Language Requirements                         | ) |

|                                 | 6.3           | Grammar                                       | ) |

|                                 | 6.4           | Expression Syntax                             | 2 |

|                                 | 6.5           | Example Text Model                            | 1 |

|                                 | 6.6           | Conclusions                                   | 1 |

| 7                               | Aut           | tomatic Code Generation 8'                    | 7 |

|                                 | 7.1           | Introduction                                  | 7 |

|                                 | 7.2           | Background                                    | ) |

|                                 | 7.3           | Algorithms                                    | 2 |

|                                 |               | 7.3.1 Off-line Redundancy Analysis Algorithms | 3 |

|                                 |               | 7.3.2 On-line Redundancy Analysis Algorithms  | 3 |

|                                 | 7.4           | Approach                                      | 3 |

|                                 | 7.5           | Examples                                      | 1 |

|                                 |               | 7.5.1 Region Identification                   | 4 |

|                                 |               | 7.5.2 Must Repair                             | 3 |

|                                 |               | 7.5.3 Branch and Bound Repair                 | 3 |

|                                 | 7.6           | Conclusions                                   | 7 |

| 8                               | $\mathbf{DR}$ | AM Redundancy Analysis Modelling Tool 11      | 9 |

|                                 | 8.1           | Introduction                                  | ) |

|                                 | 8.2           | Users and Use Cases                           | 2 |

|                                 |               | 8.2.1 Modelling a New Device                  | 2 |

|                                 |               | 8.2.2 Syntax and Semantic Checking            | 1 |

|                                 |               | 8.2.3 Exporting a Model                       | 5 |

|                                 |               | 8.2.4 Importing a Model                       | ă |

| C       | ONT  | ENTS    |                                                  | viii |

|---------|------|---------|--------------------------------------------------|------|

|         |      | 8.2.5   | Generating Code                                  | 126  |

|         |      | 8.2.6   | Implementing a new Redundancy Analysis Algorithm | 126  |

|         |      | 8.2.7   | Requirements                                     | 128  |

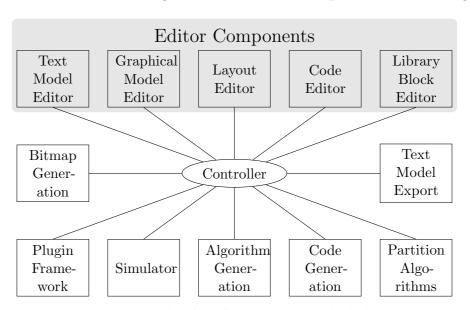

|         | 8.3  | Implen  | nentation                                        | 129  |

|         |      | 8.3.1   | Architecture                                     | 129  |

|         |      | 8.3.2   | Interface components                             | 130  |

|         |      | 8.3.3   | Text Model Import                                | 131  |

|         |      | 8.3.4   | Model Objects                                    |      |

|         |      | 8.3.5   | Model Functions                                  | 132  |

|         |      | 8.3.6   | Code generation                                  | 133  |

|         | 8.4  | Release | es                                               | 133  |

|         | 8.5  |         | bles                                             |      |

|         | 8.6  |         | isions                                           |      |

|         | 8.7  |         | r work                                           |      |

| 9       | Evn  | erimen  |                                                  | 145  |

| 9       | -    |         |                                                  |      |

|         | 9.1  |         | uction                                           |      |

|         | 9.2  |         | aring Repair Algorithms                          |      |

|         | 9.3  |         | atus                                             |      |

|         | 9.4  | Results | 5                                                | 150  |

|         | 9.5  | Conclu  | sions                                            | 153  |

| 10      | Con  | clusion | ns                                               | 157  |

|         | 10.1 | Proble  | m Review                                         | 157  |

|         | 10.2 | Object  | ives                                             | 158  |

|         | 10.3 | Achiev  | ements                                           | 159  |

|         |      | 10.3.1  | Concepts                                         | 159  |

|         |      | 10.3.2  | Implementation                                   | 161  |

|         | 10.4 | Results | S                                                | 162  |

|         |      |         | r Work                                           |      |

|         |      |         | g Remarks                                        |      |

| ${f A}$ | Tem  | plate . | Application Programming Interface                | 166  |

|   | A.1  | The Template Class                                                  |

|---|------|---------------------------------------------------------------------|

|   | A.2  | The Algorithm Class                                                 |

| В | Sup  | porting Source Code 173                                             |

|   | B.1  | File: bitmap.c                                                      |

|   | B.2  | File: bitmap.h                                                      |

|   | В.3  | File: bnb.c                                                         |

|   | B.4  | File: bnb.h                                                         |

|   | B.5  | File: model.c                                                       |

|   | B.6  | File: model.h                                                       |

|   | B.7  | File: must_repair.c                                                 |

|   | B.8  | File: queue.c                                                       |

|   | B.9  | File: queue.h                                                       |

|   | B.10 | File: region_generation.c                                           |

|   | B.11 | $File: \   {\tt region\_generation.h}  .  .  .  .  .  .  .  .  .  $ |

|   | B.12 | File: repair.c                                                      |

|   | B.13 | File: repair.h                                                      |

|   | B.14 | File: solution_record.c                                             |

|   | B.15 | File: solution_record.h                                             |

|   | B.16 | File: utils.c                                                       |

|   | B.17 | File: utils.h                                                       |

|   | B.18 | File: kaf.rml                                                       |

|   |      |                                                                     |

# List of Figures

| 1.1 | Redundancy Analysis in the context of DRAM manufacture | 4 |

|-----|--------------------------------------------------------|---|

| 1.2 | The manual repair process                              | 5 |

| 1.3 | Predicted DRAM Capacity                                | 5 |

| 1 4 | Proposed System Overview                               | 7 |

| 2.1  | Simple DRAM structure                                   | 10 |

|------|---------------------------------------------------------|----|

| 2.2  | Effects of fixing least significant bits in the fusebox | 12 |

| 2.3  | Effects of fixing most significant bits in the fusebox  | 12 |

| 2.4  | Effects of a fusebox with shared bits                   | 13 |

| 2.5  | Two redundant elements with a shared fusebox bit        | 13 |

| 2.6  | Shared redundant row repairing in both of two memories  | 15 |

| 2.7  | Shared redundant column repairing one of two memories   | 16 |

| 2.8  | Example Complex Device                                  | 17 |

| 3.1  | Experiments with Real and Modelled Failure Maps         | 25 |

| 3.2  | Overlay of Generated Failure Maps                       | 29 |

| 3.3  | Calibration curve for the yield model                   | 30 |

| 4.1  | Most Repair Solution                                    | 33 |

| 4.2  | Must Repair Solution                                    | 35 |

| 4.3  | Yield Improvement after Simple Repair                   | 37 |

| 4.4  | Repair Solutions                                        | 41 |

| 4.5  | Device with hierarchical repair                         | 44 |

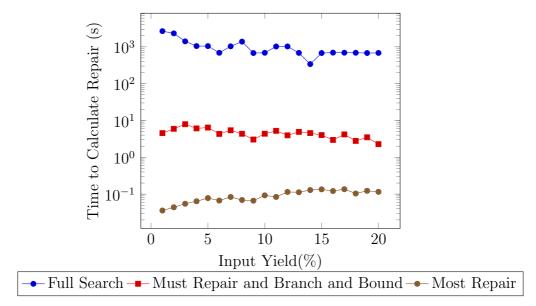

| 4.6  | Yield results for three redundancy analysis algorithms  | 49 |

| 4.7  | Repair time for three redundancy analysis algorithms    | 50 |

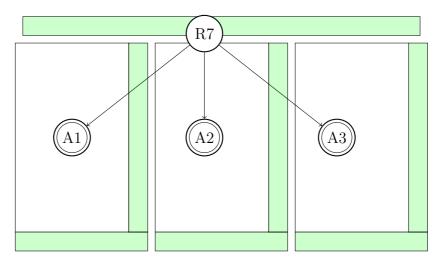

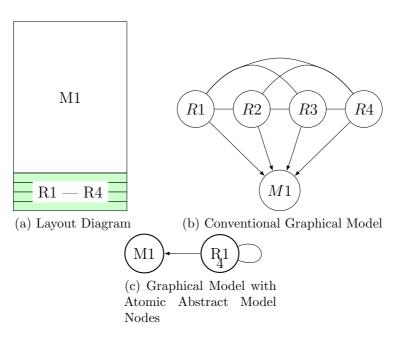

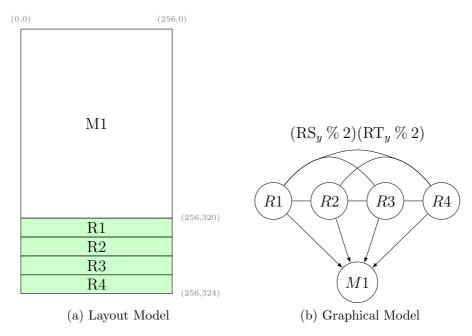

| 5.1  | Model Abstraction in DRAM                               | 53 |

| 5.2  | Block Diagram of a Simple DRAM                          | 57 |

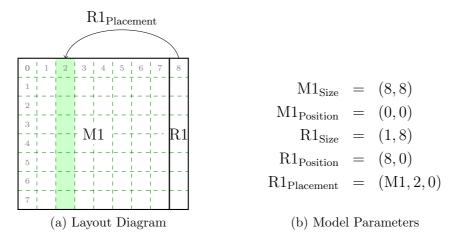

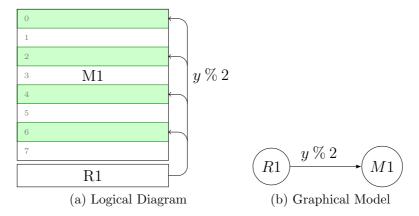

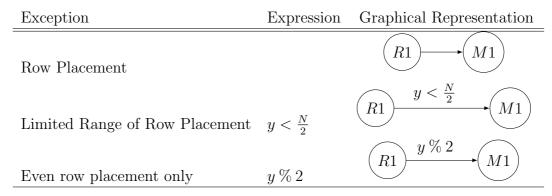

| 5.3  | Placement and Model Parameters                          | 60 |

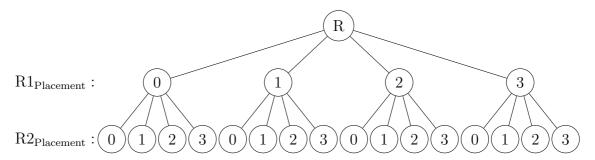

| 5.4  | Graphical Model Placements                              | 61 |

| 5.5  | Possible Placements                                     | 63 |

| 5.6  | Tied Redundant Rows                                     | 64 |

| 5.7  | Placements Constrained to One Memory                    | 64 |

| 5.8  | Constrained Placements                                  | 64 |

| 5.9  | Sets of Placements                                      | 66 |

| 5.10 | Sets of Placements Visualised                           | 74 |

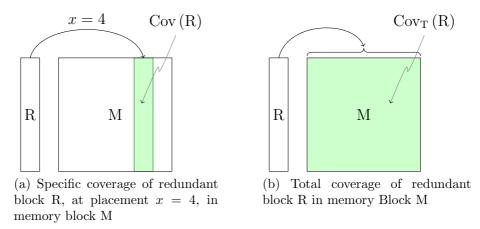

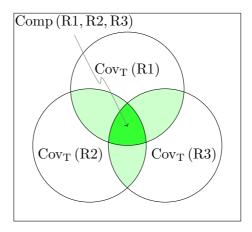

| 5.11 | Total and Specific Coverage                             | 75 |

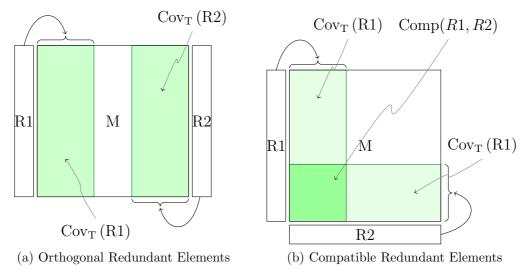

| 5.12 | Compatible and orthogonal redundant blocks              | 75 |

| 112 | 51 OF | FIGURES                                                        | <u>X1</u> |

|-----|-------|----------------------------------------------------------------|-----------|

|     | 5.13  | Associative Compatibility                                      | 75        |

|     | 5.14  | Modelling Rule Representation                                  | 76        |

|     | 5.15  | Modelling Rule Replication                                     | 76        |

|     | 5.16  | Modelling Rule Allocation                                      | 76        |

|     | 5.17  | Graphical Model Overlay                                        | 77        |

|     | 5.18  | Simplification using Abstract Models                           | 77        |

|     | 5.19  | Atomic Abstract Model                                          | 78        |

|     | 6.1   | Text Model Grammar                                             | 81        |

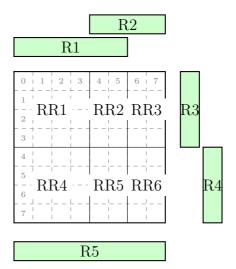

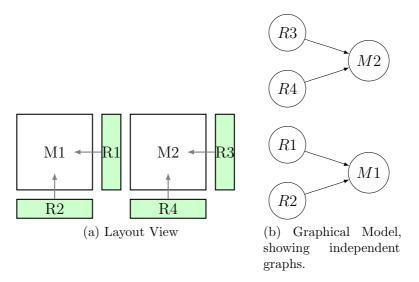

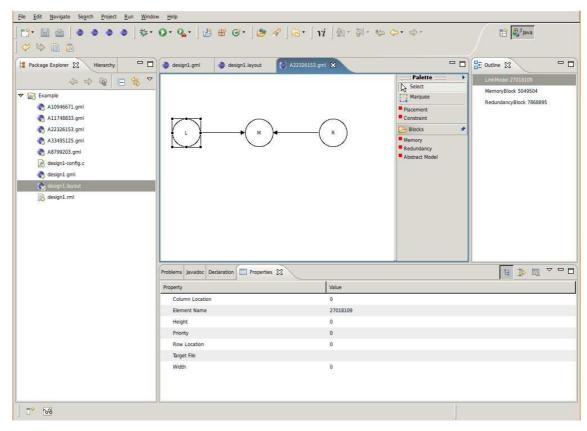

|     | 6.2   | Layout and graphical models of the example device              | 85        |

|     | 6.3   | Full Text Model                                                | 85        |

|     | 6.4   | Minimal Model                                                  | 86        |

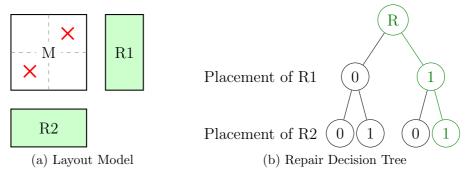

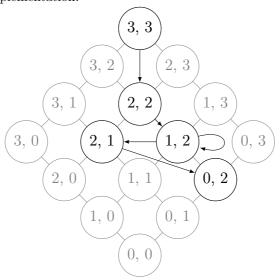

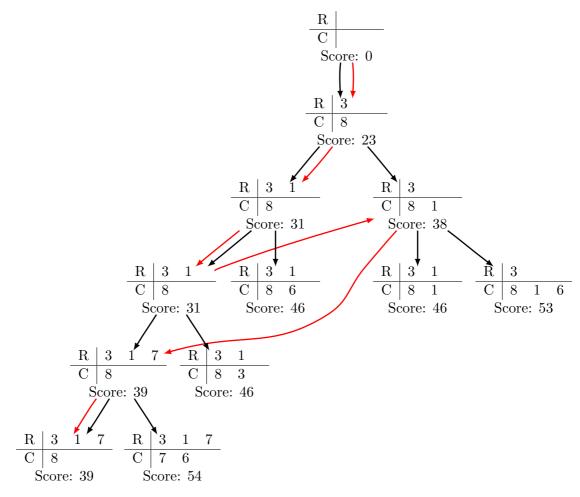

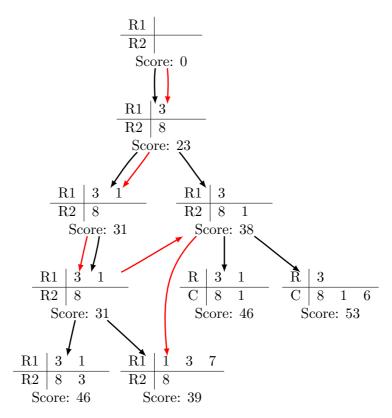

|     | 7.1   | Repair Decision Tree                                           | 89        |

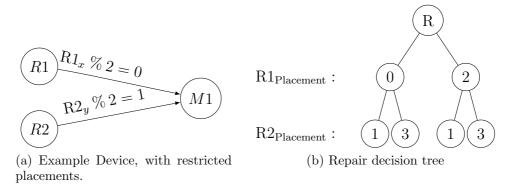

|     | 7.2   | Repair Decision Tree                                           | 93        |

|     | 7.3   | Repair Decision Tree, limited by placements                    | 93        |

|     | 7.4   | Repair Decision Tree, limited by constraint                    | 94        |

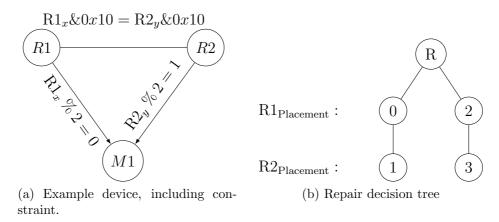

|     | 7.5   | Repair Regions                                                 | 95        |

|     | 7.6   | Independent Banks                                              | 97        |

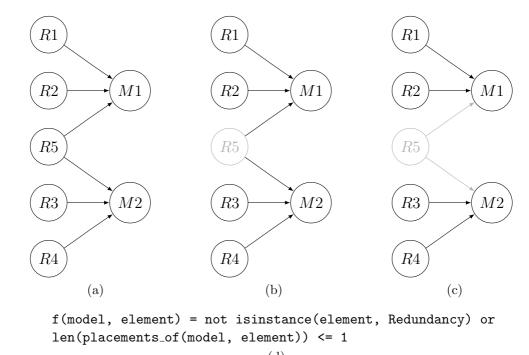

|     | 7.7   | Example Filter Function and Effects                            | 100       |

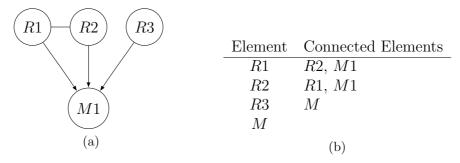

|     | 7.8   | Connected Elements                                             | 101       |

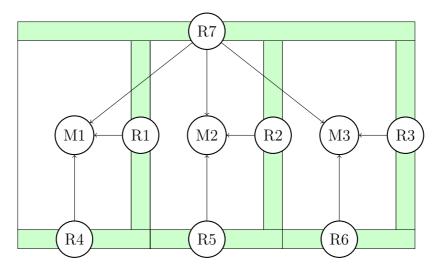

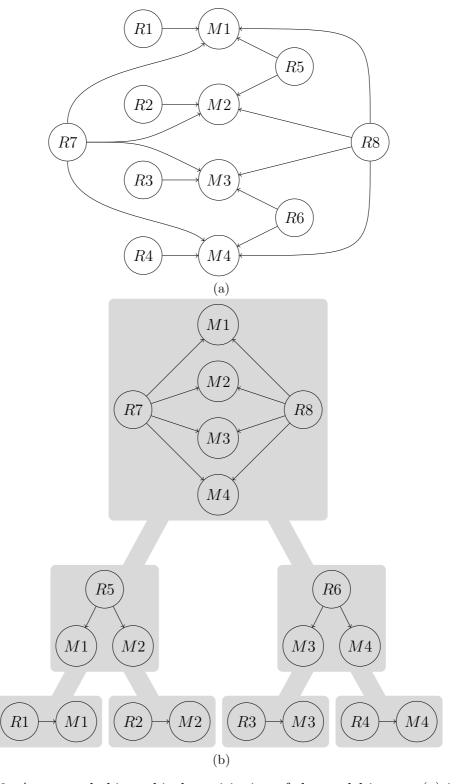

|     | 7.9   | An Example Hierarchical Partitioning                           | 102       |

|     | 7.10  | Template architecture                                          | 106       |

|     | 7.11  | Class Responsibilities and Control Flow During Code Generation | 108       |

|     | 7.12  | Class Responsibilities and Control Flow (Complex Examples)     | 112       |

|     | 7.13  | Example Device                                                 | 115       |

|     | 8.1   | Advantest Memory Repair Analysis Tool [mra01]                  | 120       |

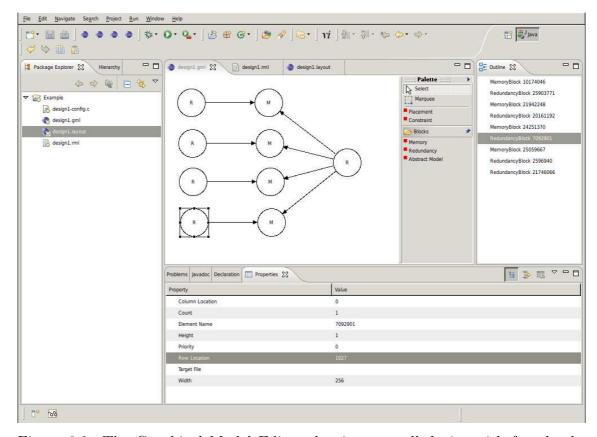

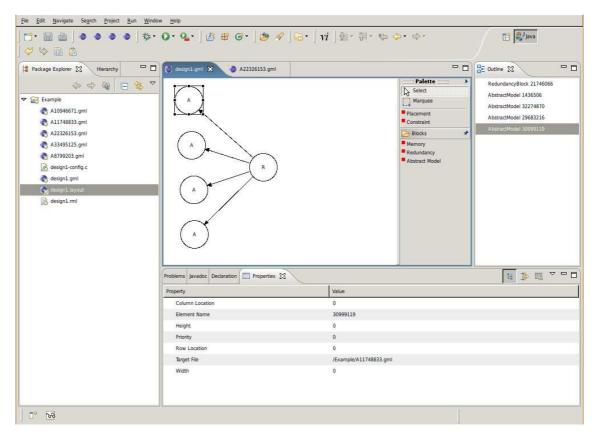

|     | 8.2   | Graphical Model Editor                                         | 122       |

|     | 8.3   | High level tool architecture block diagram                     | 129       |

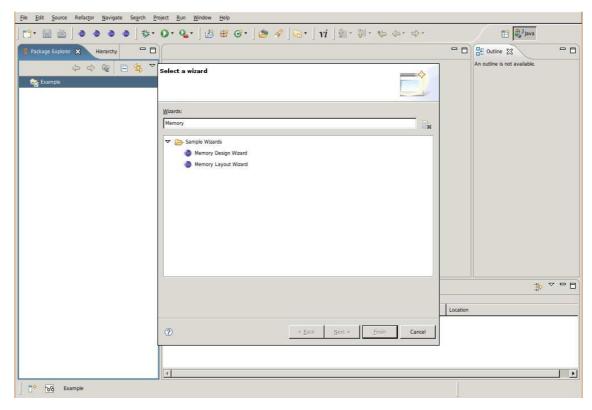

|     | 8.4   | New Design Creation                                            | 138       |

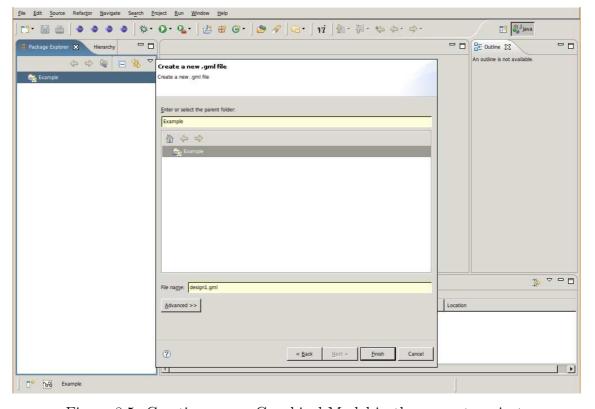

|     | 8.5   | Create New Graphical Model                                     | 138       |

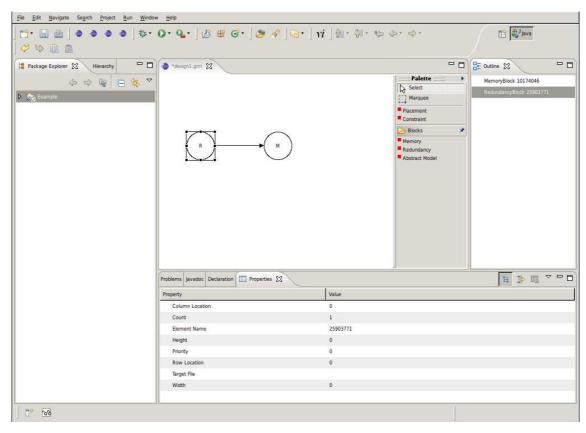

|     | 8.6   | Initial Graphical Model                                        | 139       |

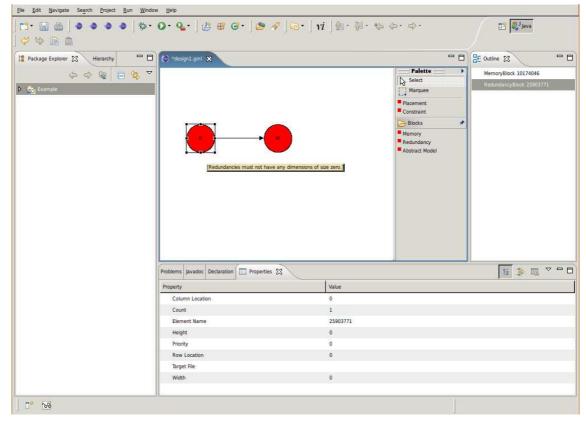

| 8.7  | Syntax Error Highlighting                     |

|------|-----------------------------------------------|

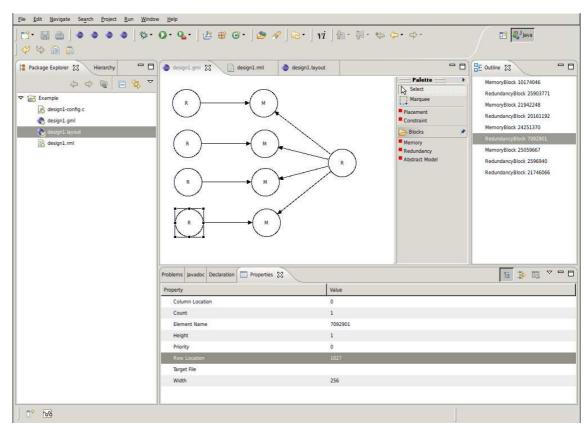

| 8.8  | Graphical Model Editor                        |

| 8.9  | Use of Abstract Models                        |

| 8.10 | Contents of Abstract Model                    |

| 8.11 | Layout Editor                                 |

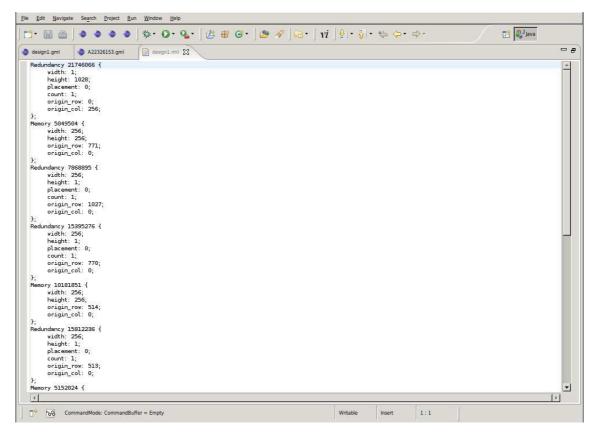

| 8.12 | Text Model Editor                             |

| 8.13 | Generated Configuration File                  |

| 9.1  | Experimental Device and Failure Map           |

| 9.2  | Experimental Results: Repairs                 |

| 9.3  | Experimental Results: Consumption Diagrams    |

| 9.4  | Experimental Results: Execution Flow Diagrams |

|      |                                               |

# List of Tables

| 3.1 | Parameters for the statistical failure model  |

|-----|-----------------------------------------------|

| 4.1 | Redundancy analysis complexity comparison     |

| 4.2 | Repair Algorithm Comparison                   |

| 5.1 | Mathematical Model Elements                   |

| 5.2 | Placement Representations                     |

| 5.3 | Common placement examples                     |

| 6.1 | Placement and Constraint Expression Variables |

| 6.2 | Placement and Constraint Expression Operators |

| 7.1 | Identified Regions                            |

| 7.2 | Regions identified for the example device     |

| 8.1 | Tool Release Details                          |

| LIST ( | LIST OF TABLES xii                                            |  |  |

|--------|---------------------------------------------------------------|--|--|

| A.1    | Basic Methods of the Template API                             |  |  |

| A.2    | Advanced Methods of the Template API                          |  |  |

| A.3    | Language Specific Methods of the Template API                 |  |  |

| A.4    | Language Specific Methods of the Template API (continued) 170 |  |  |

| A.5    | Variables of the Algorithm Class                              |  |  |

| A.6    | Methods of the Algorithm Class                                |  |  |

# Chapter 1

## Introduction

The manufacture of dynamic random access memories (DRAM) is a low yield process. Adding a small amount of redundant memory capacity allows the repair of many devices which would otherwise be unusable. To maximise the memory density limitations may be placed on the use of this redundant capacity and, as modern devices become larger, these limitations become more complex.

As the equipment necessary to test and repair DRAM devices requires a very large capital investment, and the value of each device tested and repaired is small, in order to maximise the return of this high value equipment the time taken for test and repair must be minimised, and the throughput maximised.

Redundancy analysis algorithms are responsible for solving the NP-Complete problem of optimally using this redundant capacity to repair faults in a failed device. Currently these redundancy analysis algorithms are designed, and customised, manually for each new device. This manual construction of repair algorithms is error prone and handling the high level of complexity is difficult.

The development of a tool capable of automatically generating customised redundancy analysis algorithms would automatically handle the high complexity inherent in current DRAM devices, and the increased complexity of the next generation devices. Automatic algorithm generation requires a formal description of the redundancy structures in a DRAM device. Both this description, and the automatic

algorithm generation are implemented in a prototype tool presented here.

### 1.1 Requirement for DRAM Redundancy

As the memory density of DRAM devices increases the manufacturing process becomes more sensitive to defects reducing the overall yield, and as new devices often operate at the limits of the manufacturing process the yield is further reduced. Many devices fail due to defective cells in the memory array: these devices could be made viable if redundant memory capacity were to be included in the device, along with some means by which this redundant capacity could replace faulty cells in the memory array, thus improving the overall yield.

The provision of this extra memory capacity and the logic to allow its use requires extra silicon area on the die, reducing the maximum capacity possible for a given process and silicon area available.

### 1.2 Redundancy Implementation

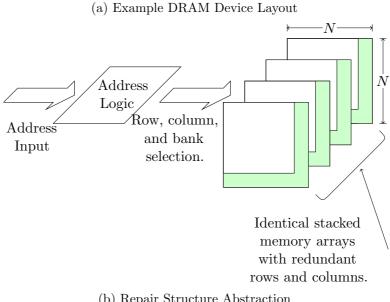

The redundant capacity in DRAM devices is provided by memory arrays with increased capacity; programmable address logic allows the remapping of addresses in the memory array into this redundant capacity. This redundant capacity is often modelled as a set of spare rows and spare columns repairing rows and columns in the main array.

The programmable address logic is controlled by a set of fuses, laser cut or non volatile memory, which can be set after manufacture to control the placement of specific rows and columns of redundant capacity. These fuses, and the additional wiring and logic required to implement the redundant capacity takes a considerable area on the chip; in an attempt to reduce the silicon area required to implement redundancy (and therefore to increase the amount of storage per device) compromises are made in both the logic, and in the number of fuses. Reducing the number

of fuses, or simplifying the remapping logic, introduces complexity into the repair process: limiting the addresses at which some redundant rows and columns may be placed, and constraining the addresses which redundant rows and columns may repair dependant on the use of other redundant capacity.

#### 1.3 Repair Process

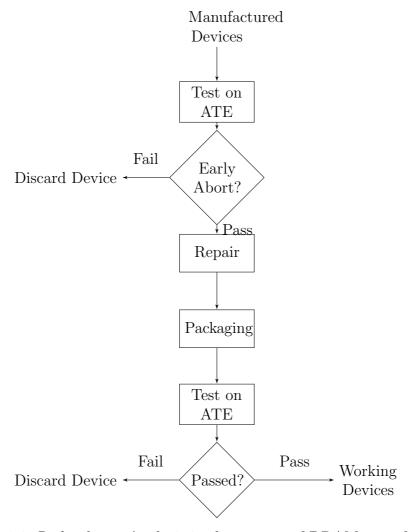

Understanding the process by which memory is tested and repaired allows a greater understanding of the limitations placed upon redundancy analysis algorithms by the environment. After DRAM devices are manufactured they are tested before packaging. Each die is tested, those shown by a heuristic test to be probably unrepairable are discarded. A redundancy analysis algorithm calculates a repair solution for each device, and the results written to the fuses, after which the devices are packaged. The devices are tested once again, and those still faulty are discarded; figure 1.1 outlines this process.

As can be seen from figure 1.1, redundancy analysis must take place in the critical path of DRAM manufacture. As a result, and due to the huge cost of the automatic test equipment, there is a strong incentive to reduce the time taken by redundancy analysis. Many redundancy analysis algorithms allow a trade-off between the time taken for analysis (the throughput) and the performance: an algorithm taking less time is likely to achieve a lower overall yield than an algorithm taking more time.

### 1.4 Redundancy Analysis Algorithms

Redundancy analysis algorithms are responsible for selecting from all the possible combinations of uses of redundant elements one potential solution. Selecting the optimum from all the potential solutions has been shown to be NP Complete for a single memory array with a number of spare rows and columns with no limits on their placements and no interdependencies. As memory size increases (both of memory array, and the number banks) the size of the repair problem also increases. The

Figure 1.1: Redundancy Analysis in the context of DRAM manufacture.

introduction of limitations and interdependencies between redundant elements decreases the number of possible solutions but makes the selection of possible solutions given a set of failures more complex.

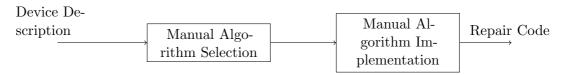

The current generation of redundancy algorithms are designed, and customised to each new device, manually; figure 1.2 illustrates this approach. The size and complexity of devices, and the lack of a formal modelling methodology for redundancy structures in DRAM, makes this manual approach either very time consuming or compromises in the correct handling of the complex interdependencies found.

Figure 1.2: The manual repair process: the memory design is interpreted by an engineer, an algorithm selected, and the algorithm manually implemented.

#### 1.5 Industrial Background

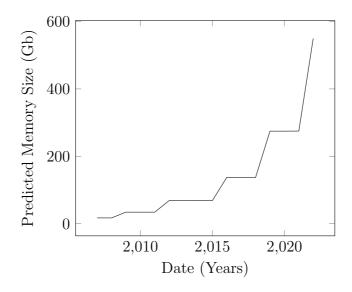

The International Technology Roadmap for Semiconductors (ITRS) [fS07] predicts an increase in the memory density and the size of DRAM devices; figure 1.3, compiled from the ITRS data, shows this predicted increase in memory size. As the memory size and density increases the size of the redundancy analysis problem becomes much larger, and the complexity of the limitations and constraints imposed by area optimisations is also increased.

Figure 1.3: Capacity of DRAM devices as predicted by the ITRS. Compiled from tables 1e and 1f of [fS07].

Despite the relatively low value of each DRAM device the massive number of devices produced means that even small improvements in yield made by improved redundancy analysis algorithms can be worth many millions, even billions, of dollars.

1.6. Problem 6

#### 1.6 Problem

Given the large memory capacity and complexity of the redundancy structures in modern DRAM devices, both of which are expected to increase, the manual construction and customisation of redundancy analysis algorithms is often unable to correctly represent the device complexity, and may include manual errors, leading to overall yield loss.

### 1.7 Proposed Solution

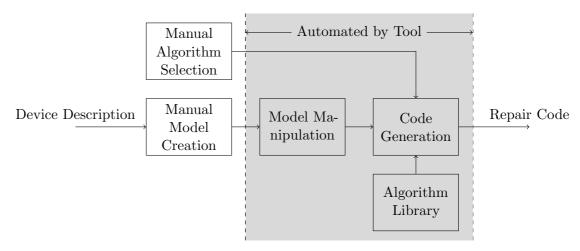

The creation of a tool to automatically generate and customise repair algorithms, accounting for the high complexity in modern devices, could eliminate the errors introduced by manual algorithm design and greatly reduce the engineering time required. Automatic generation of redundancy analysis algorithms requires a formal description of the redundancy structures in a device; this description, or model, must be capable of representing not only memory and redundancy arrays but also all the limitations and interdependences imposed upon the uses of that redundant capacity.

To use such a tool the user must first describe the device; two input methods are proposed, a parser for a simple text based language describing the model, and a graphical editor manipulating an intuitive graph based representation of the model.

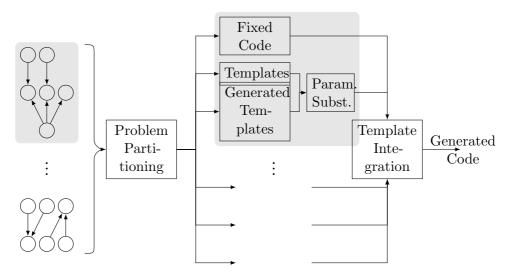

From these inputs the tool can construct an internal representation of the device. Techniques are proposed to use this model representation to customise repair algorithms including optimisations based on the model structure. Figure 1.4 shows an overview of such a system.

### 1.8 Sponsorship

This project has been sponsored by both the Engineering and Physical Sciences Research Council (EPSRC) and Verigy under an EPSRC Industrial CASE. Verigy

Figure 1.4: Proposed System Overview: The user must first describe the device using the graphical editor and select the repair algorithm required. The tool then manipulates the model and draws upon a library of repair algorithms to generate repair code.

manufacture both logic and memory automatic test equipment (the 93000 and V6000 series respectively). Verigy was formed in 2006 from the parent company Agilent, who in turn spun out from Hewlett-Packard in 1999.

The project has also included two internships at Verigy in Cupertino, CA during the summer of 2007 and 2008.

## Chapter 2

## Background

Before developing a solution to the problem proposed this chapter will give an overview of the history of repairable DRAM devices, of the causes of complexity in modern devices and a review of modelling techniques. An outline of the redundancy analysis problem will also be presented.

### 2.1 Introduction to Repairable DRAM

The first repairable memory devices were configured using discretionary wiring [CDJ67], after manufacture extra metal layers were used to connect only good cells forming a functioning memory array. Later [TA67] discretionary wiring was used to connect only good rows, simplifying the metal layers required. In 1969 Chen [Che69] extended the method to include both good rows and columns.

Much later, in 1978, Schuster *et al* [Sch78] introduced the reconfigurable device common today; using extended address logic and a bank of laser cut fuses [KGB<sup>+</sup>84] row and column re-mapping could be controlled without discretionary wiring (some more advanced devices use electrically reprogrammable fuses [KGB<sup>+</sup>84]). This system of redundant capacity allocated by manipulations in the address logic and controlled by a set of fuses, written to after manufacture, is still in common use today.

As devices became more complex the problem of optimally allocating spare rows

and columns to repair the devices became more time intensive. In 1986 Kuo and Fuchs showed that this spare allocation problem was NP Complete [KF86]. They developed a branch and bound technique with a cost function dependent on the type of element to quickly arrive at the optimum solution.

As any repair algorithm must be run between the testing and repair of each manufactured device the time taken in redundancy analysis has a direct impact on the throughput of the manufacturing process. In an attempt to reduce the running time, and increase the throughput, heuristics are used to either discard the device if it seems unrepairable, or to reduce the search space of the spare allocation problem (SAP). Kuo and Fuchs use the Must Repair heuristic [Day85] to provide a seed solution for their NP Complete SAP solver.

An alternative approach to solving the SAP (with shared spares) was proposed by Kuo et al [LYCK04, YTH+05, LFMK06] where the problem is represented as a set of boolean functions manipulated using a Binary Decision Diagram. The algorithm developed is a perfect algorithm that like the branch and bound algorithm, will always find the optimum solution. The later papers extend the modelling approach, and map the SAP to the use the well known Boolean Satisfiability Problem; as there are many application of boolean satisfiability problem solvers, there are many available implementations.

Modern practical repair of DRAM devices relies on early abort heuristics [TBM84] to prevent repair being attempted on unrepairable dies, followed by heuristic repair algorithms the result of which is used to reduce the search space for an NP complete solver. Very often must repair is used to generate an initial solution before the application of an NP complete SAP solver [Bha99].

The International Technology Roadmap for Semiconductors [fS07] predicts an increase in the complexity of redundancy structures in DRAM devices. This increase in complexity increases the search space a repair algorithm must traverse making efficient repair algorithms even more important, but also increases the complexity an engineer must manage when creating a device description from which the repair algorithm could be customised. Understanding the causes of this complexity allows

more efficient algorithms to be developed, but also allows modelling of the redundancy analysis problem and therefore the development of algorithms to manipulate the device model and create redundancy analysis algorithms.

### 2.2 Structure of Repairable RAM Devices

Analysis of the structure of repairable RAM devices allows the development of better repair algorithms, but it also provides the necessary information to develop an accurate model of the redundancy structures which in-turn allows the automatic manipulation and exchange of repair algorithms.

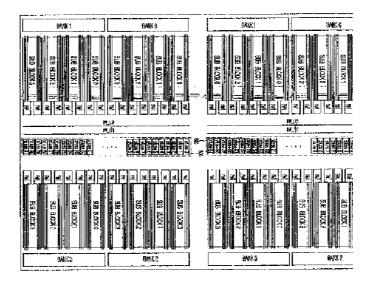

The basic description of modern DRAM devices is still similar to that given by Schuster [Sch78], with extra logic and a set of fuses controlling the use of redundant rows and columns; though modern devices are considerably more complex. Redundant rows and columns may be shared between one or more memory arrays, and these sets of redundant elements and memory blocks may be arranged into many banks.

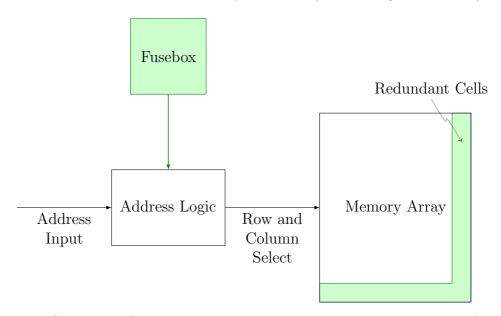

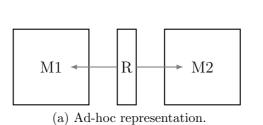

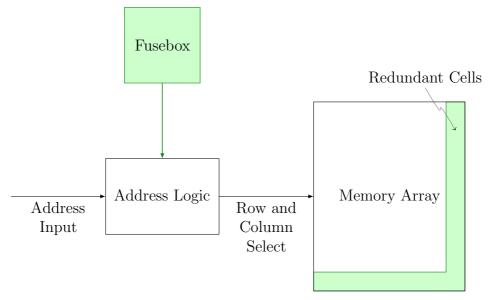

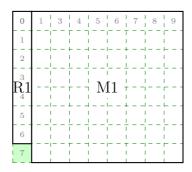

Figure 2.1: Simple DRAM structure, those blocks with additional blocks for repair with redundant spare rows and columns.

Figure 2.1 represents the key elements in one such bank: incoming addresses are translated by the address logic into addresses in the memory array, the bits in the fusebox control that mapping. The design of DRAM devices is under constant

pressure to increase memory density, which is possible by reducing the area required for redundancy structures. One such reduction is possible, by the sharing of fuses within the fusebox [Vol98], further reductions are possible by the elimination of a number of fuses to be replaced by either permanently open or permanently closed circuits.

## 2.3 Causes of Complexity

These reductions made in the silicon area available for redundant memory add complexity to the spare allocation problem: hard wired fuses impose restrictions on the addresses at which redundant cells can be used, and the sharing of fusebox bits introduces dependencies between sets of redundant cells where the use of one set of redundant cells can impose restrictions on the use of one or more other sets of redundant cells.

#### 2.3.1 Hard Wired Fusebox Bits

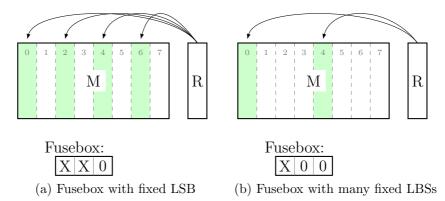

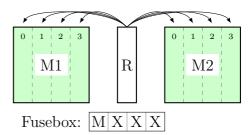

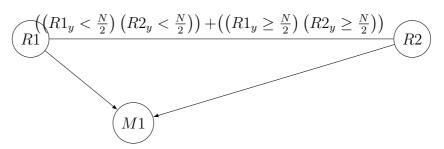

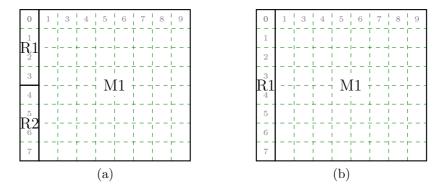

The hard wiring of fuse box bits (*i.e.* their replacement by permanent connection or disconnection) imposes restrictions upon the use of a single set of redundant cells. The fixing of the least significant fusebox bit limits the placement of the relevant set of redundant cells to addresses with a matching least significant bit: should the fusebox least significant bit (LSB) be set to zero, then the address at which the set of redundant cells is used must be even, as shown in 2.2a.

Fixing the two least significant bits in the fusebox to zero restricts the use of the set of redundant cells to addresses at multiples of four, fixing the last three bits restricts to addresses at multiples of eight, fixing more bits increases the address as expected, as can be seen in figure 2.2b.

Fixing the most significant bit (MSB) in the fusebox similarly restricts the addresses at which a set of redundant cells can be used. Setting the most significant bit in the fuse box to one limits the placement of a redundant element to the top half of the

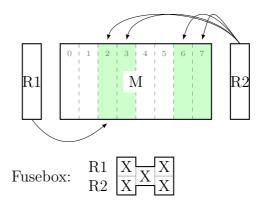

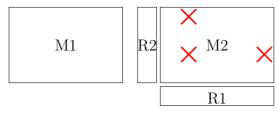

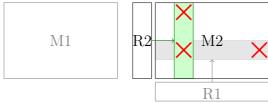

Figure 2.2: The effects of fixing least significant bits in the fusebox. Given the fusebox settings shown (X denotes don't care bits) the redundant column R can be placed only at the shaded columns in M.

memory 2.3a, that is only those addresses where the MSB is set. It is possible that a combination of fusebox bits may be hardwired, in which case the limitations on the use of a set of redundant cells becomes more strict: figure 2.3b shows the result of a MSB set to one and a LSB set to zero.

Figure 2.3: The effects of fixing most significant bits in the fusebox, and of the combination of setting the most and least significant bits in the same fusebox (X denotes don't care bits.)

#### 2.3.2 Shared Fusebox Bits

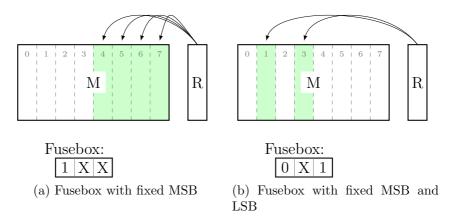

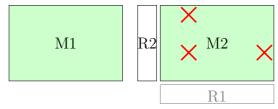

An alternative technique for reducing the area required by redundant structures is to share some bits in the fusebox between redundant elements, however when this is done the use of one redundant element may be limited by the use of another. For example, if two redundant elements share the least significant fusebox bit then if one is placed on an odd address so must the other, and visa-versa: if the most significant bit is shared then both redundant elements must be placed in the same address range; figure 2.4a illustrates such a case.

- (a) Effects of a fusebox with a shared MSB

- (b) Effects of fixed and shared fusebox bits

Figure 2.4: Effects of a fusebox with a single shared bit, and of combining shared and fixed fusebox bits (again, X indicates not fixed, or don't care bits in the fusebox).

Real devices have large fuseboxes, controlling the placement of many redundant elements, therefore the possibility for sharing and fixing of fusebox bits is greatly increased. Several types of exception arise from these area reducing compromises made in the fusebox: bits shared in the middle of the fusebox force the redundant elements to be placed at a region offset from the original placement, as shown in figure 2.5.

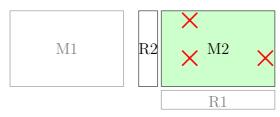

Figure 2.5: The two redundant elements R1 and R2 share a single fusebox bit. If R1 is placed at column 2, with the fusebox 010, then the fusebox for R2 must be X1X (again, X denotes don't care bits), limiting the placement of R2 to rows 2,3,6 and 7.

Given these large fuseboxes in realistic DRAM devices the possible limitations which the use of one redundant element may place on another can become very complex. By the sharing a number of the least significant fusebox bits two redundant elements must be placed at a multiple of a certain address apart: should the two least significant fusebox bits be shared between two redundant elements then given the placement of one redundant element the other must be placed at an offset of a multiple of four bits from the original redundant element.

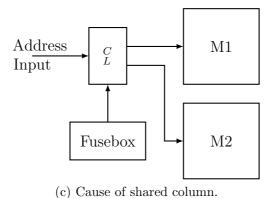

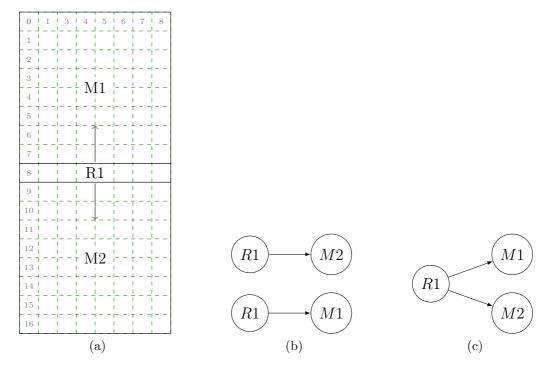

#### 2.3.3 Shared Redundant Elements

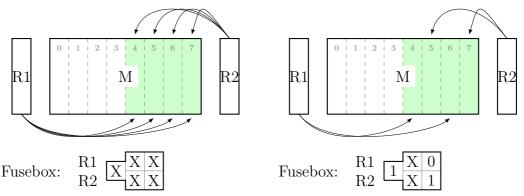

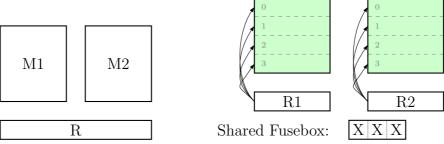

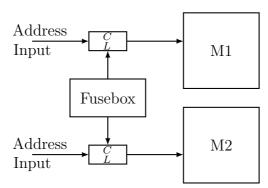

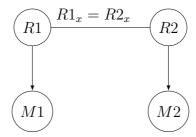

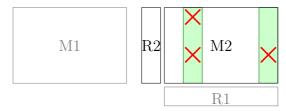

An alternative technique for reducing the area required for redundant structures is to share a whole fusebox between redundant elements which are placed in different memories, thus if redundant rows R1 and R2 are placed into memory arrays M1 and M2 respectively, and share a fusebox (figure 2.6c) then they must both be used at the same row address (2.6b) and resemble a single larger row, spanning the width of both memory arrays, and as a result are often represented as such in ad-hoc models as shown in figure 2.6a)

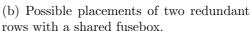

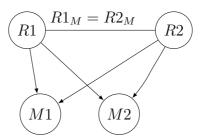

In addition to sharing fuseboxes between redundant elements, redundant elements with a single fusebox can be shared between memories [TK99]. Figure 2.7a shows the commonly used representation of such a shared column, figures 2.7b and 2.7c show the fusebox and logic configuration that cause this exception.

In a large complex device, such as [YHO97, JHCHKC<sup>+</sup>96, K<sup>+</sup>99], it is very probable that not only will all these exceptions be seen, but also that many of the exceptions may be combined. This additional complexity introduces the size of the spare allocation problem and the complexity of repair algorithms, increasing the cost of repair calculation, with possible impact on the overall test and repair throughput and therefore on the cost of the final product.

#### 2.4 Modelling DRAM devices

One of the best ways to work with very complex problems is to create a model, from a formal mathematical model to the implicit models created by the data structures

(a) Common Ad-hoc representation of redundant rows with shared fusebox.

(c) Block diagram of a DRAM device, illustrating the sharing of one fusebox between two address decoders (marked CL).

Figure 2.6: Representations of a redundant row shared between two memory blocks such that a row repair in the first memory requires a row replacement at the same address in the second memory.

within a computer program. Once a model has been developed it is possible to manage the high level of complexity, including the implementation of abstraction barriers to allow a user to concentrate on only those elements of the complex problem of particular interest.

Often, ad-hoc models and sketches of DRAM redundancy structures are used (as seen in the previous sections), for example 2.8 from [HD00] and [LTH+06], however these models cannot easily represent the complexity of element locations and effects of fusebox optimisation in even a small device.

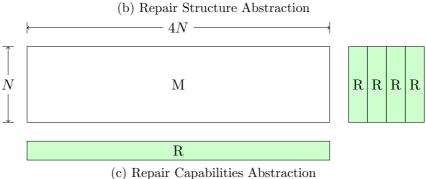

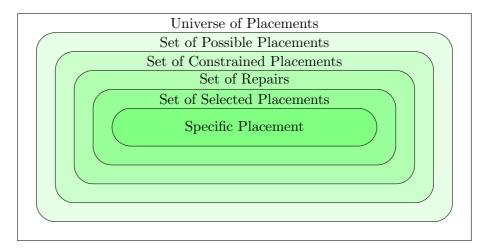

A model of DRAM redundancy need only represent those structures in the device relevant to redundancy analysis: the memory arrays, the redundant elements, their use, and the exceptions placed upon them by the fusebox optimisations.

The common model used in [KF86] can be trivially extended to cover shared redun-

(b) Shared fusebox representation, X bits in the fusebox denote don't cares, the M bit selects the memory array.

Figure 2.7: The redundant column R can repair in either memory M1 or M2. The extra bit it the fusebox, marked M, select the memory addition bits select the address.

dant elements, for example [SVZ01] and [YHAA<sup>+</sup>], but representing the exceptions found in real complex devices is often impossible (models do exist for simpler embedded devices [SDM<sup>+</sup>05]), any new model must be developed capable of representing all the complexity seen in modern, and future, devices.

The availability of accurate models allows the development of tools to manipulate complex problems, such as efficient use of grid computing resources [Hoh06a, Hoh06b]; allows the exchange of data with known reliability, and most importantly the development of algorithms to manipulate the model. Without a model, or with an unsuitable model, many of these techniques become at best very difficult, and at worst impossible.

To allow the creation of repair algorithms from a model of DRAM the model must be capable of expressing all the possible combinations of the types of complexity detailed above — in a large complex device [GSP91] many of the exceptions will be combined. If the model and associated tools are to be continually useful then the

Figure 2.8: Example complex device from [HD00].

model must be capable of representing any combination of complexity.

### 2.5 Repair Algorithms

Kuo and Fuchs [KF86] have shown the spare allocation problem to be NP Complete. That is any repair algorithm which attempts to arrive at a perfect solution is NP Complete (a perfect solution is one that is known to be optimal for a given device and a given set of failures). Another class of redundancy analysis algorithms trades the guarantee of a perfect solution in order to reduce complexity and therefore the time taken for repair.

Filtering out those devices which cannot be repaired before attempting the costly repair process can increase overall thoughput. Often heuristic early abort filters [TBM84] are used to sort devices into three types: faulty unrepairable devices, faulty repairable devices, and correct devices, ideally eliminating the time spent attempting to repair unrepairable devices but at the cost of a heuristic incorrectly marking a repairable device at unrepairable.

Heuristic repair algorithms are also often used to reduce the search space for an NP complete algorithm, by suggesting an initial set of repairs [HL88, BP93, LL96a,

Blo96, LL96b, SF92]. The two most common heuristic algorithms are the Must Repair [Day85, Bha99] and Most Repair or Greedy algorithm. The greedy repair algorithm calculates the number of failed cells in each row and column in the memory array, and repairs, in order, those with the most failed cells until no more redundant resources are available; this is a common heuristic approach to NP complete problems. The must repair algorithm again calculates the sum of failed cells in each row and column in the memory array. Each row with more failed cells than there are unused redundant columns is marked as a must repair, and one of the redundant columns is marked as used. The same criteria are used to denote must repair columns, and are re-applied recursively until either there are no redundant resources available, or no further must repairs. The must repair algorithm is so named as any row in the memory with more failed cells than there are available redundant columns can only be repaired by a redundant row: if the device is to operate correctly that row must be repaired. The must repair algorithm does not produce a complete solution for the repair of a device; very often there will be a number of failures not matching the must repair criteria. The solution generated by the must repair algorithm is used to seed an NP Complete solver, again reducing the size of the SAP, decreasing repair time, and increasing overall throughput.

Other methods have been used to try and solve the spare allocation problem in reasonable time, without the use of heuristics: the expression of the SAP as a boolean satisfiability problem [LYCK04, YTH+05, LFMK06] and genetic algorithms and neural networks [CS96] to optimise repair algorithms, but these approaches are uncommon in practice.

## 2.6 Proposed Solution

The implementation of the tool proposed in the introduction (section 1.7) as a solution to the problem of generating customised DRAM redundancy analysis algorithms and their implementation on a given platform will cover many areas of previous scientific investigation.

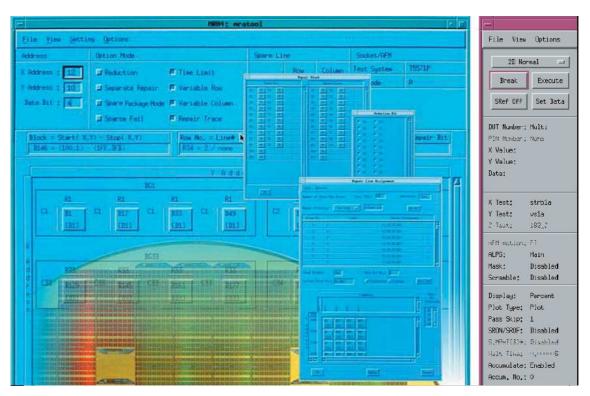

There is only one direct competitor for the tool proposed in this thesis: "MRA tool" developed by Advantest [mra01]. MRA tool provides a graphical interface representing a much simplified model of a DRAM device and it is capable of customising some repair algorithms.

As there are few comparable tools described in literature it is interesting to examine a number of similar tools that are described; by recognising those areas which the proposed tool must cover and understanding tools which cover one of those areas valuable comparisons may be made.

Graphical tools are often used to model complex problems, a particular example in this field is the DRAM BIST Tool described in by Su et al in [SHZL01]. This tool provides a graphical editor for the patterns used to test DRAM devices, allowing the user to design march patterns. The tool parses this pattern description and generates test code implementing these patterns and circuit descriptions of the BIST logic. The tool can generate test code for many different devices and many different test algorithms.

CACTI is a mature modelling program [TAM<sup>+</sup>08] representing many memory based products; for example commodity DRAM on a DIMM module, embedded SRAM in a system on chip design, or cache memory in a processor. CACTI models several physical properties of a memory system: particularly power consumption and read-/write timings, allowing a designer to simulate the use of several competing memory products in a particular application and select the device most suitable for their specific needs.

Like CACTI, the development of DRAMsim [WGT+05] has been driven by the growing disparity between CPU and DRAM core speeds. DRAMsim provides an easily configurable model of the whole memory system, providing a large number of configurable model parameters to accurately represent a particular device and allow performance comparisons between different devices and technologies in a given system and can provide estimates of manufacturing cost for each system.

A modelling framework closer to that proposed in this thesis is Raisin [HLYW07].

2.7. Conclusions

Raisin is a framework for the evaluation of DRAM redundancy analysis algorithms, and for the planning and optimisation of the redundancy strategies used during the design of DRAM devices. To perform this evaluation Raisin provides a simple, text based model of the structure of DRAM, a simulator generating memory failure bitmaps and a framework in which to execute sample redundancy analysis algorithms and record their running times and repair performance. Raisin can perform this analysis for a range of different devices and with different model parameters allowing comparisons between redundancy analysis algorithms in realistic situations.

Of these tools only MRAtool and Raisin deal directly with DRAM repair, but they do demonstrate the need for tools to manipulate complex problems (DRAM BIST tool's graphical march test editor), and all show the power of simulation in the design and optimisation of large systems.

Raisin might seem suitable for possible integration with the tool being developed here however the model developed is not sufficiently flexible to represent the devices on which the tool is expected to operate (section 5.2 for a further discussion of the model used by Raisin).

The tool developed by Advantest, MRA tool, provides a graphical interface to the internal model of DRAM but this interface cannot represent the complexities and interdependencies found in modern DRAM devices (as described in sections 2.3 and 2.4). The tool proposed as a solution to the problem described in the introduction requires a more sophisticated model of DRAM devices to properly represent the complexity and generate redundancy algorithms with a high yield.

#### 2.7 Conclusions

This chapter has surveyed the history of repairable dynamic access memories: from individual good cells connected by discretionary wiring, good rows and later good columns also connected by discretionary wiring ending finally with the controllable address logic and fusebox used today. Pressure to reduce the silicon area devoted to redundant structures forces compromise in the fusebox: the elimination of con-

2.7. Conclusions

figurable bits in favour of hard-wired and the sharing of configurable bits between one or more redundant elements.

The development of the tool proposed as a solution to the problem set out in the previous chapter must cover many areas: the structure of DRAM, including the complexities and interdependencies imposed upon the use of redundant resources by the physical design of the device; the modelling of this structure and the provision of a graphical tool to manipulate this model and subsequently generate customised redundancy analysis code solving the spare allocation problem.

Analysis of the spare allocation problem has shown it to be NP Complete, and that the execution time effects, directly, the overall throughput of the manufacturing process. The increasing complexity of redundancy structures makes both modelling the device and solving the spare allocation problem more challenging, so much so that current algorithms often combine heuristic methods with an NP Complete solver to reduce repair time. Commercial solutions have been known to ignore aspects of this complexity with a measurable yield loss.

As devices become more complex, and the uses of redundant elements more interdependent, previous ad-hoc methods of modelling redundant structures become a limiting factor when exchanging designs and generating repair algorithms specific to a device. A generic model of DRAM would allow the exchange of designs, the creation of tools to manipulate and translate the model, and the automated generation of repair algorithms and code.

Evaluating DRAM repair algorithms requires a source of many failure bitmaps. Manufacturers of DRAM devices regard this failure data as highly sensitive intellectual property and are reluctant to release it to any external entity. If a statistical model of failure bitmaps can be constructed then not only can this obstacle be avoided but a wide range of devices can be simulated, over a range of manufacturing yields, allowing a more thorough investigation of the algorithms than would be possible with real failure data.

The following chapters will investigate repair algorithms for DRAM using a statis-

2.7. Conclusions

tical yield model; the structure of DRAM will be examined, and mathematically modelled including both an intuitive, user friendly, graphical model and a machine friendly text model language. Functions will be defined to manipulate these models and techniques developed to generate code for repair algorithms and ATE configuration. Finally these modelling and code generation ideas will be integrated in a prototype graphical tool.

# Chapter 3

# Modelling DRAM Failure Maps

#### 3.1 Introduction

Experimenting with DRAM redundancy repair algorithms requires a large number of failure bitmaps, ideally showing a wide range of: bitmap size, overall yield, and error clustering properties.

Many models of failure maps in DRAM are designed for the analysis and improvement of memory test techniques, particularly the use of different march patterns; for example the RAMSES fault simulator developed by Wu et al [WHCW02]. These simulators are often used for development and characterisation of march test patterns which depends upon the type of faults encountered: a simple test pattern writing ones into each bit and expecting to read ones from each bit can only detect "stuck at one" faults; and so the simulator must replicate as many fault types as are expected in the memory device to be tested. Repair algorithms do not require information about the type of failure, only the location of those cells that have failed.

Obtaining a statistically significant number of memory failure bitmaps, from a range of devices can be difficult, making the comprehensive test of repair algorithms challenging. Though testing the large number of devices required would be time consuming, it would not be impossible; however, obtaining such devices, or the test data from such devices, can be difficult: memory manufacturers often see failure data as

part of their key intellectual property, and keenly protect it.

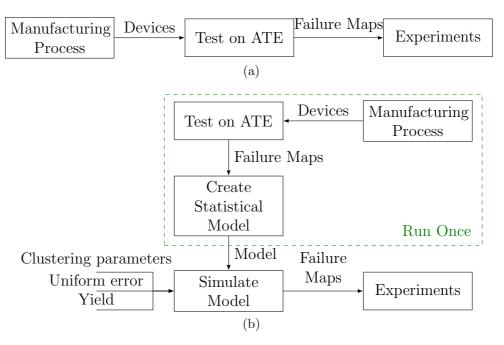

Figure 3.1a illustrates a possible methodology for such experiments using real memory failure maps: after manufacture devices are tested, producing a number of failure maps, on which experiments can be conducted.

Many frameworks for the analysis of algorithms manipulating memory failure bitmaps simulate the failed bitmap with a simple probability for failure of each cell [HLYW07, SVZ04]. However real devices show much more complex failure patterns. A common failure pattern is caused by a defect in the sense amplifiers or addressing logic forcing cells in a particular row or column out of the limits of their tolerance.

Approaching the test of repair algorithms using real memory failure bitmaps as the only input limits the points at which test data can be obtained. Data can only be taken from real devices at the sizes and yields at which they occur. A model, capable of producing memory failure bitmaps with many controllable parameters would allow testing of repair techniques over a wide range of devices and processes. A flexible model would also allow the simulation of the yield learning curve, where the test results of previous batches of devices are used to improve the next.

Developing such a model requires access to failure data during the initial construction, but once constructed could generate many failure maps without further access to real data. This model might take as parameters the size of the failure bitmap, the required yield, and a number of parameters describing the nature of the failures.

Figure 3.1b illustrates the construction of such a model: analysis of memory failure maps from real devices, followed by the establishment of a statistical model. The model can be used to produce many failure maps, with controllable clustering and yield parameters.

### 3.2 The Statistical Model

The faults common in DRAM devices have previously been categorised in many academic and industrial models. van de Goor [vdGAA00, AAvdG01] presents a

Figure 3.1: Experiments with Real and Modelled Failure Maps.

formal representation of fault models: a fault model is a set of fault primitives; each fault primitive represents a failure as a sensitising operation, and the observed and expected values read from the device after the sensitising operation.

In general industrial models of DRAM failure models are less formal than the academic model presented by van de Goor [Cro00]. This model is designed for the optimisation of test routines, particularly march patterns, and so must represent the type of failure. Models used for the testing and development of redundancy analysis algorithms need not represent the cause of failure, only the consequences. Such models assume that any failure anywhere in the device will manifest as a failure in the memory array; for example a fault in the address decoding logic might appear as a row of neighbour faults (where a cell, when read, returns the value of one of it's neighbours). Industrial models often limit the types of failure possible. Common faults represented are failures in single cells in the memory array, failures of complete rows or columns in the memory array, or failure of the complete memory array [DBT90].

The redundancy analysis framework Raisin [HLYW07] uses four parameters to control its failure bitmap simulation; a number of defects per die, the percentage of

faulty rows and faulty columns and clustered errors. In this scheme a fixed number of defects are injected into each die, these defects are distributed amongst the four fault types. (Probabilities are specified for the percentage faulty rows and columns and clustered errors, the probability of a single cell failure is not listed but defects not otherwise allocated form single cell errors.)

Ideally a model would be developed by analysis of many thousands of failure bitmaps from real devices; however in industry this information of closely guarded as key intellectual property which DRAM manufacturers are unwilling to release. Verigy hold a number of statistics about a certain commercial device and it is this data upon which the model described below is based.

A statistical model representing memory failure bitmaps must represent those failures which occur in real devices. There are two common causes of failures in DRAM devices: random defects, spread independently over the whole bitmap, often as a result of contamination during the manufacturing process and systematic defects, perhaps due to mask miss-alignment during manufacture, or defects in the supporting circuits.

Modelling the first of these fault types can be simple, each cell is assigned a probability that it will fail due to contamination, and each cell is considered independently.

Systematic defects affect sets of cells in the device; an imperfection in the sense amplifier for a column could lead to cells on that column functioning improperly, and failing, while other cells are unaffected. Both rows and columns have decoding circuits, but only columns have sense amplifiers: as a result the probability of a column failing may not be the same as that of a row failing. Should a part of the circuit driving a row or column fail then some of the cells on that row (column) may fail, while others continue to operate correctly.

The model described in this chapter is controlled by four parameters. The first of these, "Failure Map Size" describes the dimension of the memory array to be modelled; the units of each dimension are memory cells. As a result of die contamination or imperfections small areas of the device may not function, often this results

in one or more cells in the array; the model parameter "uniform failure probability" represents this chance of a cell failing. Should this contamination effect the circuits supporting the memory array then a particular row or column may fail (if for example the sense amplifier was rendered inoperable then none of the cells in the column read by that amplifier would function correctly). The model represents this probability of failure with the parameter "probability of row failure". These support circuits required for rows and columns differ: rows require only address decoders whereas columns require address decoders, sense amplifiers and connections to the data bus. As a result of this difference in complexity the probability of failure in support circuits for rows and columns differs, represented in the model by the parameter "ratio of row to column failures". It is possible that defects in the support circuits will not disable an entire row or column; for example a sense amplifier operating near the design tolerance may successfully read values from some cells on a column but not from others. To represent this limited operation the model describes the independent probability of each cell on a failed row or column failing, referred to as the "probability of cell failure on a failed row or column".

The values of individual model parameters can be derived from a simple analysis of failure bitmaps from a single device. Adjusting these parameters allows the simulation of devices with different yield (from that of original device), allowing experiments to be carried out at many points on the yield learning curve.

### 3.3 Implementation

The model described in the section above has been implemented using the Matlab programming language. The algorithm first adds independent failures to the bitmap, the uniform error probability determining the pass/fail state of each cell. The probability of a row having failed is considered to be the probability of a row or column failure multiplied by the ratio of row to column failures. Should a row be determined to have failed, each cell on that row has a higher probability of failure; Columns are considered similarly. Pseudo code for this procedure is shown in algorithm 1.

```

Algorithm 1: Failure Bitmap Generation

Input: Model Parameters

Output: Memory Failure Bitmap, bitmap

bitmap = Array of Failure Bitmap Size square working cells

foreach Memory Cell in bitmap do

if Random (0...100) < Uniform Error Probability then

Memory Cell = Failed

foreach row in bitmap do

if Random (0...100) \leq \text{Row Failure Probability then}

foreach Memory Cell in row do

if Random (0...100) < Probability of Cell Failure on a Failed Row then

Memory Cell = Failed

foreach column in bitmap do

if Random (0...100) < Ratio of Row to Column Failures × Row Failure

Probability then

foreach Memory Cell in column do

if Random (0...100) \leq Probability of Cell Failure on a Failed Row then

Memory Cell = Failed

```

| Parameter                                             | Value (%) |

|-------------------------------------------------------|-----------|

| Uniform error probability                             | 0.003     |

| Row/Column failure ratio                              | 0.8       |

| Probability of a row or column failure                | 0.5       |

| Probability of cell failure on a failed row or column | 80        |

Table 3.1: Parameters for the statistical failure model. The data used in the construction of this model is derived from data held by Verigy.

Matlab was chosen as the implementation environment as it allows rapid prototyping of largely mathematical algorithms, which was considered to be more important than the overall running time.

Though the model probabilities are derived from a single set of real failure data, manipulation of the parameters controlling uniform errors and row and column failures allows the simple simulation of a similar device at different points on the yield learning curve.

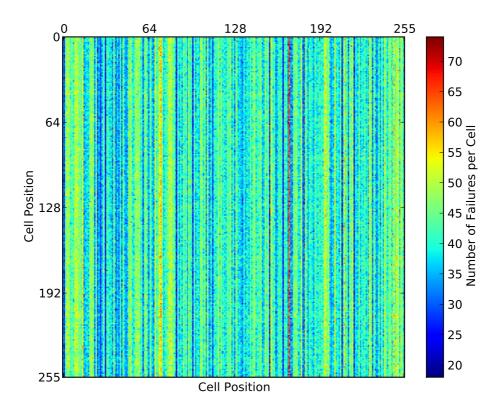

The values of the model parameters used are defined in table 3.1 and were derived from confidential failure data held by Verigy; an overlay of many generated failure maps is shown in figure 3.2. From this figure it can be seen that column failures are predominant, as expected given the model parameters. This overlay technique can be used for quick visual comparison of model data with real failure maps, for the assessment of model parameters.

Figure 3.2: In this overlay of ten thousand failure maps the colour of each cell shows the number of failures in that cell over all ten thousand bitmaps; the parameters used for all bitmaps are those shown in table 3.1.

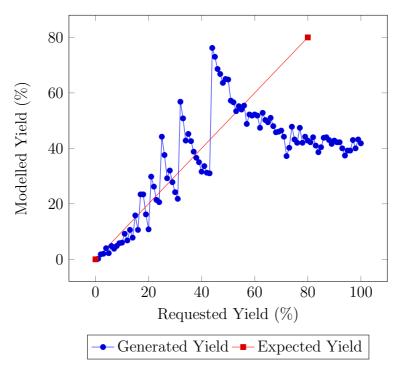

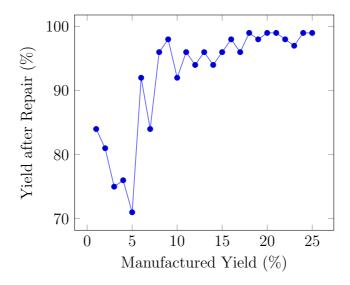

It is often useful to test repair algorithms at a range of yields. Without a statistical model the only yields available would be those from real tested devices. With a statistical model many yields can be simulated. Ideally the model parameters would be calibrated at each of these yields using real failure data. In the absence of such data it is possible to manipulate the uniform and clustered error probability to create failure maps of the required yield. The calibration curve shown in figure 3.3 shows, for each yield requested, the average (over 10000 bitmaps) of the yield generated. As can be seen from the curve, above approximately twenty percent average yield the accuracy of the model is very poor, experiments in later chapters will be restricted to yields of twenty percent or less.

3.4. Conclusions

Figure 3.3: Calibration curve for the yield model.

### 3.4 Conclusions

The yield model described in this chapter simulates realistic memory failure bitmaps, allowing the off-line test and comparison of any process which takes failure maps as an input (typically memory repair algorithms). Though realistic failure maps are produced, no further failure data, e.g. the cause or type of the failure, is available, or is modelled.

Due to the difficulty in accessing a large sample of memory failure maps the model described in this chapter uses statistical information already available within Verigy. The necessity of the use of this information limits the development of the model — the model could be improved by detailed analysis of many thousands failure maps at different points on the yield learning curve and ideally from many different devices.

This chapter has presented a novel implementation of the model described and also shown a novel technique allowing the generation of memory failure bitmaps over a range of per die yields, providing a means to test the performance of memory repair algorithms at several points on the yield learning curve.

3.4. Conclusions

Further work on this failure model should include parameter sets derived from one device at different points on the yield learning curve thus calibrating the model fully. With the collection of parameter sets for many different devices the model can more accurately represent each device and therefore many types of device.

# Chapter 4

# DRAM Redundancy Analysis

### 4.1 DRAM Repair Background

Before a detailed discussion of repair algorithms it is useful to review the need for repair in DRAM devices, the methods by which these devices may be repaired, and the algorithms used to calculate repair solutions.

The manufacture of memory devices is a low yield process due to errors in manufacturing (e.g. mask miss-alignment or contamination). To improve yield, redundant capacity is included in the memory design and a repair step is introduced after manufacture.

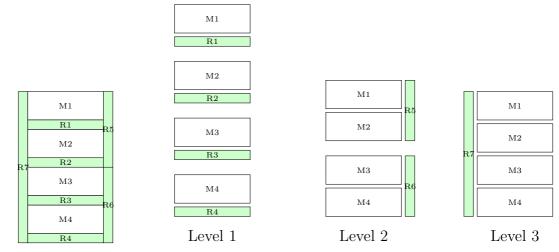

To allow this repair an amount of spare cells are included during the design of the device. In most cases this spare capacity takes the form of extra cells in the memory array, providing extra rows and columns in that memory array.

Modification to the logic used to translate memory addresses into row and column addresses allows these redundant rows and columns to be used in place of rows or columns with faulty memory cells.

Compromises made in the design of the device, often so as to improve the capacity of that device, introduce constraints upon what this remapping logic can achieve; these are further discussed in chapter 5.

Each manufactured device has a particular set of failures and therefore a particular set of row and column replacements that will best repair the device. In many cases there will be many possible sets of row and column replacements that will leave no un-repaired failures, but it is quite possible that there may be one unique solution, or no solutions at all, capable of repairing the whole device.

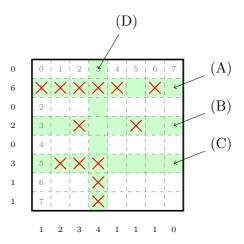

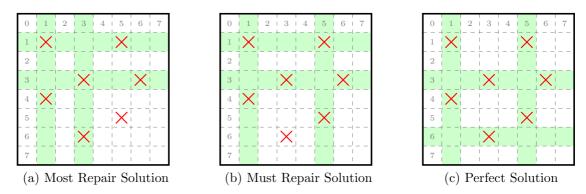

One of the simplest strategies used for repair is to calculate the number of failed cells in each row in the memory array and replace the row with the most failed cells. The process is repeated while there are spare rows remaining and while there are rows with failures to repair. The same process is applied to columns to complete the repair of the device Figure 4.1 shows the repair of a small device of eight by eight memory cells, thirteen failures, three redundant rows, and three redundant columns.

Figure 4.1: Most repair solution for a small device. The device is eight by eight cells with three redundant rows and three redundant columns. Failures (×) are repaired by these spare rows and columns (shown shaded). Per row and column failure sums are shown, and during row first most repair the rows and columns are repaired in the order labelled.

The repairs made in figure 4.1 are calculated using the most repair algorithm, first replacing the row the row with the most failures, label (A), and repeating the process until there are no redundant rows left, making the repairs labelled (B) and (C). Finally the column with the most failures is repaired, (D), and as there are no un-repaired failures remaining the algorithm terminates.

Though in this case a solution completely repairing the device was found very often that is not the case, and the most repair heuristic will exhaust the redundant capacity without repairing the device.

The order in which the most repair algorithm addresses failures in rows and columns can have an effect upon the repair solution made and therefore in the success of the algorithm. A more sophisticated algorithm might attempt to generate solutions independent of these factors; one such algorithm is the "Must Repair" algorithm.

The must repair algorithm operates by applying a simple selection criterion to choose those rows and columns to be repaired. This criterion (from Bhavsar [Bha99]) describes a row must repair as "a repair solution forced by a failure pattern with more defective cells in a single row than there are spare columns". Alternatively, and identically, it may be said that a row with more faults than can be repaired with the available spare columns must be repaired with a spare row. (Both definitions can be reversed to define must repair columns in terms of the available spare rows.)

During the first iteration of the must repair algorithm this criterion is applied to each row and column, comparing the number of failed cells with the available spare columns and rows. The result of this application to the example device of figure 4.1 is shown in figure 4.2a. These iterations continue repairing rows and columns with more failures than there are spare rows and columns until either: there are no must repairs, there are no failures, or there are no unused redundant elements. As in the example of figure 4.2b it will often be the case that the must repair algorithm terminates before all the failures are repaired, even if a complete repair is possible.

The must repair algorithm does however provide a guarantee that all of the redundant elements used cannot be used in a better arrangement: the rows and columns repaired were unrepairable by other means. Given this guarantee the must repair algorithm is often used before other, more complex, repair algorithms to reduce their running time.

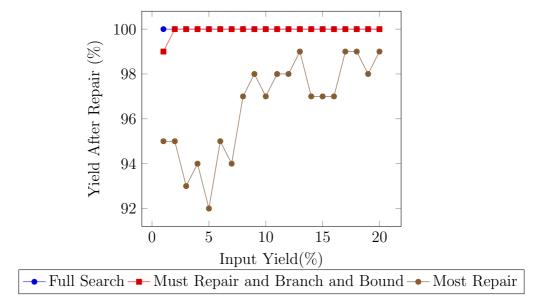

Neither the most repair nor the must repair algorithms can provide a guarantee that they will find a solution, even if one exists. Algorithms do exist that can guarantee the best possible solution will be found, if there are many solutions then the solution with fewer repairs will be chosen, if there are no complete solutions then the best

Figure 4.2: Must Repair Solution for a small device with three redundant rows and three redundant columns. During the first iteration the must repair criterion states that any row or column with more than three failed cells must be repaired, and two such repairs are made (part (a)). As one redundant row and one redundant column have now been used during the second iteration (part (b)) the criterion states that any row or column with more than two failed cells must be repaired. As there are no matching rows or columns the algorithm terminates.

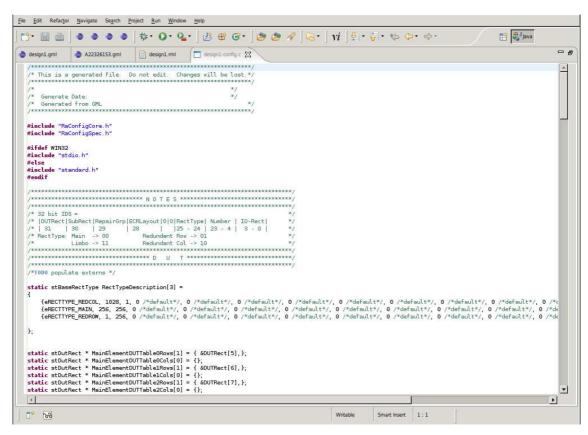

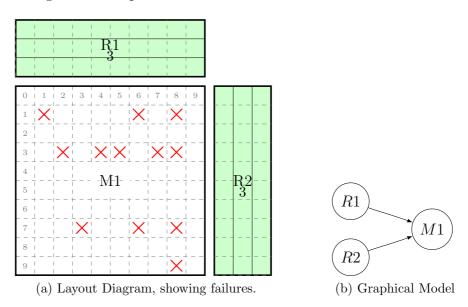

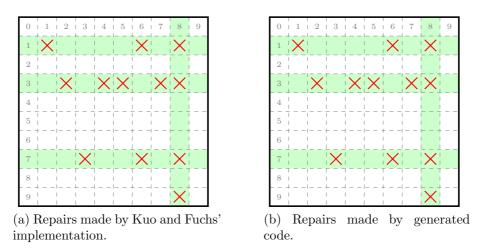

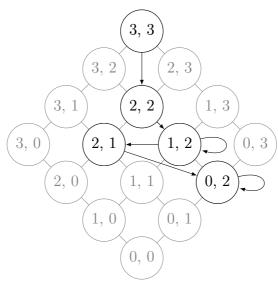

attempt will be chosen, and if there is only one complete solution it is guaranteed to to chosen. This class of algorithms are commonly called *perfect* repair algorithms.