# **Durham E-Theses**

# CDS- $CU(\underline{\hspace{0.1cm}}x)S$ single crystal and thin film solar cells

Al-Dhafiri, Abdullah M.

#### How to cite:

Al-Dhafiri, Abdullah M. (1988) CDS- $CU(\_x)S$  single crystal and thin film solar cells, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/6617/

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

# $\mathsf{CdS}\text{--}\mathsf{Cu}_{\mathbf{x}}\mathsf{S}$ SINGLE CRYSTAL AND THIN FILM SOLAR CELLS

by

# ABDULLAH M. AL-DHAFIRI

The copyright of this thesis rests with the author.

No quotation from it should be published without his prior written consent and information derived from it should be acknowledged.

Presented in candidature for the degree of

Doctor of Philosophy

in the

University of Durham

February 1988

# CONTENTS

| Acknowledgeme | nts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Abstract      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                      |

| CHAPTER 1     | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                      |

|               | <ul> <li>1.1 Introduction</li> <li>1.2 Background</li> <li>1.3 Solar Cell Materials</li> <li>1.4 Junctions Used in Solar Cells and Cell Types</li> <li>1.5 Recent Developments in Photovoltaic and Economic Views</li> </ul>                                                                                                                                                                                                                                                                                                                                                                              | 1<br>2<br>4<br>5                                                     |

|               | 1.6 Scope of the Present Work<br>References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11                                                                   |

| CHAPTER 2     | MATERIAL ASPECTS OF Cds Based Solar Cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 16                                                                   |

|               | <ul> <li>2.1 Introduction</li> <li>2.2 Preparation of CdS Single Crystals</li> <li>2.3 Preparation of CdS Thin Films <ul> <li>2.3.1 Thermal Evaporation Method</li> <li>2.3.2 Other Methods of Thin Film <ul> <li>Deposition</li> </ul> </li> <li>2.4 Properties of Cadmium Sulphide</li> <li>2.5 Deposition of Copper Sulphide</li> <li>2.6 Properties of Copper Sulphide</li> <li>2.6.1 Chemical and Structural Properties</li> <li>2.6.2 Optical Properties</li> <li>2.6.3 Electrical Properties</li> </ul> </li> <li>2.7 Cadmium Zinc Sulphide Solar Cells <ul> <li>References</li> </ul> </li> </ul> | 17<br>18<br>19<br>21<br>22<br>25<br>26<br>26<br>26<br>28<br>29<br>30 |

| CHAPTER 3     | THEORETICAL ASPECTS OF THE CdS-Cu2S SOLAR CELL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 38                                                                   |

|               | 3.1 Introduction 3.2 Photovoltaic Mechanisms in the CdS-Cu <sub>2</sub> S and Cd <sub>2</sub> Zn <sub>1-y</sub> S-Cu <sub>2</sub> S Junctions 3.3 Basic Theory of Solar Cells 3.4 Solar Cell Equivalent Circuit 3.5 Light Generated Current 3.6 Junction Capacitance 3.7 Spectral Response 3.8 Solar Cell Operational Parameters 3.8.1 Solar Cell Efficiency                                                                                                                                                                                                                                              | 38<br>38<br>43<br>49<br>53<br>55<br>56<br>58                         |

3.8.2 Solar Radiation

3.8.5 The Fill Factor

3.9 Defect and Impurity Centres

3.8.4

3.9.1

3.9.2 3.9.3

References

3.8.3 Short Circuit Current

Shallow Levels

of Defect Levels

Open Circuit Voltage

Deep Levels Photocapacitance for the Detection

59 60

61

62 63

64

64

65

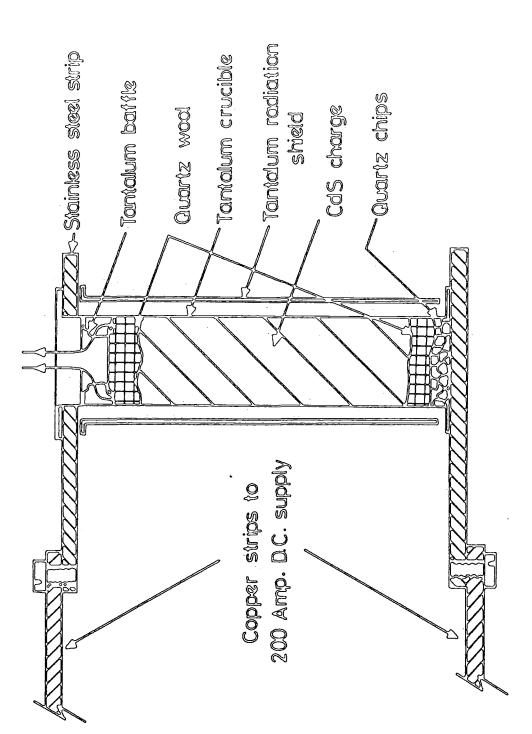

| CHAPTER   | 4 | EXPE                                   | RIMENTAL TECHNIQUE                                                                                                                                                      | 71                                     |

|-----------|---|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|           |   | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | Crystal Growth Scanning Electron Microscopy Reflection High Energy Electron Diffraction Measurement of Spectral Response Measurement of Current-Voltage Characteristics | 71<br>71<br>72<br>73<br>75<br>76<br>77 |

| CHAPTER   | 5 |                                        | Cu <sub>2</sub> S SINGLE CRYSTAL SOLAR CELLS FORMED BY ELECTROPLATING TECHNIQUE                                                                                         | 80                                     |

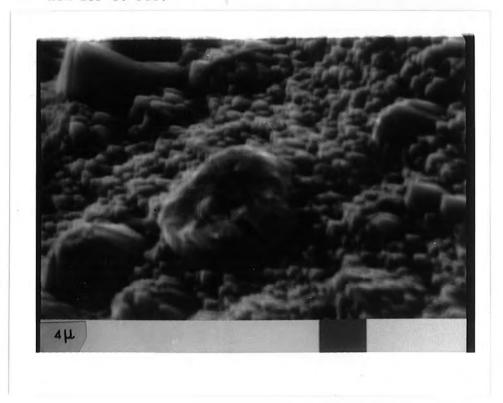

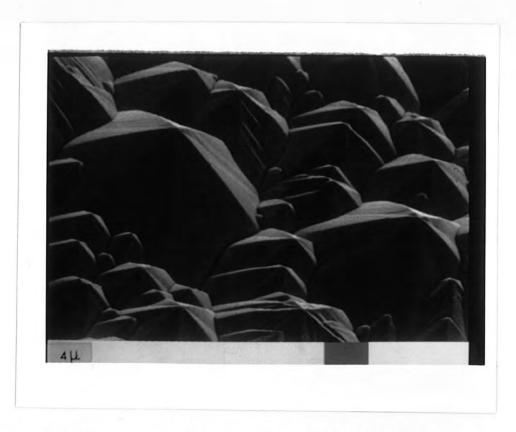

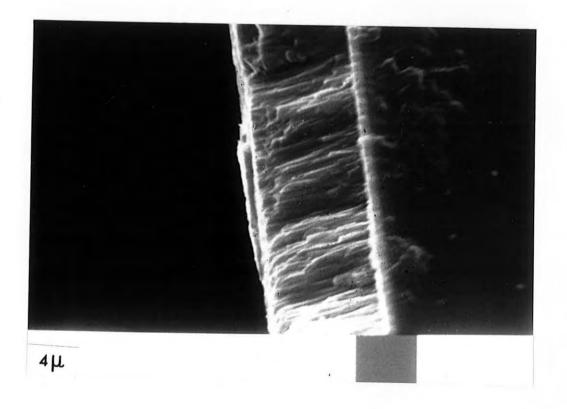

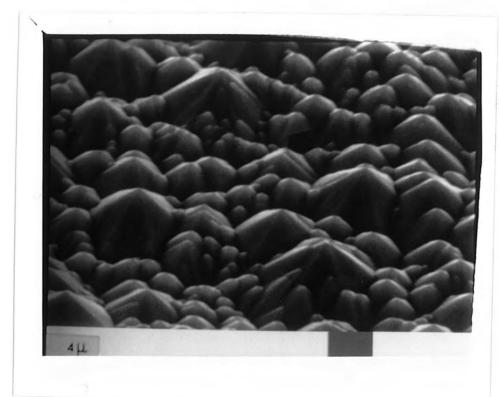

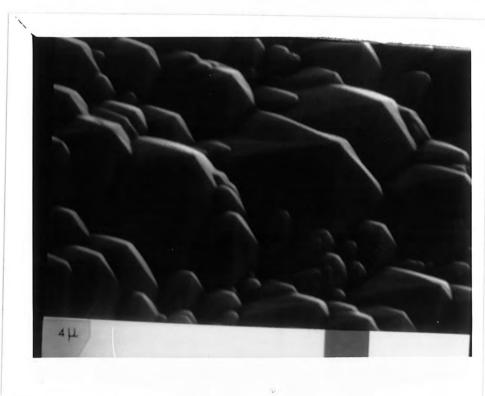

|           |   |                                        | Introduction Studies of Mechanically Polished and of Chemically Etched (0001) CdS                                                                                       | 90                                     |

|           |   | <b>.</b> .                             | surfaces                                                                                                                                                                | 80                                     |

|           |   | 5.3                                    | The Copper Sulphide Layer                                                                                                                                               | 82                                     |

|           |   |                                        | 5.3.1 Heterojunction Formation                                                                                                                                          | 82                                     |

|           |   |                                        | 5.3.2 Examination of Copper Sulphide                                                                                                                                    |                                        |

|           |   |                                        | Phases on CdS                                                                                                                                                           | 84                                     |

|           |   | 5.4                                    | Properties of As-made CdS-Cu_S Solar                                                                                                                                    |                                        |

|           |   |                                        | Cells as a Function of Electroplating Bias                                                                                                                              | 86                                     |

|           |   |                                        | 5.4.1 Current-Voltage Characteristics                                                                                                                                   | 86                                     |

|           |   |                                        | 5.4.2 Spectral Response                                                                                                                                                 | 88                                     |

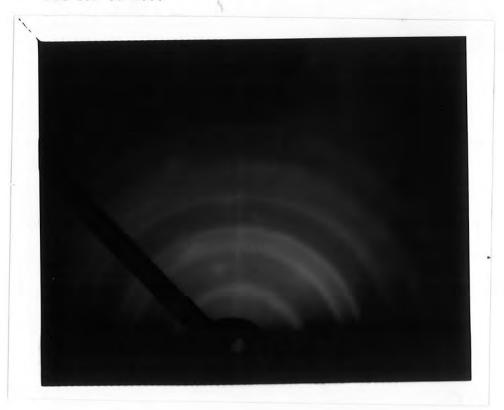

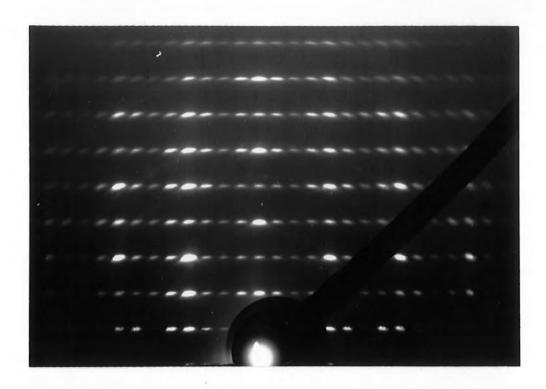

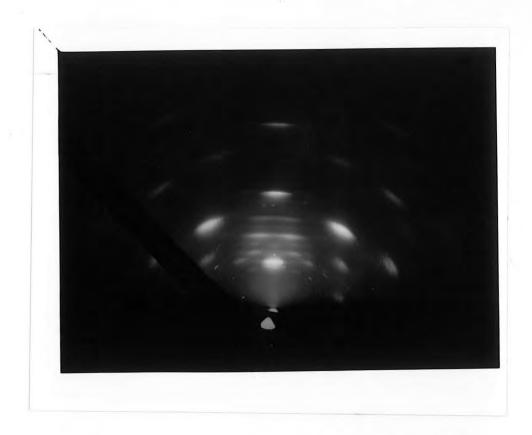

|           |   | 5.5                                    | RHEED Study After Heat Treatment In                                                                                                                                     |                                        |

|           |   | - 10                                   | Different Ambients                                                                                                                                                      | 89                                     |

|           |   | 5.6                                    | Properties of CdS-Cu_S Solar Cells After                                                                                                                                | 0)                                     |

|           |   | J.0                                    | Heat Treatment in Air or In Argon                                                                                                                                       | 89                                     |

|           |   |                                        |                                                                                                                                                                         |                                        |

|           |   |                                        | 5.6.1 Current-Voltage Characteristics                                                                                                                                   | 89                                     |

|           |   | <i>-</i> -                             | 5.6.2 Spectral Response                                                                                                                                                 | 92                                     |

|           |   |                                        | Capacitance-Voltage Measurement                                                                                                                                         | 96                                     |

|           |   | 5.8                                    | Discussion                                                                                                                                                              | 97                                     |

|           |   |                                        | 5.8.1 The Effect of Using Electroplating                                                                                                                                |                                        |

|           |   |                                        | Bias                                                                                                                                                                    | 97                                     |

|           |   |                                        | 5.8.2 The Effect of Heat Treatment                                                                                                                                      | 101                                    |

|           |   |                                        | 5.8.3 The Effect of Electroplating                                                                                                                                      |                                        |

|           |   |                                        | Method on C-V Measurements                                                                                                                                              | 105                                    |

|           |   | 5.9                                    | Conclusion<br>References                                                                                                                                                |                                        |

| CHAPTER 6 | 6 | CdS-                                   | Cu <sub>2</sub> S THIN FILM PHOTOVOLTAIC CELLS                                                                                                                          | 111                                    |

|           |   |                                        |                                                                                                                                                                         |                                        |

|           |   |                                        | Introduction                                                                                                                                                            | 111                                    |

|           |   | 6.2                                    | Film Deposition                                                                                                                                                         | 111                                    |

|           |   |                                        | 6.2.1 Substrate Preparation                                                                                                                                             | 111                                    |

|           |   |                                        | 6.2.2 Vacuum System                                                                                                                                                     | 112                                    |

|           |   |                                        | 6.2.3 Evaporation Procedure                                                                                                                                             | 113                                    |

|           |   |                                        | Film Structure                                                                                                                                                          | 113                                    |

|           |   |                                        | Heterojunction Preparation                                                                                                                                              | 114                                    |

|           |   | 6.5                                    | Properties of CdS-Cu_S Thin Films                                                                                                                                       |                                        |

|           |   |                                        | Formed by the Electroplating Technique                                                                                                                                  | 115                                    |

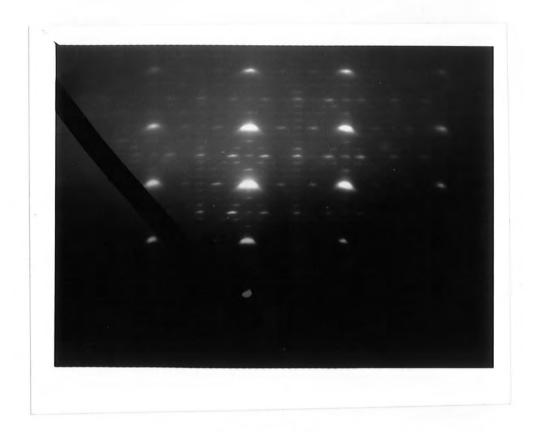

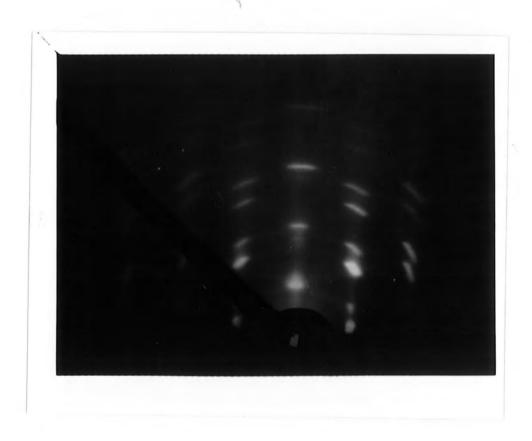

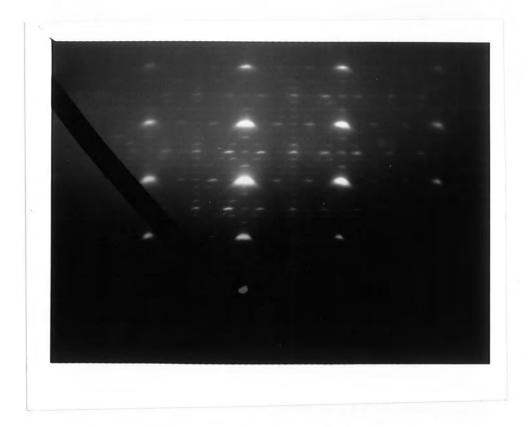

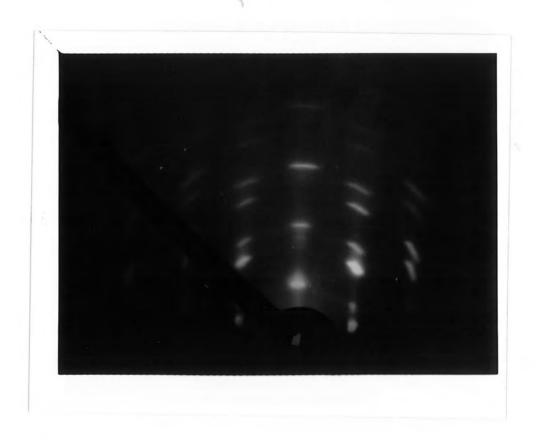

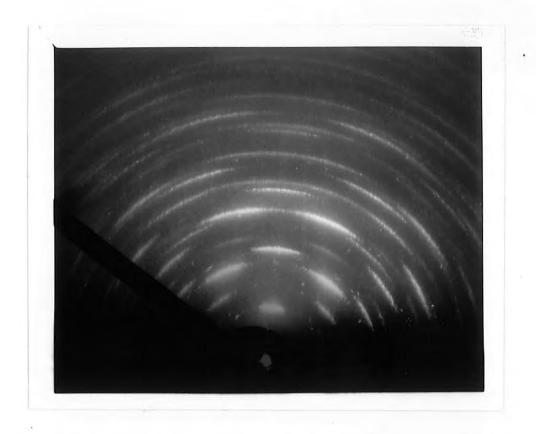

|           |   |                                        | 6.5.1 RHEED Investigation                                                                                                                                               | 115                                    |

|           |   |                                        | 6.5.2 Spectral Response                                                                                                                                                 | 117                                    |

|           |   |                                        | 0.5.2 Opectrar response                                                                                                                                                 | 11/                                    |

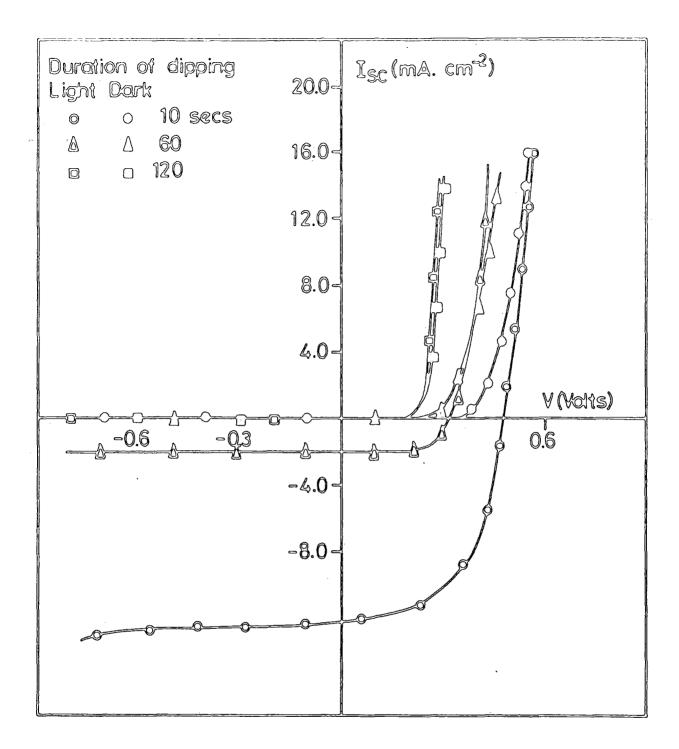

|           |                   | 6.5.3 Current-Voltage Characteristics<br>Discussion of Results<br>Conclusion<br>References                                                                                                                                                     | 119<br>123                      |

|-----------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| CHAPTER 7 | THE               | CdS-Cu <sub>2</sub> S SOLAR CELL STABILITY STUDIES                                                                                                                                                                                             | 134                             |

|           | 7.2               | Introduction The Effect of Ageing on Device Properties 7.2.1 Current-Voltage Characteristics 7.2.2 Spectral Response 7.2.3 Electron Spectroscopy for Chemical Analysis (E.S.C.A.) The Effect of an Argon Atmosphere at                         | 134<br>134<br>135               |

|           | , , ,             | Different Temperatures on the Stability of CdS-Cu <sub>2</sub> S Solar Cells                                                                                                                                                                   | 138                             |

|           |                   | 7.3.1 Cell Performance                                                                                                                                                                                                                         | 138                             |

|           |                   | 7.3.2 The Effect of Heat Treatment in H <sub>2</sub> /N <sub>2</sub> Ambient                                                                                                                                                                   | 139                             |

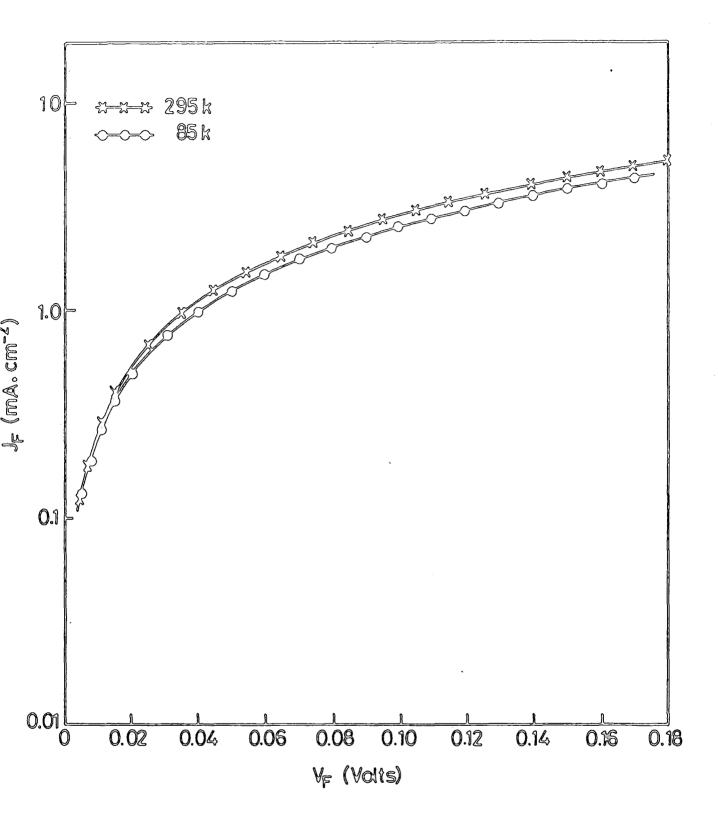

|           | 7.5<br>7.6<br>7.7 | The Effect of Etching Time on the Cross-over Between Dark and Light I-V Characteristics The Effect of Dipping Time on Cell Properties The Dependence of Dark I-V Characteristics on Electroplating Conditions Discussion Conclusion References | 140<br>141<br>143<br>146<br>152 |

| CHAPTER 8 | Cd <sub>y</sub> Z | n <sub>1-y</sub> S-Cu <sub>x</sub> S SOLAR CELLS                                                                                                                                                                                               | 157                             |

|           | 8.1<br>8.2        | Introduction $Cd_{y}Zn_{1-y}S$ Substrate Preparation                                                                                                                                                                                           | 157<br>158                      |

| •         | 8.3               | Photovoltaic Characteristics 8.3.1 Steady State Photocapacitance 8.3.2 Spectral Response and Current-                                                                                                                                          | 158<br>158                      |

|           | 8.4<br>8.5        | Voltage Characteristics Discussion Conclusion References                                                                                                                                                                                       | 160<br>162<br>166               |

| CHAPTER 9 | SUMM              | ARY AND CONCLUSIONS                                                                                                                                                                                                                            | 170                             |

803/11

- 36. Glory to God, Who created In pairs all things that of The earth produces, as well as Their own (human) kind And (other) things of which They have no knowledge.

- 37. Ind a Sign for them

Is the Night: We withdraw

Therefrom the Day, and behold

They are plunged in darkness;

- 38. And the Sun

Runs his course

For a period determined

For him: that is

The decree of (Him),

The Exalted in Might,

The All-Knowing.

- 39. And the Moon,—

We have measured for her

Mansions (to traverse)

Till she returns

Like the old (and withered)

Lower part of a date-stalk.

- 40. It is not permitted

To the Sun to eatch up

The Moon, nor can

The Night outstrip the Day:

Each (just) swims along

In (its own) orbit

(According to Law).

المرافي المرافي المرافي المرافية المرافية المرافية المرافية والمرافية المرافية المر

٥٥- وَإِنَّهُ لَكُمُ الْكِلِّ تَسْلَحُ مِنْهُ الْكَارُ وَلِمَا مُمْ مُثَنِّلُونَ ٥

> مر والقشل تجوئ الشقائة لكاث المرائغ الكرائم ف مر والفكر فكرنه مكان المعاني عاد كالمرائخ في المرائم و

؞ڔڒڰۺؙؽۼٛڹؽؙڒؠؙٲؽؙؿؙڹٟۮ ڰؙۺۯڒڰؽڶٵڣڰڰؠ ٷڴڔڹٛڟڮڰڹۺؙؽؙ٥

THE HOLY QURAN

To my parents

and

my wife

#### **ACKNOWLEDGEMENTS**

I must express my sincere gratitude to ALLAH without whose help this study would never have been possible. I would like to thank my supervisors Prof. J. Woods and Dr. G.J.Russell for their guidance, assistance and valuable discussion during the course of this research project.

I would also like to thank Prof. G.G.Roberts for allowing me to use the facilities of the department and I am grateful to workshop staff, headed by Mr. F. Spence for their technical help and advice. I wish to extend my thanks to Mr N.F. Thompson for technical assistance in the laboratory and in the crystal growth.

I am particularly indebted to Mr T. Harcourt for cutting and polishing the single crystal. I also wish to thank Dr. S. Oktik for the valuable discussion and Dr. A.W. Brinkman and other members of the group who rendered me their help during the course of this work in one way or another.

I am also grateful to Miss K. Cummins for drawing the diagrams included in this thesis and to Mrs S. Little for typing the thesis. In addition, special thanks are due to Mr T. Furlong for proof-reading. The financial support by King Saud University is gratefully acknowledged.

Finally I would like to express my gratitude to my parents for their many sacrifices, my brother, Ahmed for his constant encouragement over the years and to my wife for her understanding, support and contributions to a happy home and enjoyable family life.

#### ABSTRACT

The work presented in this thesis is concerned with photovoltaic cells formed by plating CdS single crystals and thin films, and Cd Zn  $_{\rm S}$  S single crystals, with copper sulphide. An electroplating technique has been used to control the phase of copper sulphide by changing the electric field during its formation. Different phases of Cu S have been identified directly using Reflection High Energy Diffraction (RHEED), and indirectly from spectral response measurements. A dramatic change in the spectral response accompanying the reduction in the covellite response associated with an increase in that from chalcocite following argon heat treatment has been achieved. The change from the djurleite phase to that of chalcocite has also been obtained by using argon heat treatment for 5 minutes at 200  $^{\circ}$ C. This effect was found to be reversible in that layers of chalcocite were converted to djurleite when air was used as the ambient for the heat treatment. C-V measurements have demonstrated that with increasing plating bias the donor concentration decreases at first before it assumes a constant value. This led to the effect of decreasing the junction capacitance as the width of the depletion region changed.

The problem of the stability of the CdS-Cu  $_2$ S photovoltaic devices formed by "wet plating" is addressed by studying the combined effects of the substrate onto which the CdS is deposited and the ambient used during annealing. Thin film cells have been prepared on both Ag/Cr and SnO $_x$  substrates, and the device characteristics for each have been investigated as a function of annealing ambient. The results have shown that devices formed on Ag/Cr substrates were more stable following annealing in air than in argon, while the converse was true for cells fabricated on SnO $_x$  substrates.

The degradation effects of  $\mathrm{CdS-Cu_2}\,\mathrm{S}$  photovoltaic cells have been investigated. While devices stored in the dark showed little or no degradation, those maintained under illumination exhibited a significant deterioration in all operational parameters over a four week period. As far as the combined effect of temperature and ambient on the stability of cells are concerned, it was found that the ageing of devices in argon at room temperature in the dark was negligible, and moreover the fill factor was observed to improve marginally. When the devices were stored in the same ambient conditions at  $50^{\circ}\mathrm{C}$ , they showed a significant improvement in the fill factor, but simultaneously exhibited a considerable reduction in the short circuit current. This process was reversible, since the sensitivity of degraded devices could be restored by annealing them in a hydrogen/nitrogen mixture. By comparing Electron Spectroscopy for Chemical Analysis (ESCA) studies with solar cell device characteristics, it has been shown that the formation of copper oxide on the Cu S surface plays a significant role in the degradation of CdS-Cu S devices.

The extent of the cross-over between the dark and light J-V characteristics is a function of the period of etching used prior to junction formation. The variation of current and diode factor has been established as a function of the bias value. The dependence of forward current on the temperature at fixed forward voltage has also been investigated.

Finally this work has shown that an increase in V can be achieved when Cd Zn S is used as a base material for solar cells instead of CdS. Different traps were identified through a photocapacitance investigation. An important trap was found at 0.78eV below the conduction band. It has been demonstrated that the effect of this level was found to be diminished much more slowly when the annealing was carried out in argon rather than in air. This level may play an important role in the Cd  $_{\rm 0.8}{\rm Zn}_{\rm 0.2}{\rm S-Cu}_{\rm 2}{\rm S}$  solar cell properties.

#### CHAPTER ONE

#### Introduction

#### 1.1 Introduction

It is estimated that less than 20% of the population of the developing countries are supplied with electricity. In Africa, for example, more than 400 million people out of a total population of 470 million are not connected to an electricity distribution grid. Also in the developing countries, 75% of the population are in danger of becoming marginalized in the long term [1]. In addition, since the world has been using an exhaustible energy supply, it is necessary to investigate renewable energy sources. In this connection, solar energy is regarded as one of the most promising alternative sources especially for the electrification of rural areas in Third World countries. Solar cells are particularly attractive in this respect as the incident solar energy is converted directly into electricity without movement of any mechanical parts or associated problems of pollution.

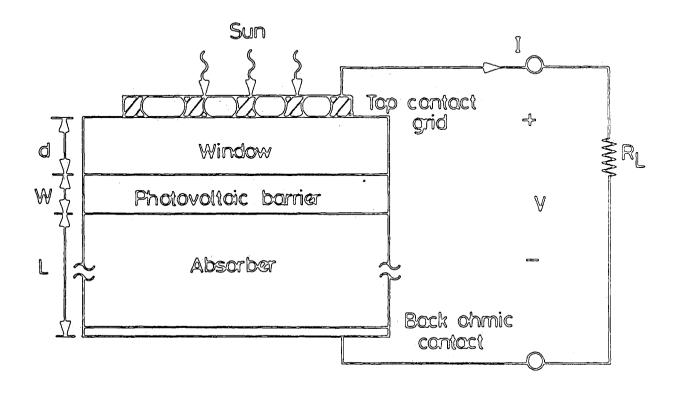

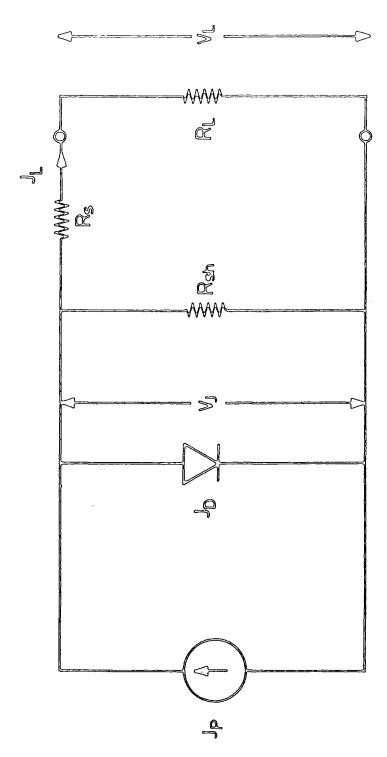

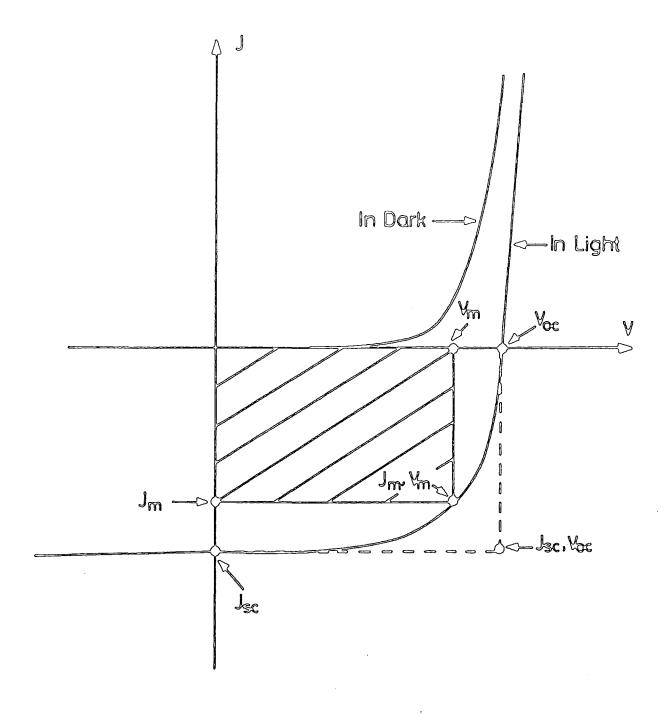

In a photovoltaic device, light photons are absorbed by the semi-conductor which forms the absorber limb and thereby creates equal numbers of electric charge carriers called electrons and holes. These diffuse to a junction which is formed between either a p- and an n-type semiconductor or between a metal and a semiconductor (Schottky barrier). In both types of device a strong internal electric field exists. Electrons and holes are separated by this field which leads to the development of a voltage and the flow of a current, so allowing power to be delivered to an external load such as a light bulb or a motor. A schematic diagram of a solar cell structure is shown in Figure 1.1. To appreciate the quantity of solar energy available, it is

Fig 1.1 : Schematic diagram of a general solar cell structure (Ref 3)

found that on a bright summers day at noon the solar energy falling on the earth's surface is about 1000 watts per square metre. If this amount of solar energy falling on a single square metre could be converted completely into electricity, then this could power ten 100 watt bulbs, or two furnace motors, or several 25 inch television sets [2].

Photovoltaic systems have many advantages; in addition to being very reliable, they are clean power sources utilising renewable energy. Operating and maintenance costs are expected to be low because of the simplicity of photovoltaic system designs. Photovoltaic energy conversion is used today for both space and terrestrial solar energy conversion. The success in space applications is well known (communication satellites, manned space laboratories) and the use of solar cells in terrestrial applications becomes clearer with their use in radios, calculators, watches, water pumping, the lighting industry ... etc [4,6]. Table 1.1 lists examples of present terrestrial applications of photovoltaic systems and devices.

#### 1.2 Background

This effect has been known for about 150 years. It was reported initially in 1839 by Becquerel [7] who observed a light-dependent voltage between two metal electrodes placed in an electrolyte solution.

Willoughby-Smith [8] discovered photoconductivity in selenium in 1873 and Adams and Day [9] observed it in solid selenium three years later.

Many of the subsequent solid state workers including Hallwachs [10], Lange [11], Grondahl [12], and Schottky [13] prepared photovoltaic cells on selemium and cuprous oxide. However, the photovoltaic effect is essentially different from the Dember [14] effect which is the production of a potential difference across a photoconductor by non-uniform

Solar cells depend upon the photovoltaic effect for their operation.

| APPLICATION                                     | COMMENTS                                                                                                                                                                    |  |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| I Large                                         | land installations                                                                                                                                                          |  |

| Building power systems                          | Provide power to single-family homes, apartment, public, or commercial buildings. Often installed on rooftops. [1 to 100s of kW].                                           |  |

| Central power station                           | Feeds ac power to utility grid for transmission and distribution. [MW to multi-MW].                                                                                         |  |

| Forest Service lookout                          | Supplies lights, communications, refrigeration; energy storage desirable.                                                                                                   |  |

| Military installations                          | For remote site; solar and wind power complementarity useful to provide more continuous supply. Grid connection, ac or dc output possibly useful. Storage likely necessary. |  |

| Village power system                            | Water pumping, refrigeration, lighting, communications. [0.1 to 100s of kW].                                                                                                |  |

| Water pumping systems                           | Mobile systems with no storage, to multi-kW fixed systems that may be grid-connected or independent, operate on ac or dc. [power to multi-kW]                               |  |

| Water purification                              | [multi-kW].                                                                                                                                                                 |  |

| II Commu                                        | nications equipment                                                                                                                                                         |  |

| Emergency or remote telephone                   | Energy storage desirable or necessary.                                                                                                                                      |  |

| Emergency or portable radio                     | Storage desirable or necessary. [power to 50 W useful].                                                                                                                     |  |

| Microwave telephone repeater station            | Storage necessary; dc output usable.                                                                                                                                        |  |

| Military radar installation                     | Storage necessary. [multi-kW].                                                                                                                                              |  |

| Radio broadcast station                         | Storage or grid connection as back-up necessary;<br>dc output usable. DOE demonstration project as<br>described in text. [multi-kW].                                        |  |

| Railroad telephone system                       | For communications between caboose and engineer on train.                                                                                                                   |  |

| Television receiver in village                  | [50 W usable].                                                                                                                                                              |  |

| III Remotely si                                 | ted equipment of all kinds                                                                                                                                                  |  |

| Alarms                                          | Intrusion, smoke, and fire alarms. Energy storage necessary. [watts].                                                                                                       |  |

| Cathodic protection system                      | To prevent corrosion of pipelines, bridges, and structures. Energy storage desirable; usually no grid connection.                                                           |  |

| Desalinization system                           | Electricity used for pumping: may be tolerant to fluctuating supply of energy.                                                                                              |  |

| Electric cattle fence                           | Dc output usable; energy storage necessary; usually no grid connection.                                                                                                     |  |

| Highway dust storm and other warning signs      | Energy storage necessary. [watts]                                                                                                                                           |  |

| Naviagation aids for boats, ships, aircraft     | Energy storage necessary. [10s of watts].                                                                                                                                   |  |

| Offshore or remotely sited landbased equipment. | Lighting, refrigeration, communications equipment; storage desirable.                                                                                                       |  |

| Scientific instrumentation for field use        | Remote recording or telemetry; storage desirable.                                                                                                                           |  |

| IV                                              | Miscellaneous                                                                                                                                                               |  |

| Airplane                                        | Ultra-light "Gossamer Penguin" in 1980 flew powered directly by solar cells without battery storage.                                                                        |  |

| Electronic calculator                           | Powered by room lights. Energy storage not necessary Low efficiency cells may be used.                                                                                      |  |

| Electronic watch                                | Solar cells used to recharge battery.                                                                                                                                       |  |

TABLE 1.1 : Examples of terrestrial application of solar cells, typical power levels for some application are given in braces (Ref 5).

illumination. In this effect electrons having the higher mobility diffuse away from the surface more quickly than holes. So the differential diffusion will tend to make the surface more positive than the bulk, in the absence of any other effect. The direction of the resulting electric field is such as to accelerate the lower mobility carriers and to slow down more mobile ones resulting in no net current.

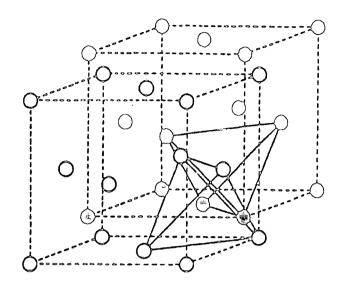

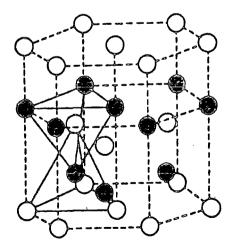

There after a variety of materials and devices were investigated, but it was not until 1954 that work directed towards the fabrication of devices utilizing the photovoltaic effect was reported in the liter-In that year Reynolds et al [15] obtained about 6% conversion efficiency with a Cu<sub>2</sub>S-CdS p-n heterojunction. In the same year Chapin et al [16] reported a high efficiency solar cell (6%) using a diffused silicon p-n homojunction. A couple of years later Jenny et al [17] obtained a 4% solar conversion efficiency from a GaAs based solar cell. With these pioneer studies, the foundation was laid for the further development of a photovoltaic device technology. The first assessments of device requirement [18,19] suggested that the optimum band gap energy for a p-n junction solar cell should be ∿1.5eV. It was Wolf [20] who first suggested the use of a heterojunction cell with a wide bandgap surface layer as one of the ways of improving the conversion efficiency. Many materials were investigated for use in thin film solar cells and these included amorphous silicon, II-VI (CdS), III-V (InP), ternary (Cd<sub>v</sub>Zn<sub>1-v</sub>S)and II-III-VI<sub>2</sub> compounds (CdInSe<sub>2</sub>) [21].

Following the work of Reynolds [15] in 1954, CdS solar cells were made by low cost techniques and became highly promising for commercial production. Williams and Bube [22] (1960) compared electroplated junctions of several metals on CdS. Then Shirland et al [23] (1965) and Shiozawa et al [24] improved the technology of CdS-Cu<sub>2</sub>S heterojunctions which were developed into thin film devices with efficiencies in excess

of 9.1% [25] in terrestrial sunlight.

More recently, problems with the stability of  $CdS-Cu_2S$  cells have led to the development of cells based on other materials. These, together with their efficiencies include single crystal GaAs [26] (26%), Silicon [27] (22%), CdTe [20] (12.8%) and  $Cd_vZn_{1-v}S$  [29] (10.2%).

#### 1.3 Solar Cell Materials

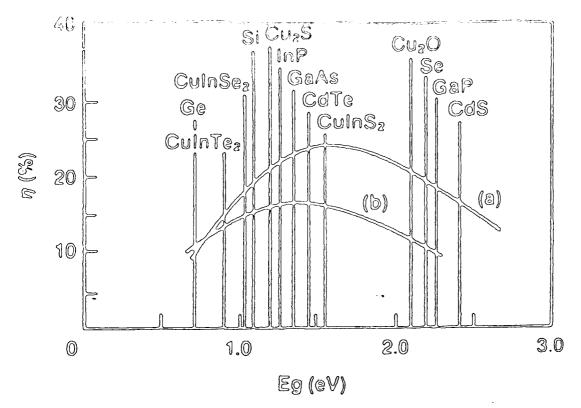

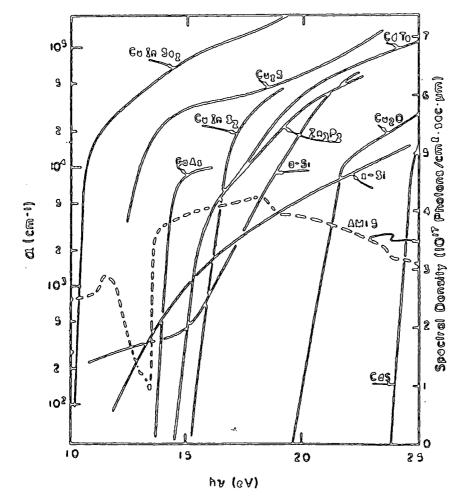

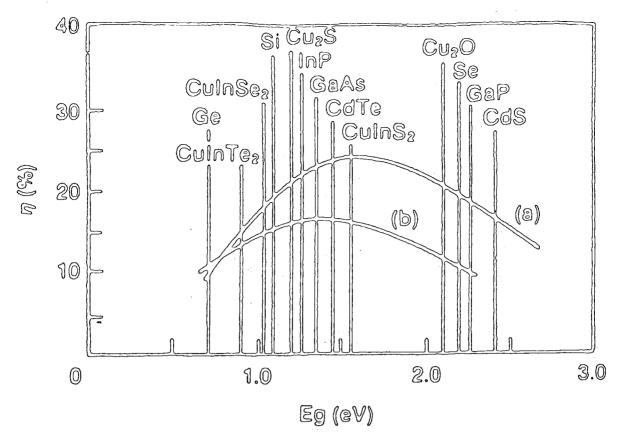

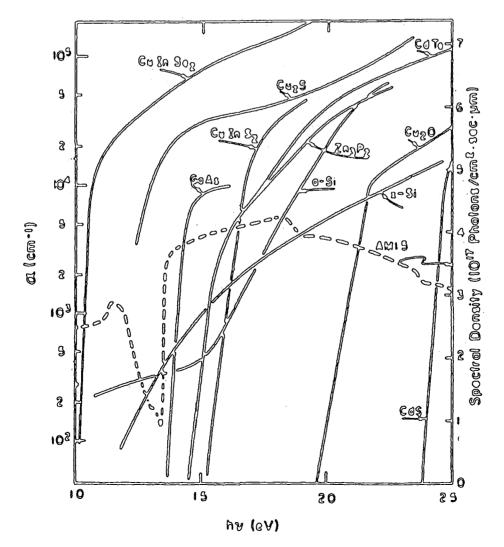

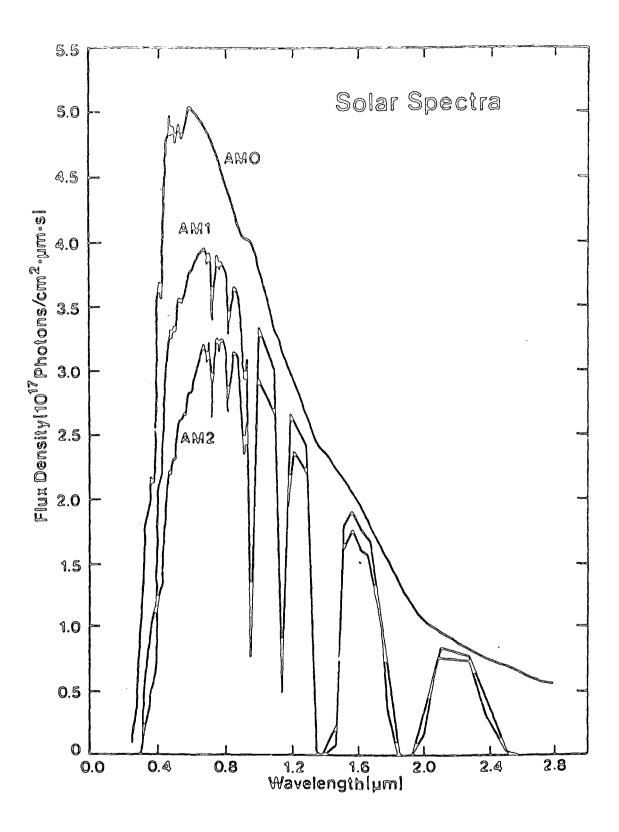

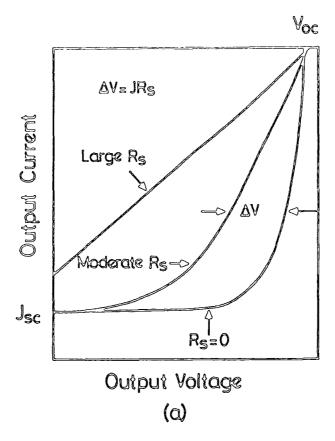

As stated above, a wide range of materials is employed in solar cell configurations. The two most important elements of a solar cell are the 'absorber', in which light-induced transitions produce mobile charge carriers, and the 'window' material which forms the other limb of the junction. The choice of these two elements is influenced by their energy gaps, their absorption coefficients at wavelengths corresponding to the solar spectrum and the diffusion lengths of minority carriers in the two materials. For the absorber, small band gap materials produce more photocurrent while, in order to obtain a large value of open circuit voltage, a window material with a large band gap is required. The dependence of the maximum conversion efficiency on the band gap for different absorber materials is shown in Figure The physical location where photon absorption takes place in the solar cell is governed by the absorption coefficient  $(\alpha)$  of the absorber material, so this part of the solar cell should have a high value of absorption coefficient to ensure the optimum conversion of the incident photon flux to electrical energy. The magnitude of  $\alpha$  depends on the physical structure of the material, on the densities of states in the conduction and valence bands, on the direct or indirect nature of the band gap transitions and on the photon wavelength. Consequently, to achieve 90% of the maximum possible output from a solar cell, the energy gap of the absorber should be between 1.0 and 1.7eV

Fig 1.2: Dependence of maximum conversion efficiency on semiconductor band gap a) for A = 1 for injection dominated current regime and b) for A = 2 for the regime dominated by the recombination in the depletion layer (Ref 19)

Fig 1.3: Optical absorption coefficient vs. photon energy for various semiconductors (Ref 30)

Fig 1.2: Dependence of maximum conversion efficiency on semiconductor band gap a) for A=1 for injection dominated current regime and b) for A=2 for the regime dominated by the recombination in the depletion layer (Ref 19)

Fig 1.3: Optical absorption coefficient vs. photon energy for various semiconductors (Ref 30)

and the carrier diffusion length should be at least twice the thickness required to absorb 90% of the incident photon energy [30]. 1.3 shows the optical absorption coefficients plotted against photon energy for various semiconductors. The diffusion length can be defined as the mean distance a charge carrier (free electron or hole) moves before recombining with another hole or electron. These distances are short, typically ranging from several to a few hundred  $\mu m$ . Cell efficiency improves with increasing carrier diffusion length. The most important part of a solar cell is the junction between the window and absorber materials where the generated minority carriers are collected and converted into majority carriers. The presence of a potential barrier at this junction inhibits the back flow of carriers. One major factor which influences the efficiency of the device is recombination of carriers ie not all the electron-hole pairs created actually reach the junction field, because some of the carriers recombine with others of opposite sign, thereby eliminating both. This usually happens at a defect or impurity called a recombination centre. The recombination lifetime therefore depends on the density of defects and on their capture cross sections for carriers.

For heterojunction solar cells, a good electron affinity and lattice match between the two semiconductors, and a high carrier mobility in the region of the junction are preferable. These parameters play an important role in determining the device performance and efficiency. Any mismatch between the lattices of the two semiconductors leads to a high density of interface states which causes the generated carriers to recombine at the interface before they can be collected.

#### 1.4 Junctions Used In Solar Cells And Cell Types

All solar cells require a junction which is capable of separating

the electrons and holes that are produced by light incident on the absorber. The types of interface structure that are used can be designated as

- i) p-n homojunctions

- ii) p-n heterojunctions; and

- iii) metal semiconductor junctions.

A p-n homojunction essentially consists of one semiconducting material which is fabricated such that it has two regions of different conductivity type, i.e.n and p. The junction is formed at the position where the conductivity changes from one type to another. In a homojunction, the light is incident through a contact grid on a thin layer of one conductivity type (usually n- type). The obvious advantage of using a homojunction is that it is free from the problems of lattice and electron affinity matching. However, such junctions are limited to just a few materials which are amphoteric, i.e. which can be made both n and p type. The most widely studied homojunctions for photovoltaic applications include single crystal silicon, amorphous and polycrystalline silicon, gallium arsenide and cadmium telluride.

A heterojunction is a junction formed between two semiconductors having different band gaps and where usually one is p- type and the other is n- type. Heterojunction p-n solar cells can be formed from two absorbers so that electron-hole pairs are created in both semiconductors or, more commonly they can be of the form of window and absorber where electron-hole pairs are created in just one of the semiconductors. The light is incident on the heterojunction in two possible configurations, either through a grid on the larger band gap material, in which case the device is designated as a backwall cell, or alternatively through a grid on a thin layer of the smaller band gap material, thereby forming a frontwall cell. Heterojunction devices provide

a wide scope for materials, and a great deal of design flexibility. If the top material has a wide band gap it serves as a window to let the light penetrate to the absorber layer beneath. With a judicious choice of materials, a device can be formed with a large built-in potential, and hence a higher open circuit voltage than with a homojunction made from the narrow band gap semiconductor. To form a good quality heterojunction, the following requirement should be satisfied. These are:

- i) the lattice constants of the two materials should be nearly equal

- ii) the electron affinities should be compatible; and

- iii) the thermal expansion coefficient of the two semiconductors should be similar.

The mismatch of lattice constants and a difference in thermal expansion coefficients can lead to interfacial strain at the heterojunction interface, giving rise to interface states which act as trapping centres. A difference in the electron affinity of the two semiconductors can cause an energy discontinuity in the form of a spike in one or both of the energy bands in an abrupt heterojunction [31].

Fonash and Rothwarf [32] listed the advantageous features of heterojunction cells to show how they are so useful and why they are particularly promising for economic reasons. The more important of these advantages are:

- i) heterojunction structures allow the use of semiconductors that can only be effectively doped either n-or p-type, but yet have attractive properties of cost considerations;

- ii) heterojunction structures enable devices to be fabricated using wide band gap materials that can serve as barrier-formers as well as reducing recombination losses at surfaces, interfaces and ohmic contacts;

- iii) heterojunction structures have effective force fields [33] in addition to the electrostatic field and these may be used to assist in the collection of photocarriers, and

- iv) the presence of these effective force fields can give rise to additional photovoltage [33].

In fact, the most promising combination of semiconductors for heterojunctions from the view point of the lattice match, electron affinity and predicted efficiency are  $\text{Ga}_{1-x}\text{Al}_x\text{As}$  - GaAs, ZnSe - GaAs, GaP-Si and ZnS-Si [34]. The thin film  $\text{CdS-Cu}_2\text{S}$  solar cell has also been considered to be very promising [35] and is expected to be  $^{15}$ % efficient under optimised conditions of fabrication. The lattice mismatch and the difference in electron affinity can both be minimized by alloying the CdS with ZnS. The efficiencies and other operational parameters for a range of different cells are shown in Table 1.2.

Finally, in metal-semiconductor or Schottky barrier, a potential drop occurs in the interfacial region between the metal and semiconductor as a result of the difference in work functions. The barrier height is the energy difference between the work function of the metal and the top of the valence band (for a p-type semiconductor) or the bottom of the conduction band (for n-type). In the Schottky barrier it is possible to have the light incident either through the semitransparent metal forming the barrier (frontwall) or through the semiconductor (backwall). The problem is that the resultant efficiency is usually limited to low values.

There are a number of other semiconductor junctions that have been considered for the use in solar cells. Two promising devices are the metal-insulator-semiconductor (MIS) and semiconductor-insulator-semiconductor (SIS) junctions where a thin insulating layer is formed between a semiconductor and a metal or between two semiconductors.

| Material                   | v<br>V       | J <sub>SC</sub><br>mÅ/cm² | FF    | η<br>% | Area,<br>cm² | Remarks                          |

|----------------------------|--------------|---------------------------|-------|--------|--------------|----------------------------------|

| Silicon                    | 0.622        | 34.3                      | 0.796 | 16.8   | 2            | p <sup>+</sup> -n-n <sup>+</sup> |

| Silicon                    | 0.621        | 36.5                      | 0.806 | 18.3   | 2.8          | MIS, active area                 |

| Silicon                    | 0.540        | 32.7                      | 0.76  | 13.3   | 2.8          | semicrystalline, MIS             |

| Silicon                    | 0.572        | 24.2                      | 0.76  | 10.5   | 5            | silicon-on-ceramic               |

| Silicon                    | 0.522        | 28.1                      | 0.79  | 11.5   | 11.4         | ITO/semicrystalline              |

| Amorphous-Si               | 0.84         | 17.8                      | 0.676 | 10.1   | 1.1          | a-SiC/a-Sip-i-n                  |

| Amorphous-Si               | 0.880        | 13.1                      | 0.57  | 6.6    | 0.73         | MIS                              |

| Amorphous-Si               | 0.878        | 11.1                      | 0.66  | 6.4    | 1.2          | p-i-n                            |

| GaAs                       | 0.93         | 28                        | 0.81  | 18.2   | 1.5          | AlGaAs/GaAs                      |

| GaAs                       | 1.05         | 270                       | 0.85  | 23     | 1.5          | AlGaAs/GaAs,10X                  |

| GaAs                       | ,—           | _                         | _     | 21     | _            | AlGaAs/GaAs, 1000X               |

| GaAs                       | 0.95         | 23                        | 0.78  | 17     | 0.5          | CLEFT                            |

| GaAs                       | 0.76         | 24.4                      | 0.63  | 12     | 0.1          | on Ge-coated Si                  |

| A1GaAs/GaAs                | 2.05         | 10.8                      | 0.74  | 16.5   | 4.0          | tandem cell                      |

| GaAs                       | 0.56         | 22.7                      | 0.67  | 8.5    | 9            | CVD thin film, MIS               |

| Cu <sub>2</sub> S/CdS      | 0.52         | 24.8                      | 0.71  | 9.2    | 1            | solution ion-exchange            |

| Cu <sup>2</sup> S/ZnCdS    | 0.6          | 22.8                      | 0.75  | 10.2   | 1            | 16% Cd, 84% Zn                   |

| CuÍnSe,/CdS                | 0.4          | 38                        | 0.63  | 9.4    | 1            | evaporation                      |

| CuInSe <sup>2</sup> /CdZnS | 0.431        | 39                        | 0.631 | 10.6   | _            | 20% Cd, 80% Zn                   |

| CdS/CdTe                   | <del>-</del> | _                         | _     | 10.5   | _            | thin film                        |

| CdS/CdTe                   | 0.79         | _                         | _     | 8      | _            | electrodeposition                |

| CdS/InP                    | 0.63         | 15                        | 0.71  | 12.5   | 0.23         | single crystal InP               |

| ÍnΡ                        | 0.66         | 24.8                      | 0.64  | 11.5   |              | PEC                              |

| WSe <sub>2</sub>           | 0.72         | 22.6                      | 0.57  | 10.2   |              | PEC                              |

| MoSé,                      | 0.65         | 25                        | 0.56  | 9.4    | _            | PEC                              |

| CdTe                       | 0.723        | 18.7                      | 0.64  | 8.6    | 0.02         | electrodeposition, Au/CdTe       |

| CdSe                       | 0.57         | 23.8                      | 0.48  | 6.5    | 1            | electrodeposition                |

| CdSe/ZnSe/Au               | 0.6          | 20                        | 0.45  | 5.0    | 0.01         | •                                |

| CuTe/CdTe                  | 0.59         | 13                        | 0.63  | 4.8    | 6            |                                  |

| $Zn_{2}P_{2}$              | 0.48         | 18                        | 0.55  | 4.3    | 1            | $Mg/Zn_3P_2$ thin film           |

| CuIn\$/CuInS <sub>2</sub>  | 0.41         | 19                        | 0.43  | 3.3    | 0.12         | 5 2                              |

| Merocyanine/Al             | 1.2          | 1.8                       | 0.25  | 0.7    | 1            |                                  |

TABLE 1.2 : Operational parameters for a range of different solar cells (Ref 5).

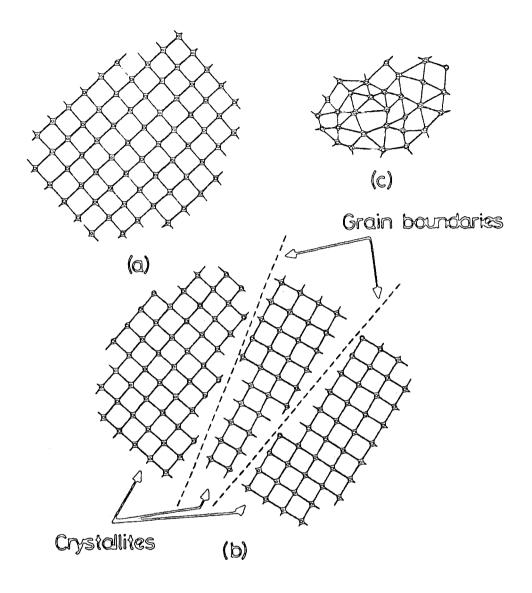

An efficiency of 7% using an MIS device has been achieved with CdSe [36]. When describing types of cell it is usual to consider each material and its degree of crystallinity as illustrated in Figure 1.4. Thus there are

- i) single crystal cells which are free from grain boundaries where the structure approximates to an ideal lattice. However, such cells are expensive to produce, though their superior efficiencies warrant their use in space applications.

- ii) cells fabricated from polycrystalline material containing individual grains with diameters ranging from a fraction of a micron to millimetres. The grain size of such materials depends not only on the material itself but also on the processing technique used to fabricate it into a solar cell;

- iii) cells formed from amorphous material in which there is only shortrange order, that extends over a few atomic distances. These are

promising because of their low cost. In particular, amorphous

silicon cells already form a major part of the photovoltaic industrial activity and they are likely to continue to be important

for some years to come.

# 1.5 Recent Developments In Photovoltaics And Economic Views

Photovoltaic technology has developed extensively over the past fifteen years or so. Solar cells have been used for several years in terrestrial applications where they are economically competitive with alternative electrical energy sources particularly in remote locations. It is expected that the market for solar cells will expand rapidly as the cost of the power from conventional and non-renewable sources rises, while that of solar cells should fall in real terms because of technological improvements and the economies of large scale

Fig 1.4 : Portions of (a) single crystal (b) polycrystalline (c) amorphous solids (Ref 5)

manufacture. The largest photovoltaic generator plant (1MWDC) has been installed by Arco Solar Inc. in Hesperia in Southern California [37]. More recently (1986) Overstraeten and Mertens [38], have compiled a list of pilot projects co-funded by the CEC and built under their auspices. The location, application, total rated power and its conditioning system are summarised in Table 1.3.

The price of photovoltaic energy continues to decline. For example in 1956 silicon single crystal homojunction cells cost 350\$ per peak watt. By 1966 the cost had dropped to 100\$ per peak watt through improved processing and technology [39] and by 1977 it was below 15\$ per peak watt for arrays. The production of polycrystalline silicon cells in the USA increased by one third from 1984 to 1985 (from 1.8 to 2.4 MW), while production of single crystal photovoltaic cells dropped by 19% (from 6.6 to 3.35 MW). On the other hand, work on amorphous silicon photovoltaics is expanding at a fast rate [40]. In the USA the production of amorphous Si increased six-fold from 1984 to 1985(from 0.1 to 0.6 MS) [40]. Present investigations suggest that the cost of photovoltaic plants in the Megawatt range would be of the order of 10.0 ECU per kW, with a conversion efficiency well about 10% [41]. It is generally agreed that photovoltaic systems in favourable locations would be economically competitive with other generating technologies, if the capital cost of the photovoltaic plant were in the \$2.0-4.0/W range [42]. By the year 2000, the USA photovoltaic program aims to reduce the price of photovoltaic energy to 0.1 to 0.3\$ per peak watt at  $10^{10}$  per watts per year [43]. Over the expected lifetime of an installation, this level should provide electricity at a cost equivalent to 0.04 to 0.06\$ per kWhr for projections 20 years hence [43]. Hay et al [44] compared the energy consumption in the fabrication of four types of cell, namely these based on single crystal silicon, ribbon

TABLE 1.3: List of pilot projects co-funded by the CEC and built under their auspics (Ref 38)

| Site                        | Total<br>rated<br>power (KWp) | Application                                                                                                                                                                                                                                                                                                       | Power conditioning system                                                                                                                                                      |  |

|-----------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pellworm Island,<br>Germany | 300                           | The plant covers the electrical needs of the Pellworm recreation centre. The power surplus is fed into the grid. The appliances include heat pumps and water pumps for the swimming pool, TV sets, radios, stores, lighting, etc.                                                                                 |                                                                                                                                                                                |  |

| Kythnos Island,<br>Greece   | 100                           | Supplies energy to the 15 kV network, in parallel with diesel power station and wind generators It saves costly diesel fuel. It also tests the combination of wind generators and photovoltaic convertors.                                                                                                        | Four DC/DC convertors each 25 KW with integrated MPPT to charge the batteries, three self-commutated invertors, each 50 kVA to feed into the grid.                             |  |

| Chevetogne,<br>Belgium      | 63                            | The plant is installed on a 500 ha Provincial Domain with camping grounds and sports centre.  An outdoor swimming pool is heated by solar thermal collectors. The photovoltaic system provides energ for the pumps of the solar thermal plant (40 kW) and for lighting (23 kW) at night.                          | energy is fed into the grid.                                                                                                                                                   |  |

| Aghia Roumeli,<br>Greece    | 50                            | The plant meets the electrical needs of a small Cretan village located 15 km from the nearest grid. The electricity is used for the electrification of homes shops and hotels (lighting, water pumps, cold stores, refrigerators and other appliances).                                                           | One self-commutated invertor 40 kVA to feed the grid in a stand-alone mode.                                                                                                    |  |

| Mont Bouquet,<br>France     | 50                            | The aim is to partially power an emitter station of Telediffusion de France with three radio and three TV emitters. In the future, similar stations with lower consumption equipment could be powered by photovoltaic energy only.                                                                                |                                                                                                                                                                                |  |

| Nice Airport<br>France      | 50                            | The energy is used to power the electronic equipment of the control tower and ground signalling. These applications require an electricity supply free of distortion and microcuts.                                                                                                                               | One self-commutated invertor 5 kVA, monophase 220 V output. One battery charge 7 kVA, working in parallel with the photovoltaic array during sunless periods.                  |  |

| Fota Island                 | 50                            | Electricity is supplied to a dairy farm with, as a load, milking machine motors, cooling motors and washing machines. The power needs of the dairy industry correspond to the seasona variation of the available sunlight.                                                                                        | Three self-commutated invertors, 10 kVA each, to feed the loads. One line-commutated invertor 50 kVA to deliver surplus energy to the grid.                                    |  |

| Terschelling,<br>Holland    | 50                            | The photovoltaic plant is used in combination with a wind generator of 40 kW. The system supplies 95% of the power needed by a school for maritime studies. It is also connected to the grid.                                                                                                                     | 29 MPPT, one without MPPT, one load-commutated invertor (60 kVA) for grid connection, one synchronous motor (50kVA) for stand-alone operation and for power factor correction. |  |

| Kaw, French<br>Guiana       | 35                            | The electrification of a small village (70 inhabitants) remote from the grid. Diesel generators are too expensive. The energy is used for lighting streets, a school, a church, private homes and for refrigerators and cold stores. The scheme aims to stop the rural exodus by improving the living conditions. | One self-commutated invertor (40kVA) to feed the grid in a stand-alone mode.                                                                                                   |  |

TABLE 1.3 contd....

| Site                              | Total<br>rated<br>power (kWp) | Application                                                                                                                                                                                                                                                                                                                                                                                                          | Power conditioning system                                                                                                                                            |

|-----------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hoboken,<br>Belgium               | 30                            | The photovoltaic power is used for the production of hydrogen by electrolysis of water. Surplus power is used for pumping water. The loads are coupled directly to the photovoltaic array without convertors, invertors or batteries.                                                                                                                                                                                | Three DC/DC convertors, 750 W each for powering the monitoring and control equipment.                                                                                |

| Marchwood,<br>United Kingdom      | 30                            | The plant is constructed on a power station site. The power output is integrated into the local distribution system either to supplement the power taken from the national grid or to support individual, isolated, selected loads. The plant's scheme facilitates four modes of operation: grid connected with or without battery storage connected and stand-alone mode with or without battery storage connected. | One self-commutated invertor with integral MPPT.                                                                                                                     |

| Tremiti Island,<br>Italy          | 65                            | The system provides drinkable water by sea water desalinataion, using the reverse osmosis process. It is a standalone plant. The main loads are pumps with voltage and frequency controlled AC motors.                                                                                                                                                                                                               | Three DC/DC convertors, each 25 kW with MPPT. Several variable frequency and voltage invertors, approx 5KVA each.                                                    |

| Giglio Island,<br>Italy           | 45                            | The power is used for a water disinfection system and for a food cold store. A commercial ozoniser is used for the disinfection.                                                                                                                                                                                                                                                                                     | DC/DC convertors with MPPT,<br>one invertor 12 kVA for the<br>cold store unit and one<br>invertor 3.5 kVA, for the<br>ozoniser unit.                                 |

| Vulcano Island,<br>Italy          | 80                            | The plant can either supply power into the grid in parallel with an existing diesel station or feed a group of 30 isolated homes.                                                                                                                                                                                                                                                                                    | One line-commutated invertor 80 kVA with MPPT, one rectifier to charge the battery from the grid, one self-commutated invertor, 40 kVA, to power isolated consumers. |

| Rondolinu<br>(Corsica),<br>France | 30                            | It is a stand-alone plant to power a remote village. The power is used for electrification of the homes, public lighting and for a submersible water pump to supply potable water. It brings the possibility of developing a cottage industry and starting some touristic activities.                                                                                                                                | One self-commutated invertor, 50 kVA, to feed the village grid in a stand-alone mode.                                                                                |

silicon, amorphous silicon and  $CdS-Cu_2S$ . They found that the  $CdS-Cu_2S$  cell requires less energy for its preparation than any of the other. The prime advantage of  $CdS-Cu_2S$  cells is due to the low cost of processing and the use of relatively low cost materials. Thin film  $CdS-Cu_2S$  heterojunction material is one of the few commercially available alternatives to silicon cells at the present time. The total estimated production cost for  $CdS-Cu_2S$  thin film cells is \$0.18/peak W of which 32% is material cost and 25% is labour cost [5]. One proposal for minimizing the interface and electron affinity problems is to introduce some zinc into the CdS as was first suggested by Palz et al [45]. However, this modification has not led to significant improvements in device performance.

# 1.6 Scope Of The Present Work

The work reported in this thesis is primarily concerned with the application of the electroplating technique to the formation of  ${\rm Cu_2S}$  on thin film and single crystal CdS, and on  ${\rm Cd_yZn_{1-y}S}$  single crystal substrate to produce heterojunctions. The effects of the plating bias, the ambient in which the annealing was carried out, and the period of annealing on the phase of copper sulphide and on the electrical properties for these devices have been investigated. Chapters 5,6 and 8 are concerned with CdS-Cu\_S single crystal, thin film and  ${\rm Cd_yZn_{1-y}S-Cu_2S}$  devices respectively. The combined effects of the substrate and annealing ambient on the characteristics of  ${\rm CdS-Cu_2S}$  thin film heterojunction have been studied. Chapter 7 described the degradation behaviour of  ${\rm CdS-Cu_2S}$  single crystal cells as a function of illumination and ambient. Also in Chapter 7, the mechanism of dark current conduction is reported as a function of the value of electroplating bias. Chapter 8 records a study of cells based on  ${\rm Cd_{0.8}\ Zn_{0.2}\ S}$  substrates.

This includes the influence of the plating and heat treatment on the properties of the copper sulphide phase, and on the characteristics of the heterojunction devices formed. Steady state photocapacitance studies were carried out on these devices as a function of the ambient and the period of annealing.

#### REFERENCES TO CHAPTER ONE

- De Gromard and B.Cornut: Proceeding of 7th EC Photovoltaic Solar Energy Conf., Sevilla, Spain 23-31 Oct 1986. p.20.

- D Maycock Paul and N.Edward Stirevalt: "A Guide to the Photovoltaic Revolution" Rodale Press, Emmaus, Pa, 1985 p.7.

- 3 S.Ashok and K.P.Pande: Solar Cells I4 (1985) p.61.

- 4 L.David Pulfrey: "Photovoltaic Power Genertion", Van Nostrand Reinhold Company 1978

- Chenning Hu and R.M.White: "Solar Cells from Basic to Advanced System" McGraw-Hill Book Company 1983 p.75.

- 6 J.M.Gordon: Solar Cells 20 (1987) p.295.

- 7 E.Becquerel: Comt.Rend.Vol.9 (1039) p.561.

- 8 Willoughby-Smith: Nature London 7 (1873) p.303.

- 9 W.G.Adams and R.E.Day: Proc.Roy.Sec.London Ser A25 (1877) p.113.

- 10 K.Hallwachs: Phys.Zechr.5 (1904) p.489.

- 11 B.Lange: Zeit phys. Vol.31 (1930) p.139.

- 12 L.O.Grondahl: Revi.Mod.phys. Vol.5 (1933) p.141.

- 13 W.Schottky: Zeit Phys. Vol. 31 (1930) p.913.

- 14 H.Dember: Phys.Z. 32 (1931) p.554.

- D.C.Reynolds, G.Leies, L.L.Antes and R.E.Marburger: Phys.Rev.96 (1954) p.533.

- D.M.Chapin, C.S.Fuller and G.L.Pearson: J.Appl.Phys. 25 (1954) p.676.

- D.A.Jenny, J.J.Loferski and P.Rappaport: Phys.Rev. 101 (1956) p.1208.

- 18 M.P.Prince: J.Appl.Phys. Vol.26 (1955) p.534.

- 19 J.J.Loferski : J.Appl.Phys. 27 (1956) p.777.

- 20 M.Wolf: Proc. IRE 48 (1960) p.1246.

- 21 A.Rothwarf : J.Vac.Sci. Technol. 20 (1982) p.282.

- 22 R.Williams and R.H.Bube : J.Appl.Phys. 31 (1960) p.968.

- F.A.Shirland and J.R.Hietanen: Proceeding 5th Photovoltaic Specialists Conf. IEEE, Sec 111C New York 1965.

- L.R.Shiozawa, F.Augustine, G.A.Sullivan, J.M.Smith and W.R. Cook: Aerospace Res.Lab. Report ARL 69-0155 1969.

- A.M.Barnett, J.A.Braganolo, R.B.Hall, J.E.Philips and J.D.Meakin: 13th Photovoltaic Specialists Conf. IEEE, New York 1978 p.419.

- J.C.C. Fan: Proceeding 18th IEEE Photovoltaic Specialists Conf. Las Vegas, Nevada, Oct 21-15 (1985) p.28.

- 27 R.M.Swanson and R.A.Sinton: 7th EC Photovoltaic Solar Energy Conf. Sevilla, Spain, 27-31 Oct (1986) p.742.

- 28 H.Matsumato, K.Kuribayashi, H.Hda, Y Komatsu, A.Nakano and S.Ikegami: Solar Cells 11 (1984) p.367.

- 29 R.B.Hill, R.W.Birkmire, J.E.Philips and J.D.Meakin: Appl.Phys. Lett.38 (1981) p.925.

- A.M.Barnett and A.Rothwarf: IEEE Trans. of Electron Devices Ed-27 4 (1980) p.615.

- 31 K.L.Chopra and S.R.Das: "Thin Film Solar Cells", Plenum Press (1983) p.83.

- 32 S.J.Fonash and A.Rothwarf: "Heterojunction Solar Cells" in "Current Topics in Photovoltaic" edited by T.J.Coutts and J.D.Meakin, Academic Press, 1985.

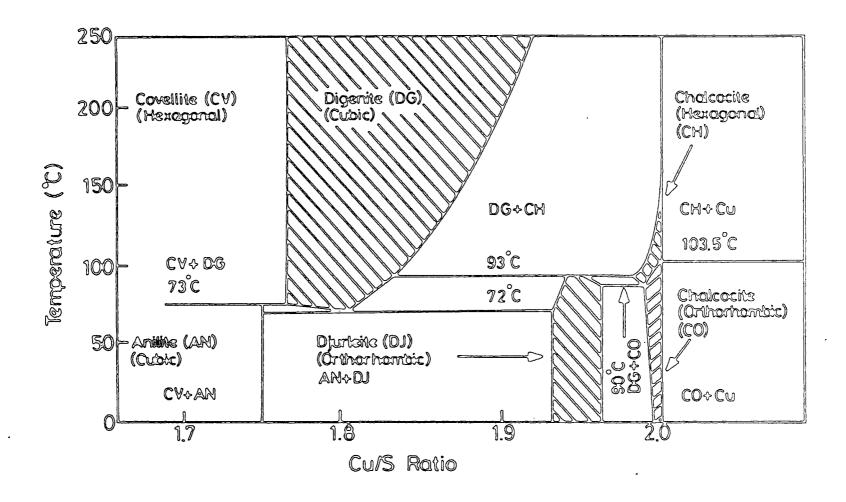

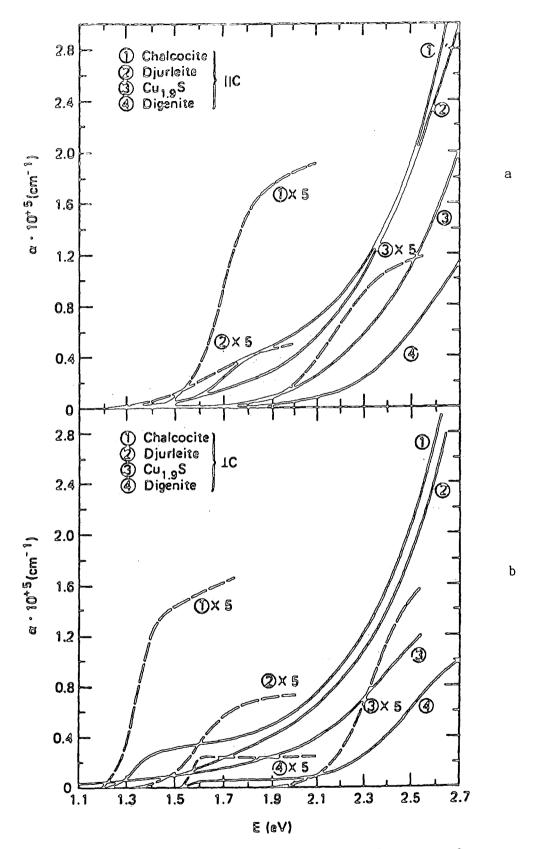

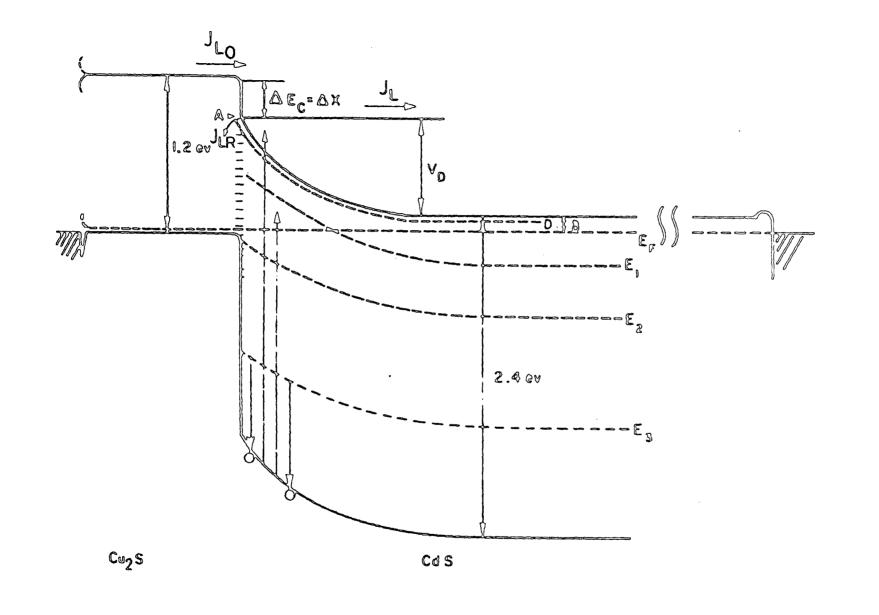

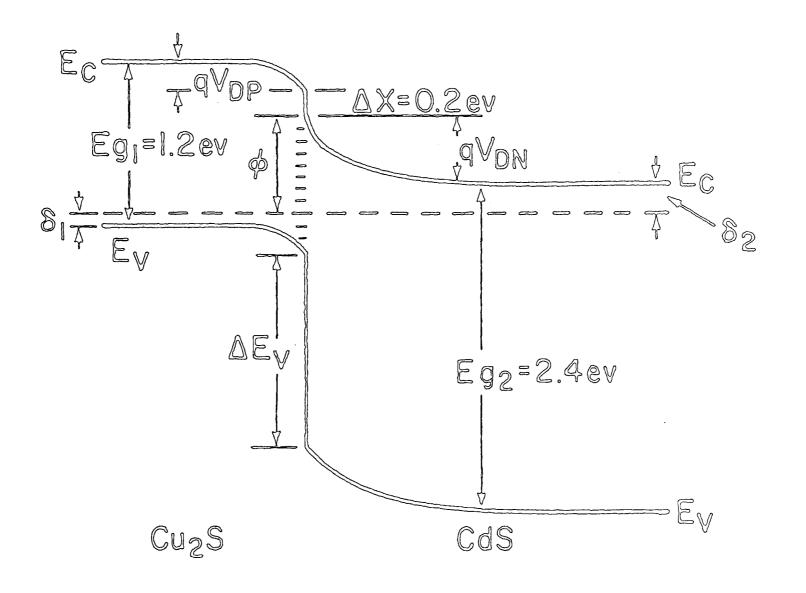

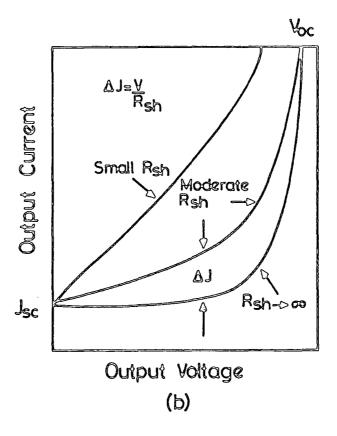

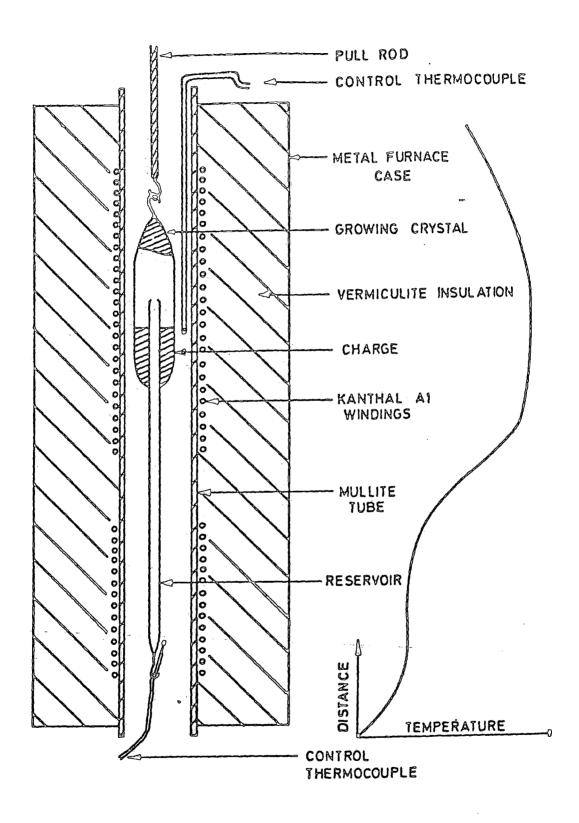

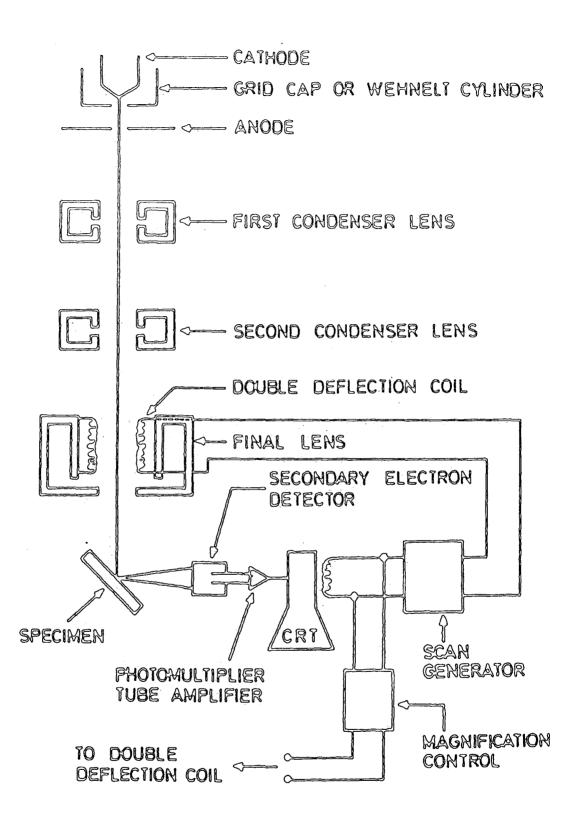

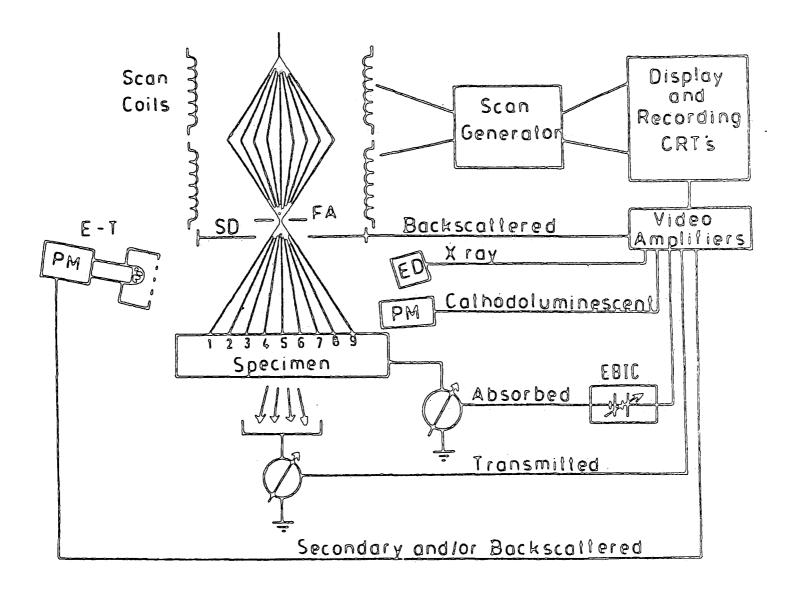

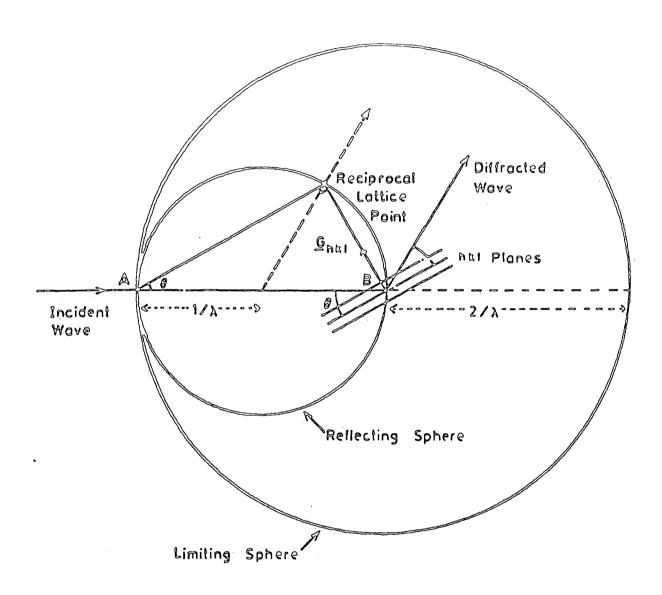

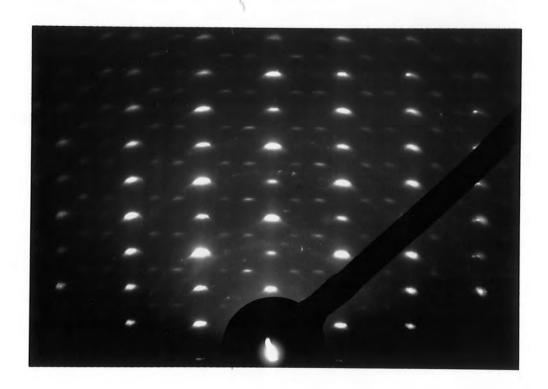

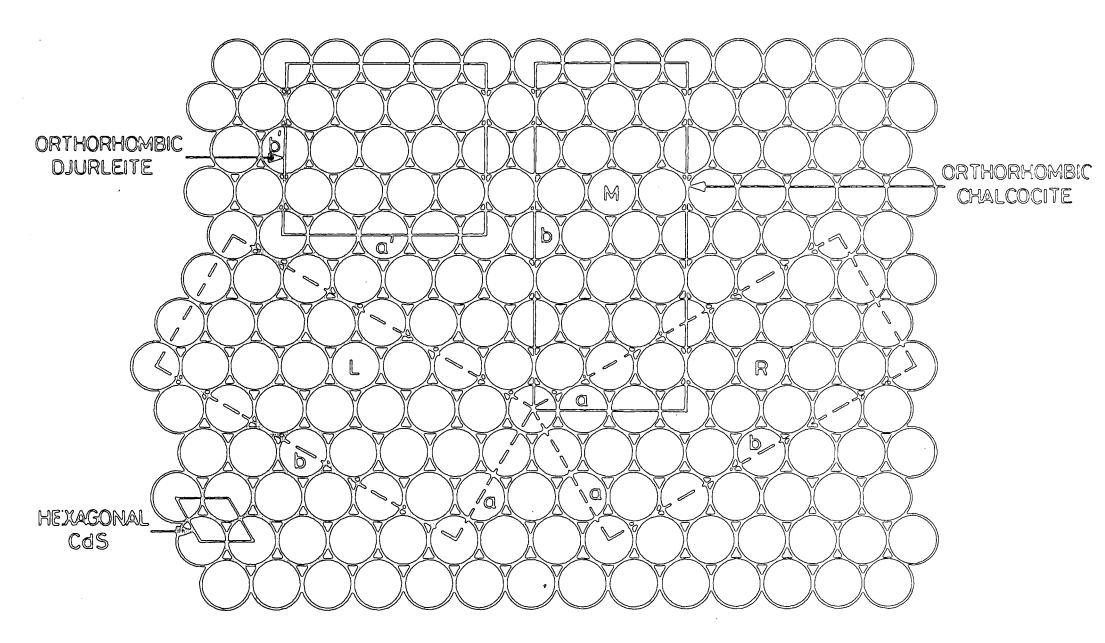

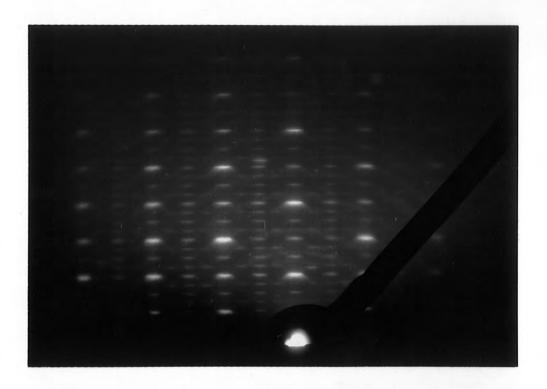

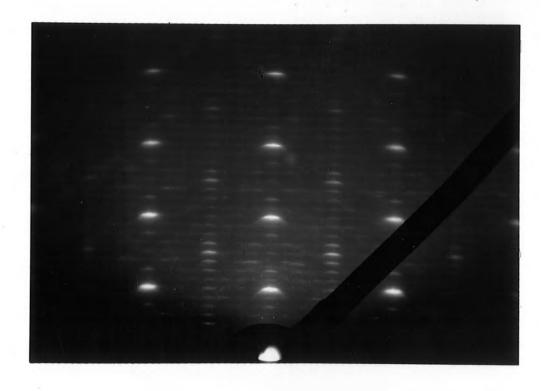

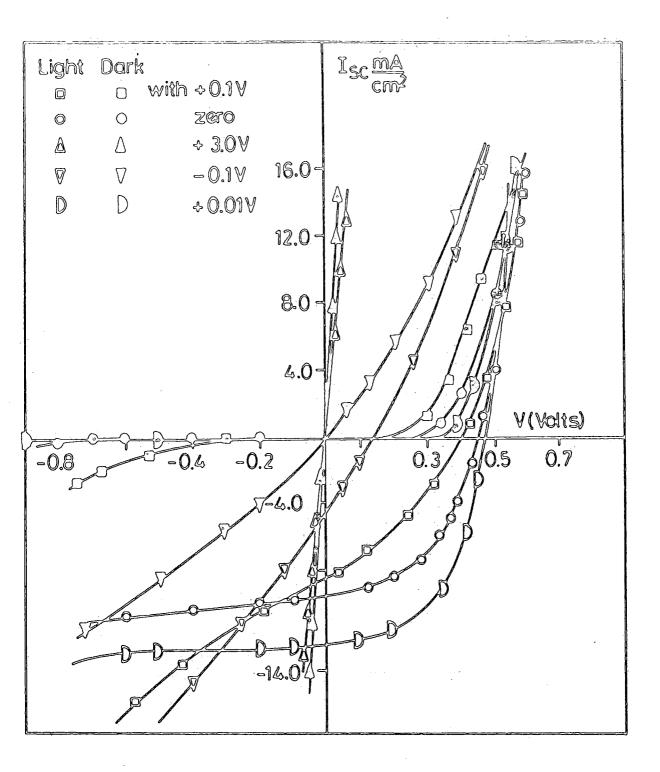

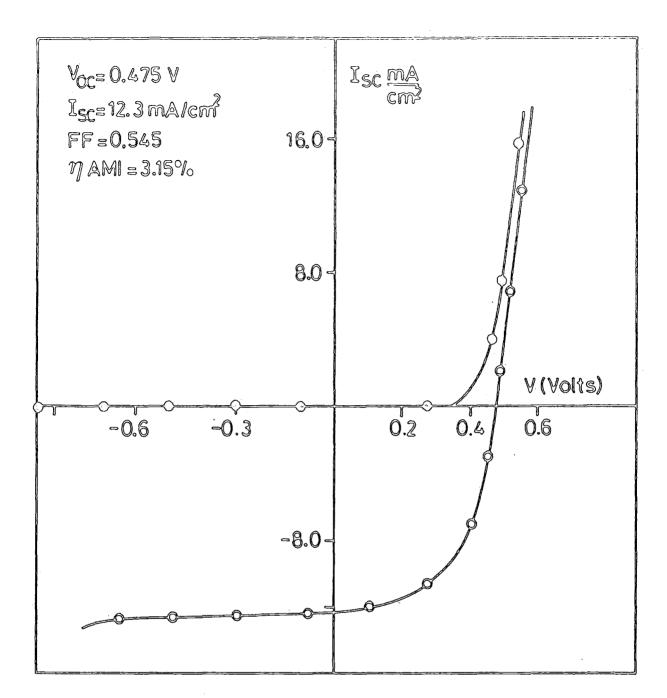

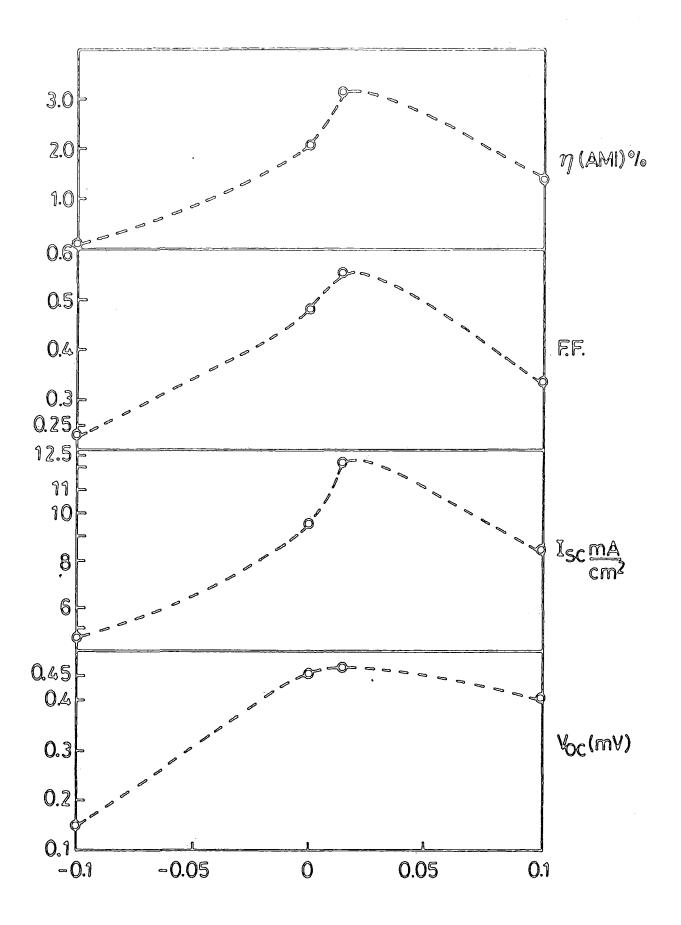

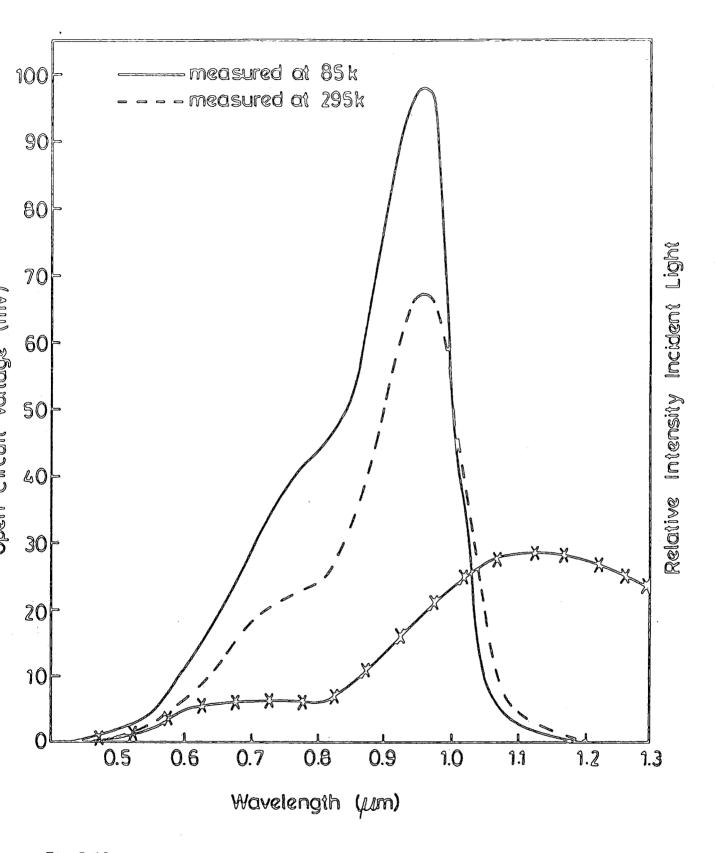

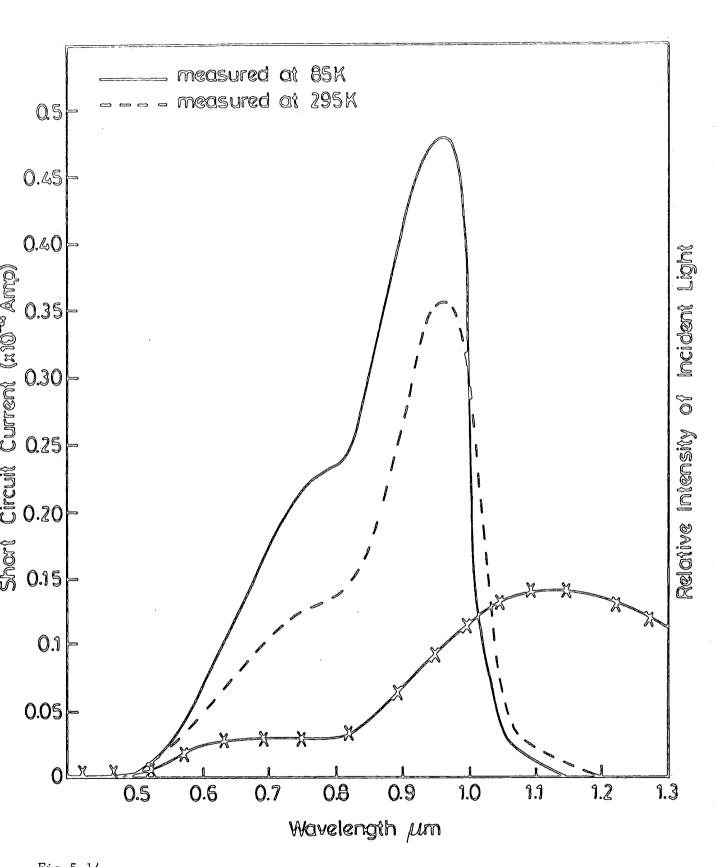

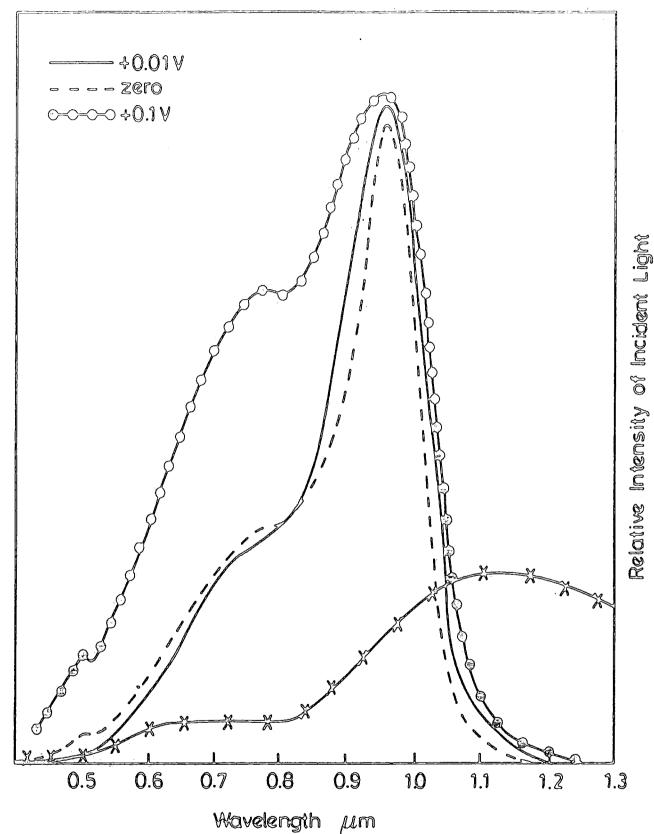

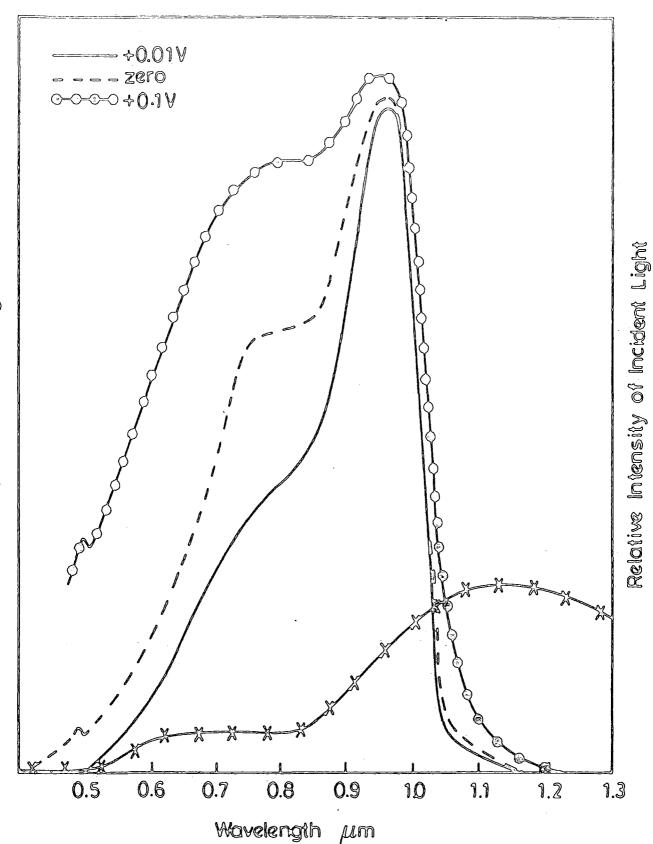

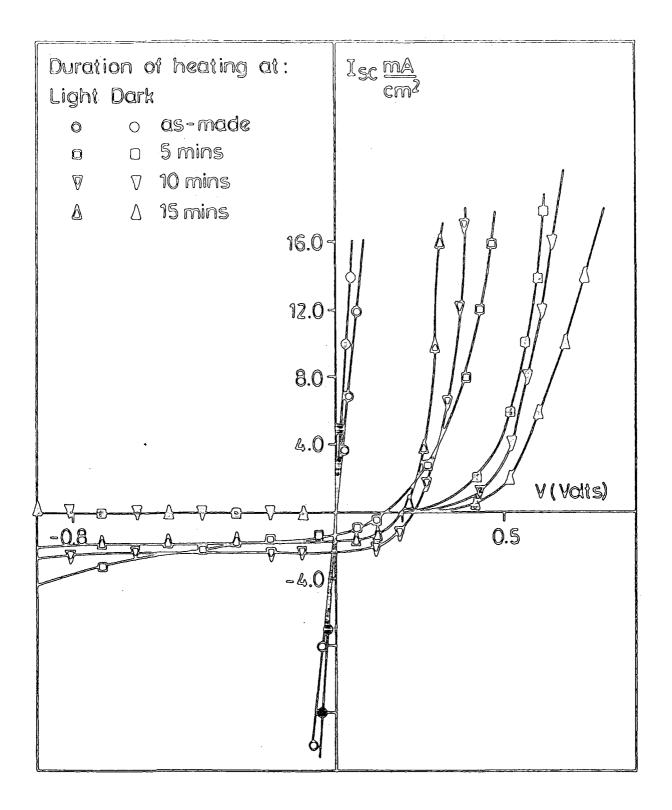

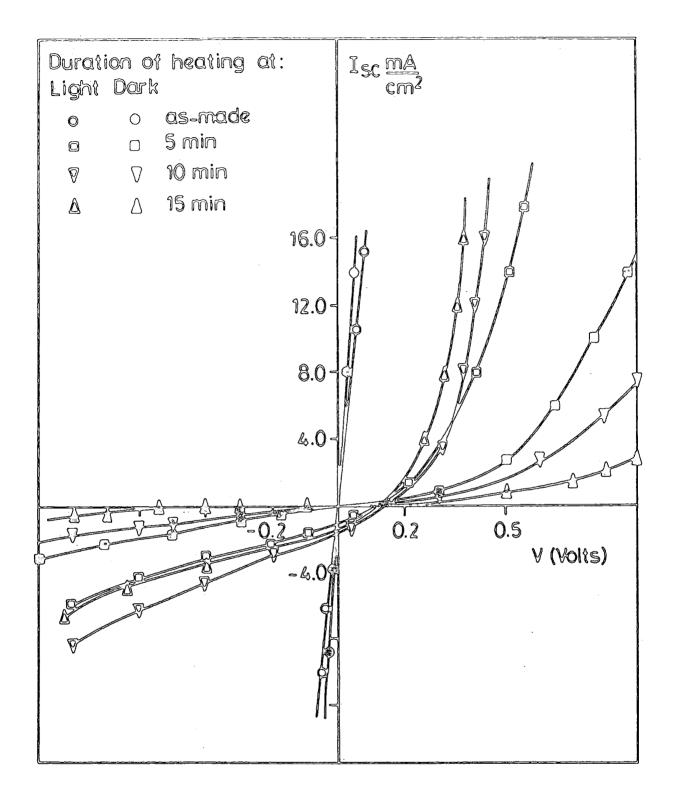

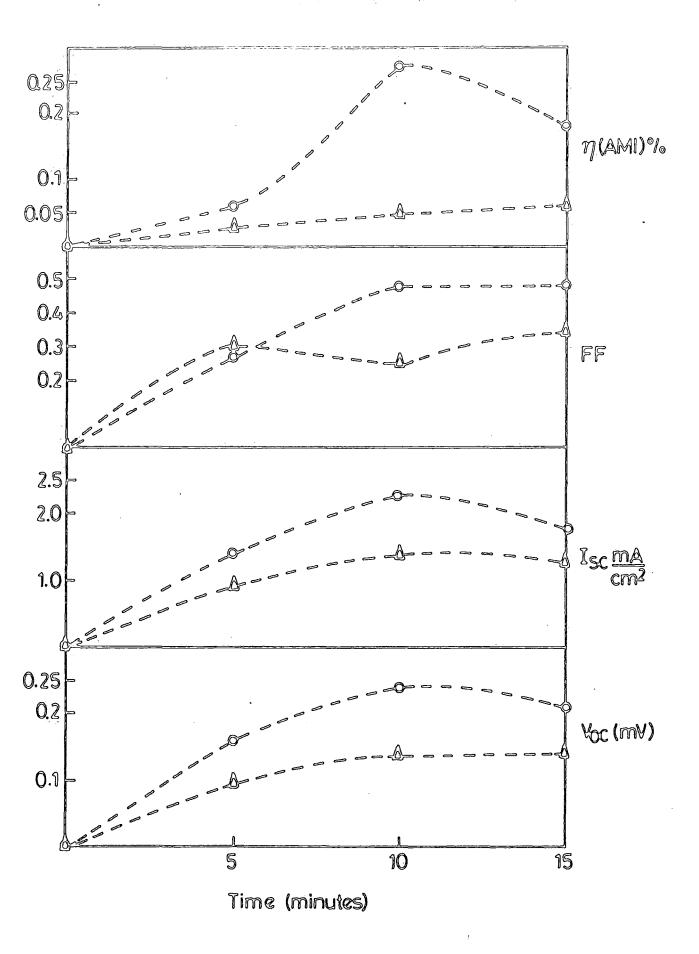

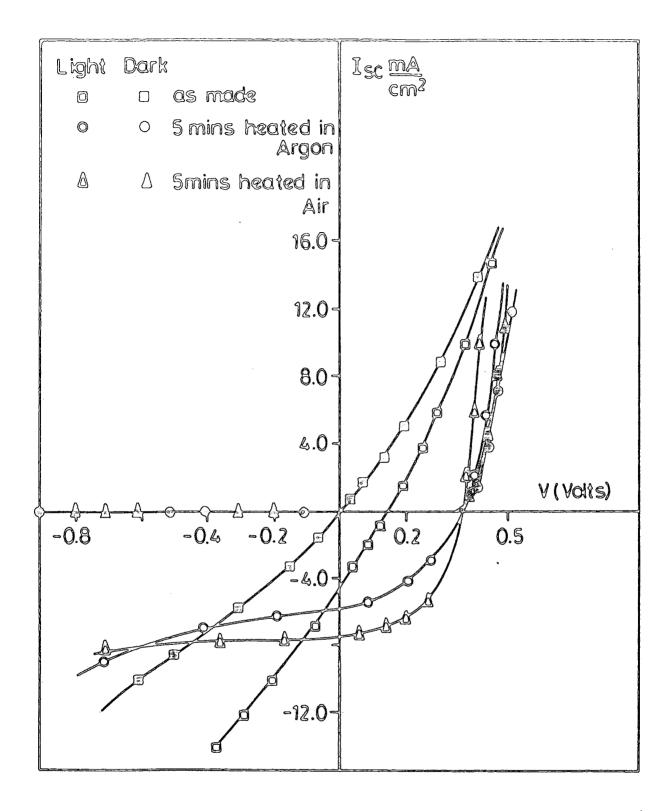

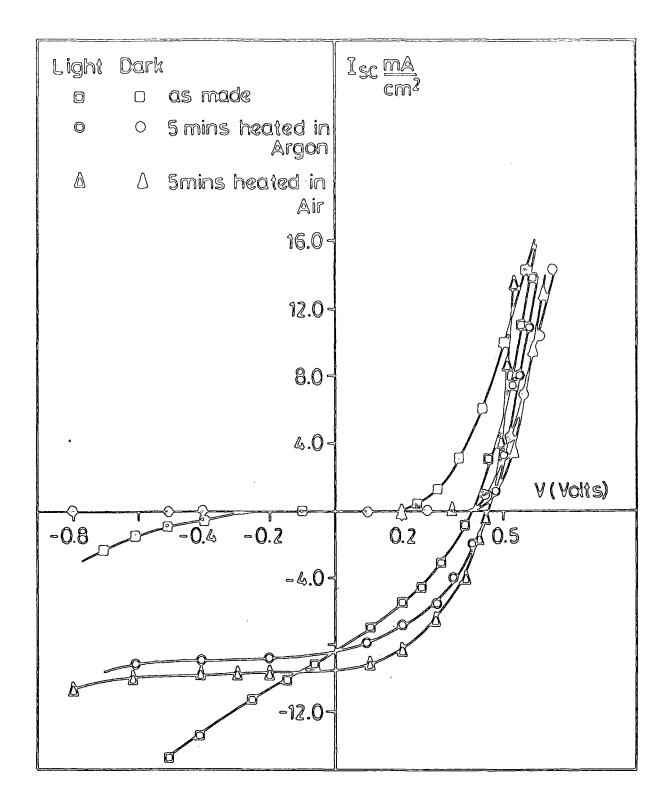

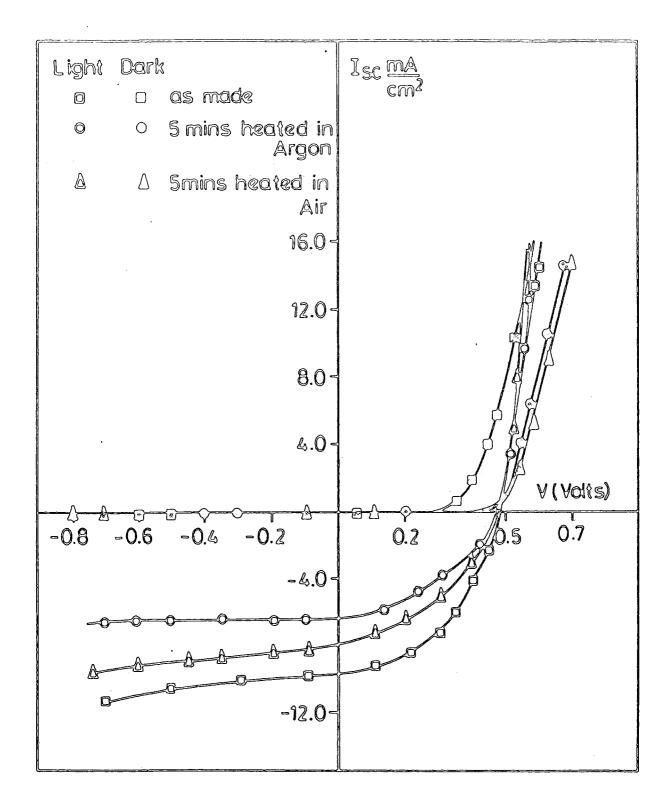

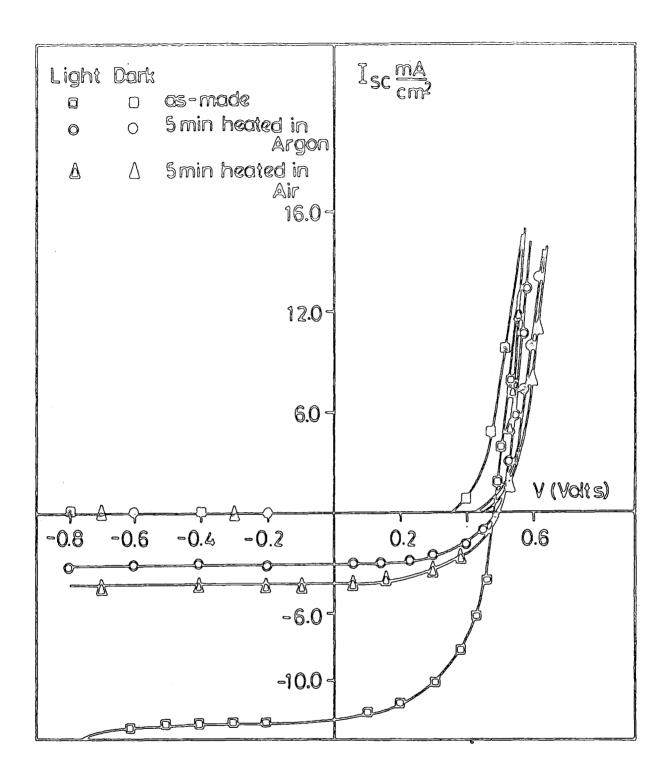

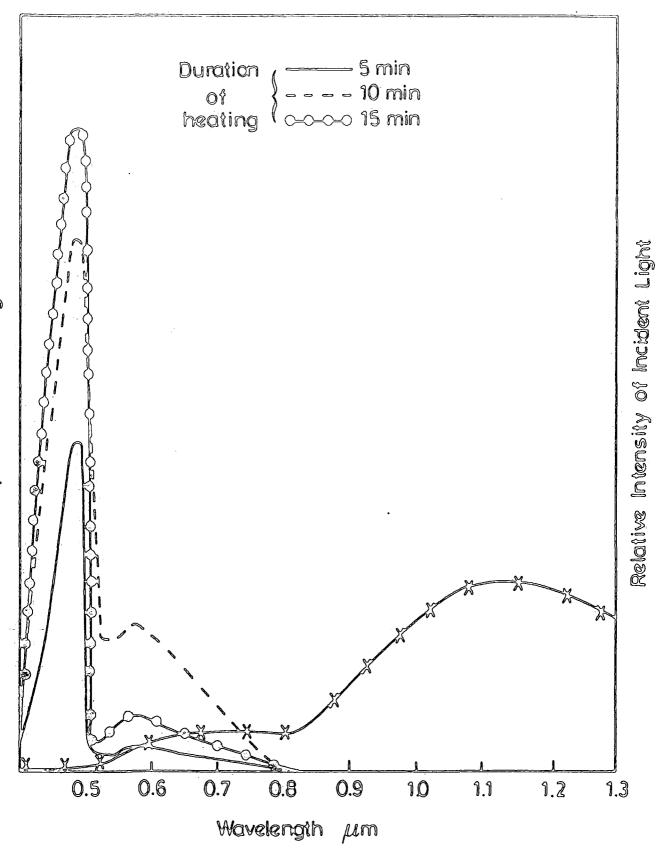

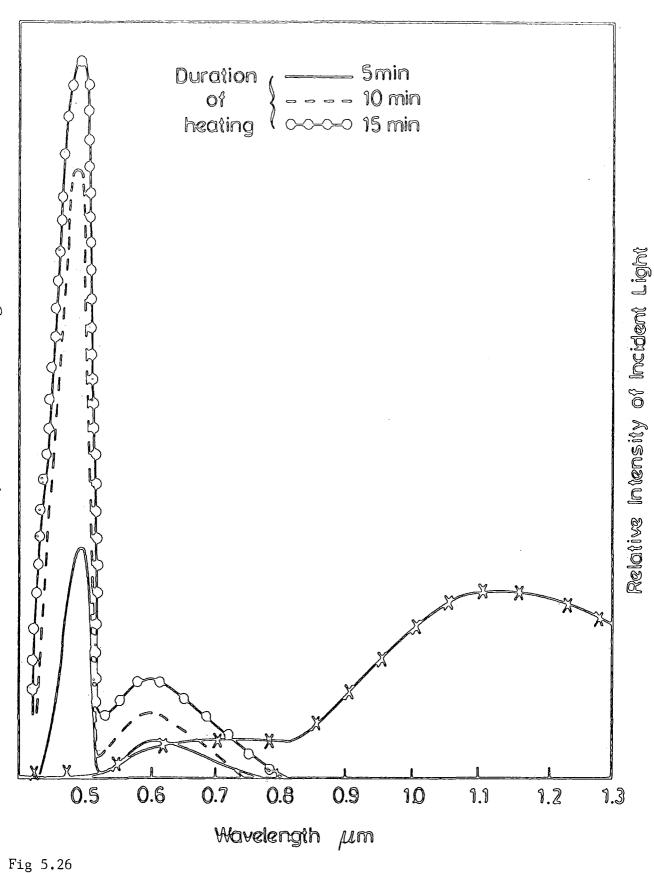

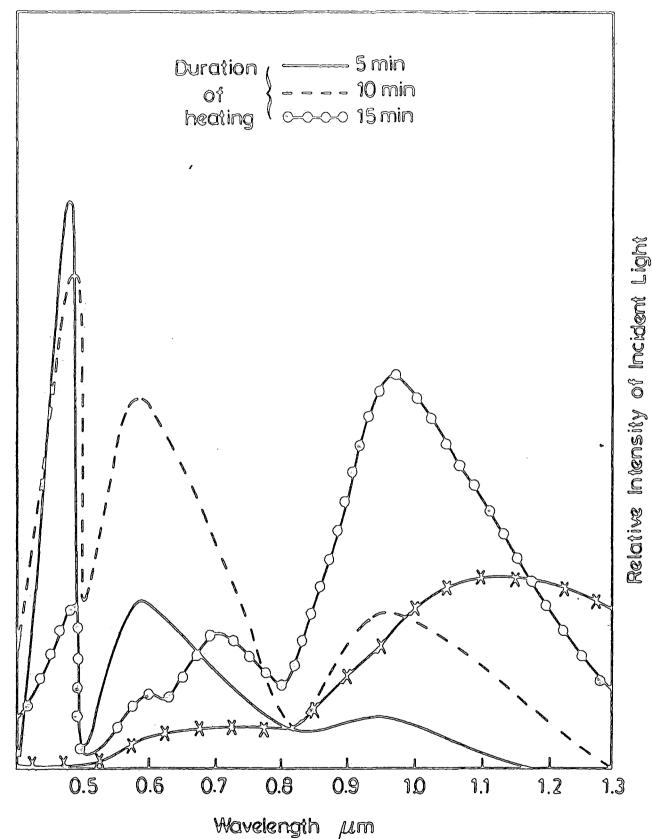

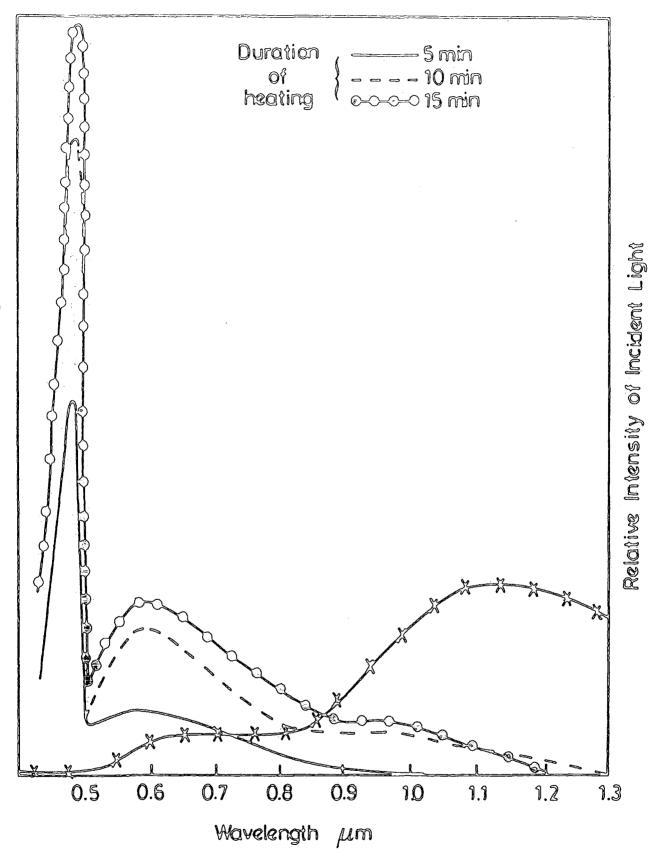

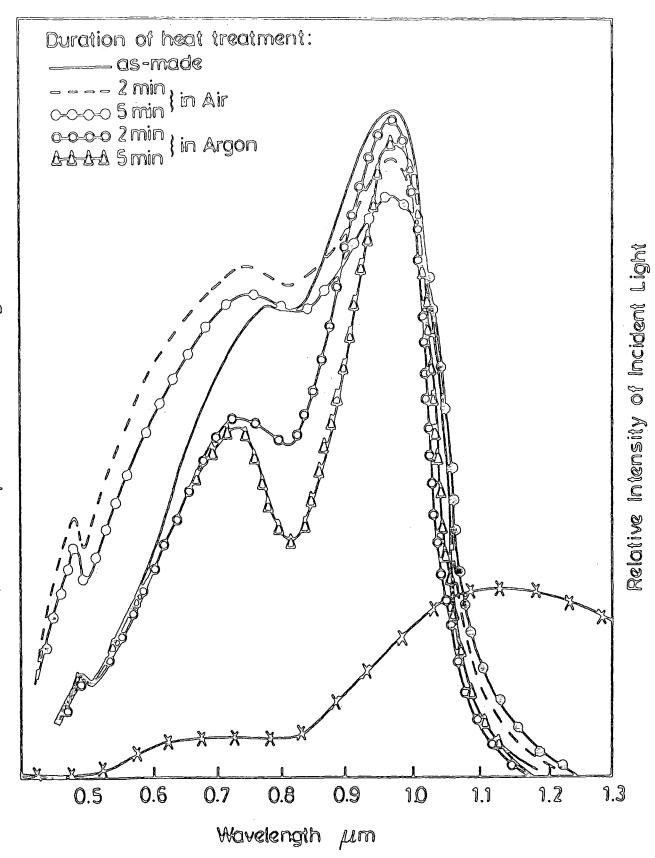

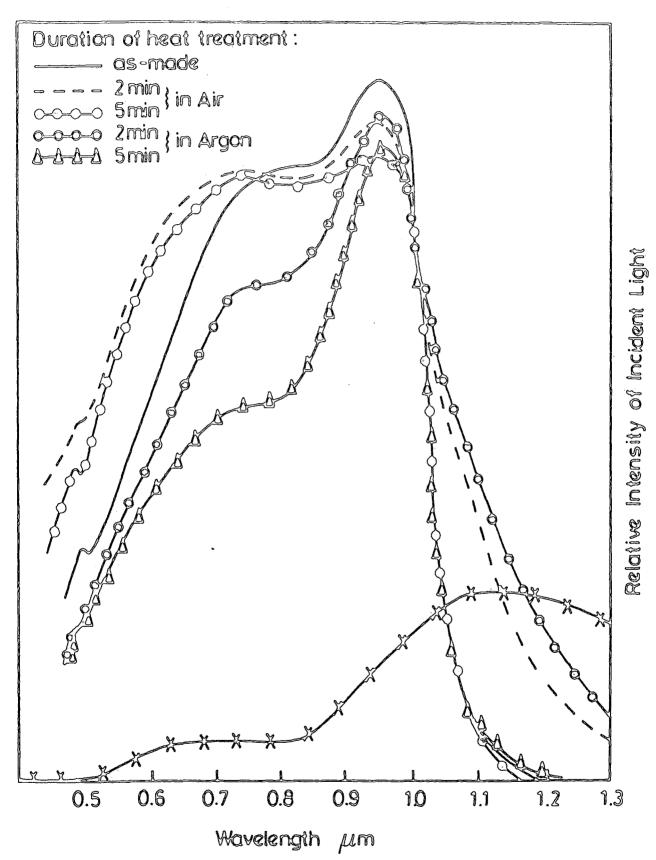

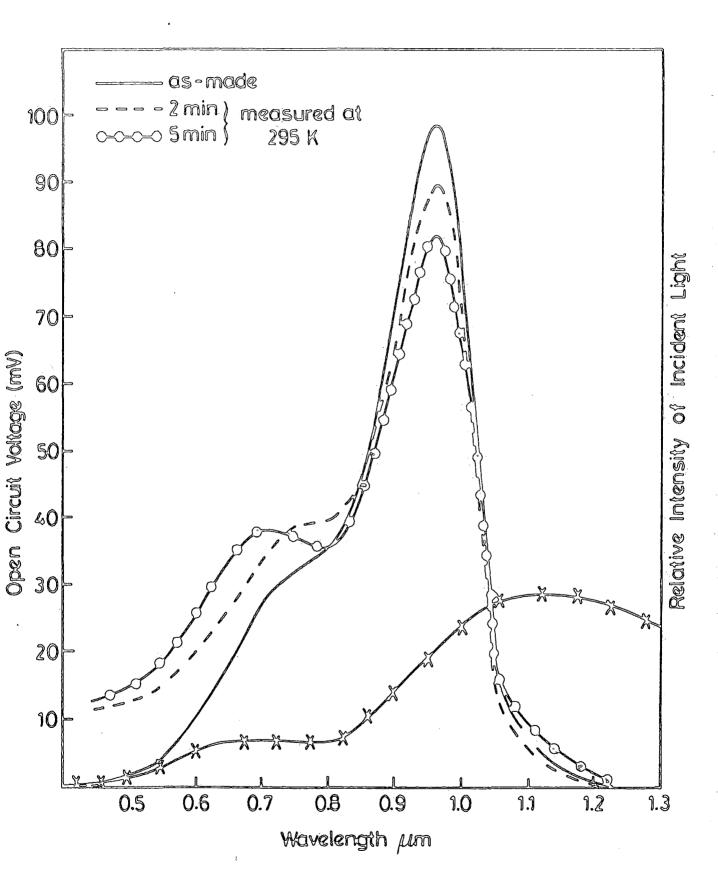

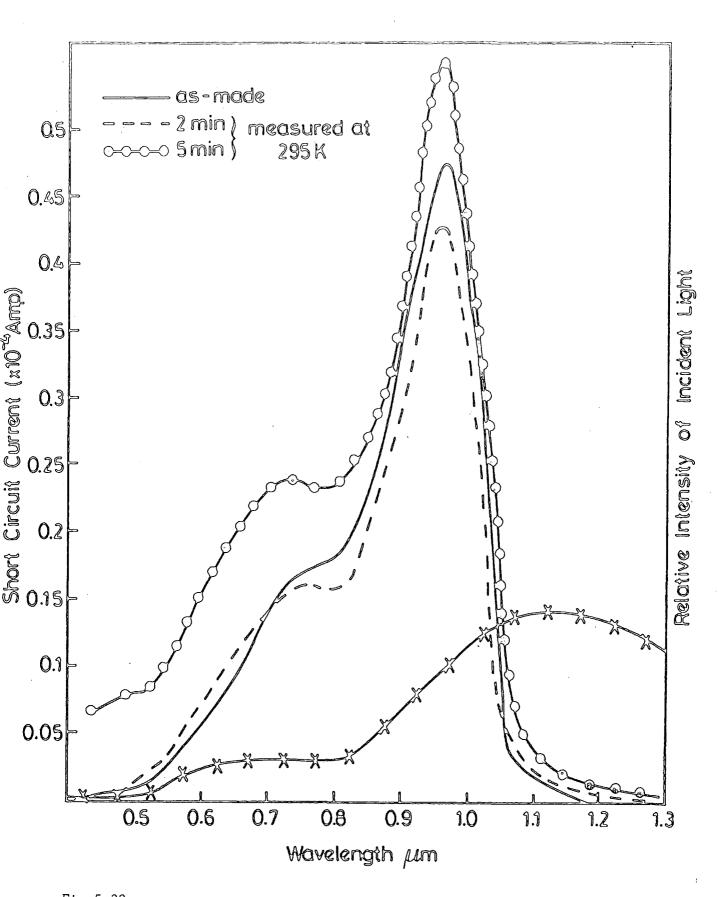

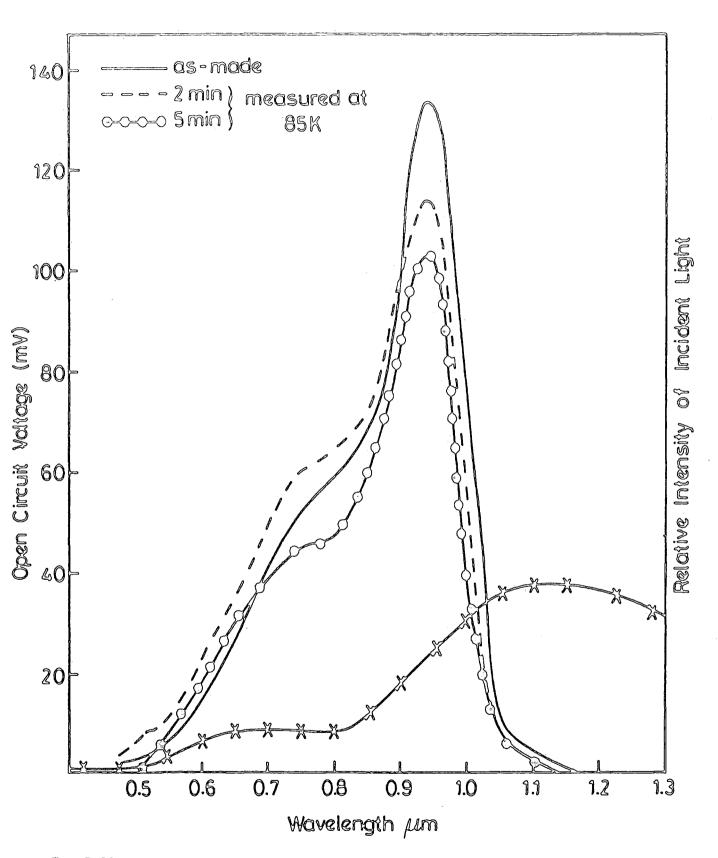

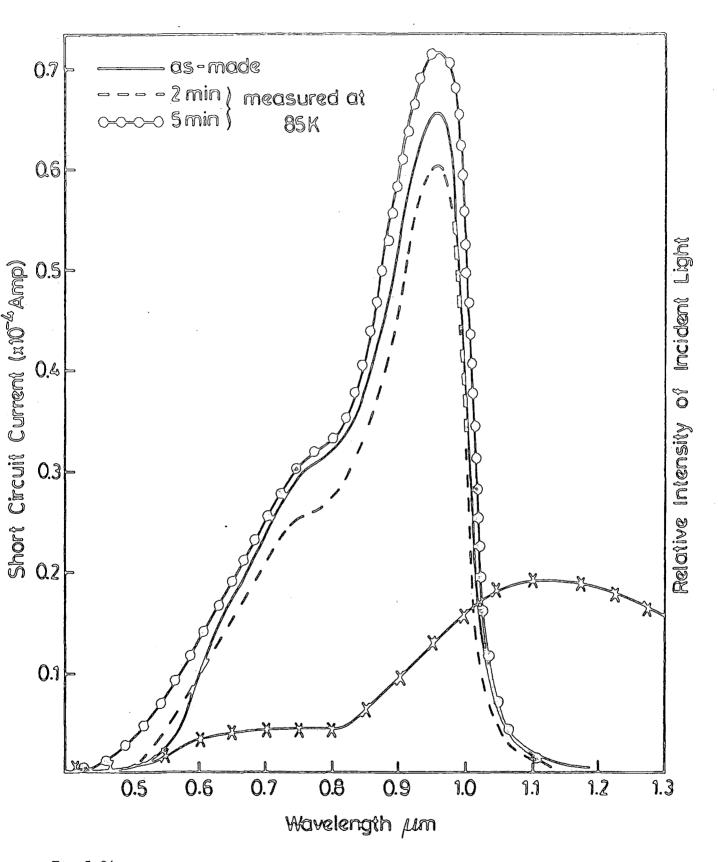

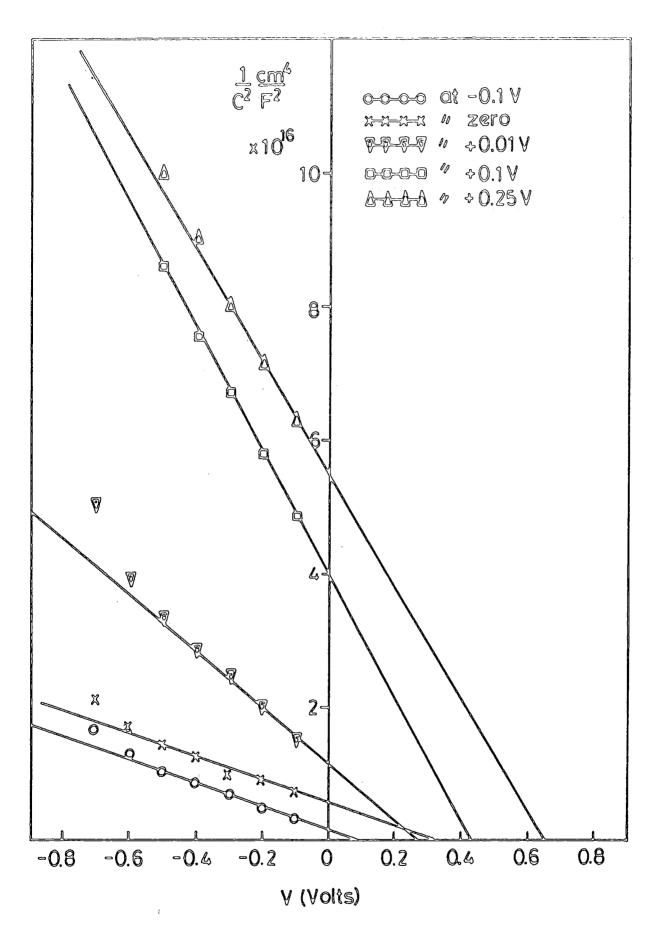

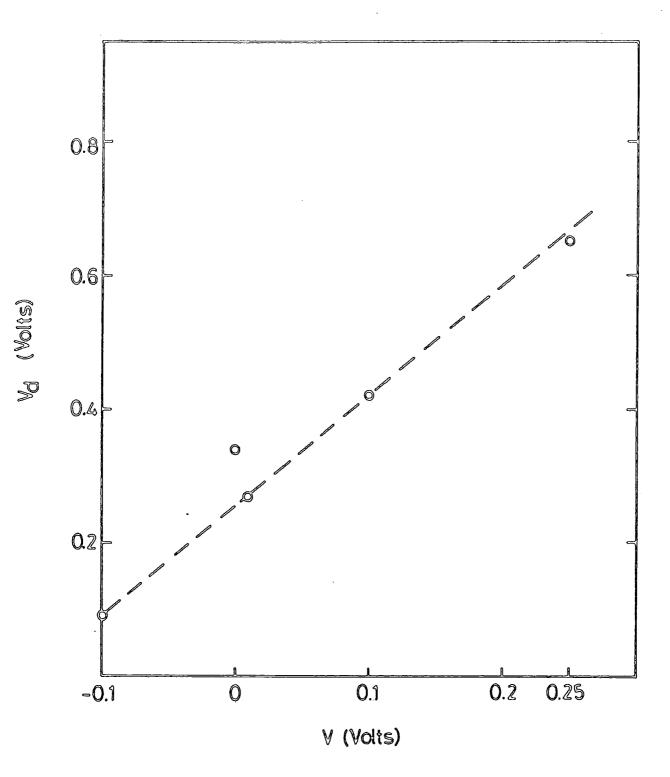

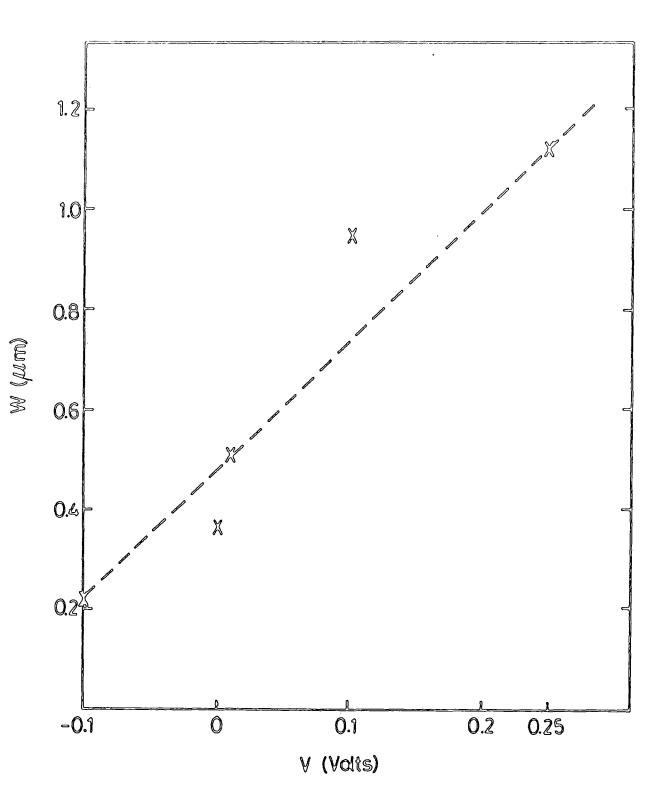

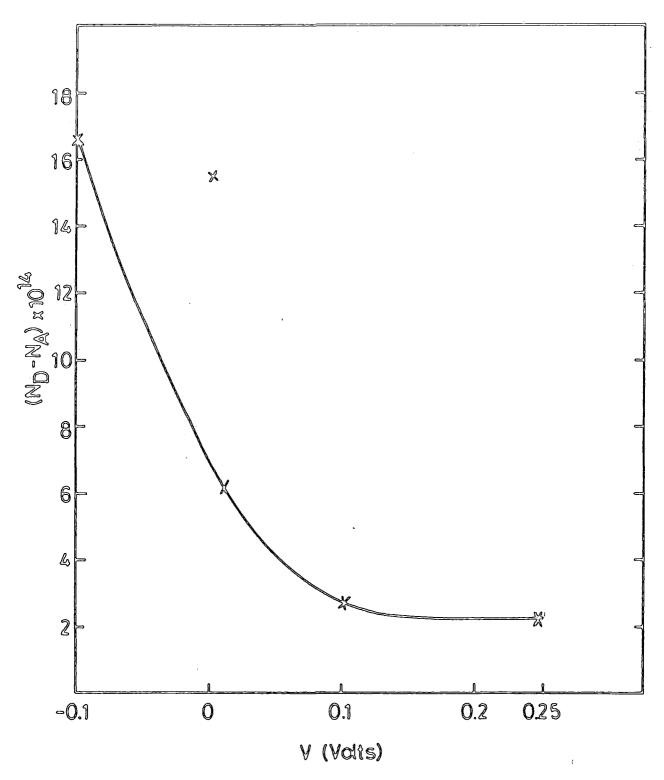

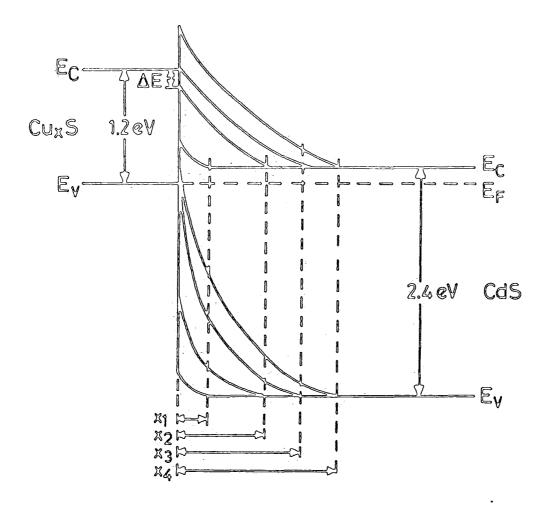

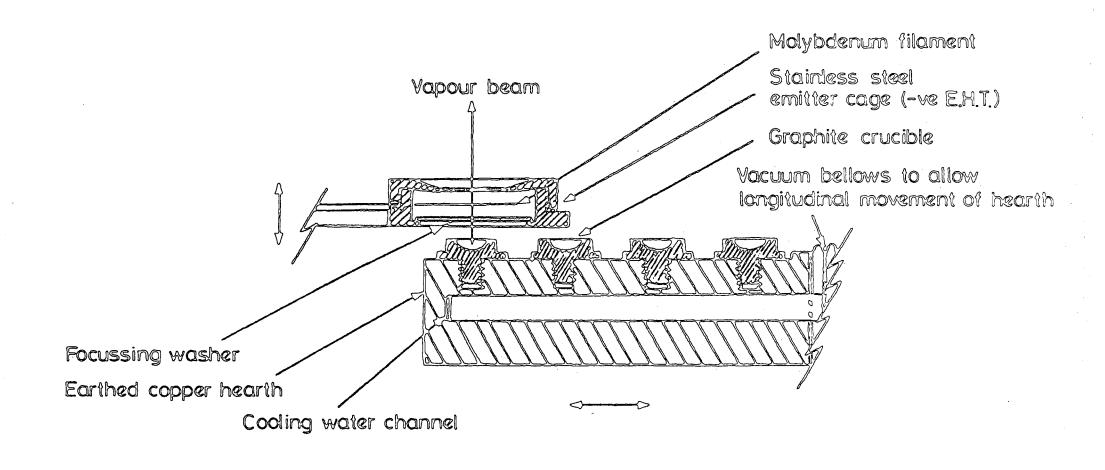

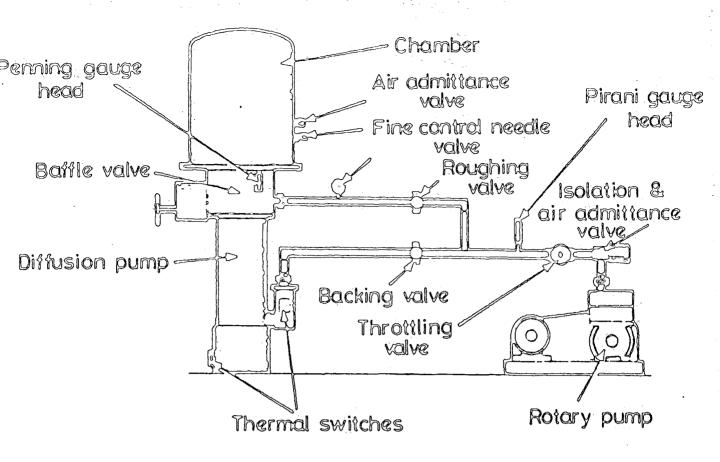

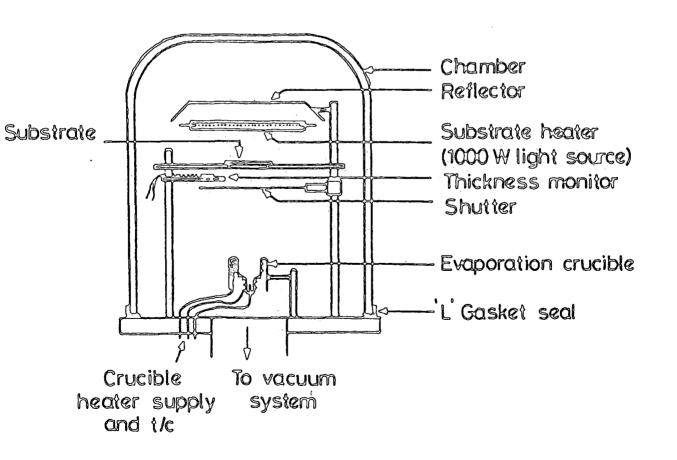

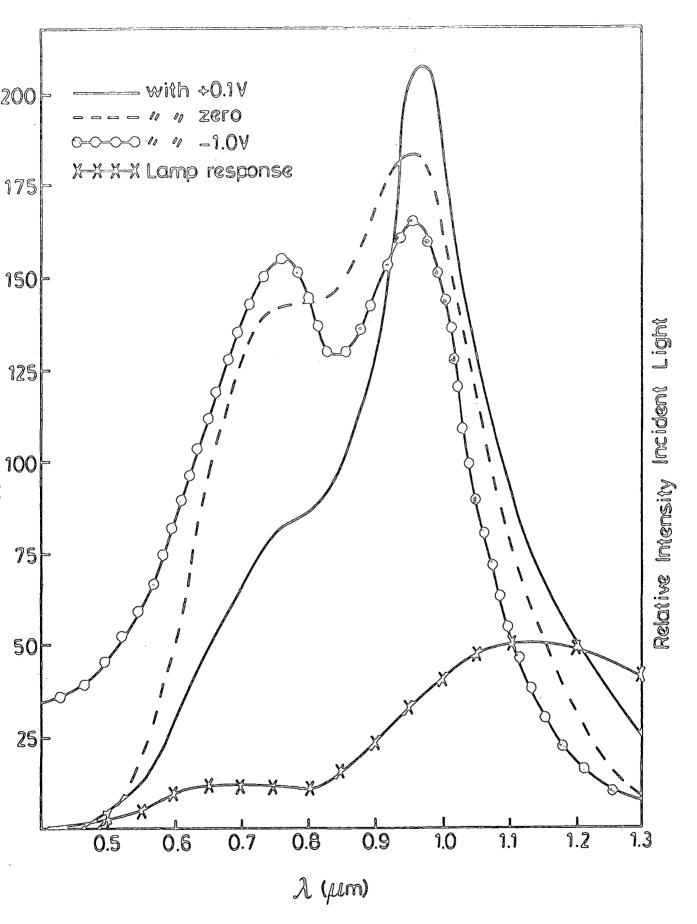

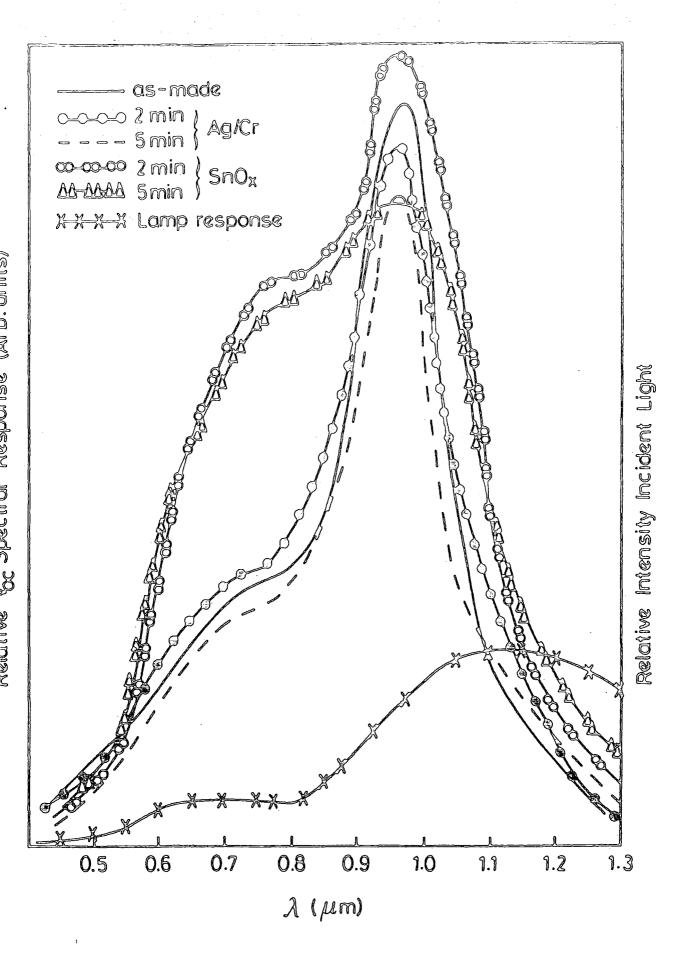

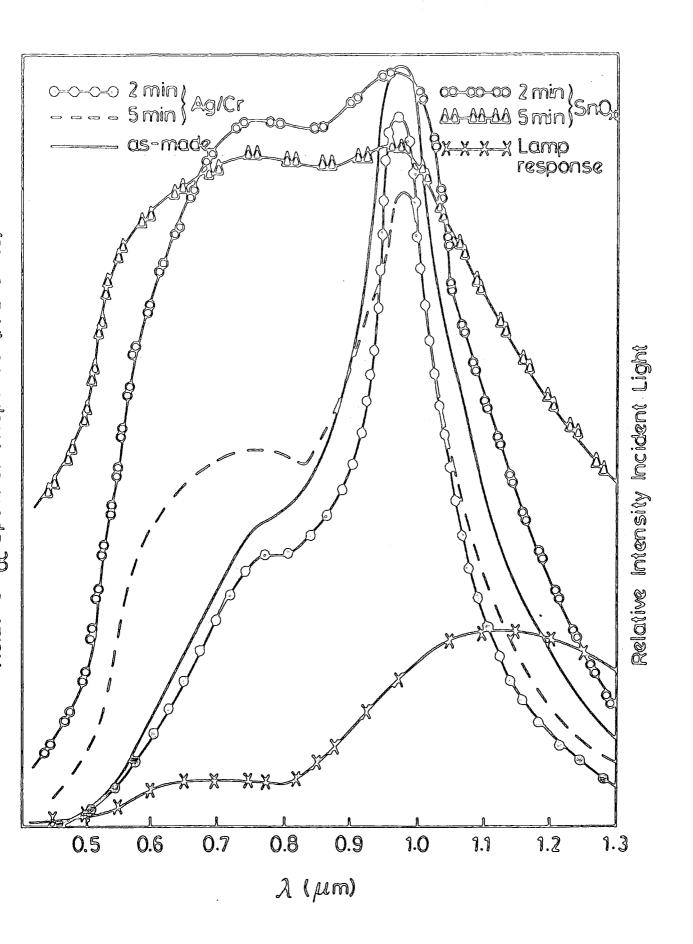

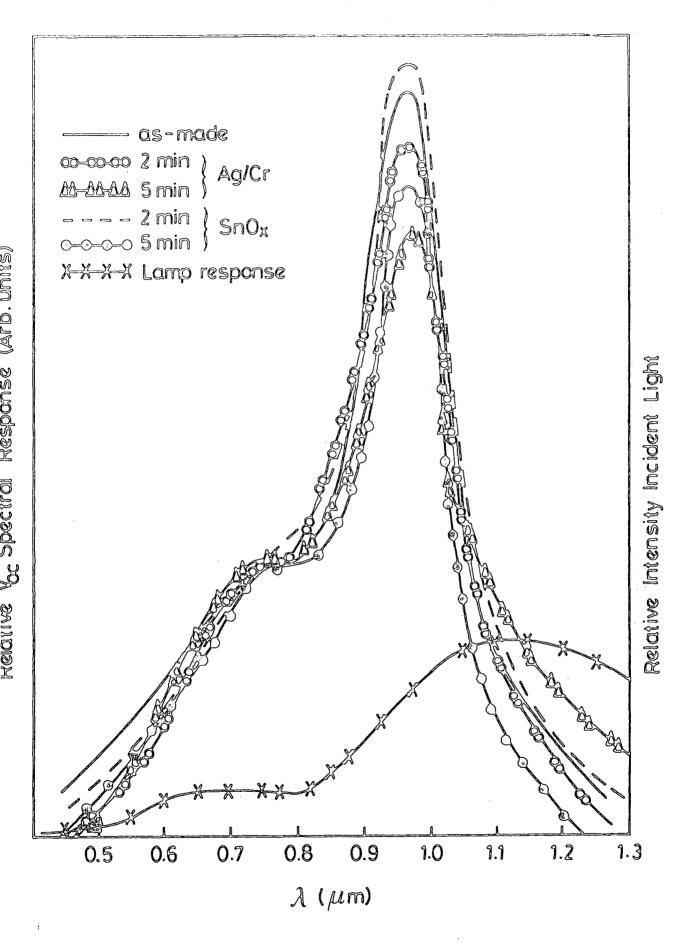

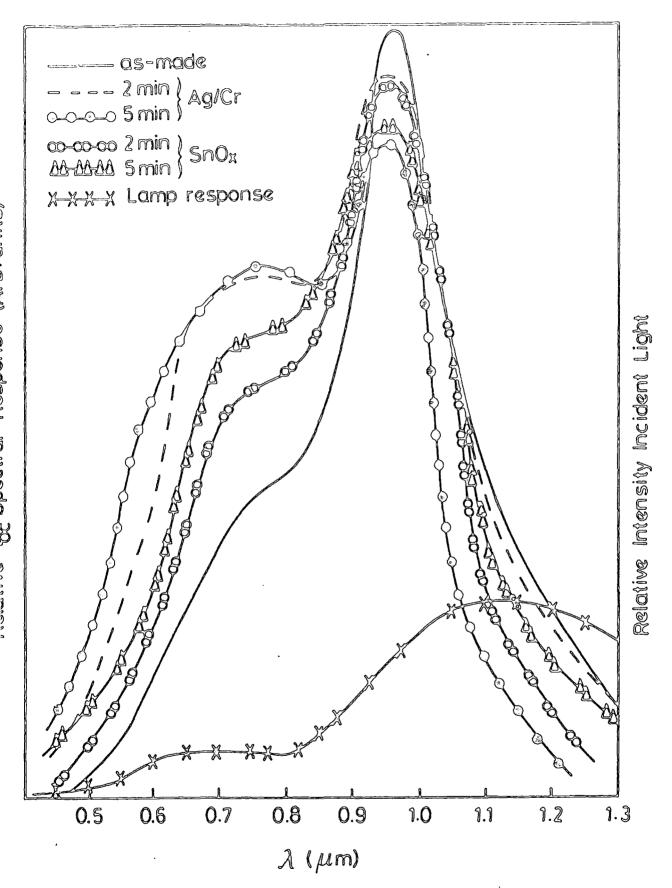

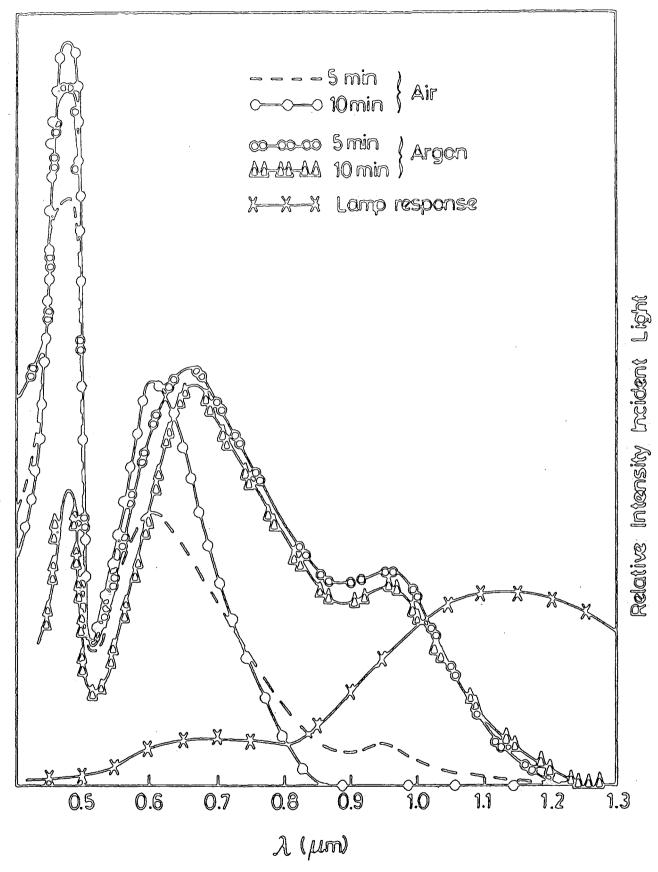

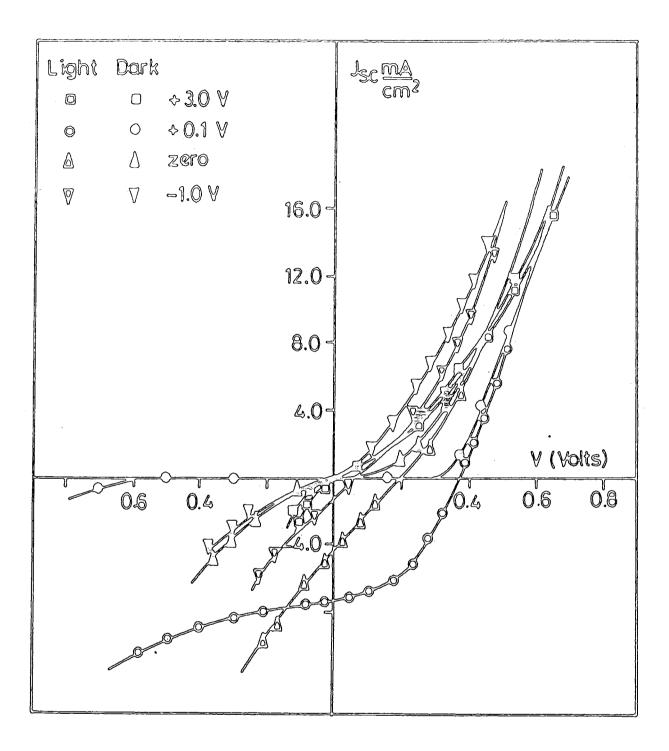

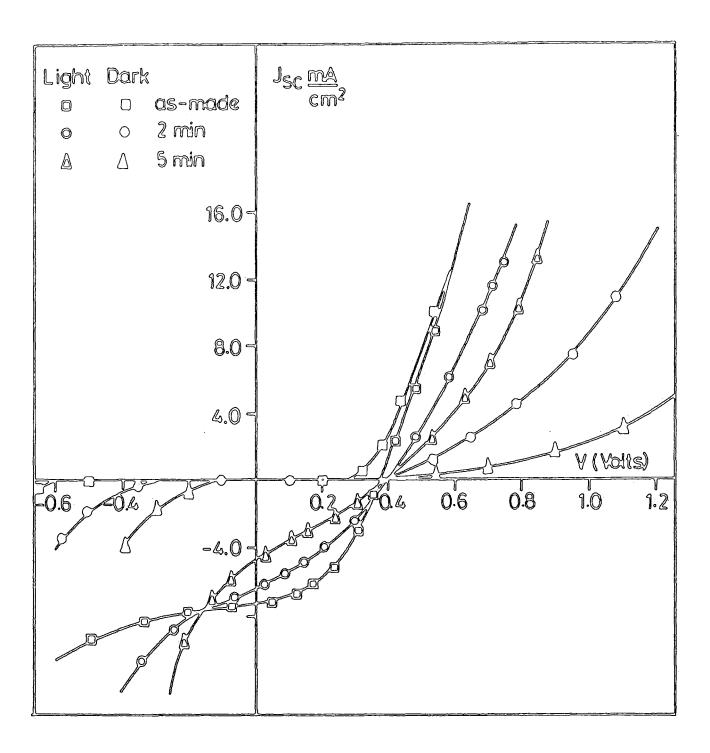

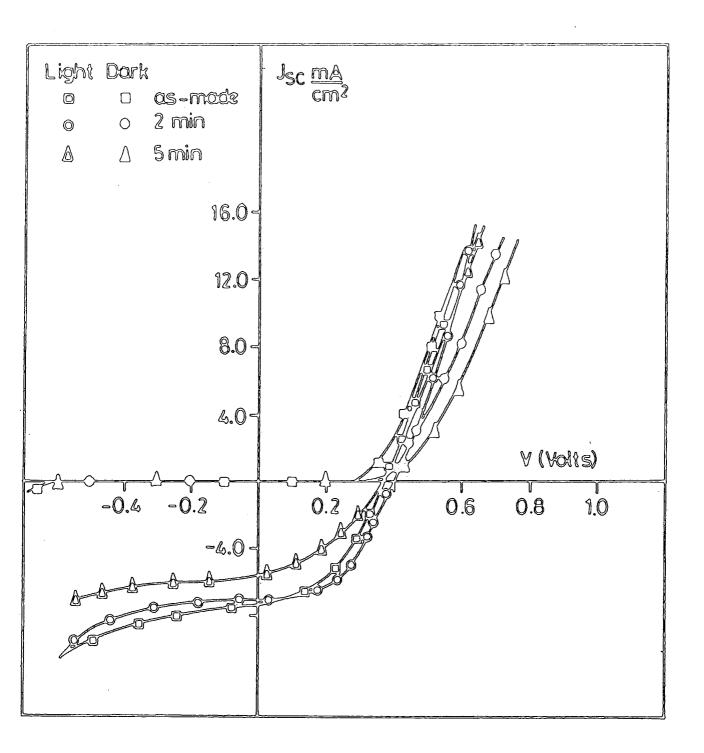

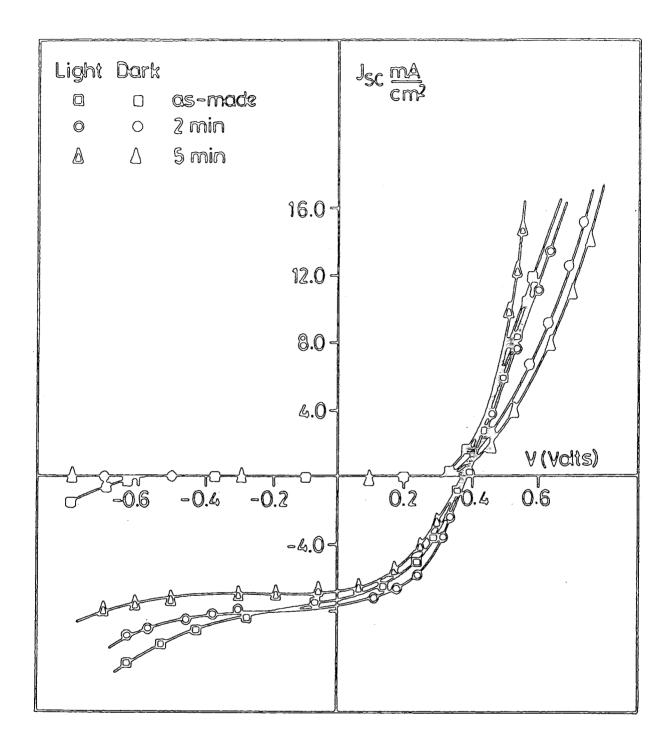

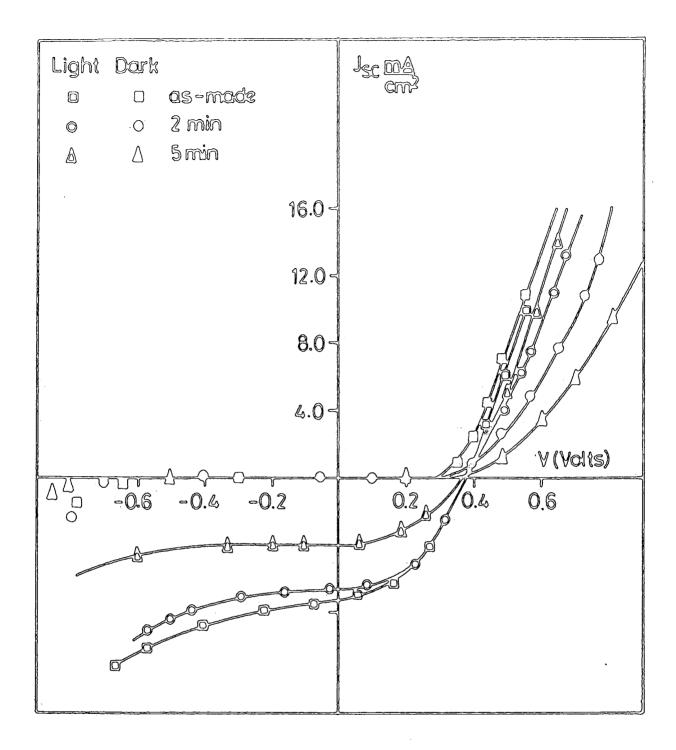

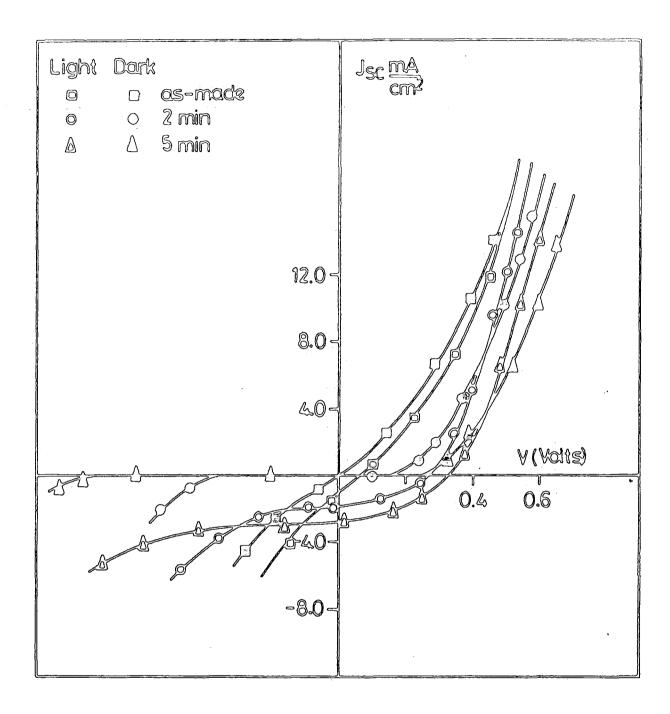

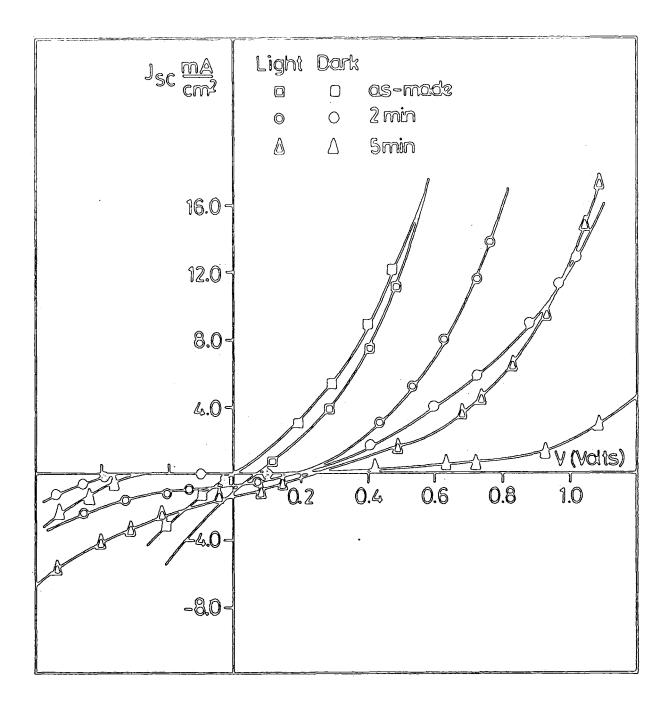

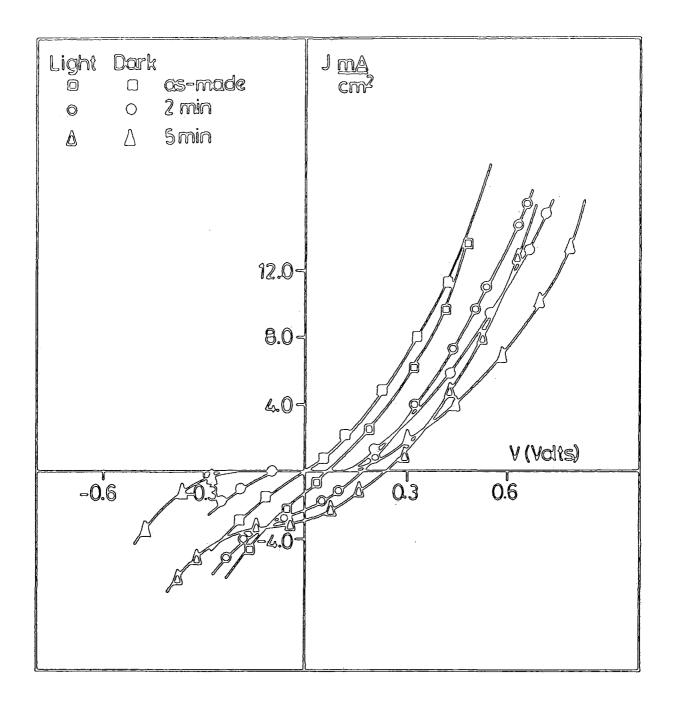

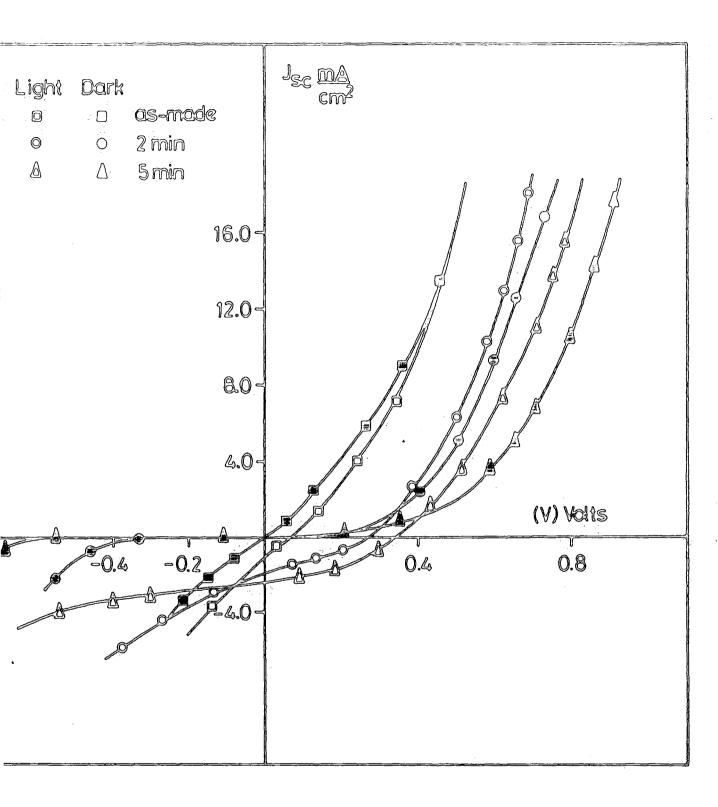

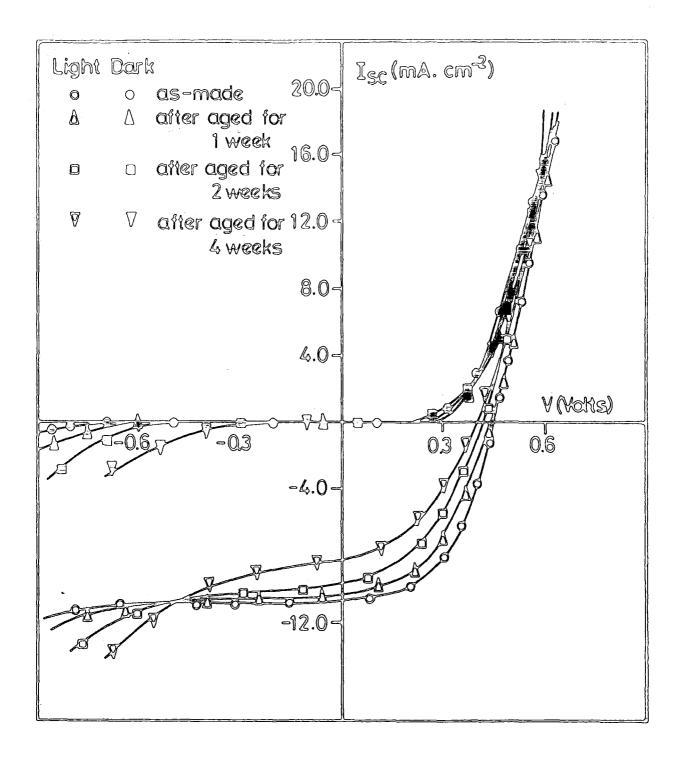

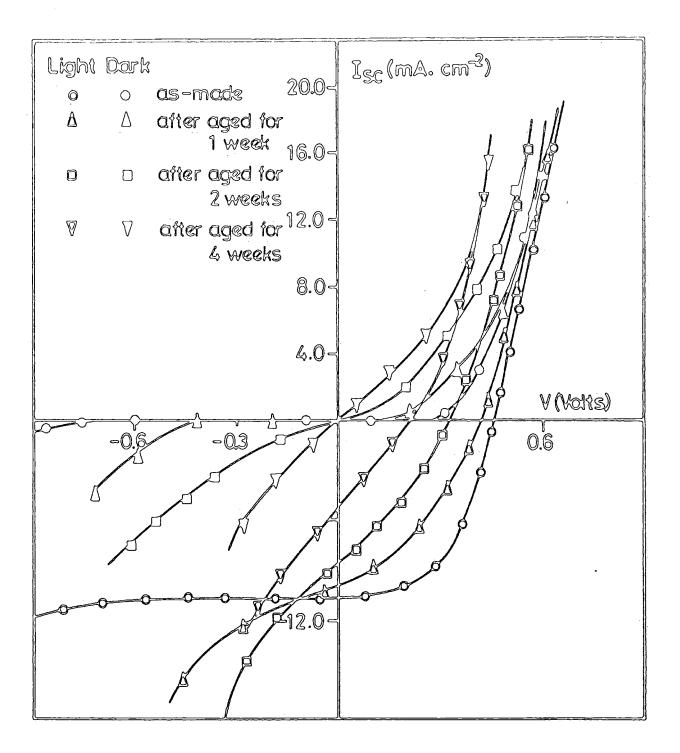

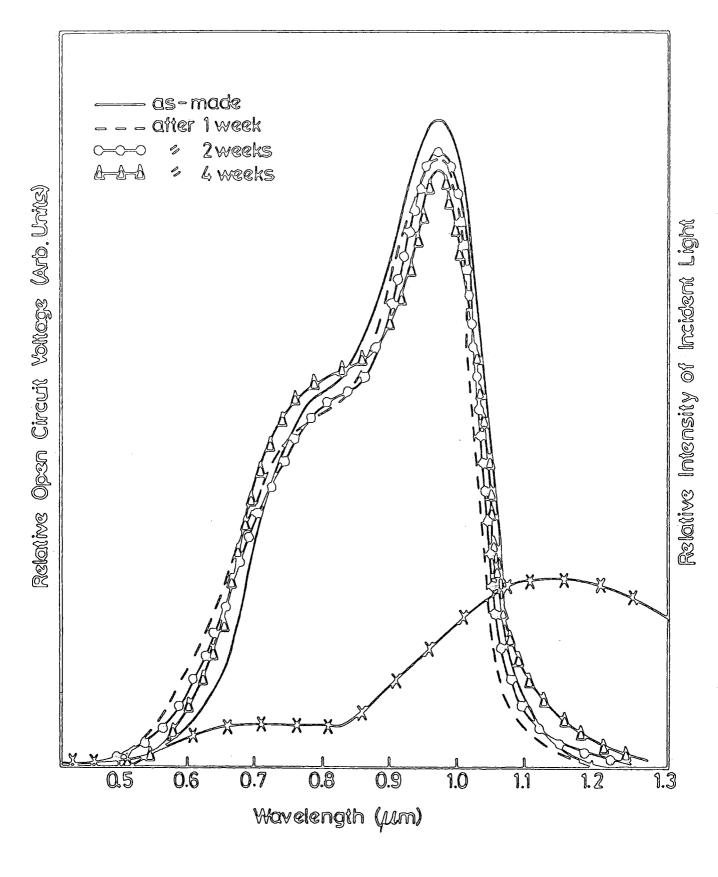

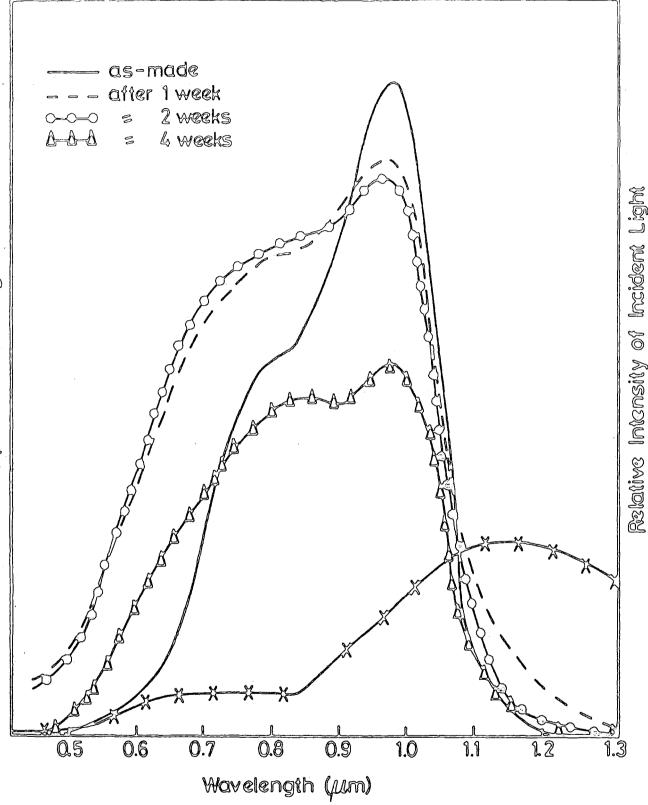

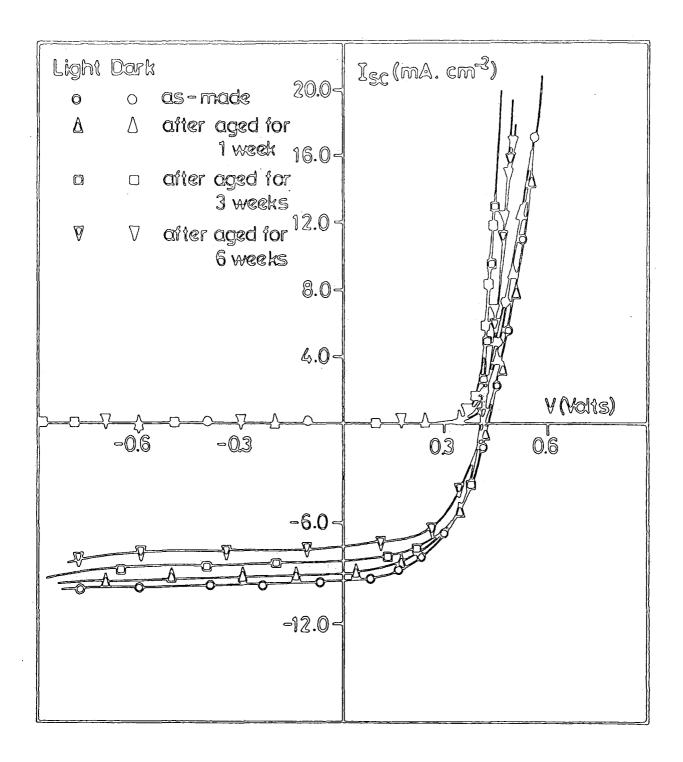

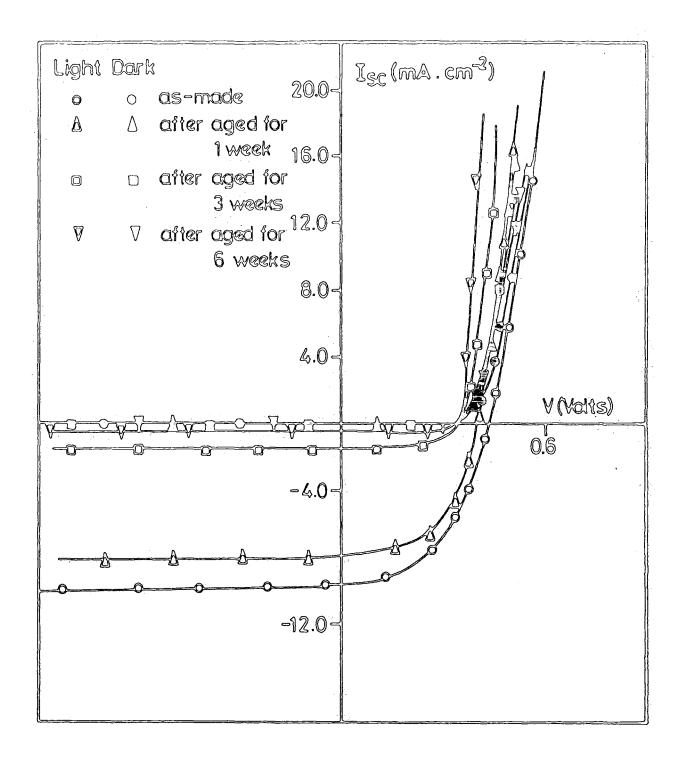

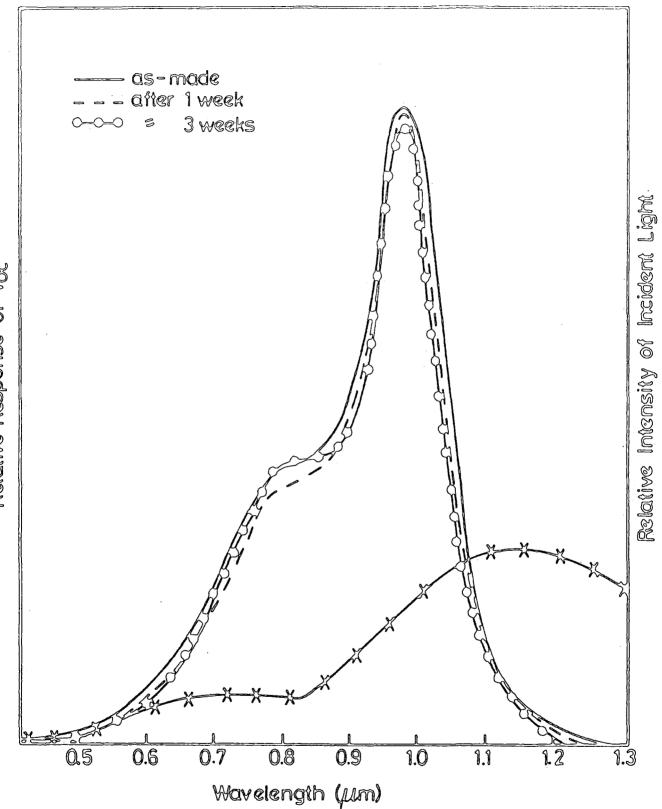

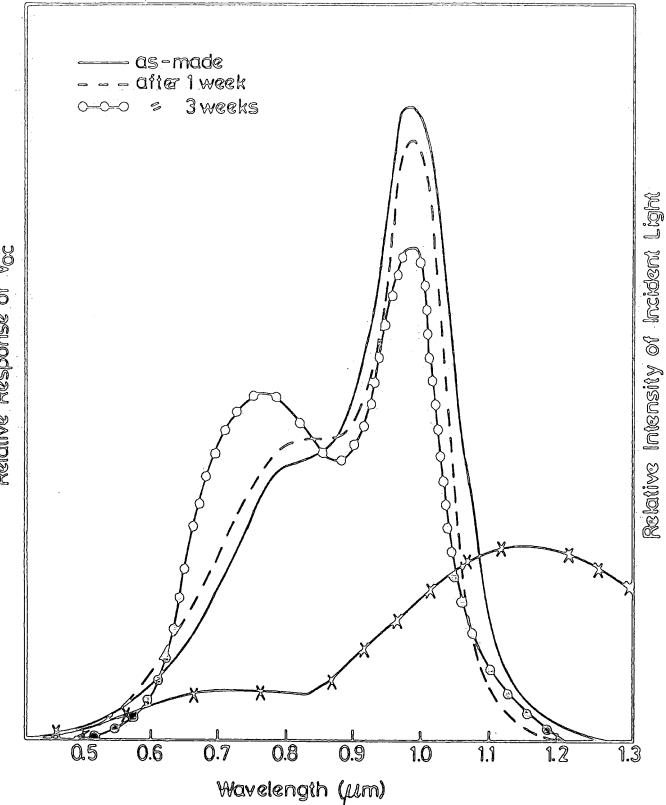

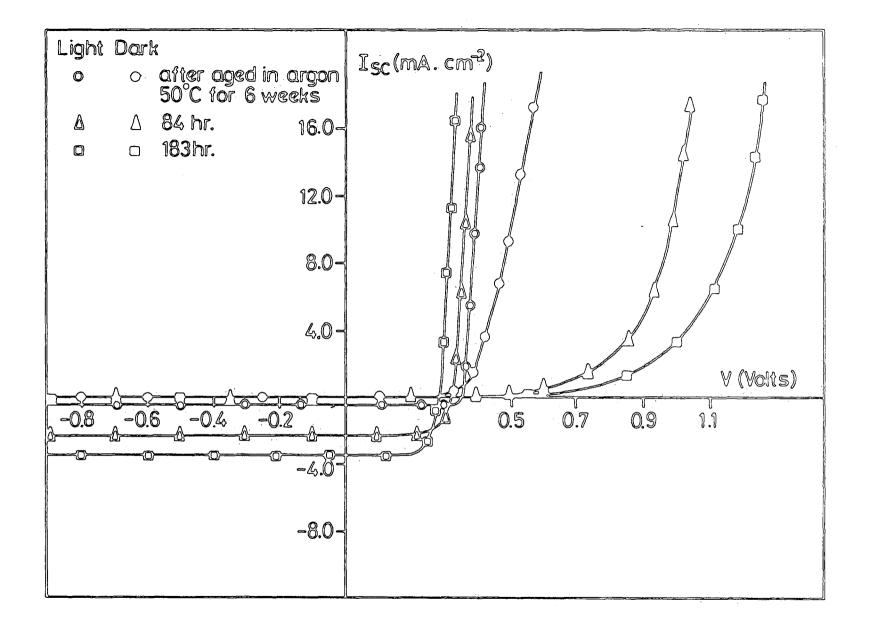

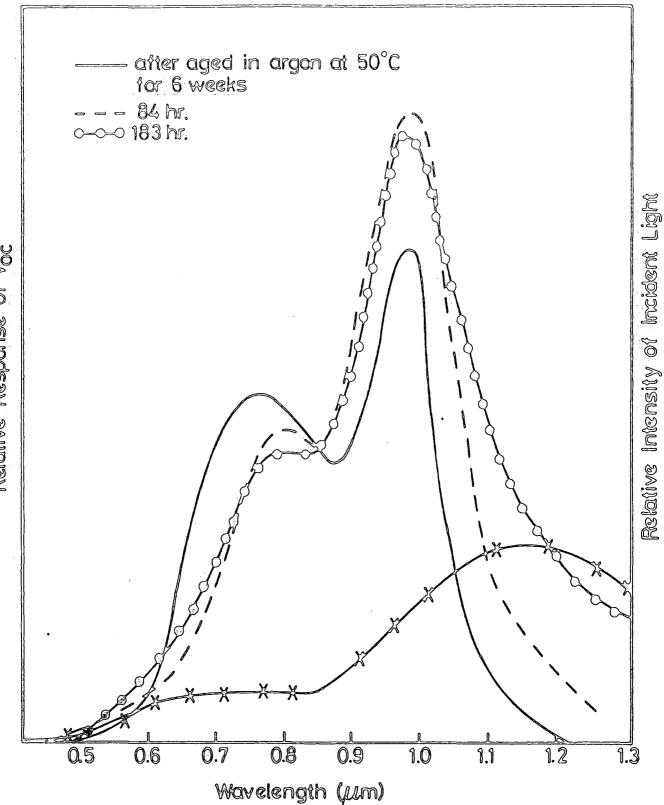

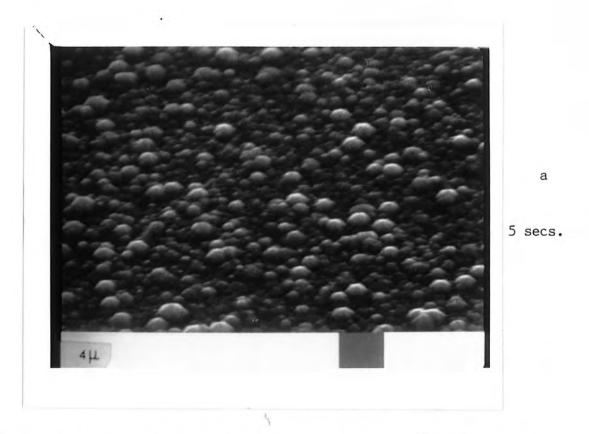

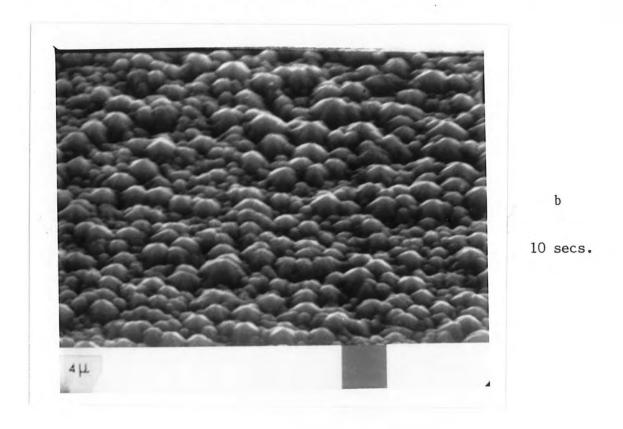

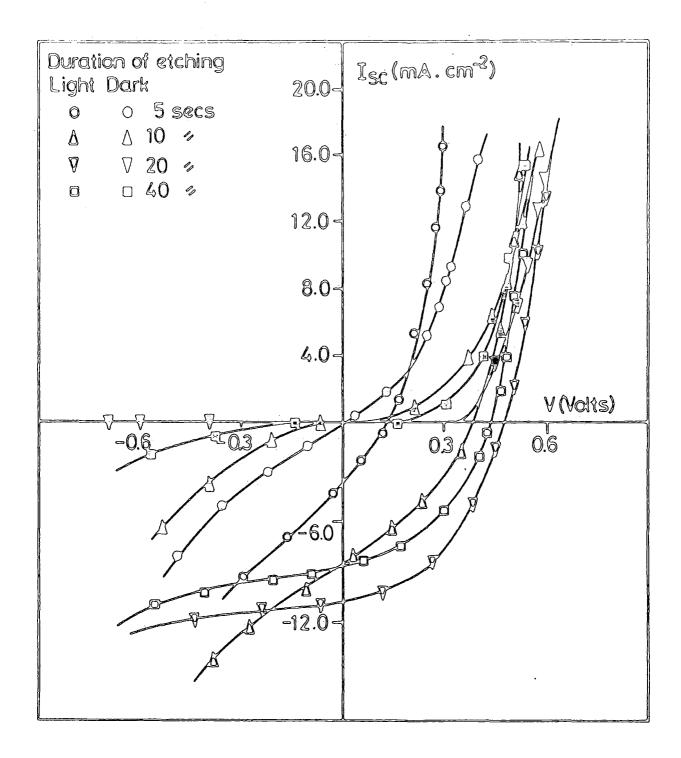

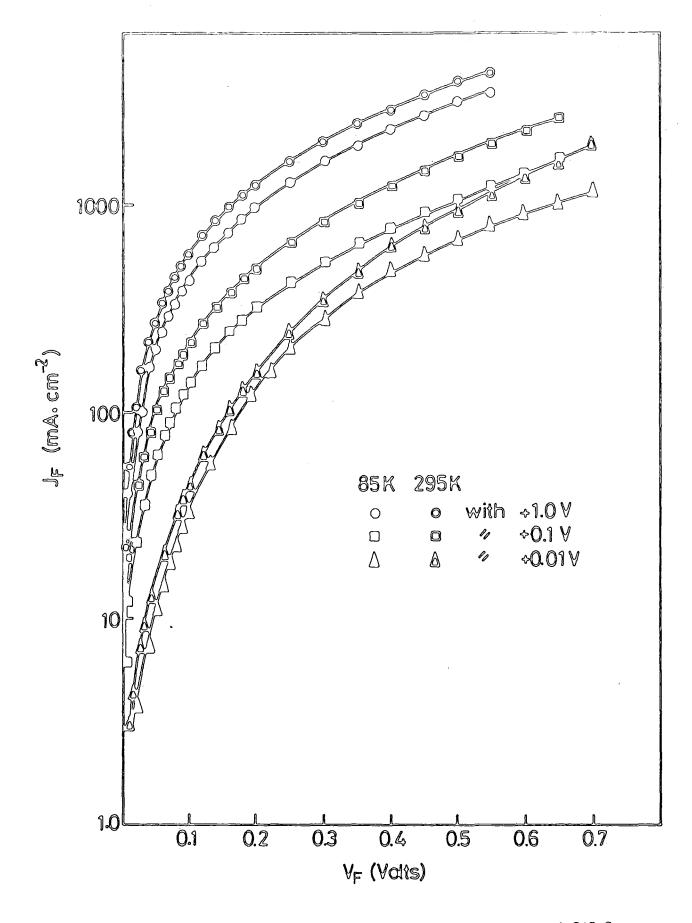

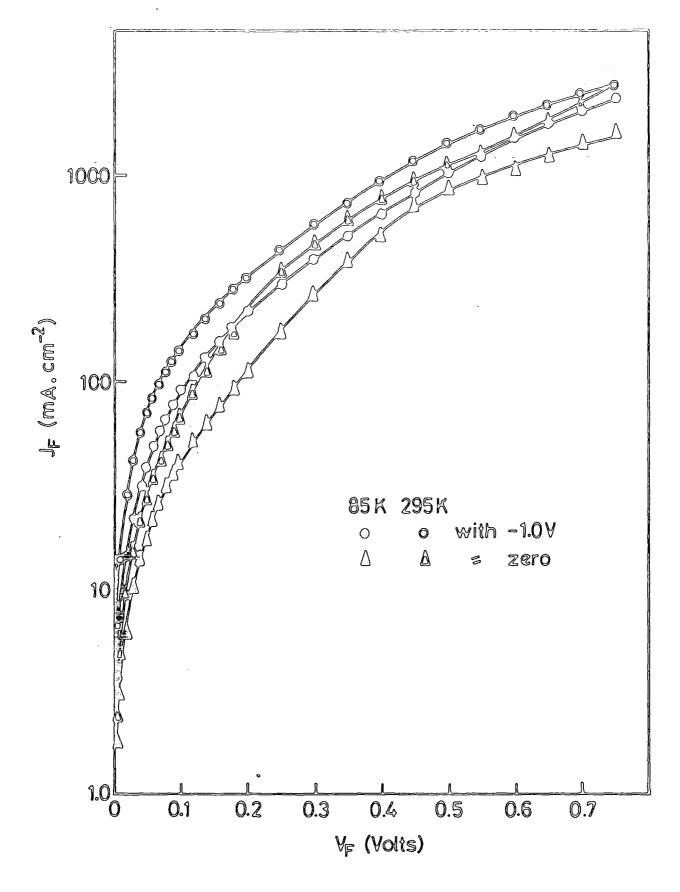

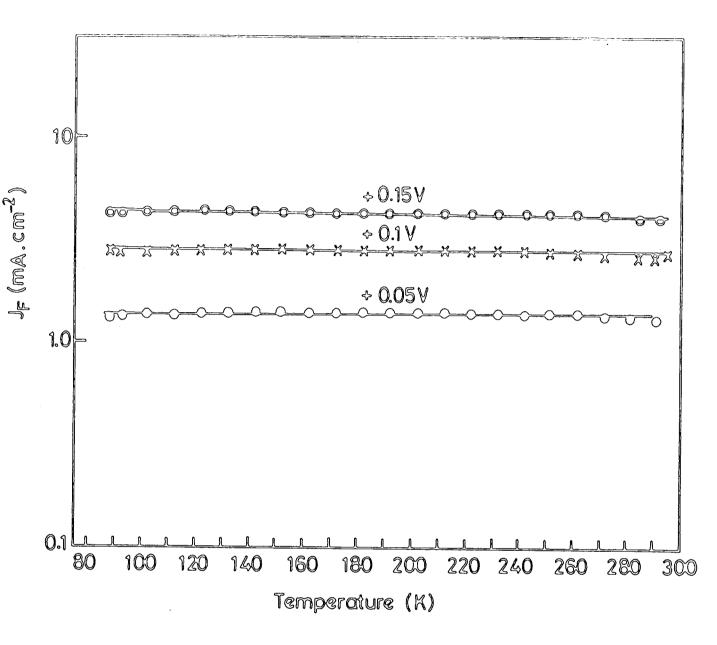

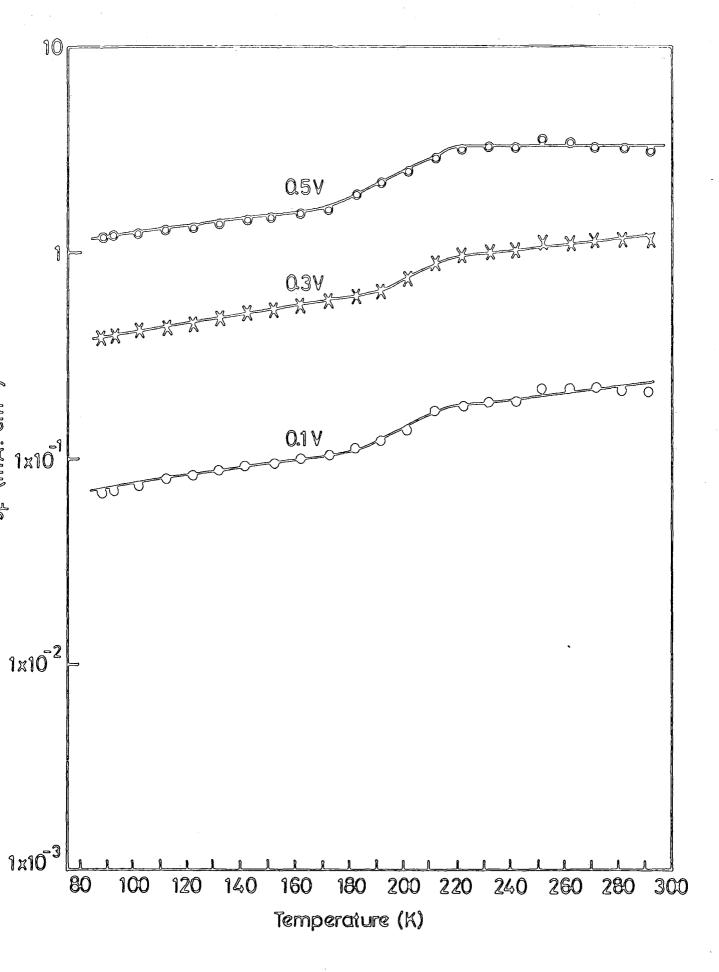

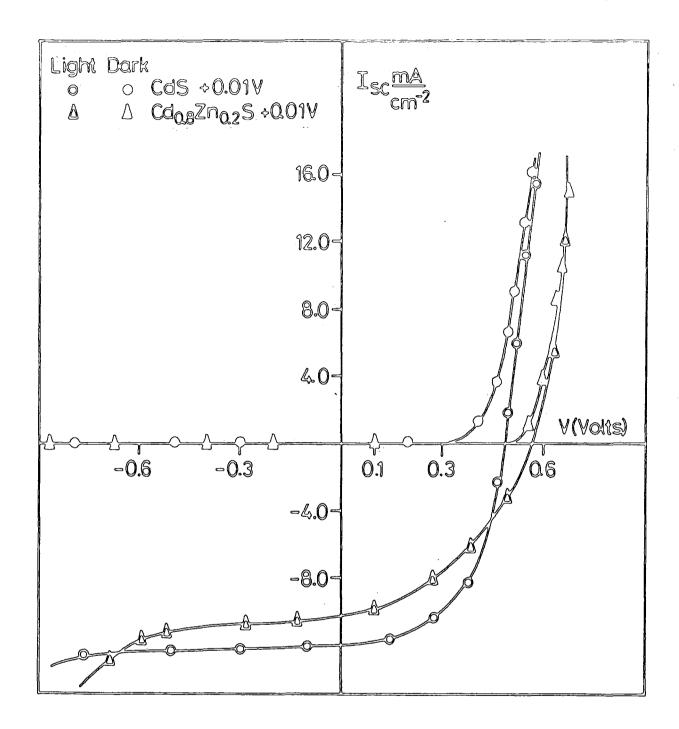

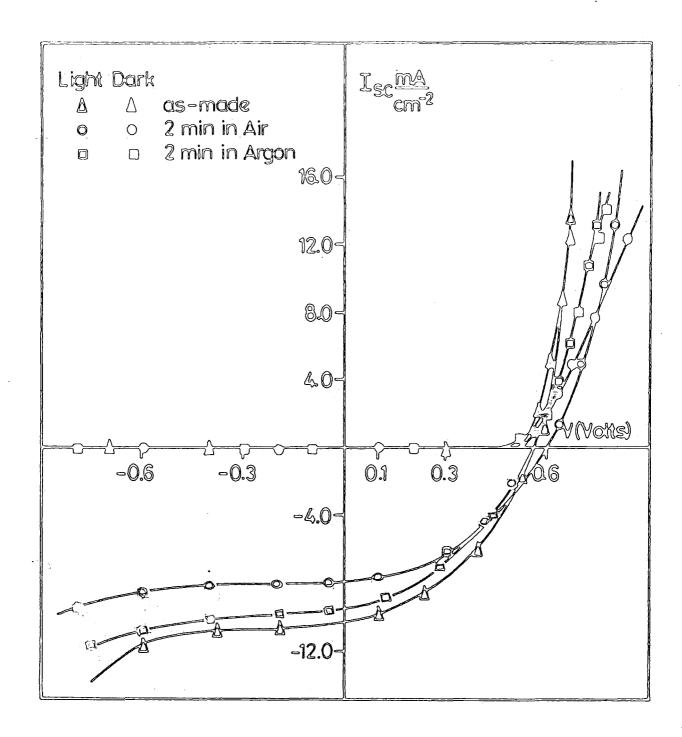

- 33 S.J.Fonash: "Solar Cell Device Physics" Academic Press, New York 1981.