# **Durham E-Theses**

# Modelling and analysis of crosstalk in scaled CMOS interconnects

Mahoney, Patrick Francis

How to cite:

Mahoney, Patrick Francis (1995) Modelling and analysis of crosstalk in scaled CMOS interconnects, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/5376/

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

Academic Support Office, The Palatine Centre, Durham University, Stockton Road, Durham, DH1 3LE e-mail: e-theses.admin@durham.ac.uk Tel: +44 0191 334 6107 http://etheses.dur.ac.uk

## Abstract

The development of a general coupled RLC interconnect model for simulating scaled bus structures in VLSI is presented. Several different methods for extracting submicron resistance, inductance and capacitance parameters are documented. Realistic scaling dimensions for deep submicron design rules are derived and used within the model. Deep submicron HSPICE device models are derived through the use of constant-voltage scaling theory on existing  $0.75\mu m$  and  $1.0\mu m$  models to create accurate interconnect bus drivers. This complete model is then used to analyse crosstalk noise and delay effects on multiple scaling levels to determine the dependence of crosstalk on scaling level. Using this data, layout techniques and processing methods are suggested to reduce crosstalk in systems

# Modelling and Analysis of Crosstalk in Scaled CMOS Interconnects

Volume 1 of 1

Patrick Francis Mahoney

Thesis for qualification for degree of Master of Science Durham University School of Engineering and Computer Science

Sept. 1995

The copyright of this thesis rests with the author. No quotation from it should be published without his prior written consent and information derived from it should be acknowledged.

# Table of Contents:

| 1. INTRODUCTION                                                                                                                                                                                | 6                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 1.1 History of Crosstalk Modelling                                                                                                                                                             | 7                           |

| 1.2 Organisation                                                                                                                                                                               | 9                           |

| 1.3 Simulation vs. Measurement                                                                                                                                                                 | 11                          |

| 1.4 Project Methodology                                                                                                                                                                        | 12                          |

| 2. ELECTRICAL MODELLING OF INTERCONNECTIONS                                                                                                                                                    | 14                          |

| 2.1 Introduction                                                                                                                                                                               | 14                          |

| 2.2 RC Line Model                                                                                                                                                                              | 14                          |

| 2.3 RLC Line Model                                                                                                                                                                             | 19                          |

| 2.4 Transmission Lines                                                                                                                                                                         | 21                          |

| 3. CAPACITANCE PARAMETER CALCULATION                                                                                                                                                           | 23                          |

| 3.1 Introduction                                                                                                                                                                               | 23                          |

| 3.2 Area and Perimeter Based Capacitance Calculation Techniques<br>3.2.1 The Lewis Technique for Coupled Interconnect Capacitance Calculation                                                  | 23<br>26                    |

| 3.3 Numerical Techniques for Capacitance Calculation                                                                                                                                           | 29                          |

| <ul> <li>3.4 Matthaei's Method for Coupled Interconnect Capacitance Calculation</li> <li>3.4.1 Introduction to Mattahei's method</li> <li>3.4.2 Implementation of Matthaei's Method</li> </ul> | 32<br>32<br>35              |

| 3.5 Implementation of Matthaei's Method in the Absence of a Reference Plane                                                                                                                    | 39                          |

| 3.6 Comparison of Accuracy for Calculation Methods                                                                                                                                             | 40                          |

| 4. INDUCTANCE AND RESISTANCE PARAMETER CALCULATION                                                                                                                                             | 44                          |

| 4.1 Introduction                                                                                                                                                                               | 44                          |

| 4.2 Inductance Parameter Calculation                                                                                                                                                           | 45                          |

| <ul> <li>4.3 Resistance Parameter Extraction</li> <li>4.3.1 DC Line Resistance</li> <li>4.3.2 AC Line Resistance</li> <li>4.3.3 Dielectric Loss</li> </ul>                                     | <b>48</b><br>48<br>49<br>51 |

| 5. INTERCONNECTION SCALING                                                                                                                                                                                                                                                                                                                                                                                                                           | 52                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                     | 52                               |

| 5.2 Ideal Scaling                                                                                                                                                                                                                                                                                                                                                                                                                                    | 53                               |

| 5.3 Quasi-Ideal Scaling and Other Methods                                                                                                                                                                                                                                                                                                                                                                                                            | 55                               |

| <ul> <li>5.4 Variation of Track Capacitance with Scaling</li> <li>5.4.1 Variation of Capacitance with Width</li> <li>5.4.2 Variation of Capacitance with Height</li> <li>5.4.3 Variation of Capacitance with Thickness</li> <li>5.4.4 Variation of Capacitance with Separation</li> <li>5.4.5 Conclusions on Scaling of Interconnect Capacitance</li> </ul>                                                                                          | 57<br>58<br>59<br>60<br>62<br>63 |

| 5.5 Scaled Track Geometries                                                                                                                                                                                                                                                                                                                                                                                                                          | 64                               |

| 6. TRANSISTOR SCALING AND MODELLING                                                                                                                                                                                                                                                                                                                                                                                                                  | 66                               |

| 6.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                     | 66                               |

| 6.2 Transistor Scaling                                                                                                                                                                                                                                                                                                                                                                                                                               | 67                               |

| 6.3 Transistor Scaling Theory                                                                                                                                                                                                                                                                                                                                                                                                                        | 68                               |

| <ul> <li>6.4 HSPICE Transistor Model</li> <li>6.4.1 History of SPICE</li> <li>6.4.2 Transistor Modelling Using HSPICE</li> <li>6.5 Comparison of Scaled Transistor Models</li> </ul>                                                                                                                                                                                                                                                                 | 70<br>70<br>72<br>75             |

| 7. CROSSTALK DELAY AND NOISE                                                                                                                                                                                                                                                                                                                                                                                                                         | 79                               |

| 7.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                     | 79                               |

| <ul> <li>7.2 Introduction to Crosstalk Noise</li> <li>7.2.1 Analysis of Crosstalk Noise on Parallel Lines in Scaled Bus Structures</li> <li>7.2.2 Analysis of Crosstalk Noise at Sampling Points along a Distributed Line</li> <li>7.2.3 Evaluation of the Contribution of Inductance to the Crosstalk Signal</li> <li>7.2.4 Effect of Temperature on Crosstalk Noise</li> <li>7.2.5 Analysis of Crosstalk Noise in Scaled Bus Structures</li> </ul> | 80<br>83<br>87<br>89<br>92<br>94 |

| 7.3 Introduction to Crosstalk Delay<br>7.3.1 Analysis of Crosstalk Delay in Scaled Bus Structures                                                                                                                                                                                                                                                                                                                                                    | 99<br>102                        |

| 7.4 Methods of Reducing Crosstalk                                                                                                                                                                                                                                                                                                                                                                                                                    | 105                              |

| 8. CONCLUSIONS                                                                                                                                                                                                                                                                                                                                                                                                                                       | 109                              |

| 8.1 Electrical Modelling of Interconnections                                                                                                                                                                                                                                                                                                                                                                                                         | 109                              |

| 8.2 Capacitance Parameter Calculation                                                                                                                                                                                                                                                                                                                                                                                                                | 109                              |

| 8.3 Inductance and Resistance Parameter Calculation | 110 |

|-----------------------------------------------------|-----|

| 8.4 Interconnection Scaling                         | 110 |

| 8.5 Transistor Scaling and Modelling                | 110 |

| 8.6 Crosstalk Delay and Noise                       | 110 |

## APPENDIX H: IMPLEMENTATION OF MATTHAEI'S METHOD IN PASCAL

# **Declaration:**

I declare that this work is completely my own, that it comes from no other outside source and that no portion of this work has previously been submitted for a degree in this or any other university.

# Statement of Copyright

The copyright of this thesis rests with the author. No quotation from it should be published without his prior written consent and information derived from it should be acknowledged.

# List of Tables and Figures:

| Fig. 2.1. A lumped RC model for interconnection.                                                                                                                                                                                       | 15    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Fig. 2.2. A distributed RC line model approximated as a cascade of $\pi$ -sections.                                                                                                                                                    | 16    |

| Fig. 2.3. Transient Response of lumped and distributed RC models.                                                                                                                                                                      | 18    |

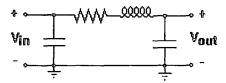

| Fig. 2.4. Circuit used to model 0.35µm inverter driving an RLC line model.                                                                                                                                                             | 20    |

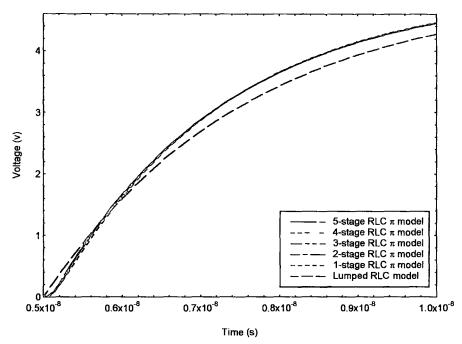

| Fig. 2.5. Transient Response of lumped and distributed RLC models.                                                                                                                                                                     | 21    |

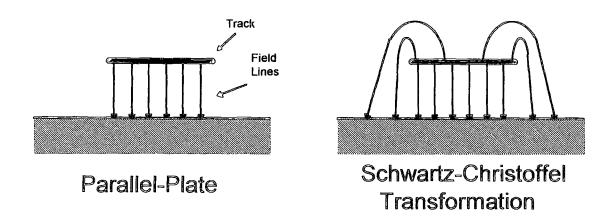

| Fig. 3.1. Comparison of field lines for parallel-plate and Schwartz-Chistoffel transformation methods of calculating capacitance.                                                                                                      | 25    |

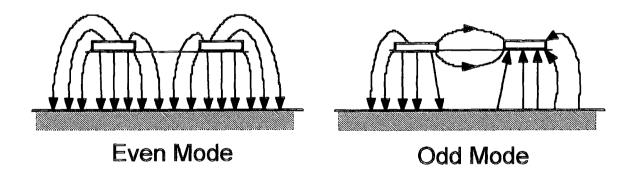

| Fig. 3.2. Even and odd mode field line configurations in coupled microstrip lines.                                                                                                                                                     | 26    |

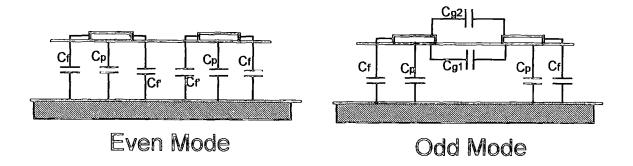

| Fig. 3.3. Even and odd mode capacitance models.                                                                                                                                                                                        | 27    |

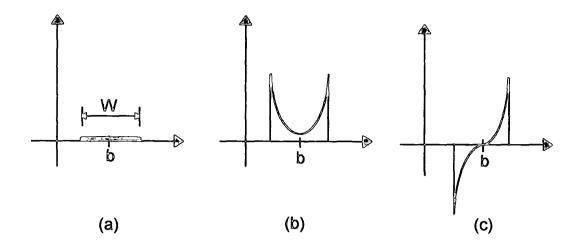

| Fig. 3.4. (a) A two dimensional metal strip that extends into and out of the paper. (b) An even charge basis function for a fixed charge along the length of the strip. (c) The corresponding odd charge basis function. <sup>15</sup> | 34    |

| Fig. 3.5. Pseudo-code description of Matthaei's method for capacitance parameter extraction.                                                                                                                                           | 39    |

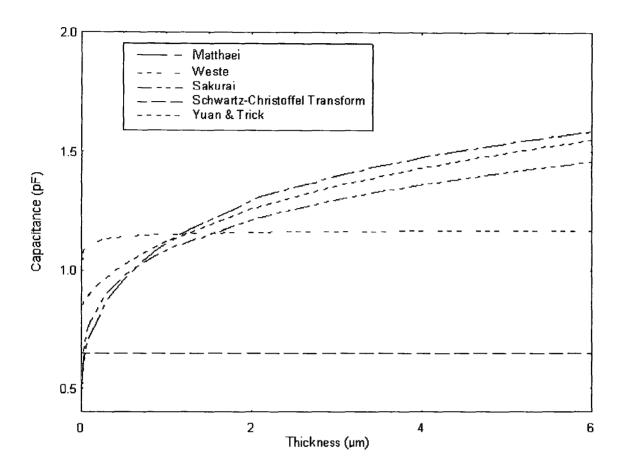

| Fig.3.6. A comparison of the results from multiple methods for extracting interconnect capacitance                                                                                                                                     | ce.41 |

| Fig. 3.7. Comparison of total line capacitance using different techniques.                                                                                                                                                             | 43    |

| Fig. 4.1. Basic RLC line model.                                                                                                                                                                                                        | 44    |

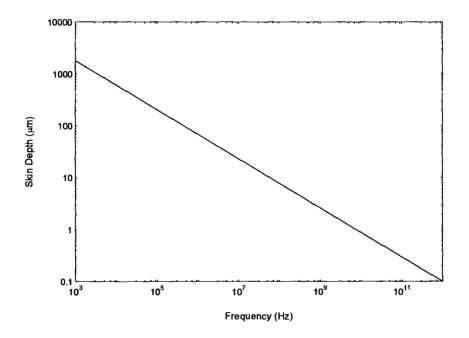

| Fig. 4.2. Skin depth as a function of frequency for aluminium at room temperature.                                                                                                                                                     | 50    |

| Fig. 5.1. Scaling of Global Interconnections.                                                                                                                                                                                          | 54    |

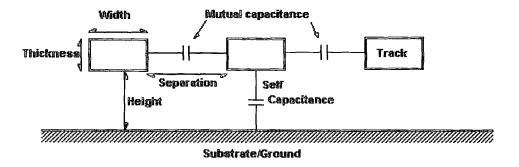

| Fig. 5.2. Explanation of the terms used in the graphs in this section.                                                                                                                                                                 | 58    |

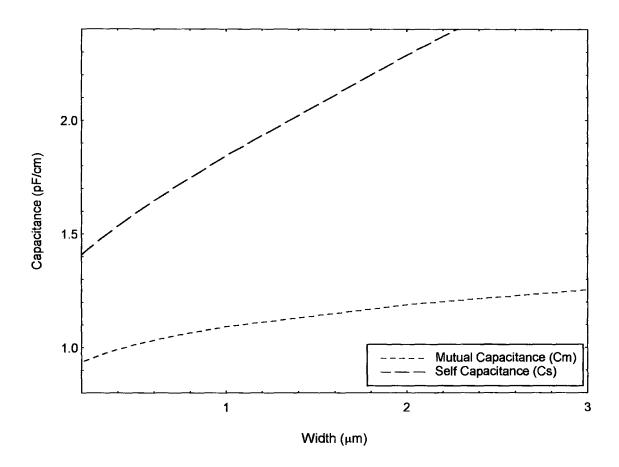

| Fig.5.3. Variation of Self and Mutual Capacitance with Interconnect Width.                                                                                                                                                             | 59    |

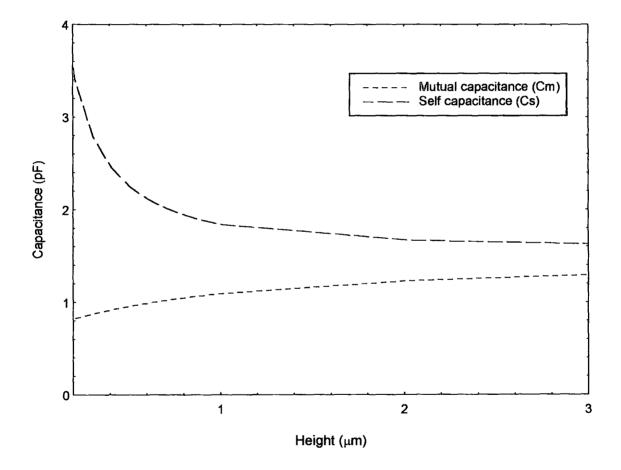

| Fig.5.4: Variation of Self and Mutual Capacitance with Height (substrate thickness).                                                                                                                                                   | 60    |

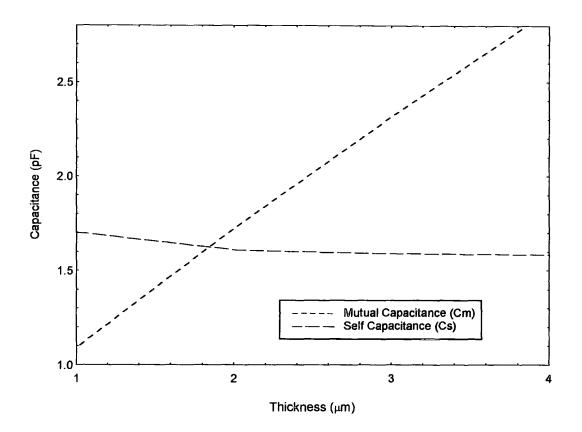

| Fig.5.5. Variation of self and mutual capacitance with thickness.                                                                                                                                                                      | 62    |

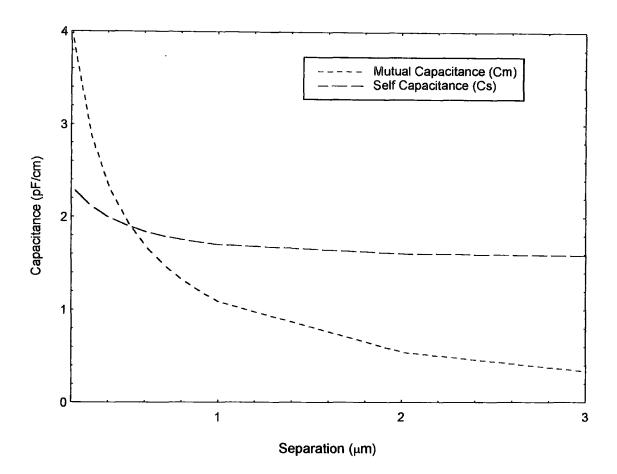

| Fig.5.6. Variation of self and mutual capacitance with separation.                                                                                                                                                                     | 63    |

| Fig. 5.7. Table showing the physical dimensions of track parameters at different scaling levels.                                                                                                                                       | 65    |

| Fig.6.1. Influence of different MOS-device scaling models.                                                                                                                                                                             | 69    |

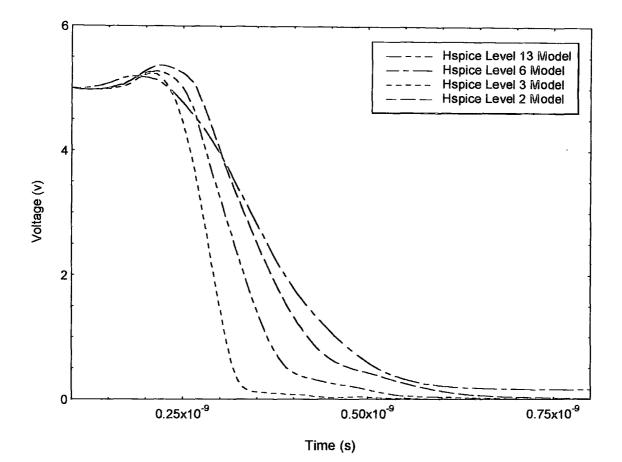

| Fig.6.2. Comparison of HSPICE process models for the falling transition of a $0.50\mu m$ inverter .                                                                                                                                    | 74    |

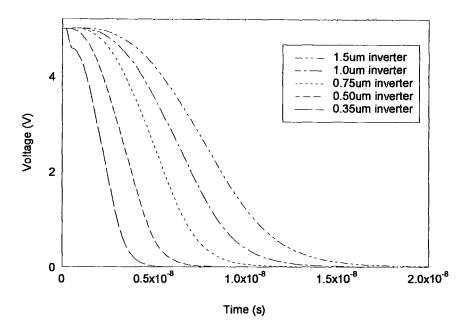

| Fig.6.3. Comparison of the transition times of scaled transistors.                                                                                                                                                                     | 76    |

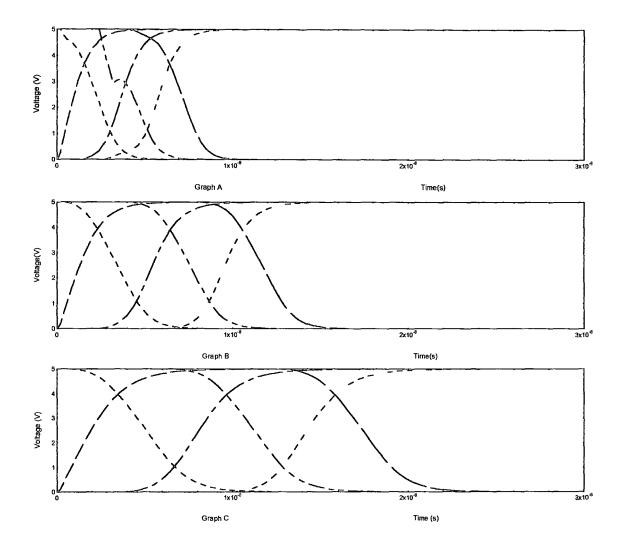

| Fig.6.4. Comparison of the switching speeds for a chain of scaled inverters. Graph A. shows a $0.35 \mu m$ inverter chain, while graphs B. and C. shows the switching of $0.50 \mu m$ and $0.75 \mu m$ device respectively. | ces<br>77    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

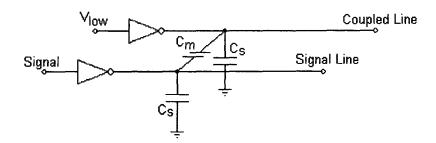

| Fig. 7.1 Simple example of crosstalk coupling on a 2-bit signal bus.                                                                                                                                                        | 80           |

|                                                                                                                                                                                                                             | 80           |

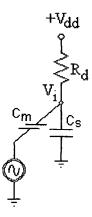

| Fig. 7.2: A simplified representation of the circuit in fig. 7.1 while the signal line inverter is switching.                                                                                                               | 81           |

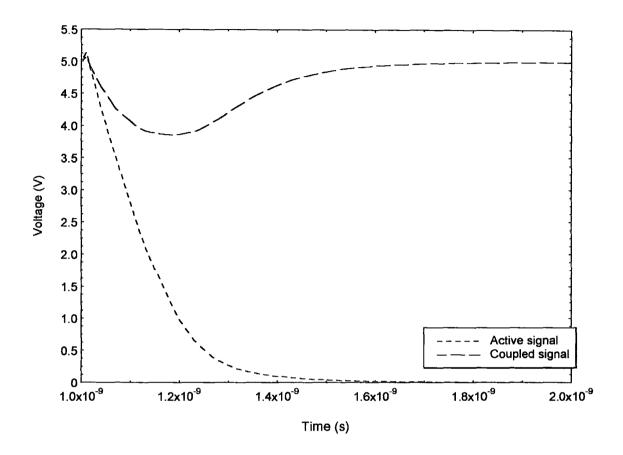

| Fig. 7.3: Graph illustrating signal coupling between an active and an inactive line.                                                                                                                                        | 82           |

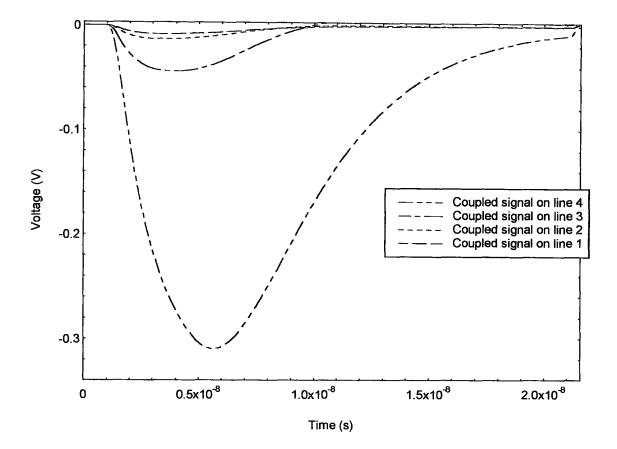

| Fig. 7.4. Coupled crosstalk signal on each signal line in an 9 bit bus.                                                                                                                                                     | 84           |

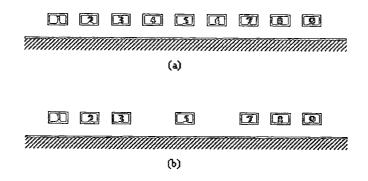

| Fig. 7.5. Illustration of the nine bit bus. (a) the complete nine bit bus, and (b), with two conduct removed.                                                                                                               | tors<br>86   |

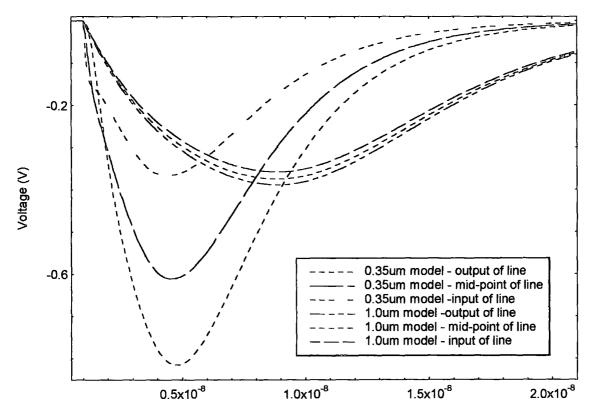

| Fig.7.6. Comparison of the coupled voltage at various point along a line at different scaling leve                                                                                                                          | els.88       |

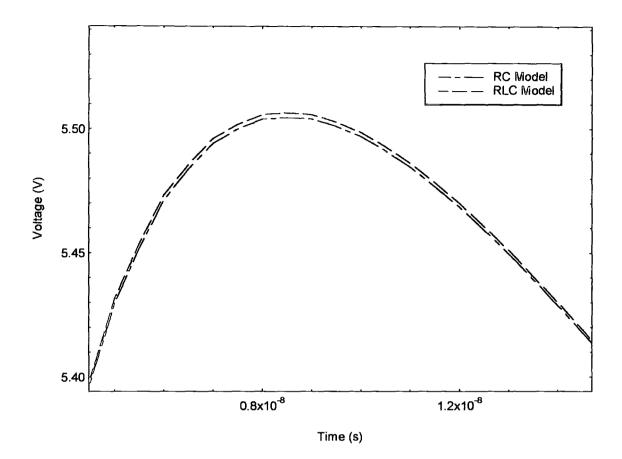

| Fig. 7.7. Comparison crosstalk signal noise for RC and RLC line models on a 0.35µm process.                                                                                                                                 | 90           |

| Fig.7.8. Comparison of the output slope of an interconnect of RC and RLC line models                                                                                                                                        | 91           |

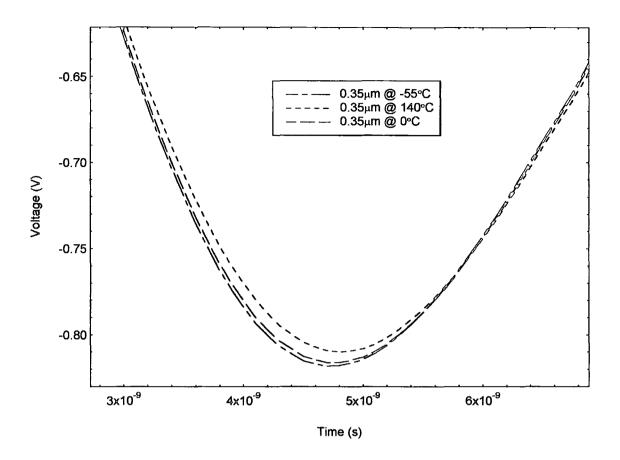

| Fig. 7.9 Comparison of coupled crosstalk voltage against simulation temperature                                                                                                                                             | 93           |

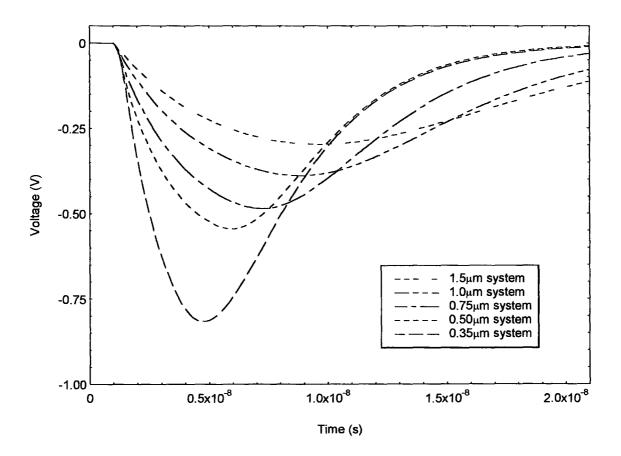

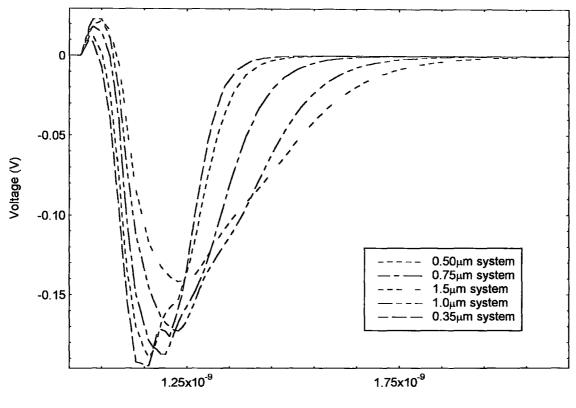

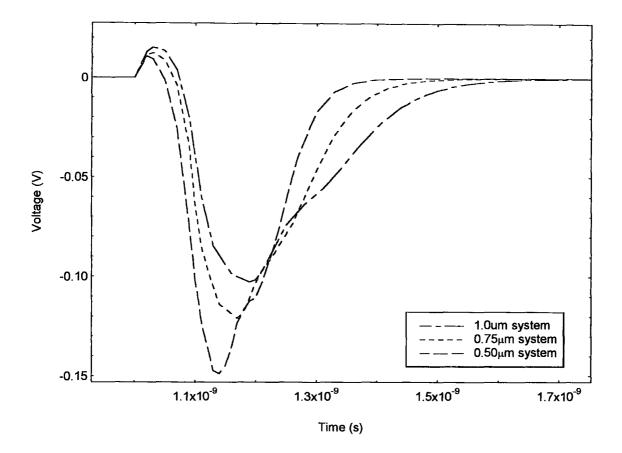

| Fig. 7.10. Comparison of crosstalk noise against scaling for a 1cm long 8-bit bus.                                                                                                                                          | 95           |

| Fig. 7.11. Table summarising key features in the graph in figure 7.12.                                                                                                                                                      | 96           |

| Fig. 7.12. Comparison of crosstalk noise against scaling for a 100µm long 8-bit bus.                                                                                                                                        | 97           |

| Fig. 7.13. Comparison of crosstalk noise against scaling for a 10µm long 8-bit bus.                                                                                                                                         | 98           |

| Fig. 7.14 Illustration of crosstalk delay.                                                                                                                                                                                  | 100          |

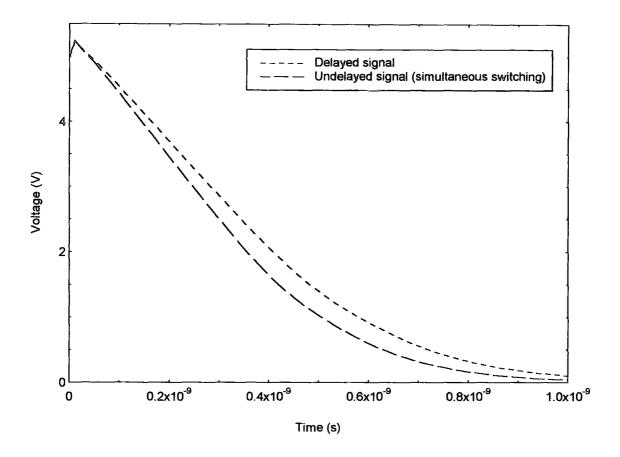

| Fig. 7.15. Example of crosstalk delay showing difference in the slopes between the delayed and undelayed signals.                                                                                                           | 101          |

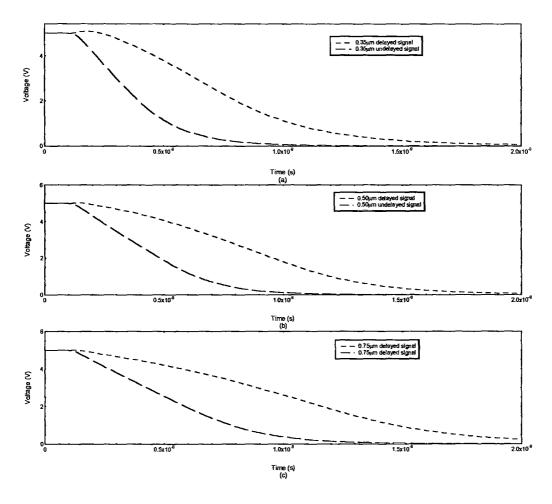

| Fig. 7.16. Comparison of crosstalk delay against scaling for a 1cm long 8-bit bus for three proces (a.) $0.35\mu m$ , (b.) $0.50\mu m$ and (c.) $0.75\mu m$ .                                                               | sses:<br>104 |

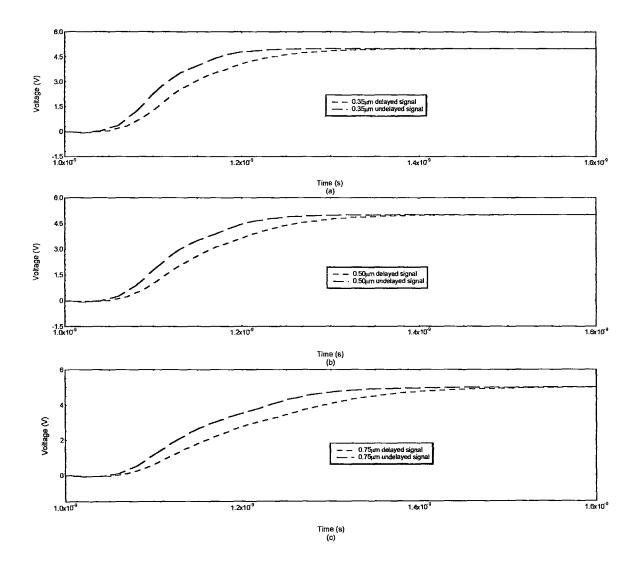

| Fig.7.17. Comparison of crosstalk delay against scaling for a $100\mu m \log 8$ -bit bus for three processes: (a.) $0.35\mu m$ , (b.) $0.50\mu m$ and (c.) $0.75\mu m$ .                                                    | 104          |

| Fig.7.18. Summary of 50% crosstalk delay measurements and percentage margin that crosstalk c is to slope for different interconnect scaling and length values.                                                              | lelay<br>105 |

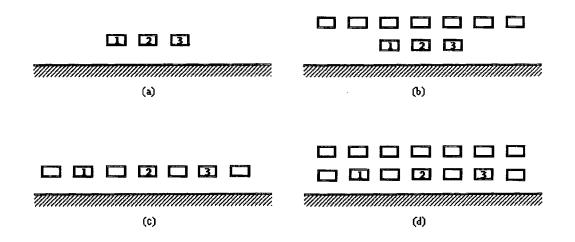

| Fig. 7.19. Different layout techniques that can be used to reduce crosstalk effects: (a) normal 3-                                                                                                                          | bit          |

| bus, (b) stripline configuration, (c) shielded interconnects, and (d) shielded stripline (pseudo-<br>coaxial) configuration.                                                                                                | 106          |

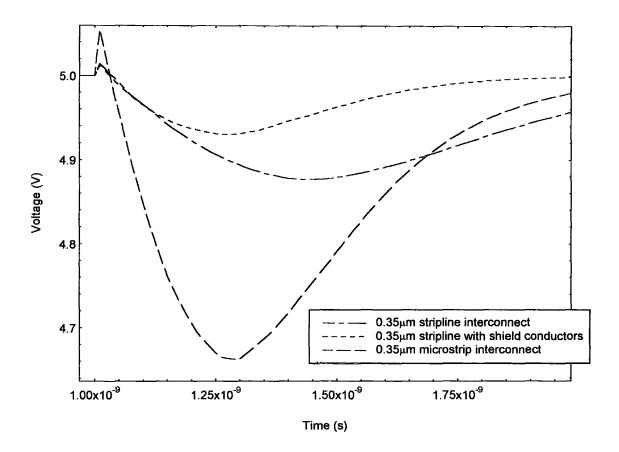

| Fig.7.20. Comparison of layout techniques used to reduce crosstalk effects.                                                                                                                                                 | 107          |

## 1. Introduction

For VLSI and ULSI chip design, interconnections have a greater importance than in earlier technologies. Today, a chip no longer contains a single circuit, but may contain a large part of an entire system - for example, an entire computer on a chip. For such complex designs, there is less flexibility available to the engineer than in the design of simple circuits and this results in interconnections that are more than just the nuisance level of added delay, additional power consumption and higher noise. The layout of interconnections can change the entire architecture and operation of a VLSI system Thus, the designer requires accurate methods for modelling interconnections in order to optimise the design of a modern chip.

Additionally, the scaling of devices and interconnect dimensions in VLSI has resulted in interconnections playing a more pervasive and dominating role in circuit performance. As CMOS device dimensions have been reduced resulting in devices with faster transition times, the RC delay associated with the interconnections between these devices has increasingly begun to dominate overall circuit performance. In addition, analogue signal effects such as crosstalk are a concern as they can lead to delay and logic hazards. Dynamic circuitry which is useful in high performance circuit is particularly susceptible to crosstalk logic errors.

A poor understanding of crosstalk can lead to overly conservative design rules resulting in poor performance, or it can lead to sporadic logic errors which may only be triggered by certain logic combinations and may be difficult to detect. Thus an accurate simulation model is essential for efficient and reliable circuit designs. This paper presents a general method for the creation of scaleable model for coupled lossy transmission bus structures. This model is then used to derive general trends in crosstalk as designs are scaled in the submicron region.

#### 1.1 History of Crosstalk Modelling

Crosstalk noise in high-frequency designs is not a recent effect. It has been welldocumented in microwave and RF literature for decades. The results for microstrip lines documented in these papers do not directly apply to CMOS because they consider very thin "lossless" lines (negligible resistance) and older studies neglected the thickness of the tracks. Investigation into crosstalk for integrated circuit design began with several papers within a few years of each other describing crosstalk in ECL and TTL logic circuits<sup>1,2,3</sup>. In all of these papers, the coupling of signals between two parallel lossless conductors were considered and the solution to the problem of terminating lines was considered. The main limitation of these papers with respect to CMOS circuits is that they consider lines with a negligible resistance only. The resistance of the metal and polysilicon tracks in a CMOS system, however, is significant and this resistance plays a significant role in crosstalk coupling.

The effects of crosstalk on coupled "lossy" (significant resistance) interconnections in a thin-film package were studied by Isaac and Strakhov<sup>4</sup>. In this paper, a general analytical model for coupled transmission lines is presented, but little consideration is made as to the driving devices and the model is not directly applicable to CMOS structures due to the parameterisation scheme. An analysis of wafer-scale transmission lines using weakly-coupled slightly-lossy interconnections was made by Kim and McDonald<sup>12</sup> and simulations and measurements of interconnections on tape automated bonding packages was made by Su, Raid, Elshabini-Raid and Poulin<sup>5</sup>. Similar to the work by Isaac and Strakhov, the analysis in these papers only considers the general case of two parallel interconnections. Although all three of these papers provide a detailed analysis of delay and crosstalk in parallel transmission lines, they both require extensive computer calculation which is impractical in VLSI systems with thousands or millions of interconnections to be considered.

More recent work has focused on methods which are more computationally efficient to speed up crosstalk and delay analysis in VLSI and ULSI systems. One new technique developed by Pillage and Rohrer<sup>6</sup>, referred to as the asymptotic waveform evaluation (AWE) technique, approximates the waveform response of general linear circuits using a lumped model. This technique was adapted for use in estimating the response of linear lossy coupled transmission lines by Tang and Nakhla<sup>7</sup>. One further adaptation was proposed by Xie and Nakhla to allow the method to deal with non-linear terminations. The advantage of the AWE technique over the more exacting analysis of the methods described in the previous paragraph, is that it is comparatively much faster, although it is also less accurate.

While the AWE technique is useful for approximate evaluation of large networks of interconnections at lower frequencies and exact transmission line solutions are useful for understanding the coupling mechanism in detail at high frequencies, a more general method of examining the crosstalk response of an interconnection network is through the use of existing circuit simulation software (such as SPICE) with accurate interconnect models. Although simulation with SPICE is more time consuming than other methods such the AWE technique, it is the most commonly used method of simulating complex models and has the most complete models for devices.

One SPICE model proposed by Tripathi and Rettig approximates the response of a multiple coupled system of lossless interconnects using a system of uncoupled lines and linear dependent current and voltages sources<sup>8</sup>. This model was later adapted by Tripathi and Bucolo<sup>9</sup> to model multi-level parallel and crossing lossy coupled interconnections and by Papaioannou, Dimopoulos and Avarisiotis<sup>10</sup> for simulation of off-chip interconnections. Other models, such as that described by Chang, Chang, Oh and Lee<sup>11</sup> use SPICE subcircuits and macros to create complex general models which can be adjusted for different conditions.

The most serious deficiency of all of these models, with the possible exception of the model suggested by Chang<sup>11</sup>, is that they only use limited approximations for the devices driving the interconnect lines. Since the device characteristics have a serious impact on the crosstalk signal, these imprecise models for the devices can result in large inaccuracies. In addition, none of these methods have detailed the complete model including the modelling of the devices and the extraction of the interconnect characteristic parameters. The model used in this project uses an distributed RLC model and includes accurate models for the device drivers.

#### 1.2 Organisation

This first chapter introduces the concepts used in the paper and establishes the importance of this investigation. Prior work in the subject areas of interconnect modelling, parameter extraction, scaling and crosstalk and delay modelling are also mentioned. Although each of the sections will later mention previous work in the field in more detail, looking at what has already been done is a logical way to begin to present the subject of this thesis.

Chapter two examines various line models that can be used to represent an interconnect line by starting with the simplest model and eventually expanding to more complex models that more accurately describe the behaviour of interconnects under different drivers and signal inputs. A comparison of the accuracy and complexity of each of these models is then presented with a detailed description of the interconnect model used.

The third chapter analyses different methods of extracting capacitance parameter information from a physical layout. It starts with an examination of the simplest methods and adds greater complexity while increasing the accuracy of the method. The method used to compute capacitance for the project is then presented and compares the accuracy and the simulation time of this method against other algorithms that have been detailed in academic literature.

The methods used to calculate resistance and inductance parameters are examined in the fourth chapter. A description of the method used to calculate inductance from the capacitance matrix derived through the use of one of the methods described in the third chapter is presented. An explanation of the method used to determine the resistance of a track from physical dimensions and a discussion and evaluation of the contribution of each of the components of the overall track resistance is made.

In the fifth chapter, the scaling of interconnect physical dimensions is considered. The theories of ideal and quasi-ideal scaling are explained and the problems with each method are presented. A series of graphs showing the variation of self and mutual capacitance with changes in physical dimensions are shown and conclusions are made regarding the dependence of the two components of capacitance on geometry. Finally a summary of the scaled interconnect dimensions used in simulations at each certain process are given.

The sixth chapter looks at modelling and scaling of the MOSFET devices used to drive the interconnections. The theory of CMOS device scaling is explained and the advantages and difficulties with scaling are analysed. The history and the capabilities of the circuit simulation package are described and the method used to create the models used in the simulation is illustrated. Finally, a comparison of the models under loaded and unloaded conditions is presented to evaluate the speed switching improvement with scaling.

The results of the crosstalk delay simulations are presented in the seventh chapter. An example of crosstalk noise is described and the dependencies of crosstalk on certain circuit parameters is established. Crosstalk noise on parallel tracks in a bus is analysed for changes in temperature, scaling, and length. The peak crosstalk voltages at different points along a distributed interconnect are compared and the concept of shielding interconnects with other tracks is introduced. The concept of crosstalk delay in a bus and

the problems that it may lead to in the design of synchronous circuits is presented and described through the use of an example. The results of simulations showing the variation of crosstalk delay with scaling are presented. Lastly, methods that can be used to reduce crosstalk delay are described and evaluated.

Conclusions are made on the each of the results described and a final summary is made of the project is made in chapter eight. An appendix follows which lists the PASCAL computer program used to determine the resistance, inductance and capacitive components from the line geometries

#### 1.3 Simulation vs. Measurement

The primary goal of the project is to analyse the effect that scaling of interconnections and devices has on the immunity of circuits to crosstalk noise. The most obvious method of performing this task would be to construct multiple scaled structures using a variety of scaled devices, interconnection layouts, and input waveforms to determine worst case conditions and inputs, analyse the data gathered and present conclusions on the significance of the problem and strategies that can be used to overcome these obstacles.

A small fraction of the previous research examining the effect of crosstalk on silicon systems have used methods similar to this<sup>5,12</sup>, but the majority have used circuit models that simulate the effect of crosstalk rather than physically measuring it. This is primarily for four reasons:

• Cost: The cost required to fabricate the devices with the number of variables that often need to be considered can make the cost of manufacturing the test structures prohibitive in terms of time and money. This becomes especially true when the systems under investigation are still in the developmental stage and have limited availability outside of the companies developing them.

- Accuracy: Accurate measurement of the exact region that is desired can be difficult using a physical construction. For example, to measure the crosstalk of an on-chip interconnect, signal noise from other sources such as from coupling at the pins and in the probe wires must be considered and compensated for.

- Speed: In terms of the total time required by a project, it is much faster to develop and construct a model of a complex integrated circuit using existing simulation software than it is to actually design and fabricate the physical device.

- Flexibility: Once a model is constructed, it is easier to adjust the physical parameters of that model (for example, the wiring resistance) in a simulation than to manufacture a new device. In addition, in a simulation varying a physical parameter such as the thickness of a wire at small intervals requires only a minor adjustment to the simulation whereas on a physical system this would require the manufacturing of multiple devices.

Based on these reasons a simulation method was chosen over construction of multiple systems and the physical measurements of circuit characteristics.

#### 1.4 Project Methodology

The project was divided into sections which appear in this paper as chapters. Each of these sections had an exact goal and in this paper each chapter concludes with a summary of results obtained. Every section added built upon the results of the last to create the complete model which was then used in simulations to acquire the crosstalk results. The sections are:

- Determination of an accurate, computationally efficient model for an RLC line model.

- Determination of an accurate and efficient method for the calculation of the capacitance parameters for the RLC model.

- Evaluation of a method for the efficient calculation of the inductance and resistance parameters for the RLC model.

- Determination of scaling dimensions for the interconnections.

- Creation of accurate device models for each of the scaling levels.

- Simulation of the complete model at each of the scaling levels to evaluate crosstalk noise and delay

# 2. Electrical Modelling of Interconnections

#### 2.1 Introduction

The simplest model for a wire or an integrated circuit track is a short circuit in which the wire has no resistance or capacitance and thus adds no delay to the circuit. In an integrated circuit, this model is only a reasonable estimate when the device resistance and capacitance completely dominate over the wire resistance and capacitance and when the switching time of the driving device is slow. Only in the earliest days of integrated circuit design was this the case.

When the device delay is much larger than the RC delay<sup>\*</sup> of the line, but the capacitance of the interconnect line is significant in regards to power consumption and device switching delay, then the line may be modelled as a lumped capacitor. In this case, the finite resistance of the line must be negligible compared to the transistor resistance when the device is in saturation mode. This model was used in earlier process technologies, but more recent processing techniques have increased the interconnect resistance and capacitance and recently more accurate models of integrated circuit tracks have been required.

### 2.2 RC Line Model

The simplest line model of a IC interconnection that considers both the resistance and the capacitance of the line is a lumped resistor and capacitor which form a basic low-pass

<sup>\*</sup> The term "RC delay" refers to the amount of time required to charge up the interconnect capacitance through the combined resistance of the driver and the interconnect.

filter. This model is as shown in Fig 2.1 where R and C are the line resistance and capacitance per unit length and l is the wire length.

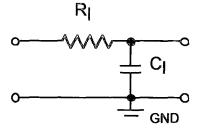

Fig. 2.1. A lumped RC model for interconnection.

This model illustrates the basic limitations of interconnections: they have a finite resistance and a finite capacitance. These two properties lead to a delay in signal propagation while the line capacitance is charged through the resistance. It also illustrates that an interconnect line is a low-pass filter. The size of the resistance and capacitance are both dependent on the length of the interconnect line, 1. More specifically the resistance of the line is determined by the geometry of the line (length, width and thickness) as well as the resistance of the conducting material while the capacitance is determined by the geometry of the line, the dielectric material surrounding the wire, and the distance of the wire from other conductors.

In the lumped model, the resistance and capacitance are "lumped" at one node. More realistically, however, the capacitance and resistance aren't lumped at one specific point in the centre of line, but are distributed along the length of the conductor. In this case of a distributed RC model, this distribution of resistance and capacitance is represented by a cascade of the  $\pi$ -sections. This is shown in figure 2.2. These sections are referred to " $\pi$ -sections" due their resemblance to the Greek letter pi.

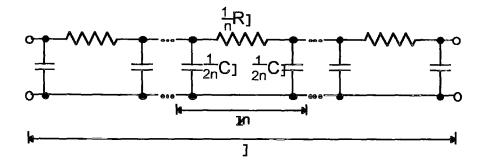

Fig. 2.2. A distributed RC line model approximated as a cascade of  $\pi$ -sections.

In this case, the number of subsections is given by n, and the value of each discrete resistor and capacitor are divided by the total number of sections. This creates a more accurate representation of the line in that the resistance and capacitance are interspersed. As would be expected, the more subsections there are in this model, the more realistic is the representation to that of a real wire. As the number of these subsections tends towards infinity when the total line length is fixed, the cascade becomes governed by the equations:

$$\frac{\partial I}{\partial z} = -C \frac{\partial V}{\partial t}$$

and  $\frac{\partial V}{\partial z} = -RI$  (2.1)

These can be combined to produce the diffusion equations describing voltage and current signal propagation through an RC line:

$$\frac{\partial^2 \mathbf{V}}{\partial z^2} = \mathbf{R}\mathbf{C}\frac{\partial \mathbf{V}}{\partial t} \quad \text{and} \quad \frac{\partial^2 \mathbf{I}}{\partial z^2} = \mathbf{R}\mathbf{C}\frac{\partial \mathbf{I}}{\partial t} \qquad (2.2)$$

In equation 2.2, I and V are signal current and voltage, respectively, with respect to a ground plane and the co-ordinate z measures distance along the track. Solutions to the diffusion equation are well known from the theory of heat conduction and so the behaviour of such a circuit is well understood as long as R and C are voltage-independent.

Although this solution is useful in the initial stages of VLSI design, it is not compatible with circuit simulators. In order to model an interconnect accurately in these packages, a compromise between the number of sections to include and the amount of time required to simulate the circuit must be evaluated. In other words, a compromise between accuracy and complexity needs to be made. Sakurai analysed accuracy of distributed RC lines using multiple sections and showed that a three-section  $\pi$  model had a relative error of typically less than  $3\%^{13}$ .

Other circuits may be used in place of the  $\pi$  model described above. Other commonly used circuits are the L and the T ladder circuits named for the approximate shape of their unit blocks. Rajput proposed a non-linear form of cascaded circuit to describe a distributed RC line<sup>14</sup>, but this circuit has several limitations in addition to being unnecessarily complex and the  $\pi$ , L and T configurations are more commonly used. Sakurai showed that the widely used L configuration is a poor approximation which may be as much as 30% in error from a true distributed line, even when as many as three stages have been added. The  $\pi$  and T circuits produce nearly identical results, but the  $\pi$ circuit is preferred because the T circuit contains two nodes per cascade while the  $\pi$ circuit has only one. Since the computational time of the HSPICE circuit simulation package is strongly dependent on the number of nodes in the circuit, the  $\pi$  configuration will give nearly identical results to the T, but can be calculated more efficiently.

The graph shown below in figure 2.3 illustrates the difference in response by that is found when multiple cascades are added in series. The circuits are simulated using the HSPICE circuit simulator (described in section 6.4). The circuit uses an HSPICE level 3 model of 1.0 $\mu$ m inverters which are driving a load of 1pF and 50 $\Omega$  and the input of another 1.0 $\mu$ m inverter. There are three driving inverters in series at the input to create a realistic slope on the input of the line model from the much faster 0.5ns input to the circuit model. The devices in these inverters use 1 $\mu$ m minimum lengths and widths for

the n-channel devices and minimum length and  $3\mu m$  wide p-channel devices. The voltage source for the inverters is 5V and the operating temperature is 20°C.

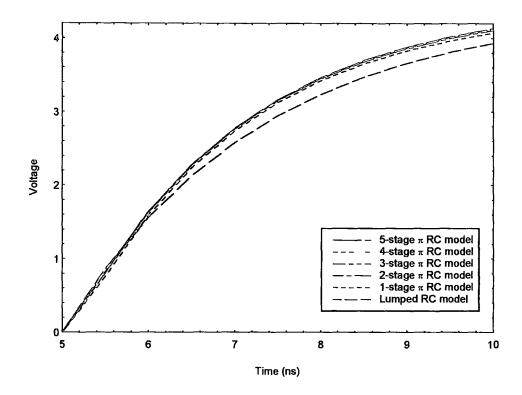

Fig. 2.3. Transient Response of lumped and distributed RC models.

From this graph it can be seen that, while significant variations are evident between the lumped and the one stage models, and some difference exists between the two stage model, the transient response of the other three models are nearly identical. In terms of HSPICE simulation time, however, for a system of eight interconnects the five stage  $\pi$  RC model requires more than one and half times the computation time and results in 32 more lines of code than the comparable three-stage  $\pi$  RC model of the same system.

The graph in figure 2.3 agrees well with results published by Sakurai as well as Mey<sup>15</sup>. Bakoglu<sup>16</sup>, the author of "Circuits, Interconnections and Packaging for VLSI", commenting on the results obtained by Sakurai, noted that the accuracy of the models is improved as the number of cascades in the system is increased, but concluded that "the

accuracy of the [ $\pi$  and T] models is improved as n increases, but it saturates at about three or four ladder steps." where the value n mentioned is the number of cascaded circuits. Similarly, Goel<sup>17</sup>, commenting on the results reported by Mey said, "In fact, there is negligible difference between the results for the 5-stage and 10-stage ladder networks". After simulations were performed on different systems using various values of load and line capacitances which resulted in results similar to those published, it was decided that a three-stage  $\pi$  network would be an adequate compromise between complexity and accuracy.

#### 2.3 RLC Line Model

The inclusion of inductance into an RC line model has two primary effects on the propagation of the signal through the line. It can introduce the problems of ringing and overshoot which are not found in RC models. Ringing and overshoot can lead to logic errors and can result in slower transition times since the output will take longer to settle. Inductance also creates wave propagation and transmission line effects which are quite different from the diffusive propagation found in distributed RC lines. Transmission line effects can result in reflection noise and can introduce a fundamental limit to how fast a signal can travel down the line.

Inductance becomes important in interconnect simulation if the line is long and as a result has a large inductance, or if the transition times are sufficiently fast that LdI/dt becomes significant. At this point, the current in the line cannot be increased indefinitely by reducing the source resistance of the driver due to the effect of the inductors which resist changes in current by generating a reverse electromotive force. This limits the amount of current in the line and a fundamental limit on waveform propagation is introduced based on the amount of time this limited current can charge up the capacitance in the line. The line is no longer equipotential, but now accommodates a travelling wave.

This explanation of transmission line effects can also be shown quantitatively using equation (2.1) modified to include inductance:

$$\frac{\partial I}{\partial z} = -C \frac{\partial V}{\partial t} \quad \text{and} \quad \frac{\partial V}{\partial z} = -RI - L \frac{\partial I}{\partial t} \quad (2.3)$$

which combine to give:

$$\frac{\partial^2 V}{\partial z^2} = RC \frac{\partial V}{\partial t} + LC \frac{\partial^2 V}{\partial t^2}$$

(2.4)

and similarly for current:

$$\frac{\partial^2 I}{\partial z^2} = RC \frac{\partial I}{\partial t} + LC \frac{\partial^2 I}{\partial t^2}$$

(2.5)

The second derivative in time indicates that the RLC line supports the propagation of a wave rather than simple diffusion with the coefficient of the second derivative determining the velocity of propagation. Similar to (2.2), exact solutions exist for these equations, but for use in circuit simulation packages an approximation must be made in terms of the number of sections to be included in the model.

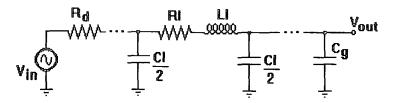

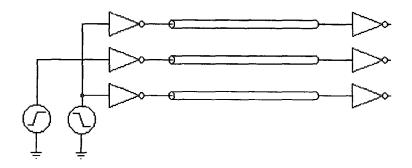

Fig. 2.4. Circuit used to model 0.35µm inverter driving an RLC line model.

In order to evaluate the number of sections required to accurately simulate an RLC model, a model of  $0.35\mu m$  inverter modelled as an AC voltage source in series with a resistor,  $R_d$ , as shown in figure 2.4, was used. This simplified model was used because HSPICE models for  $0.5\mu m$  and  $0.35\mu m$  transistors were not completed at the time these

simulations were performed. An rising input slope of 0.5ns was used as the switching delay of the inverter and  $8.35k\Omega$  was used as the device resistance of a minimum width and length NMOS transistor. A capacitor with a value of 20fF was used to represent the gate capacitance. The interconnect being modelled was 1cm long, 2µm wide, 0.5µm thick and the dielectric thickness (height) was 1µm.

Fig. 2.5. Transient Response of lumped and distributed RLC models.

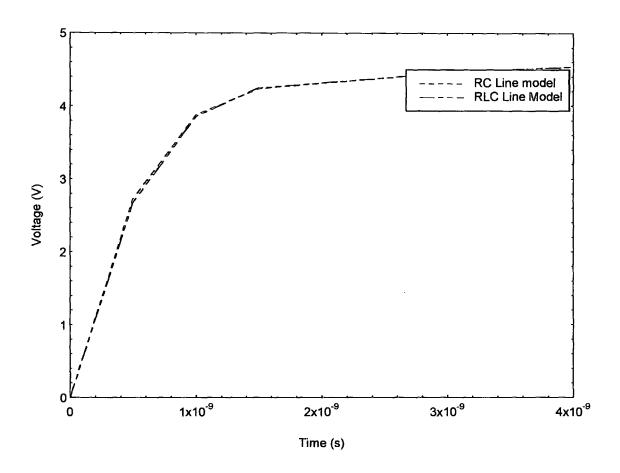

Essentially this graph shows similar results to those shown in figure 2.4. It can be seen that the three stage RLC interconnect model produces similar results to the more complex four and five stage models while requiring less computational time to simulate. The most significant difference between the RC and RLC models is that the differences between the models are less apparent. Using the same logic as was described in choosing the number of stages of the RC model to use in simulations it was concluded that 3 stages provided reasonable accuracy. A comparison between the contribution of inductance to the output waveform of a coupled crosstalk will be evaluated in section 7.4 using a more accurate model.

#### 2.4 Transmission Lines

The label transmission line could be applied to any line which transfers electromagnetic energy between two points in a circuit or communication system. In this section, the term transmission line specifically refers to the lossy transmission line element which is provided for use in modelling high frequency signals within HSPICE (version H92). The transmission line model included within the HSPICE package conveniently solves many of the problems discussed in the previous two sections as well as all of the difficulties associated with parameter extraction that will be covered in chapters 3 and 4. It reduces the problem of accuracy by automatically calculating the number of circuit sections that should be included. It is capable of calculating the R,L,C, and G circuit parameters and will either calculate them based on the physical dimensions of the interconnect, or will allow them to the pre-determined and inputted. It is also capable of supporting three levels of dielectric and can simulate a stripline ground plane configuration. Finally, the model provided includes the ability to automatically simulate crosstalk between conductors. In essence, the model provided within the program seems to provide the ideal tool for interconnect simulation.

Unfortunately, several restrictions are imposed by HSPICE and these limitations greatly reduce the usefulness of this element for analysing crosstalk. One major limitation of this model is that it only supports a maximum of five conductors. Additionally, these conductors can't be stacked vertically and must be made of the same material. There is also an error built into the calculation of the number of stages which can result in more ringing in the simulation than is actually present. The transmission line element calculation takes longer than the three-stage  $\pi$  RLC model described in the previous section. Finally, this included element is only available within the latest version of HSPICE. This reduces the value of any developed method for analysing crosstalk to those who have access to the HSPICE package (Inmos presently use a circuit simulator called ST-SPICE which doesn't currently support this HSPICE element).

# 3. Capacitance Parameter Calculation

#### 3.1 Introduction

Any two isolated conductors form a capacitor with a finite value of capacitance between them. The value of the capacitance is the constant of proportionality between charge and voltage on each of the two conductors. Capacitors are essential to nearly every circuit application in electronics. They are used for waveform generation, filtering, in the blocking and bypass of signals, and as integrators and differentiators. Although in CMOS VLSI circuits the gate capacitance creates the inversion layer necessary to switch the devices on and off, unwanted capacitance can also be the cause of several problems.

Capacitive coupling between tracks can lead to RC delays between devices, increased power dissipation and logic errors caused by crosstalk. As minimum feature sizes decrease and chip dimensions increase, these problems will become more prominent and will require the development of accurate tools for estimating capacitance in order to anticipate its effects. Research in the development of methods of capacitance parameter extraction in interconnects has led to two schools of thought. The first applies analytical formulae for simplified cases to obtain fast calculations at the expense of limited accuracy and minimal flexibility. The second school uses more rigorous mathematical techniques such as finite-element and boundary-element methods that are more flexible about conductor layout and are capable of more accurate calculations at the cost of extensive computation time and memory requirements. Other methods lie between these two extremes but all of them strike a compromise between accuracy, flexibility and computational resources.

#### 3.2 Area and Perimeter Based Capacitance Calculation Techniques

The most basic of the analytical methods considers each conductor to be an isolated parallel-plate capacitor in which distortion of the electric field due to edge effects is ignored and in which the bottom plate of the capacitor is an infinite plane. For this method to be reasonably accurate, the following must be true:

- 1. The conductor must be of negligible thickness. In other words, the width of the conductor must be much greater than the thickness. (W >> t)

- The ratio of the separation of the conductor from other conductors versus the height of the conductor over the reference plane must be much greater than the width. (S/H >> W)

- The ratio of the width of the conductor over its height must be much greater than one.

(W/H >>1)

To summarise these three conditions in one rule, the conductor mu s t be thin, much closer to the reference plane than it is to other conductors and must be have a width much greater than its height. If any of these three conditions are not met then fringing effects will become significant and the result will be increasingly inaccurate depending on how badly these conditions are broken.

A better approximation of a interconnect using an analytical formula is to use the Schwartz-Christoffel<sup>18</sup> transformation on the conductor which effectively transforms the edges of the base of the conductor into two point-sized wires<sup>†</sup>. This technique takes into account the fringing fields from the top of the conductor as well as the distortion of the electric field at either end due to edge effects. This formula, however, underestimates

<sup>&</sup>lt;sup>†</sup> A point-sized wire in two dimensions is formed by the intersection of an infinitely thin wire with a plane.

the capacitance of a track because it fails to take into account the thickness of the conductor.

Fig. 3.1. Comparison of field lines for parallel-plate and Schwartz-Chistoffel transformation methods of calculating capacitance.

When research into capacitance calculation of microstrips first began, it was focused entirely on the microstrips used in microwave circuits. In older microwave circuits, the width was in fact much greater than the thickness and the assumption that the conductors be of negligible thickness was justified. In certain circumstances, when the thickness was comparable to the width, a method called effective width was used to compensate for the fringing field from the top and sides of the conductor<sup>19</sup>. By adjusting the effective width of the conductor for certain values of thickness, the requirement of negligible thickness in both the parallel-plate and Schwartz-Christoffel methods can be effectively ignored with little or no loss in accuracy.

While the parallel-plate formula and the use of effective width historically form the basis of many of the analytical techniques that were developed for use in microwave circuits, more recent methods have been developed specifically for microelectronics which don't have limitations on thickness, width or separation and can calculate the coupling capacitance between neighbouring conductors as well. These methods consider the simplest case of two symmetric conductors and apply these results to more general cases. Although there are several methods which are generally employed, the simplest and most convenient is to describe the wave propagation of a signal along a coupled pair of symmetric lines as the sum of an even and odd mode of propagation.

## 3.2.1 The Lewis Technique for Coupled Interconnect Capacitance Calculation

One treatment which used even and odd modes of propagation and which is directly applicable to microelectronic structures was described in a paper by E.T.Lewis<sup>20</sup> which builds on earlier formulas used in microwave circuits developed by K.C.Gupta<sup>21</sup>. The method developed by Lewis is based on the analysis of the propagation modes supported by two adjacent coupled microstrips. If these two lines are symmetric then the supported modes can be reduced to an even and an odd mode corresponding to an even and odd symmetry of field lines as shown below in figure 3.2. In a typical VLSI chip all of the interconnects usually have the same dielectric completely surrounding the interconnects and this simplifies the analysis of the system compared to typical microwave circuits which have two or more layered dielectrics.

Fig. 3.2. Even and odd mode field line configurations in coupled microstrip lines.

Fig. 3.3. Even and odd mode capacitance models.

Figure 3.2 shown above illustrates the field lines configurations for the even and odd modes of propagation. In the even mode, the lines have the same voltage (+V or -V) and thus the field lines are between the conductors and the plane of metallisation (illustrated by the cross-hatched lines). In an odd mode, the conductors each have different voltages so the field lines are split between the ground plane and the other conductor. This can also be seen by examining the capacitance models describing these two modes which are shown in figure 3.3.

The general method described by Lewis consists of dividing the total capacitance of each conductor into its component parts: the coupled capacitance between the two conductors and the self capacitance between each conductor and the ground plane. These two capacitances can then be divided further by considering the field components of the two propagation modes. As is shown in figure 3.3, the total capacitance of the even mode,  $C_{et}$  is:

$$C_{et} = C_p + C_f + C_f \tag{3.1}$$

and it can be noted that there is no mutual capacitive component of the even mode. For the odd mode, the total capacitance,  $C_{ot}$ , is:

$$C_{ot} = C_s + C_m \tag{3.2}$$

where

$$C_s = C_p + C_f$$

and  $C_m = C_{gl} + C_{g2}$

Once the total capacitance has been split into its component elements, the actual values must be determined.  $C_p$  is simply the parallel plate capacitance between the strip and the ground plane.  $C_f$  is the outer fringe capacitance and can be found by working out the Schwartz-Christoffel transform of one of the strips, subtracting the parallel-plate component and then dividing by two (to obtain only one half of the fringing component). The modified inner fringe capacitance  $C_f$  can be found by dividing  $C_f$  by the ratio of the height over the separation. The final two components,  $C_{gl}$  and  $C_{g2}$ , describe the mutual capacitance between the two tracks and their calculation requires two complex formulas which are given in the book by Gupta<sup>4</sup>.

While the Lewis method for capacitance calculation was only rarely used in the course of the research, the method behind it is simple to understand and illustrates a technique that is easy to use and requires minimal computing power. It also provided a good approximation used to check whether, in the early programming stages, the more accurate method described later in section 3.4 was working correctly.

It was recognised early on that the Lewis method had several limitations that made it impractical for accurate calculations of realistic interconnect models. In order to satisfy the requirement that the conductors be symmetrical, all of the conductors in the calculation must be completely identical. In realistic bus structures, however, the power, the signal and the clock lines are typically made to different separations and widths to satisfy restrictions imposed by delay, crosstalk and electromigration problems. Further, most modern microelectronic integrated circuits utilise multiple levels of metallisation and commonly employ different interconnect dimensions on each level. Not only does the Lewis method require that all conductors be of the same dimensions, but it also requires that all conductors should be in the same y-plane. This restricts this technique to single level structures.

One additional limitation that is imposed by the method applies to systems with more than two conductors. In this case, the conductor width must be less than or equal to twice the height of the conductors above the ground plane ( $w \le 2h$ ). While this is a reasonable restriction in most VLSI systems, it can result in large errors in the calculation of inductance (see section 4.1) and in alternate materials such as GaAs and SOI<sup>22</sup>. These limitations in combination with the inherent inaccuracies in this method made it obvious that a more rigorous approach to capacitance calculation was required.

#### 3.3 Numerical Techniques for Capacitance Calculation

As mentioned in the introduction to this chapter, rigorous numerical techniques for the calculation of capacitance are characterised by high accuracy, flexibility on conductor geometry, complex computational algorithms, long computation times and large requirements on computing power and memory. There are three principle numerical techniques used to calculate capacitance in an arbitrary multiconductor system, namely, the finite element method (FEM)<sup>23,24</sup>, the boundary element method (BEM)<sup>25,26,27</sup> and the partial element equivalent circuit technique (PEEC)<sup>28,29</sup> The FEM, when used to calculate capacitance, works by partitioning the entire region of interest into a mesh of elements to determine the potential distribution by modelling the electric field. Capacitances are then derived from this potential distribution by the application of either an electric field on the conductor. This technique allows the modelling of nonhomogeneous conductors, curved geometries and very large conductor systems (since the resulting element matrix is sparse).

<sup>&</sup>lt;sup>‡</sup> In GaAs and SOI (Silicon On Insulator) processes, the effective ground plane of the substrate is farther from the the conductors than in silicon processes due to the high resistance of the substrate material.

The BEM, more commonly known as the Green's function technique, is the most frequently used numerical method for computing the inductive and capacitive matrices for multiconductor systems. It works similarly to the FEM, but models the charges on the conductor rather than the electric field. It's primary advantage is its computational efficiency. Additionally, only conductor surfaces and dielectric interfaces need be discretised so that open regions do not contain elements and artificial boundaries do not need to be introduced. The BEM replaces all conductor surfaces and dielectric interfaces with the charge distribution that exists in free space to produce a potential distribution equivalent to the original system. Using the principle of superposition, the electric field of a point in space is due to the cumulative effects of all charges present in the system. A Green's function is then defined that gives the potential at any point based on the distribution of total charge in the system and the potential of the conductor used as a reference (typically an infinite ground plane). The main limitation to the BEM is that the segmentation of the dielectric interfaces can result in extremely large and dense matrices. There are several disadvantages of this method which include complex mesh generation leading to elaborate data preparation and the necessary imposition of boundaries for open region problems which can lead to inaccuracies.

The PEEC is a technique in which all of the conductors in the system are broken down into rectangular cells and the equivalent electrical circuit is determined by computing the "partial" capacitances and inductances within these subsections of the main conductor. The resulting equivalent circuit consists of a three-dimensional mesh of inductors and capacitors. The primary advantage of the PEEC technique is that it is inherently threedimensional due to the method used to construct the mesh and as such is more efficient in terms of computation time and memory requirements at calculating parameters in three dimensional systems. This is not usually an advantage in many practical structures as they can be modelled by assuming considering a cross-section and assuming that all parameters in the third dimension are uniform. One obvious restriction with this method

is that it requires that all conductors are approximated by rectangular cells, but this is not a serious limitation with most practical interconnect structures.

Comparing each of these three numerical methods a few points can be made:

- For most practical structures which are uniform in the third dimension, there is no computational advantage to be gained by using the PEEC technique over the BEM and FEM methods.

- Compared with the FEM, data preparation is simpler with the BEM and the PEEC technique.

- Open areas are automatically catered for in the BEM and PEEC technique whereas the FEM requires a truncation of the problem space for calculation which can introduce a significant error.

- In simple systems involving few dielectric layers and containing a minimal number of conductors, the BEM provides the same accuracy as the FEM with a smaller mesh. As the problem complexity increases, however, the required computer resources needed by the BEM increases very rapidly, and a geometry dependent cutoff point will be reached above which the FEM becomes more efficient.

All of the numerical techniques described result in extremely accurate calculations of capacitance with varying degrees in geometric flexibility dependent on the method in use. They are all very computationally intensive, however, and generally require the inversion of extremely large matrices - a process that is demanding on both memory requirements and computational resources. In the course of the project I anticipated using different conductor configurations which would each involve multiple calculations.

Investigation into these techniques found that a FEM implementation using a fast Sun 4 computer resulted in typical run-times of 6 minutes for simple three conductor systems using a relatively coarse mesh and in excess of 30 minutes for more complex eight conductor systems using finer meshes<sup>30,31,15</sup> These run-time<sup>5</sup>/<sub>4</sub> do not include the time spent creating the mesh used to calculate the inductance and capacitance parameters which would commonly be a significantly larger amount of time. Ideally, a method was sought which would run faster than this on smaller machines such as the more common and (compared to the Sun 4) more inexpensive 386 and 486 desktop personal computers and which required much smaller memory considerations. The basic requirements for this new method were: computationally efficient with typical run times of less than a minute for three conductor systems on a 386 or 486 compatible desktop computer, modest memory requirements for small systems (matrix fits into 8Mb of RAM), reasonable accuracy (within a 5% tolerance), and that it allows multiple layers and different conductor dimensions.

#### 3.4 Matthaei's Method for Coupled Interconnect Capacitance Calculation

#### 3.4.1 Introduction to Mattahei's method

An alternative technique which can be used to determine distributed capacitance parameters is described in a paper by G.L.Matthaei<sup>32</sup>. The method was investigated and as it was found to match the requirements for this project, it was adapted for our capacitance calculations. This method is essentially a combination of the BEM and the even-odd mode of capacitance calculation described in section 3.2.1. In essence it works very much like the BEM described in the previous section, but rather than determine the charge distribution through the solution of the Green's function, it uses two charge basis functions, each associated with an entire side of a conductor. Since there are two functions used per side of rectangular conductor, the calculation requires a square matrix

of eight times the number of conductors - a significant reduction over the BEM. Since the matrix is smaller the memory requirements are economical and computation time is low.

The two charge basis functions used are similar to the even and odd mode functions described in section 3.2.1, but in this case they are describing the charge distribution within the conductor rather than electric field or equivalent capacitances. Figure 3.4a shows a one dimensional conductor of width w and figure 3.4b shows the first of the two charge basis functions - the even-symmetric function. If a charge of q was placed along the length of the conductor with an equal and opposite charge existing at infinity, this is the charge distribution that would occur on an infinitely thin conductor . Using Green's function, it can be shown<sup>33</sup> that the potential arising from this charge distribution at any point z in the complex plane is:

$$\phi_{e}(z,b,w) = q\left(\frac{1}{\varepsilon_{0}}H_{e}(z,b,w)\right) \qquad (3.3)$$

where

$$H_{e}(z,b,w) = \left(-\frac{1}{2\pi}\right) Im\left[ \arcsin\left(\frac{2(z-b)}{w}\right) \right] \quad (3.4)$$

In these equations,  $\varepsilon_0$  is the dielectric constant of the medium, b is the position of the centre of the conductor and w is the width of the conductor as indicated in the figure.

Fig. 3.4. (a) A two dimensional metal strip that extends into and out of the paper. (b) An even charge basis function for a fixed charge along the length of the strip. (c) The corresponding odd charge basis function.<sup>15</sup>

The corresponding odd-symmetric charge distribution is shown is figure 3.4c. This is the charge distribution along the conductor shown in figure 3.4a if it were placed in a uniform electric field along the x-axis direction in the figure. Again, using Green's function, it can be shown that the potential at any point z in the complex plane caused by this charge distribution is given by:

$$\phi_{o}(z,b,w) = g\left(\frac{1}{\varepsilon_{0}}H_{o}(z,b,w)\right) \qquad (3.5)$$

where

$$H_{o}(z,b,w) = Re\left[(z-b) - sign(Re(z-b))\sqrt{(z-b)^{2} - (w/2)^{2}}\right]$$

(3.6)