# **Durham E-Theses**

# Pentacene Based Organic Electronic Devices

YUN, YOUNGJUN

#### How to cite:

YUN, YOUNGJUN (2010) Pentacene Based Organic Electronic Devices, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/532/

### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- $\bullet \,$  the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

## Pentacene Based Organic Electronic Devices

### Youngjun Yun

# Abstract

This thesis describes a study of pentacene-based organic electronic devices with poly(methyl methacrylate) (PMMA) and cross-linked PMMA (cPMMA) gate dielectrics. The electrical characteristics of pentacene-based organic thin-film transistors (OTFTs) using PMMA as the gate dielectric are reported. Uniform pinhole-free and crack-free films of PMMA could be obtained by spin-coating, with a lower limit to the thickness of about 150 nm. The effects of the insulator thickness and channel dimensions on the performance of the devices has been investigated. Leakage currents, which are present in many devices using polymeric gate dielectrics, were reduced by patterning the pentacene active layer. The resulting transistors exhibited minimal hysteresis in their output and transfer characteristics with an acceptable performance (a field-effect mobility of 0.33 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, a threshold voltage of -11 V, an on/off current ratio of  $1.2 \times 10^6$  and a subthreshold slope of 1.5 V per decade). A bootstrapped inverter incorporating optimised pentacene OTFT structures, with PMMA as the gate dielectric, has been designed, fabricated and tested. The inverter uses capacitive coupling and bootstrapping effects, and exhibits superior performance to the normal diode-connected load inverter. The circuit has a 30 µs rise time and 450 µs fall time, at an operating frequency of 1 kHz and 30 V drive voltage. Pentacene-based OTFTs incorporating a PMMA gate insulator usually possess a large operating voltage, related to the thickness of the PMMA layer. A physical method, in particular ion-beam irradiation, to produce ultra-thin cross-linked layers of PMMA (33 nm) is introduced. It is demonstrated that physical cross-linking of the PMMA gate dielectric can be used to produce OTFTs with improved performance (a field-effect mobility of 1.1 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, a threshold voltage of -1 V, an on/off current ratio of  $1.0 \times 10^6$  and a subthreshold slope of 220 mV per decade) and

operating at low voltages, < 10 V. Low voltage memory transistors based on various charge storage elements (gold nanoparticles, ultra-thin aluminium and silver films) with cPMMA as the gate dielectric, have been investigated. Solution-processed OTFTs based on 6,13-bis(triisopropylsilylethynyl) (TIPS) pentacene with PMMA and cPMMA as the gate dielectric were also studied.

# Pentacene Based Organic Electronic Devices

by

Youngjun Yun

Ustinov College

A Thesis submitted in partial fulfilment of the requirements for the degree of PhD

Centre for Molecular and Nanoscale Electronics

School of Engineering and Computing Sciences

University of Durham

6 December 2010

# Contents

| 1 | Intr | oduction                                                          | 1  |

|---|------|-------------------------------------------------------------------|----|

|   |      | References                                                        | 4  |

| 2 | ΑL   | iterature Review of Organic Electronics                           | 5  |

|   | 2.1  | Introduction                                                      | 5  |

|   | 2.2  | Historical Background                                             | 6  |

|   | 2.3  | Applications                                                      | 7  |

|   |      | 2.3.1 Flat Panel Displays                                         | 7  |

|   |      | 2.3.2 Low-End Smart Cards and Electronic Identification Tags $$ . | 8  |

|   |      | 2.3.3 Sensors                                                     | Ĝ  |

|   | 2.4  | Organic Thin-Film Transistors                                     | 10 |

|   |      | 2.4.1 Charge Transport in Organic Semiconductors                  | 11 |

|   |      | 2.4.2 Organic Semiconductors                                      | 14 |

|   |      | 2.4.3 Gate Dielectrics                                            | 18 |

|   |      | 2.4.4 Contact Resistance                                          | 22 |

|   |      | 2.4.5 Device Structures of OTFTs                                  | 24 |

|   |      | 2.4.6 Electrical Characteristics of OTFTs                         | 25 |

|   | 2.5  | Methodology                                                       | 29 |

|   | 2.6  | Conclusions                                                       | 29 |

|   |      | References                                                        | 31 |

| 3 | Exp  | erimental Techniques                                              | 35 |

|   | 3.1  | Introduction                                                      | 35 |

|   | 3.2  | Film Deposition                                                   | 36 |

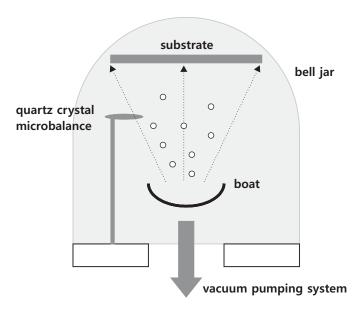

|   |      | 3.2.1 Physical Vapour Deposition                                  | 36 |

|   |     | 3.2.2   | Chemical Vapour Deposition                           | 39 |

|---|-----|---------|------------------------------------------------------|----|

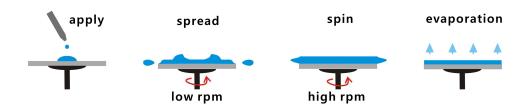

|   |     | 3.2.3   | Spin-Coating                                         | 41 |

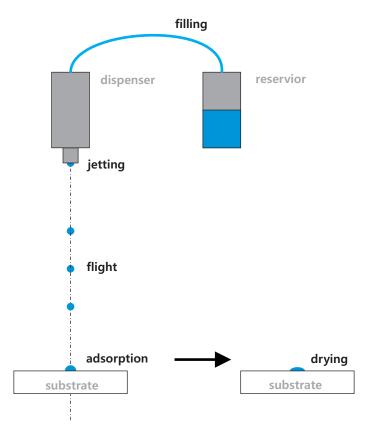

|   |     | 3.2.4   | Inkjet-Printing                                      | 41 |

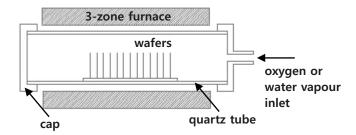

|   |     | 3.2.5   | Thermal Oxidation                                    | 43 |

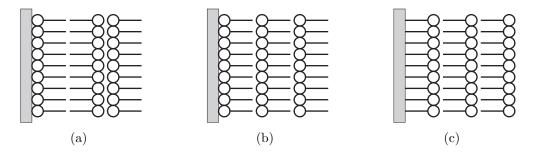

|   |     | 3.2.6   | Langmuir-Blodgett Deposition                         | 44 |

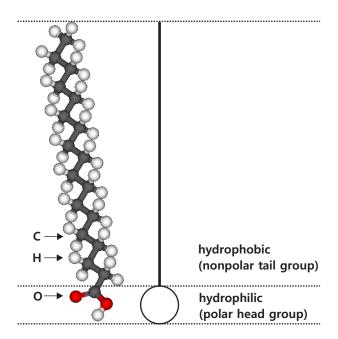

|   |     | 3.2.7   | Self-Assembly                                        | 45 |

|   | 3.3 | Experi  | imental Details                                      | 46 |

|   |     | 3.3.1   | Thermal Evaporation                                  | 46 |

|   |     | 3.3.2   | Spin-Coating                                         | 48 |

|   |     | 3.3.3   | Surface Treatments                                   | 48 |

|   | 3.4 | Device  | e Characterisation                                   | 50 |

|   |     | 3.4.1   | Physical Characterisation                            | 50 |

|   |     | 3.4.2   | Electrical Characterisation                          | 52 |

|   | 3.5 | Materi  | ials                                                 | 54 |

|   |     | 3.5.1   | Pentacene                                            | 54 |

|   |     | 3.5.2   | 6,13-bis(triisopropylsilylethynyl) Pentacene         | 55 |

|   |     | 3.5.3   | Poly(methyl methacrylate)                            | 57 |

|   | 3.6 | Conclu  | asions                                               | 58 |

|   |     | Refere  | nces                                                 | 59 |

| 4 | Pen | tacene  | Thin-Film Transistors with Poly(methyl methacrylate) | )  |

|   | Gat | e Diele | ectrics                                              | 62 |

|   | 4.1 | Introd  | uction                                               | 62 |

|   | 4.2 | Experi  | iment                                                | 63 |

|   | 4.3 | Poly(n  | methyl methacrylate) Gate Dielectrics                | 64 |

|   |     | 4.3.1   | Surface Morphology                                   | 64 |

|   |     | 4.3.2   | Electrical Characteristics                           | 65 |

|   |     | 4.3.3   | Thickness and Field-effect Mobility                  | 69 |

|   | 4.4 | Patter  | ning the Organic Semiconductor                       | 73 |

|   | 4.5 | Chann   | nel Dimensions                                       | 75 |

|   | 4.6 | Device  | e Characteristics                                    | 77 |

|   | 17  | Invert  | org                                                  | 70 |

|   |      | 4.7.1 Device Modelling                                          | 80   |

|---|------|-----------------------------------------------------------------|------|

|   |      | 4.7.2 Diode-Connected Load Inverter                             | 83   |

|   |      | 4.7.3 Bootstrapped Inverter                                     | 84   |

|   | 4.8  | Conclusions                                                     | 87   |

|   |      | References                                                      | 89   |

| 5 | Phy  | rsically Cross-linked Poly(methyl methacrylate) Gate Dielectric | s 93 |

|   | 5.1  | Introduction                                                    | 93   |

|   | 5.2  | Experiment                                                      | 94   |

|   | 5.3  | Cross-linked Poly(methyl methacrylate)                          | 95   |

|   |      | 5.3.1 Surface Morphology                                        | 96   |

|   |      | 5.3.2 Electrical Characteristics                                | 98   |

|   | 5.4  | Device Characteristics                                          | 100  |

|   | 5.5  | Low Voltage Operating Memory Devices                            | 105  |

|   |      | 5.5.1 Thin Aluminium Film                                       | 106  |

|   |      | 5.5.2 Thin Silver Film                                          | 110  |

|   |      | 5.5.3 Gold Nanoparticles                                        | 111  |

|   | 5.6  | Conclusions                                                     | 113  |

|   |      | References                                                      | 116  |

| 6 | Solu | ntion-Processed Organic Thin-Film Transistors                   | 119  |

|   | 6.1  | Introduction                                                    | 119  |

|   | 6.2  | Experiments                                                     | 119  |

|   | 6.3  | Device Characteristics                                          | 120  |

|   |      | 6.3.1 Poly(methyl methacrylate) Gate Dielectric                 | 120  |

|   |      | 6.3.2 Cross-linked Poly(methyl methacrylate) Gate Dielectric    | 123  |

|   | 6.4  | Conclusions                                                     | 126  |

|   |      | References                                                      | 127  |

| 7 | Con  | aclusions and Suggestions for Further Work                      | 128  |

|   | 7.1  | Conclusions                                                     | 128  |

|   | 7.2  | Suggestions for Further Work                                    | 130  |

|        | References                                    | 132 |

|--------|-----------------------------------------------|-----|

| Appen  | dices                                         | 133 |

| A.1    | SPICE simulation                              | 133 |

|        | A.1.1 Amorphous-Si TFT Model ASIA2 (level 15) | 133 |

|        | A.1.2 SPICE code                              | 137 |

| A.2    | SRIM Calculated Results                       | 139 |

|        | References                                    | 142 |

| Public | cations                                       | 143 |

# List of Figures

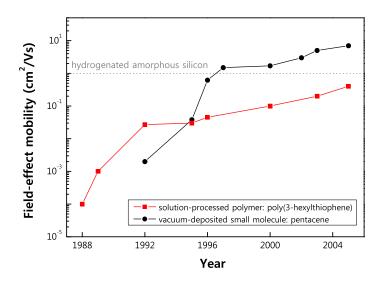

| 2.1 | Improvement in organic semiconductor mobility since the 1980s $[2,7]$ .                                                | 6  |

|-----|------------------------------------------------------------------------------------------------------------------------|----|

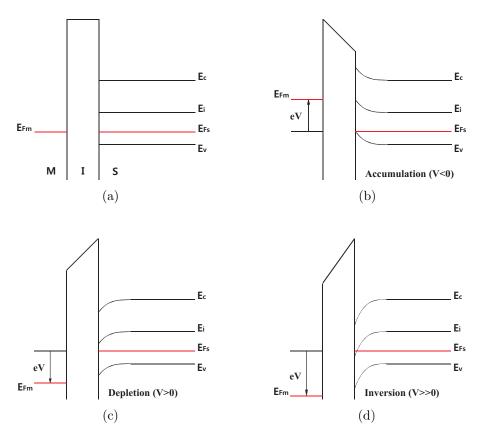

| 2.2 | Energy band diagrams for an ideal p-type MIS device under (a) flat                                                     |    |

|     | band, (b) accumulation, (c) depletion and (d) inversion conditions                                                     | 10 |

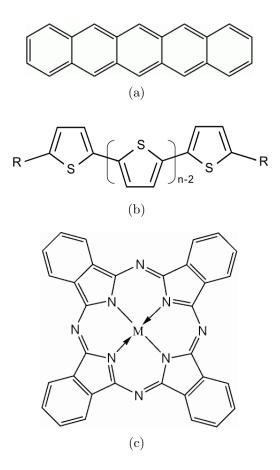

| 2.3 | Chemical structure of (a) pentacene, (b) unsubstituted (R=H) and                                                       |    |

|     | alkyl end-substituted ( $R=C_nH_{2n+1}$ ) oligothiophenes and (c) metal                                                |    |

|     | phthalocyanine (Pc) where the central hydrogen atom is changed to                                                      |    |

|     | the metal atom (M= $H_2$ .)                                                                                            | 15 |

| 2.4 | Chemical structure of (a) poly(3-hexylthiophene) (P3HT) and (b)                                                        |    |

|     | poly<br>(3-alkylthiophene) (P3AT) (R=C $_4$ H $_9$ , C $_8$ H $_{17}$ , C $_{10}$ H $_{21}$ and C $_{12}$ H $_{25}$ ). | 16 |

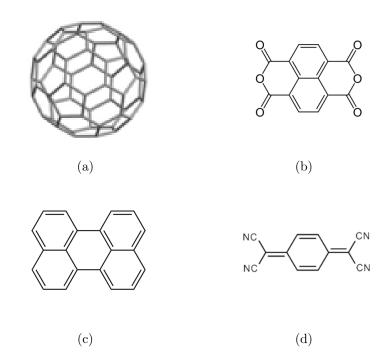

| 2.5 | Chemical structure of (a) buckminsterfullerene ( $C_{60}$ ), (b) naphthalene-                                          |    |

|     | tetracarboxylic-dianhydride (NTCDA), (c) perylene and (d) tetra-                                                       |    |

|     | cyanoquinodimethane                                                                                                    | 17 |

| 2.6 | Chemical structure of (a) polystyrene (PS), (b) poly(methyl methacry-                                                  |    |

|     | late) (PMMA), (c) poly(vinyl phenol) (PVP), (d) poly(vinyl alcohol)                                                    |    |

|     | (PVA), (e) benzo<br>cyclobutene (BCB) and (f) parylene                                                                 | 21 |

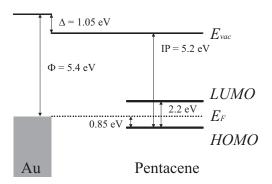

| 2.7 | Band line-up diagram for the gold-pentacene junction [40]                                                              | 23 |

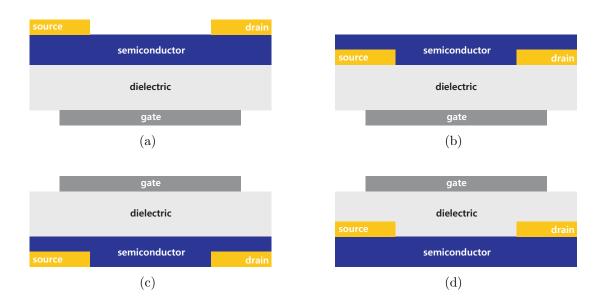

| 2.8 | Schematic diagrams of OTFTs with (a) bottom-gate, top-contact                                                          |    |

|     | (BG-TC) configuration, (b) bottom-gate, bottom-contact (BG-BC)                                                         |    |

|     | configuration, (c) top-gate, bottom-contact (TG-BC) configuration                                                      |    |

|     | and (d) top-gate, top-contact (TG-TC) configuration                                                                    | 24 |

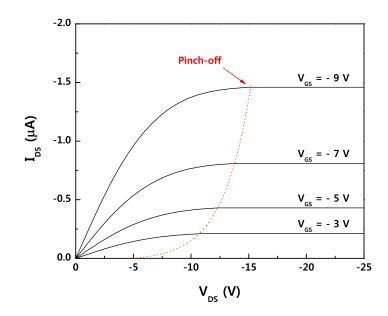

| 2.9 | Output characteristics for a typical OTFT based on a p-type semi-                                                      |    |

|     | conductor. The dashed line indicates where the channel of the OTFT                                                     |    |

|     | becomes pinched-off                                                                                                    | 26 |

|     |                                                                                                                        |    |

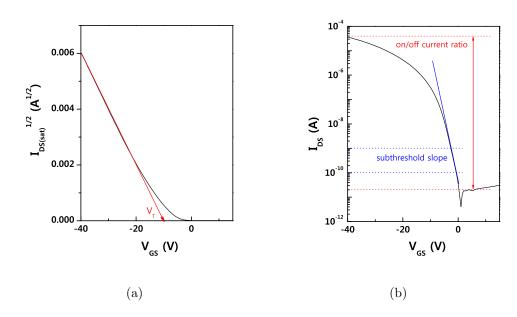

| 2.10 | Transfer characteristics for a typical OTFT based on a p-type semi-<br>conductor in the form of (a) $I_{DS(sat)}^{1/2}$ versus $V_{GS}$ and (b) $I_{DS(sat)}$ |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | on a logarithmic scale versus $V_{GS}$                                                                                                                        |

|      | on a logarithmic scale versus $VGS$                                                                                                                           |

| 3.1  | Thermal evaporation system for thin film deposition                                                                                                           |

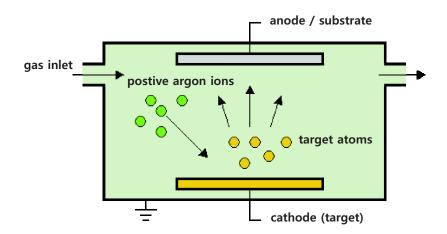

| 3.2  | DC planar diode system for thin film deposition                                                                                                               |

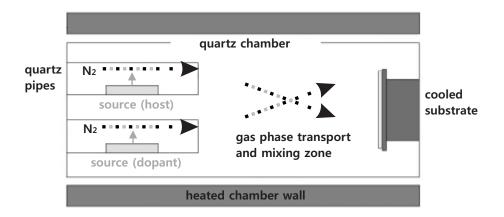

| 3.3  | Schematic diagram of organic vapour phase deposition (OVPD) pro-                                                                                              |

|      | cess                                                                                                                                                          |

| 3.4  | Schematic diagram of spin-coating                                                                                                                             |

| 3.5  | Schematic diagram of inkjet-printing                                                                                                                          |

| 3.6  | Schematic diagram of thermal oxidation                                                                                                                        |

| 3.7  | Chemical structure of n-octadecanoic acid (stearic acid)                                                                                                      |

| 3.8  | (a) Y-type (hydrophilic substrate), (b) Z-type (hydrophilic substrate)                                                                                        |

|      | and (c) X-type (hydrophobic substrate) Langmuir-Blodgett film de-                                                                                             |

|      | position                                                                                                                                                      |

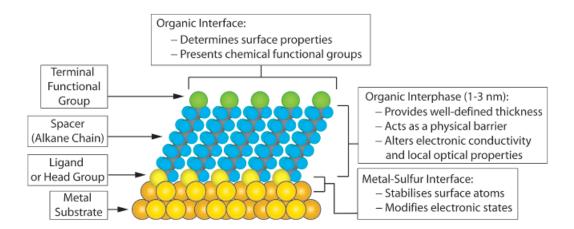

| 3.9  | Self-assembled monolayer of alkanethiolates on a gold surface with a                                                                                          |

|      | (111) texture [10]                                                                                                                                            |

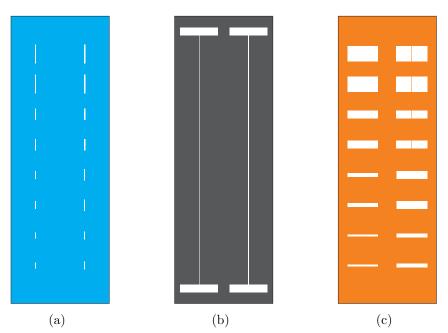

| 3.10 | Shadow masks for (a) semiconductor layers, (b) gate contacts and                                                                                              |

|      | (c) source/drain contacts                                                                                                                                     |

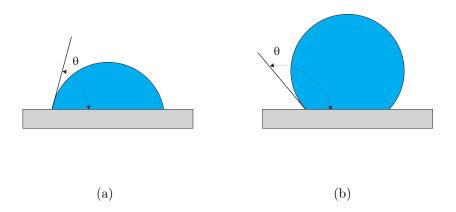

| 3.11 | (a) Wetting of hydrophilic substrate surface with contact angle $\theta <$                                                                                    |

|      | $\pi/2$ and (b) dewetting of a hydrophobic surface with $\theta > \pi/2$                                                                                      |

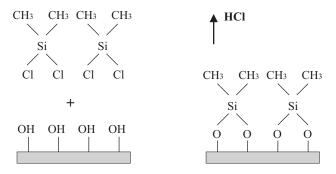

| 3.12 | Hydrophobic treatment of a glass surface with dimethyldichlorosilane                                                                                          |

|      | [14]                                                                                                                                                          |

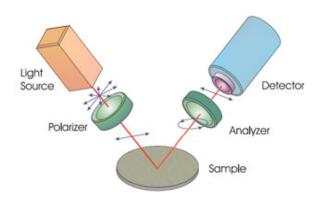

| 3.13 | The basic configuration of the ellipsometer [15]                                                                                                              |

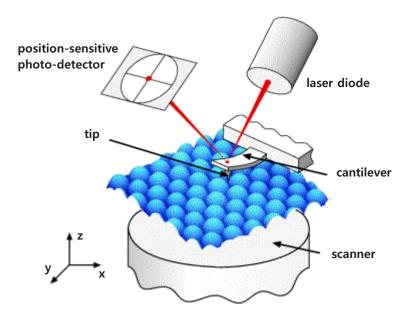

| 3.14 | Typical optical detection scheme in atomic force microscopy [17]                                                                                              |

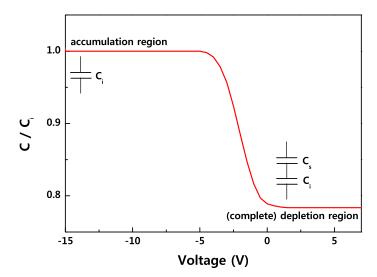

| 3.15 | Capacitance versus voltage behaviour for an typical MIS structure                                                                                             |

|      | based on a p-type organic semiconductor                                                                                                                       |

| 3.16 | The principal synthesis of pentacene from 6,13-pentacenequinone                                                                                               |

| 3.17 | The chemical structure of 6,13-bis(triisopropylsilylethynyl) (TIPS)                                                                                           |

|      | pentacene                                                                                                                                                     |

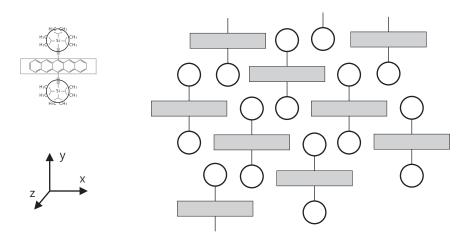

| 3.18 | The arrangement of molecules in TIPS pentacene. View normal to                                                                                                |

|      | plane of aromatic rings                                                                                                                                       |

| 3.19 | The principal synthesis for methyl methacrylate                                  | 57 |

|------|----------------------------------------------------------------------------------|----|

| 3.20 | Molecular structure of poly(methyl methacrylate)                                 | 58 |

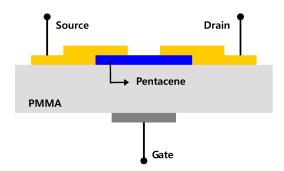

| 4.1  | A schematic cross-section of a pentacene-based OTFT with a PMMA                  |    |

|      | gate dielectric                                                                  | 63 |

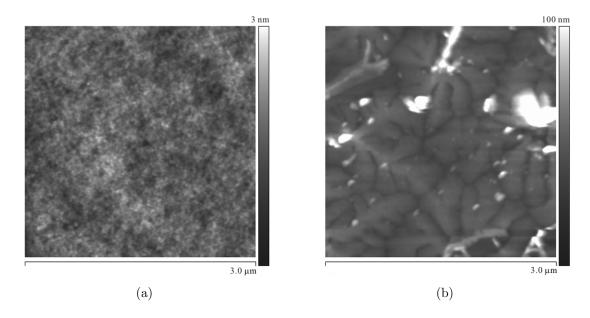

| 4.2  | Atomic force microscope images of (a) 150 nm thick PMMA film                     |    |

|      | spin-coated onto a glass slide and (b) 30 nm thick pentacene film                |    |

|      | thermally evaporated on top of the PMMA                                          | 64 |

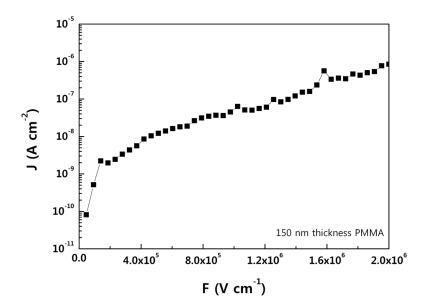

| 4.3  | Current density versus applied electric field for an Al/PMMA/Au                  |    |

|      | structure. The PMMA thickness = 150 nm                                           | 65 |

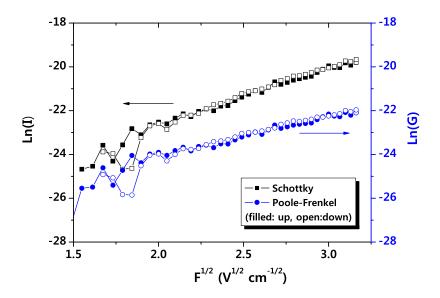

| 4.4  | Schottky (ln(I) versus $F^{1/2}$ ) and Poole-Frenkel (ln(I/V) versus $F^{1/2}$ ) |    |

|      | plots for an Al/PMMA/Au structure. The PMMA film thickness $=$                   |    |

|      | 150 nm                                                                           | 66 |

| 4.5  | Capacitance versus frequency characteristics of a spin coated PMMA               |    |

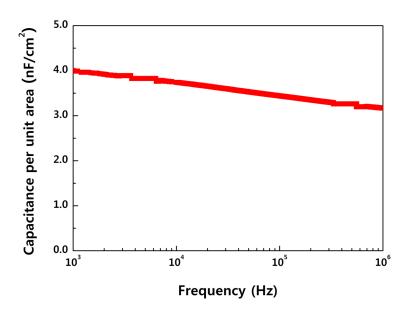

|      | layer; thickness = 810 nm                                                        | 67 |

| 4.6  | Capacitance versus voltage characteristics, measured at 1 MHz and a              |    |

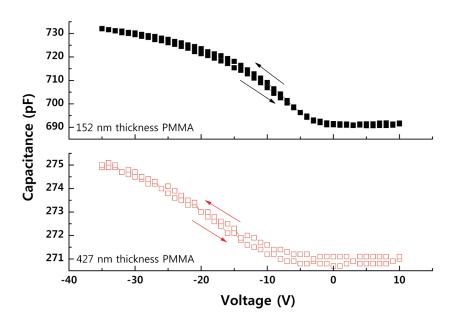

|      | voltage scan rate of 1 V $\rm s^{-1}$ for Al/PMMA/pentacene/Au structure         |    |

|      | for two different thicknesses of PMMA. Pentacene thickness = $30$ nm.            | 68 |

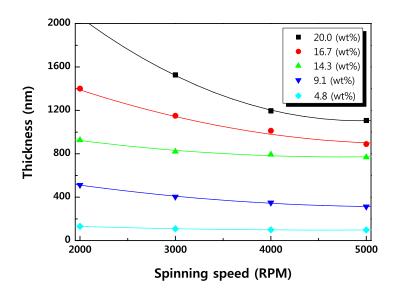

| 4.7  | Thickness of spin-coated PMMA films as a function of spinning speed              |    |

|      | and solution concentration                                                       | 70 |

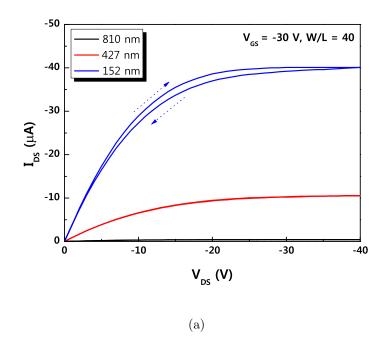

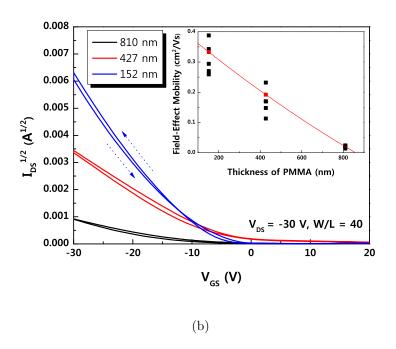

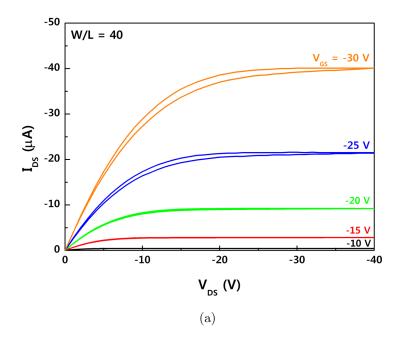

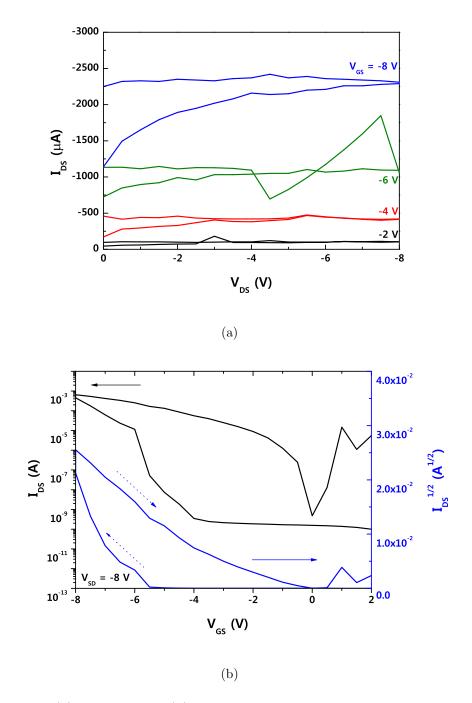

| 4.8  | (a) Output and (b) transfer characteristics for pentacene based OTFTs            |    |

|      | having PMMA gate dielectrics with different thickness. Inset: field-             |    |

|      | effect mobility as a function of the thickness of PMMA                           | 71 |

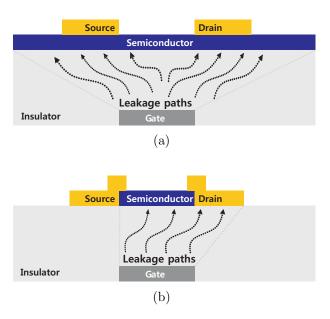

| 4.9  | Possible leakage paths in (a) an un-patterned pentacene OTFT and                 |    |

|      | (b) a patterned pentacene device                                                 | 73 |

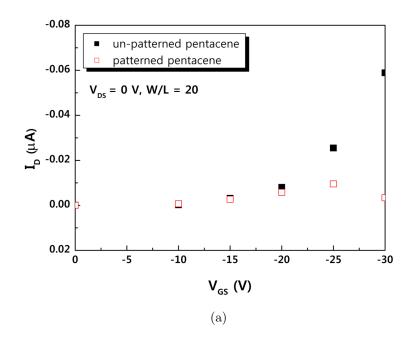

| 4.10 | (a) $I_D$ offset ( $V_{DS}=0$ V) and (b) leakage current ( $V_{DS}=$ -25 V) in   |    |

|      | patterned and un-patterned pentacene OTFTs                                       | 74 |

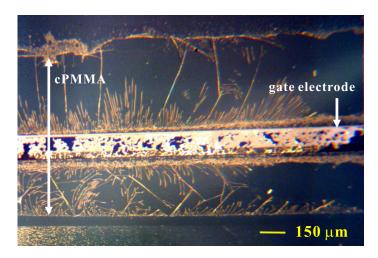

| 4.11 | Optical micrograph of a patterned pentacene-based OTFT with PMMA                 |    |

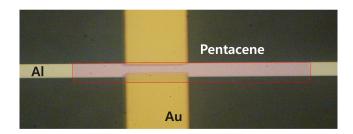

|      | gate dielectric. Channel length = 50 $\mu m,$ channel width = 500 $\mu m.$       | 75 |

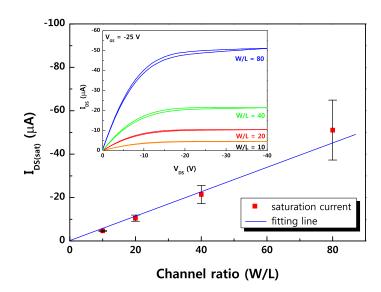

| 4.12 | $I_{DS(sat)}$ versus channel width/length ratio $\it{W/L}$ for pentacene OTFTs.  |    |

|      | The output characteristics are shown inset. $V_{GS} = -25$ V. PMMA               |    |

|      | thickness = 152 nm                                                               | 76 |

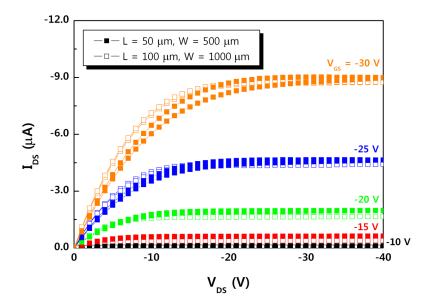

| 4.13 | Output characteristics for OTFTs with the same channel width/length     |    |

|------|-------------------------------------------------------------------------|----|

|      | ratio but different channel lengths and widths. PMMA thickness =        |    |

|      | 152 nm                                                                  | 76 |

| 4.14 | (a) Output and (b) transfer characteristics of a pentacene-based        |    |

|      | OTFT using PMMA as the gate dielectric. Channel length $= 50$           |    |

|      | $\mu m$ , channel width = 2000 $\mu m$                                  | 78 |

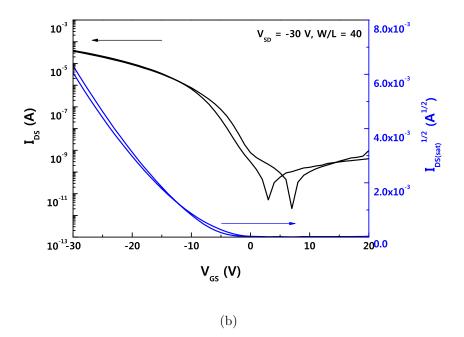

| 4.15 | (a) Output and (b) transfer characteristics of a pentacene-based        |    |

|      | OTFT using PMMA as the gate dielectric. Channel length $= 200$          |    |

|      | $\mu m,$ channel width = 4000 $\mu m.$                                  | 81 |

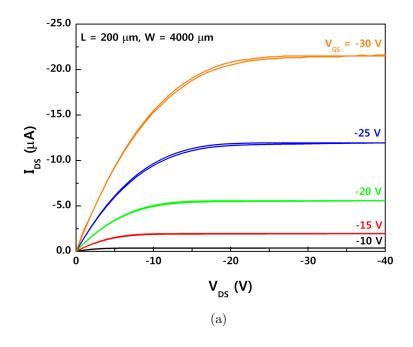

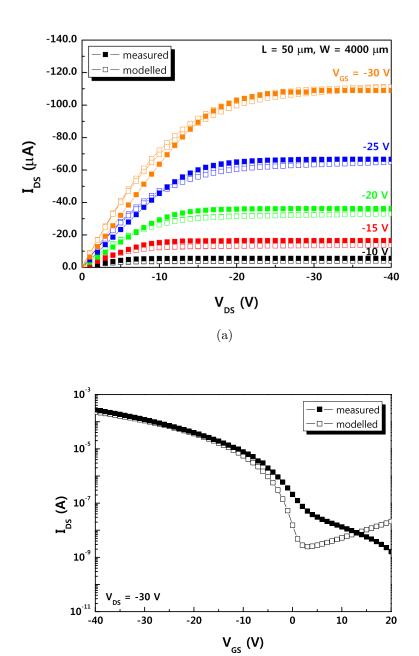

| 4.16 | Comparison between measured (full data points) and modelled (open       |    |

|      | data points) OTFT (a) output and (b) transfer characteristics. Chan-    |    |

|      | nel length = 50 $\mu m,$ channel width = 4000 $\mu m.$                  | 82 |

| 4.17 | Circuit diagram of a diode-connected load inverter                      | 83 |

| 4.18 | Measured and simulated output signals of a diode-connected load         |    |

|      | inverter. Operating frequency = 1 kHz; drive voltage = 30 V. $$         | 84 |

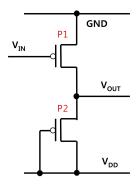

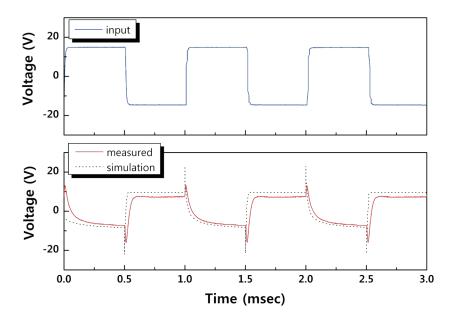

| 4.19 | Circuit diagram of the bootstrapped inverter used in this work          | 84 |

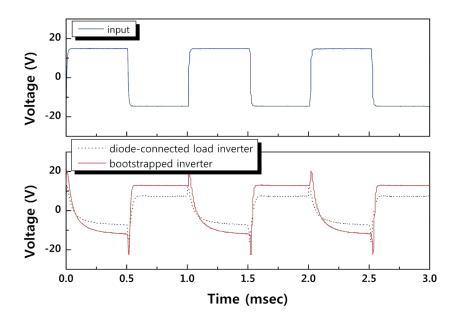

| 4.20 | Measured and simulated output signals of a bootstrapped inverter.       |    |

|      | Operating frequency = 1 kHz; drive voltage = 30 V                       | 86 |

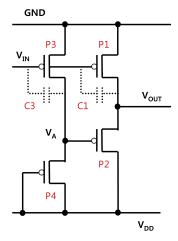

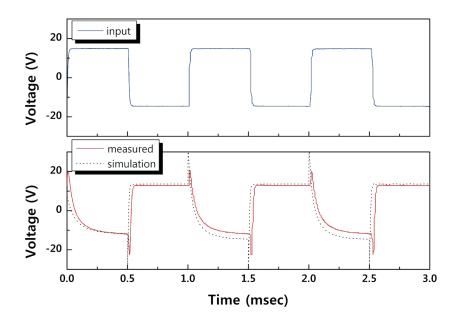

| 4.21 | The simulated difference voltage between nodes $V_A$ and $V_{OUT}$ com- |    |

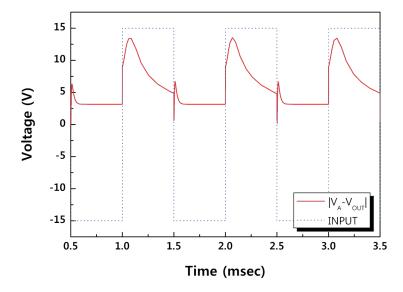

|      | pared to the input voltage of a bootstrapped inverter                   | 86 |

| 4.22 | Comparison of the measured dynamic switching characteristics of a       |    |

|      | diode-connected load inverter (dots) and a bootstrapped inverter (full  |    |

|      | line). Operating frequency = 1 kHz; drive voltage = 30 V                | 87 |

|      |                                                                         |    |

| 5.1  | The structure of PMMA with (a) a simple thermal pyrolysis, (b) low      |    |

|      | LET (gamma ray) irradiation and (c) high LET (ion-beam) irradia-        |    |

|      | tion [12]                                                               | 96 |

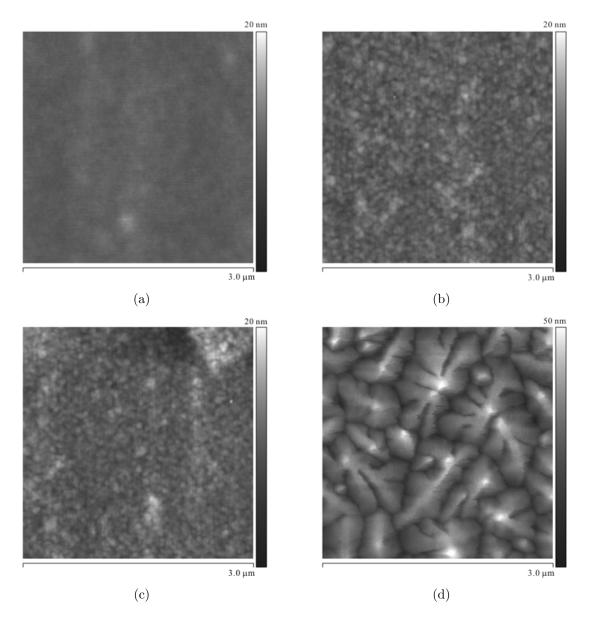

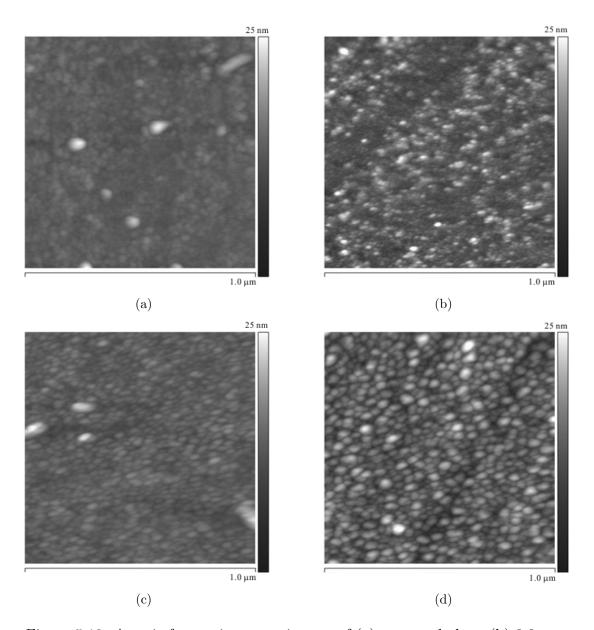

| 5.2  | Atomic force microscope images of (a) 57 nm thick PMMA film spin        |    |

|      | coated onto a glass slide, (b) 33 nm thick cross-linked PMMA film by    |    |

|      | ion-beam irradiation, (c) 33 nm thick cross-linked PMMA film after      |    |

|      | development in acetone and (d) 40 nm thick pentacene film thermally     |    |

|      | evaporated on top of the cross-linked PMMA                              | 97 |

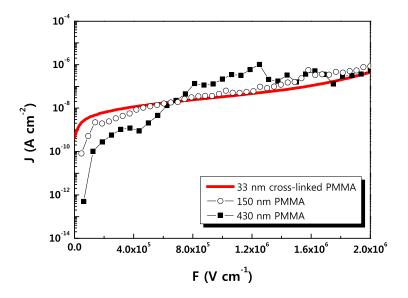

| 5.3  | Current density versus applied electric field for PMMA films (80 nm                   |     |

|------|---------------------------------------------------------------------------------------|-----|

|      | and 430 nm in thickness) and a cross-linked PMMA film (33 nm)                         |     |

|      | sandwiched between aluminium and gold electrodes                                      | 98  |

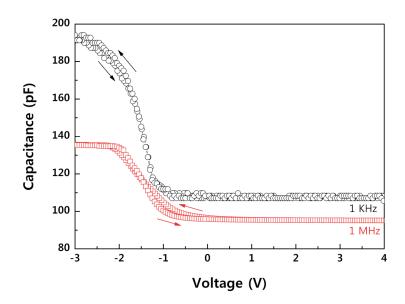

| 5.4  | Capacitance versus voltage characteristics, measured at 1 MHz and 1 $$                |     |

|      | kHz and a voltage scan rate of 0.05 V $\rm s^{-1}$ for aluminium/cross-linked         |     |

|      | PMMA (33 nm)/pentacene (40 nm)/gold structure                                         | 99  |

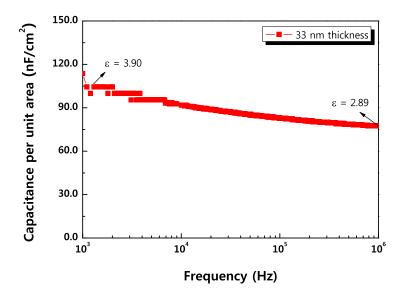

| 5.5  | Capacitance versus frequency characteristics for 33 nm thick cross-                   |     |

|      | linked PMMA layer sandwiched between aluminium and gold elec-                         |     |

|      | trodes                                                                                | 99  |

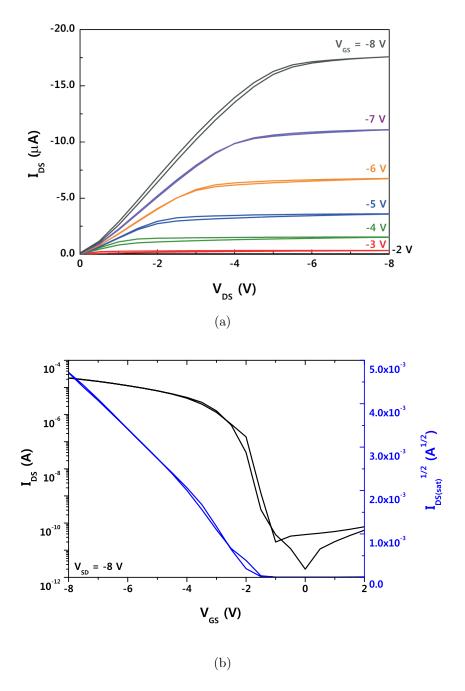

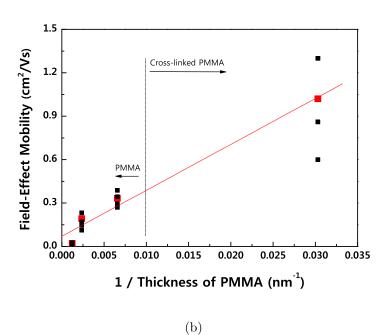

| 5.6  | (a) Output and (b) transfer characteristics of a pentacene-based                      |     |

|      | OTFT using 33 nm cross-linked PMMA as the gate dielectric. For-                       |     |

|      | ward and reverse voltage scans are shown for both sets of data. De-                   |     |

|      | vice channel length = 50 $\mu m;$ channel width = 500 $\mu m.$                        | 101 |

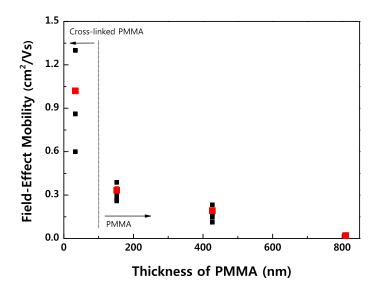

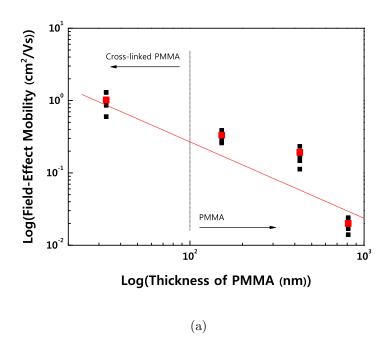

| 5.7  | Saturated field-effect mobility as a function of the thickness of PMMA.               | 102 |

| 5.8  | Saturated field-effect mobility $(\mu_{sat})$ as a function of the thickness          |     |

|      | of PMMA (d) in the form of (a) $\log(\mu_{sat})$ versus $\log(d)$ and (b) $\mu_{sat}$ |     |

|      | versus $d^{-1}$                                                                       | 103 |

| 5.9  | (a) Output and (b) transfer characteristics of a pentacene-based                      |     |

|      | OTFT using 20 nm cross-linked PMMA as the gate dielectric. For-                       |     |

|      | ward and reverse voltage scans are shown for both sets of data. De-                   |     |

|      | vice channel length = 50 $\mu m;$ channel width = 2000 $\mu m.$                       | 105 |

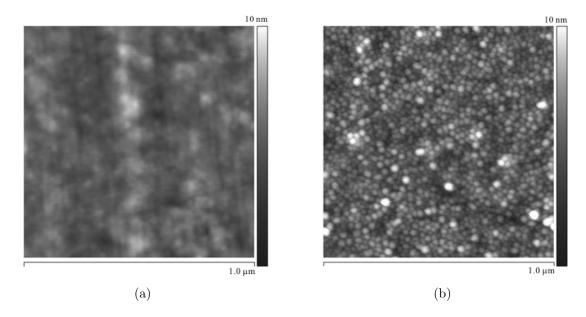

| 5.10 | Atomic force microscope images of (a) uncoated glass, (b) 3.3 nm, (c)                 |     |

|      | 6.5 nm and (d) 10.5 nm thick aluminium film thermally evaporated                      |     |

|      | on the bare glass                                                                     | 107 |

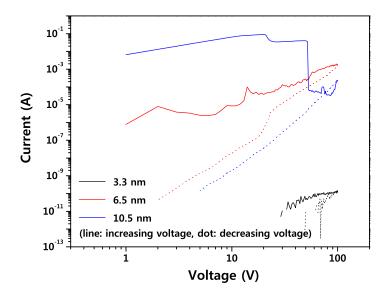

| 5.11 | In-plane $I\!\!-\!V$ electrical characteristics of 3.3 nm, 6.5 nm and 10.5 nm         |     |

|      | thermally evaporated aluminium film                                                   | 108 |

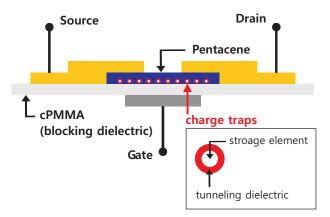

| 5.12 | A schematic cross-section of a pentacene-based OTFMT with a cPMMA                     |     |

|      | gate dielectric                                                                       | 108 |

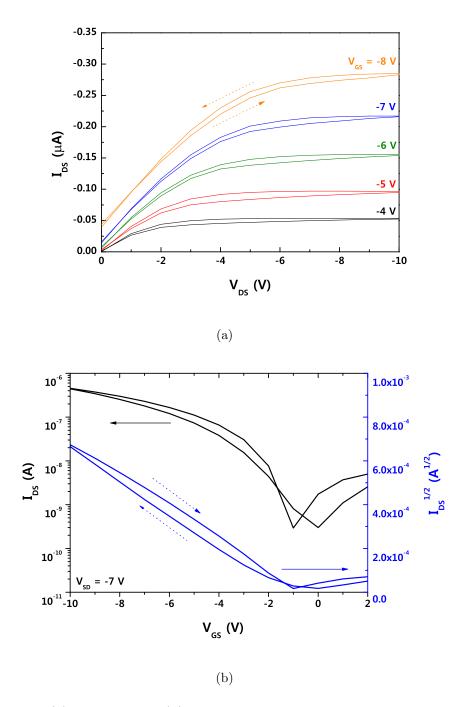

| 5.13 | (a) Output and (b) transfer characteristics of a pentacene-based                |     |

|------|---------------------------------------------------------------------------------|-----|

|      | memory transistor using 43 nm cross-linked PMMA as the gate di-                 |     |

|      | electric with a 3.3 nm thick aluminium film as the charge trapping              |     |

|      | layer. Forward and reverse voltage scans are shown for both sets of             |     |

|      | data. Device channel length = 50 $\mu m;$ channel width = 4000 $\mu m.~$ .      | 109 |

| 5.14 | Atomic force microscope images of (a) a 43 nm thick cross-linked                |     |

|      | PMMA film and (b) a 3 nm thick silver film thermally evaporated                 |     |

|      | on top of the cross-linked PMMA                                                 | 110 |

| 5.15 | In-plane $I\text{-}V$ electrical characteristics of a 3 nm thermally evaporated |     |

|      | silver film                                                                     | 111 |

| 5.16 | (a) Output and (b) transfer characteristics of a pentacene-based                |     |

|      | memory transistor using 43 nm cross-linked PMMA film as the gate                |     |

|      | dielectric with a 3 nm thick silver film as the charge trapping layer.          |     |

|      | Forward and reverse voltage scans are shown for both sets of data.              |     |

|      | Device channel length = 50 $\mu m;$ channel width = 2000 $\mu m.$               | 112 |

| 5.17 | Optical micrograph of a pentacene-based OTFMT with a cPMMA                      |     |

|      | gate dielectric and gold nanoparticles                                          | 113 |

| 5.18 | (a) Output and (b) transfer characteristics of a pentacene-based                |     |

|      | memory transistor using a 43 nm cross-linked PMMA film as the                   |     |

|      | gate dielectric with gold nanoparticles as charge traps. Forward and            |     |

|      | reverse voltage scans are shown for both sets of data. Device channel           |     |

|      | length = 100 $\mu m;$ channel width = 1000 $\mu m.$                             | 114 |

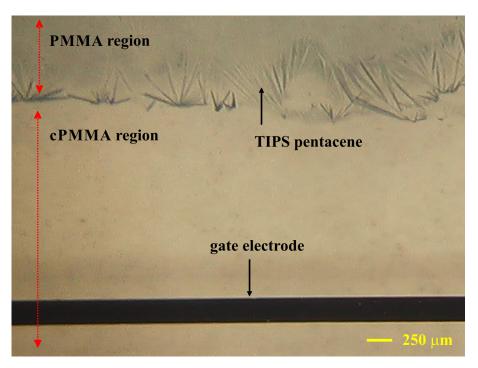

| 6.1  | Polarised optical micrograph of spin-coated TIPS pentacene on di-               |     |

|      | methyldichlorosilane (DMDCS) treated PMMA gate dielectric with                  |     |

|      | bottom-gate, bottom-contact configuration                                       | 121 |

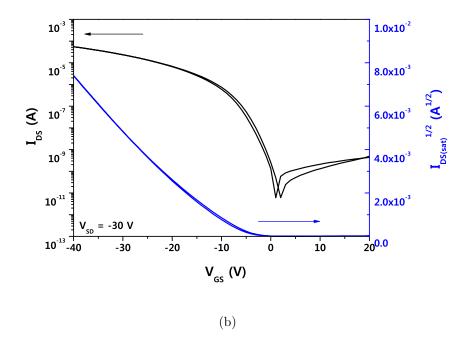

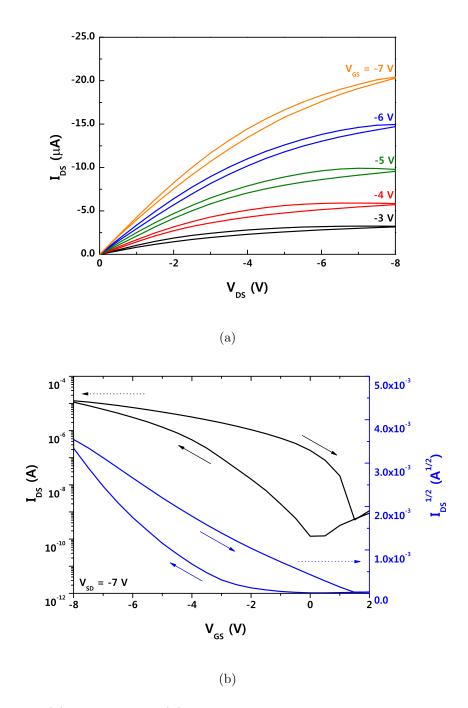

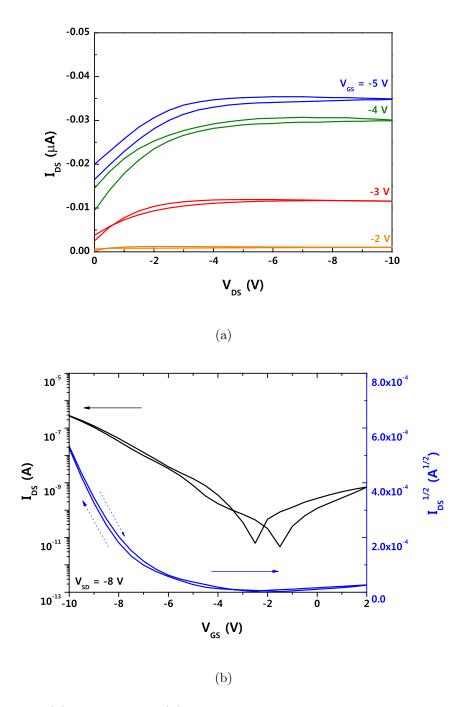

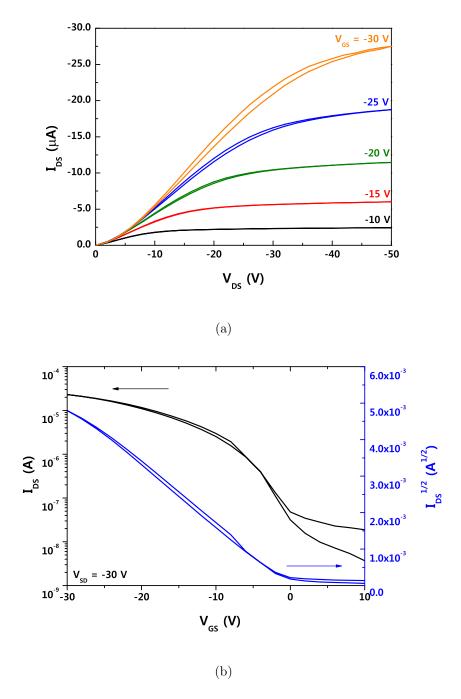

| 6.2  | (a) Output and (b) transfer characteristics of a spin-coated TIPS               |     |

|      | pentacene transistor using 150 nm PMMA as the gate dielectric with $$           |     |

|      | DMDCS treatment. Forward and reverse voltage scans are shown for                |     |

|      | both sets of data. Device channel length = 50 $\mu$ m; channel width =          |     |

|      | 1000 µm                                                                         | 122 |

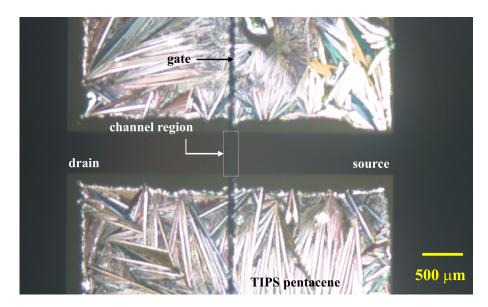

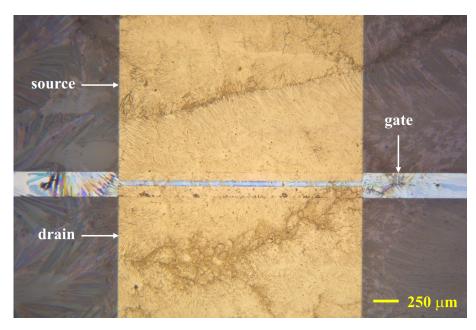

| 6.3 | Optical micrograph of spin-coated TIPS pentacene on a DMDCS                                                                        |     |

|-----|------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | treated PMMA and cPMMA gate dielectric                                                                                             | 123 |

| 6.4 | Polarised optical micrograph of spin-coated TIPS pentacene on a                                                                    |     |

|     | cPMMA gate dielectric with a DMDCS treated PMMA buffer layer.                                                                      | 124 |

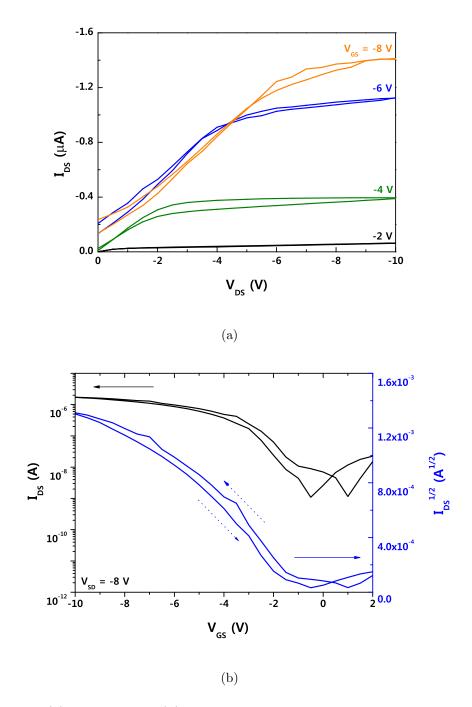

| 6.5 | (a) Output and (b) transfer characteristics of a spin-coated TIPS                                                                  |     |

|     | pentacene transistor using cPMMA gate dielectric and PMMA buffer                                                                   |     |

|     | layer with DMDCS treatment. Forward and reverse voltage scans are                                                                  |     |

|     | shown for both sets of data. Device channel length = 200 $\mu m;$ channel                                                          |     |

|     | $width = 2000~\mu m. \dots $ | 125 |

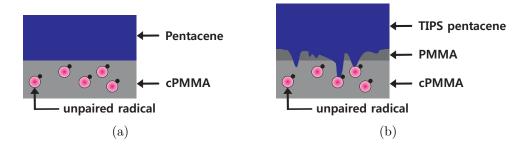

| 6.6 | Diagrams of (a) a thermally evaporated pentacene/cPMMA and (b)                                                                     |     |

|     | a spin-coated TIPS pentacene/PMMA/cPMMA interface                                                                                  | 126 |

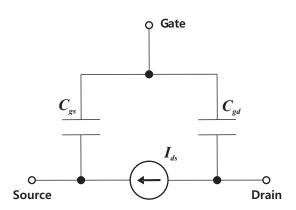

| A.1 | An equivalent circuit of amorphous-Si TFT                                                                                          | 133 |

# List of Tables

| 2.1 | Overview of inorganic dielectric materials [2]                                         | 19  |

|-----|----------------------------------------------------------------------------------------|-----|

| 2.2 | Overview of organic dielectric materials [27]                                          | 20  |

| 3.1 | Channel dimensions of shadow mask                                                      | 47  |

| 3.2 | Crystallographic data for pentacene [22, 23]                                           | 55  |

| 4.1 | Summary of pentacene/PMMA OTFT characteristics                                         | 77  |

| 5.1 | The results of linear fit $(yscale(Y) = A + B \times xscale(X))$ for the               |     |

|     | plots of $\log(\mu_{sat})$ versus $\log(d)$ and $\mu_{sat}$ versus $d^{-1}$            | 104 |

| A.1 | Amorphous-Si TFT Model ASIA2 Parameters (level 15)                                     | 136 |

| A.2 | SRIM calculated results with helium ion source and a PMMA density                      |     |

|     | of 1.20 g cm <sup>-3</sup> . Stopping Units = MeV (mg cm <sup>-2</sup> ) <sup>-1</sup> | 139 |

| A.3 | Table for other Stopping Units.                                                        | 141 |

# Declaration

I hereby declare that the work carried out in this thesis has not been previously submitted for any degree and is not currently being submitted in candidature for any other degree.

| Signed    | <br> | <br> | <br> |  |

|-----------|------|------|------|--|

| Candidate |      |      |      |  |

The work of this thesis was carried out by the candidate.

| Signed              |  |

|---------------------|--|

| Director of Studies |  |

|                     |  |

| Signed              |  |

| Director of Studies |  |

|                     |  |

| Signed              |  |

Candidate

Several of the chapters in this thesis are based on papers that are published. A list of papers and their corresponding chapters is provided in the **Publications**.

# Copyright © 2010 by Youngjun Yun

The copyright of this thesis rests with the author. No quotation from it should be published without the prior written consent and information derived from it should be acknowledged.

## Acknowledgements

I would like to give grateful acknowledgements to the following people and institutions that have enabled me to pursue and complete this work. This thesis would not have been possible unless the Higher Education Funding Council for England (ORSAS Scholarship) and the School of Engineering and Computing Sciences, Durham University (PhD Scholarship) had provided tuition fees and living expenses. To my supervisors, Prof. Michael C. Petty and Dr Christopher Pearson, I am profoundly indebted. I express my gratitude to Prof. Michael C. Petty, for all his time, advice, constant encouragement and support concerning not only my research but also living in Durham. I would like to show my gratitude to Dr Christopher Pearson for his advice and guidance of experimental techniques. I really thank them from my heart.

To all the current and former colleagues in the Centre for Molecular and Nanoscale Electronics goes my gratitude. I would like to particularly thank Dr Mohammed F. Mabrook, Dr Duncan H. Cadd, Prof. David Wood, Dr Dagou Zeze, Dr Palat Ushasree and Dr Mark Rosamond. In particular, very special thanks to the best friend I have met in Durham, Dr (to be) Supachai Ritjareonwattu, for his firm friendship and kind help with various tasks. It is my pleasure to thank those who made this thesis possible by allowing me access to their facilities and sharing their knowledge, in particular Prof. Graham Sandford and Dr Richard Thompson in the Department of Chemistry.

Most importantly, my parents for encouraging and inspiring me even while they are halfway around the world. And my brand new son, Siwoo, for providing a happiness in which to study and live. Finally, I want to especially thank my loving wife, Hyeyeon, for her understanding, patience and encouragement, without which I would not have succeeded this far.

Dedicated to my wife

## Chapter 1

### Introduction

The current performance of organic electronic devices suggest that they can be used for existing or new applications requiring large-area coverage, structural flexibility, low-temperature processing and low-cost manufacture. Among the various organic electronic devices, the organic thin-film transistor (OTFT) might become an important element in future microelectronics technology. OTFTs possess two key advantages over devices fabricated from inorganic semiconductors: mechanical flexibility and low-cost manufacture. These properties make OTFTs promising candidates for information displays, chemical sensors and radio frequency identification tags. For these and other applications, it is important to develop OTFTs with high performance and low cost manufacture. Various organic semiconductor materials have been used as the active layer in OTFTs. These include molecular crystals such as pentacene, which can be deposited in thin film form by thermal evaporation, and 6,13-bis(triisopropylsilylethynyl) (TIPS) pentacene, which can be conveniently processed by solution-based methods, such as spin-coating and inkjet-printing [1]. The gate dielectric layer also plays a crucial role in determining the performance of OTFTs [2]; the benefits of OTFTs can easily be lost if inappropriate insulators are used. For example, the inorganic insulators silicon dioxide and silicon nitride, both common gate dielectrics in OTFTs, are formed at high temperature. This precludes the use of many organic substrates. Certain organic insulators, such as benzocyclobutene (BCB), also need a very high curing temperature.

This thesis is concerned with pentacene-based organic electronic devices with a poly(methyl methacrylate) (PMMA) gate insulator. In this thesis, three strategies have been used to obtain low voltage organic electronic devices with high perfor-

mance and low-cost manufacture. First, thermally evaporated pentacene OTFTs with a spin-coated PMMA gate dielectric are investigated for hysteresis-free devices. Secondly, thermally evaporated pentacene OTFTs with physically cross-linked PMMA (cPMMA) gate dielectrics for low voltage operating devices are studied. Thirdly, spin-coated TIPS pentacene OTFTs with PMMA and cPMMA gate dielectrics for printed electronic applications are explored.

This thesis is organised as follows:

In Chapter 2, a general introduction to organic electronics is given. The historical background and various applications of organic electronics are briefly discussed and special attention is given to OTFTs. Charge transport mechanisms in organic semiconductors are reviewed and the various structures and electrical characteristics of OTFTs are discussed. Chapter 3 begins with an overview of film formation techniques for OTFTs. The experimental details of this thesis and the techniques used to characterise thin films and OTFTs are described. Details of the organic materials which are used in this thesis are also given.

Chapter 4 is the first results' chapter and focuses on pentacene-based OTFTs with a PMMA gate dielectric. The properties of PMMA films deposited by spincoating are described. These layers are then incorporated into pentacene OTFTs. The operation of two different inverter circuits (a simple diode-connected load inverter and a bootstrapped inverter) exploiting pentacene-based OTFTs with PMMA gate dielectrics are contrasted. Chapter 5 is concerned with cPMMA gate dielectrics for low voltage operating devices. The use of ion-beam irradiation to produce ultrathin cross-linked layers of PMMA is introduced. The device characteristics of a pentacene-based OTFT using cPMMA as the gate dielectric are reported. In particular, the saturated field-effect mobility as a function of the thickness of the gate dielectric is detailed. The remainder of Chapter 5 focuses on low voltage operating memory devices. Low voltage operating memory transistors based on various charge storage elements (a thin aluminium film, a thin silver film and gold nanoparticles) with cPMMA as the gate dielectric are investigated. In Chapter 6, the electrical characteristics of solution-processed OTFTs based on TIPS pentacene with either PMMA or cPMMA as the gate dielectric are given.

Finally, Chapter 7 provides the conclusions derived from the thesis and some suggestions for further work.

# References

- [1] H. Klauk (eds.), Organic Electronics, Wiley-VCH Verlag GmbH, Weinheim, 2006.

- [2] J. Veres, S. Ogier and G. Lloyd, *Chem. Mater.* 16: 4543, **2004**.

## Chapter 2

# A Literature Review of Organic Electronics

#### 2.1 Introduction

According to a study conducted by the US marketing research institute IDTechEx in 2006, the global market for organic and printed electronics will grow from its current 1.18 billion US dollars to more than 40 times that, to a volume of 48.18 billion US dollars, within the next 10 years [1]. Because of the relatively low charge carrier mobilities in organic materials, organic semiconductors cannot achieve the device performance of single-crystalline inorganic semiconductors, such as silicon (Si) and gallium arsenide (GaAs), which possess mobilities about three orders of magnitude higher. However, organic electronics is largely motivated by other considerations. The first attraction is the possibility of making some silicon-like functionality at a small fraction of the cost, by the use of inexpensive solution processes. A second is to use the capabilities of organic semiconductors that are not as readily available in silicon, such as sensing and mechanical flexibility. Research into organic semiconductor devices may open the way to completely new fabrication processes, and applications where organic semiconductors may prove advantageous.

This chapter begins with the historical background of organic electronics and its various applications. Important charge transport mechanisms in organic semiconductors are then introduced. The main components of organic thin-film transistors (OTFTs), organic semiconductors for the active layer, gate dielectrics and source and drain electrodes are described in the following section. The various device structures of OTFT are then discussed. Finally, the extraction methods for field-effect mobility, threshold voltage, subthreshold slope and on/off current ratio from the

electrical characteristics of OTFTs are reviewed.

### 2.2 Historical Background

Organic semiconductors were identified in the late 1940s [2] but work on organic light-emitting diodes (OLEDs) [3,4], organic photovoltaic cells (OPVCs) [5] and OTFTs [6] only emerged in the late 1980s. The initial organic devices were based on either small organic molecules, 8-hydroxyquinoline aluminium (Alq<sub>3</sub>) for the emitting layer in OLEDs [3] for example, or conjugated polymers, such as poly(p-phenylenevinylene) (PPV) [4] and polythiophene (PT) for the active layer in OTFTs [6].

Figure 2.1: Improvement in organic semiconductor mobility since the 1980s [2,7].

The performance of organic electronic devices has continuously improved over the last 20 years, and OLEDs have now been launched onto the display market. In the case of OPVCs, power conversion efficiencies have reached over 5 % [8]. Although these efficiencies are significantly lower than those of their inorganic counterparts (10 $\sim$ 20 %), the prospects of cheap production by roll-to-roll or printing processes drives the development of OPVCs further in a dynamic way. The progress of OTFTs has been less intense but the performance of some OTFTs now competes

with amorphous silicon TFTs which are used in active-matrix (AM) liquid crystal displays (LCDs), as shown in Figure 2.1 [2,7]. From now on, this review will focus on OTFTs.

### 2.3 Applications

The processing characteristics and performance of OTFTs so far show that they can be used for existing or novel TFT applications requiring large-area coverage, structural flexibility, low-temperature processing, and low-cost manufacture. The applications of organic semiconductors include AM flat panel displays (FPDs) based on liquid crystal pixels, organic light emitting diodes and electronic ink, low-end smart cards, electronic identification tags, sensors and perhaps all-flexible electronics.

### 2.3.1 Flat Panel Displays

An important potential application of OTFTs is in backplanes for displays. Despite a slowdown in the worldwide growth of FPDs, sales revenues are forecast to grow from 82.6 billion US dollars in 2009 to 111.5 billion US dollars by 2016, according to the latest results in the "Quarterly Worldwide FPD Shipment and Forecast Report" from Austin, Texas-based DisplaySearch [9]. In particular, OLED television (TV) and e-Book sales revenues may rise up to 140 % and 49 %, each year from 2008 to 2016, respectively [9].

To date, most backplanes of AM LCDs and AM OLED displays are based on TFTs comprising hydrogenated amorphous silicon (a-Si:H) or low temperature poly silicon (LTPS) as the active layer. However, OTFTs possess several advantages over structures fabricated from inorganic semiconductors: flexibility, large-area coverage and low-cost manufacture. These make OTFTs a promising candidate for inexpensive and flexible displays. For example, it is impossible to make AM LCDs based on a-Si:H TFTs on a transparent plastic substrate because of the relatively high processing temperature needed for a-Si:H deposition. However, OTFTs can be processed at room temperature and thus are compatible with flexible substrates. Furthermore, solution-processed OTFTs can enable low-cost large-area manufactur-

ing approaches, such as those based on inkjet-printing and roll-to-roll processing, for large-area AM LCD of TVs.

The first AM display based on organic semiconductors was reported in 2000 by Philips Research [10]. In 2001, Rogers et al. reported an electrophoretic flexible display using a backplane based on OTFTs [11]. Following Rogers's report, many research groups have described OTFT backplanes in combination with electrophoretic display media and simple OLED pixels. Hong et al. have also shown the possibility of an OTFT backplane with fairly large size and high resolution for AM LCDs in 2005 [12].

### 2.3.2 Low-End Smart Cards and Electronic Identification Tags

Devices based on organic semiconductors are still in their infancy and certain parameters such as field-effect mobility, uniformity of threshold voltage and dark currents are far inferior to those of silicon field-effect transistors (FETs). However, the performance of today's organic semiconductor technology is sufficient to develop low-cost circuits for applications that require only modest speeds such as intelligent electronic tickets, card games and product packaging. In particular, an integrated radio frequency identification (RFID) tag, which normally operates at 13.56 MHz (high-frequency, HF), and is used for providing power to the tag via inductive coupling (as used in smart cards, tickets, library book labels, passports, laundry tags and many other applications) becomes a promising candidate for organic electronics. The cost of organic RFID tags produced by solution processing could be low enough to compete with that of bar codes while providing a lot of the advantages offered by silicon-based RFID tags. Furthermore, organic RFID tags, being made of plastics, are more flexible and thinner than those based on silicon.

Baude et al. demonstrated pentacene based RFID circuits by vacuum deposition in 2003 [13]. The RFID circuits, without a rectification stage, were powered directly by RF and operated at 125 kHz. In 2004, Subramanian et al. reported 135 kHz all-printed organic RFID tags using novel pentacene and oligothiophene precursors for p-type semiconductors and ZnO nanoparticles for the n-type semiconductor [14]. Following this in 2009, Blache et al. described the first working 4 bit transpon-

der based on organic complementary metal-oxide-semiconductor (CMOS) operating at a carrier frequency of 13.56 MHz [15]. The devices were fabricated on flexible polyester substrates and all the active layers of the device consisted of soluble organic molecules deposited by spin coating.

#### 2.3.3 Sensors

In recent years, sensors, which are used for food safety, environmental monitoring, medical diagnostics and home security, have been intensively studied. Organic semiconductors offer many advantages in comparison with their inorganic counterparts, which make them particularly attractive for sensor applications. First, organic sensors can be manufactured at room temperature on flexible substrates with large-area coverage and using low-cost processes, an important attribute for disposable sensors and artificial skin. Second, their properties can be tunable via chemical synthesis. This includes not only electronic characteristics such as energy band gap and electron affinity but also the surface energy. Of particular interest for sensors is the ability to covalently attach biologically relevant moieties to organic semiconductor molecules [16]. Such hybrid materials have the potential to lead to the fabrication of sensors with high sensitivity and specificity.

Bartic et al. described ion-selective (IS) FETs for pH monitoring using a proton sensitive OTFT as a transducer in 2002 [17]. In 2004, Someya et al. reported a large-area, flexible pressure sensor suitable for electronic artificial skin with organic transistors [18]. The organic transistors, which were integrated with a graphite-containing rubber pressure sensor layer to form a very wide area structure, were used to realise a flexible AM, which was used to read out pressure images from the sensors. The device was electrically functional when it was wrapped around a cylindrical bar with a 2-mm radius. In 2008, OTFTs for chemical and biological sensors, capable of detecting parts per billion (ppb) anyalyte concentrations in water, were demonstrated with reliable operation by Roberts et al. [19]. Organic thin-film transistors, based on a thin, cross-linked gate dielectric and a stable organic semiconductor, could detect changes in pH and low concentrations of chemicals, such as trinitrobenzene, cysteine, methylphosphonic acid and glucose in water.

### 2.4 Organic Thin-Film Transistors

The metal-insulator-semiconductor (MIS) structure is the core technology in modern-day microelectronics. The energy-band diagram for an ideal MIS device, based on a p-type semiconductor, is shown in Figure 2.2 [20].

Figure 2.2: Energy band diagrams for an ideal p-type MIS device under (a) flat band, (b) accumulation, (c) depletion and (d) inversion conditions.

With no external bias, the Fermi levels of the metal and semiconductor align and the various bands are flat throughout the MIS structure (Figure 2.2(a)). When a negative voltage is applied to the metal with respect to the semiconductor (Figure 2.2(b)), the bands bend upward and the valence band moves closer to the Fermi level, causing an accumulation of holes near the insulator-semiconductor interface. A depletion of holes occurs when a positive voltage is applied to the metal (Figure 2.2(c)). If the positive voltage is increased further (Figure 2.2(d)), the bands bend down more strongly and the intrinsic level at the surface eventually becomes lower than the Fermi level. In this situation, the density of electrons exceeds that of

holes, and an inversion layer forms at the insulator-semiconductor interface. In the case of a MISFET, the inversion layer provides a conducting channel between the source and drain electrodes. One of the main advantages of the MISFET is that the depletion region between the p-type substrate and both the n-type and  $n^+$  regions below source and drain electrodes provides isolation from any other device fabricated on the same substrate. Furthermore, very low off currents can be achieved because both  $n^+$  regions act as reverse-biased diodes.

The concept of a TFT was proposed by Weimer in 1962 [21] and this led to the first a-Si:H TFT in 1979 by Le Comber [22]. The crucial difference between the TFT and the MISFET is that the channel is formed by the accumulation of charge carriers near the dielectric-semiconductor interface. There is no inversion of charge carriers in the channel as with MISFETs. For a p-type semiconductor, if a positive voltage is applied to the gate electrode, it operates in the depletion mode, and the channel region is depleted of charge carriers, resulting in a high channel resistance (off-state). For this reason, low off currents are only guaranteed by the low conductivity of the semiconductor. Meanwhile, if a negative voltage is applied to the gate electrode, it operates in the accumulation mode and a large concentration of charge carriers is accumulated in the channel, resulting in low channel resistance (on-state).

### 2.4.1 Charge Transport in Organic Semiconductors

The weak intermolecular interaction forces, normally Van der Waals bonds, result in a narrow bandwidth and strong interactions between free charge carriers and the lattice. This gives rise to polaron (self-localised charge) formation. These may be responsible for the low charge carrier mobilities in organic semiconductors. In contrast, the bonding energies in inorganic single-crystalline semiconductors are strong, due to covalent or ionic bonding, so that the charge carriers move in highly delocalised states in a wide bandwidth and have a very high charge carrier mobility.

In conventional single-crystalline inorganic semiconductors, charge transport occurs in delocalised states (band transport), and is limited by lattice vibrations, phonons, which scatter the charge carriers. Such a mechanism is not applicable to disordered materials such as polymers. Here, charge transport may take place by hopping between localised states. Hopping is assisted by phonons and the charge carrier mobility, which increases with temperature, is given by

$$\mu = \mu_0 \exp\left[-\left(\frac{T_0}{T}\right)^{1/\alpha}\right] \tag{2.1}$$

where  $\alpha$  is an integer ranging from 1 to 4 [23]. However, trapping attributed to grain boundaries and other structural defects in polycrystalline films significantly affects the temperature dependence of the charge carrier mobility [24].

While hopping is appropriate to describe charge transport in disordered materials, the multiple trapping and thermal release (MTR) model applies to well-ordered materials such as pentacene and oligothiophenes. Charge carriers interact with the localised levels, which act as traps, through trapping and thermal release. The effective field-effect mobility,  $\mu_{\rm eff}$  will be given by

$$\mu_{\text{eff}} = \mu_0 \alpha \exp\left[-\frac{(E_c - E_t)}{kT}\right]$$

(2.2)

where  $E_c$  is the energy of the transport level. In the case of a single trap level,  $E_t$  is the energy difference between the trap level and the transport level and  $\alpha$  is the ratio of the effective density of states (DOS) at the transport level to the concentration of traps [23]. An important outcome of the MTR model is that the gate voltage dependence of the field-effect mobility can be explained by an energy distributed DOS. This will be discussed in more detail in section 2.4.6.

On the other hand, band-like transport in delocalised states becomes the dominant charge transport mechanism in single crystals of organic semiconductors. The boundary between band transport (delocalised process) and hopping (localised process) is normally defined by materials having room temperature charge carrier mobilities around 1 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. However, it is hard to guarantee that the mean free path l does not exceed the intermolecular distance, which is the necessary condition for the diffusive band-like transport except at very low temperatures. Podzorov et al. have made it possible to distinguish between the charge transport in delocalised

states and thermally activated hopping between localised states because of defects and impurities by measuring the Hall effect on single crystals of rubrene [25]. The results suggest a band-like transport in delocalised states as a possible charge transport mechanism in highly ordered organic semiconductors. An advantage of the Hall experiment is that it allows independent measurements of the density of charge carriers. The charge carriers, which are temporarily trapped in shallow traps, do not make a contribution to the Hall voltage. Thus, the mobility extracted from the Hall experiments should coincide with the intrinsic, trap-free mobility. Furthermore, Pernstich et al. have reported band-like transport not only in single crystals of rubrene but also in polycrystalline films of pentacene by measuring the thermopower (Seebeck coefficient) [26]. The thermoelectric voltage  $V_{therm}$  arises when two ends of a sample are held at different temperatures ( $\Delta T$ ) and the Seebeck coefficient S is given by

$$S = \frac{V_{therm}}{\Delta T}. (2.3)$$

The general expression for the electronic contribution to the Seebeck coefficient is

$$S = \frac{k_B}{e} \int \frac{E_F - E}{k_B T} \cdot \frac{\sigma(E)}{\sigma} dE, \qquad (2.4)$$

where  $k_B$  is the Boltzmann constant,  $\sigma(E)$  is the electrical conductivity and includes terms describing the DOS and energy-dependent scattering mechanisms,  $\sigma$  is the total conductivity and T is the temperature [26]. For p-type semiconductors, the thermoelectric voltage can be given by rewriting Equations 2.3 and 2.4 in terms of valence band edge  $E_v$  and a weighted average  $\mathcal{A}$  as

$$V_{therm} = \frac{k_B}{e} \left( \frac{E_F - E_v}{k_B T} + \mathcal{A} \right) \Delta T, \tag{2.5}$$

where  $E_F$ - $E_v$  is the Fermi level position with respect to the valence band edge. The rate at which  $E_F$  changes with gate voltage depends on the trap density of the semiconductor. The quantity  $\mathcal{A}$  accounts for carriers distributed beyond  $E_v$ . The

values of  $\mathcal{A}$  in single crystals of rubrene (2.1~3.6) have been found to be well within the range of the electronic contribution in conventional single-crystalline inorganic semiconductors (2~4); depending on the nature of the scattering mechanisms up to room temperature, highlighting the similarity of transport mechanisms in single crystals of organic and conventional single-crystalline inorganic semiconductors. The values that have been found in the polycrystalline films of pentacene transistors are slightly smaller (1.7~2.2); whereas in amorphous inorganic semiconductors the values are in the range of -7 to -11 [26].

### 2.4.2 Organic Semiconductors

Various organic semiconductor materials have been used as the active layer in OTFTs. These include molecular crystals such as pentacene, which can be deposited in thin film form by thermal evaporation, and conductive polymers, which can be conveniently processed by solution-based methods, such as spin-coating and inkjet-printing [27].

### **Small Molecules**

Pentacene, oligothiophenes (nT, where n stands for the number of thiophene units) and phthalocyanines (Pcs) are the most representative p-type semiconductor materials based on small molecules. Vacuum deposition is the normal process for producing thin films of these materials. However, some compounds can be processed by solution-based methods using a soluble precursor molecule that may afford certain advantages in device fabrication.

Pentacene is a promising candidate for the active layer in OTFTs because of its high field-effect mobility. The molecule is a polycyclic aromatic hydrocarbon consisting of five aligned condensed benzene rings, called linear acenes or oligoacenes, as shown in Figure 2.3(a). Structurally, pentacene is one of the polyacenes, which were extensively studied as organic semiconductors during the 1960s and the 1970s. Oligothiophenes are also important small molecule p-type semiconductors for OTFTs. Oligothiophenes used in OTFTs are either non-substituted, or substituted at both ends by a linear alkyl group (Figure 2.3(b)). One of the most widely studied oligoth-

Figure 2.3: Chemical structure of (a) pentacene, (b) unsubstituted (R=H) and alkyl end-substituted (R= $C_nH_{2n+1}$ ) oligothiophenes and (c) metal phthalocyanine (Pc) where the central hydrogen atom is changed to the metal atom (M= $H_2$ .)

iophenes is  $\alpha$ -6T. The outstanding performance of these small molecules has been attributed to their ability to form well-ordered polycrystalline films in a herringbone arrangement. Phthalocyanines are another of the first reported families of small molecule p-type semiconductors. The phthalocyanine molecule has the structure of a molecular cage, into which various metals can be introduced (Figure 2.3(c)). Most devices based on Pc are fabricated by vacuum deposition, i.e. thermal evaporation. However, the solution-based Langmuir-Blodgett (LB) technique has also been used. Furthermore, Pcs may be substituted with electron withdrawing groups at their periphery, such as hexadecafluoro-substituted copper Pc (R=F, M=Cu). These materials can exhibit n-type field-effect mobilities, as high as 0.03 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, under ambient conditions and with excellent stability [27].

### **Polymers**

The carrier mobilities in polymers are still one order of magnitude lower than those of the small molecules as indicated in Figure 2.1. This can be explained by the fact that as solution-processed materials, polymers, provide poorer ordering than evaporated small molecules. This can result from the addition of soluble groups (e.g. alkyl chains) or soluble precursors.

Figure 2.4: Chemical structure of (a) poly(3-hexylthiophene) (P3HT) and (b) poly(3-alkylthiophene) (P3AT) ( $R=C_4H_9$ ,  $C_8H_{17}$ ,  $C_{10}H_{21}$  and  $C_{12}H_{25}$ ).

Polythiophenes (PTs) were the first solution-processed semiconductors used for OTFTs. Various derivatives have now been incorporated on the polymer backbone to impact functionality, increase solubility and induce self-assembly. The alkyl derivatives can be incorporated into a PT-based polymer chain with two types of arrangement, either head-to-tail (HT) or head-to-head (HH). A polymer with a mixture of HH and HT linkages in PT is referred to as regiorandom, while one with only HT linkages is referred to as regioregular [27]. Among PT-based polymers, poly(3-hexylthiophene) (P3HT), in which the addition of alkyl side-chains enhances the solubility of the polymer chains, is the most widely studied p-type semiconductor material (Figure 2.4(a)). Poly(3-alkylthiophene)s (P3ATs) are also important thiophene-based polymers with side chains ranging from butyl to dodecyl (Figure 2.4(b)).

### n-Type Semiconductors

The development of n-type organic semiconductors will enable the fabrication of complementary logic circuits which have many advantages; high robustness, low power consumption and low noise. However, most of the organic semiconductors studied so far are p-type. Molecules such as unsubstituted pentacene or oligothiophenes are more conducive to the injection of holes than electrons. On the other hand, an n-type semiconductor is one in which electrons are more easily injected than holes.

Figure 2.5: Chemical structure of (a) buckminsterfullerene ( $C_{60}$ ), (b) naphthalene-tetracarboxylic-dianhydride (NTCDA), (c) perylene and (d) tetracyanoquinodimethane.

As mentioned above, substituted Pcs (R=F or Cl, M=Cu, Zn, Co or Fe) have exhibited n-type behaviour. Furthermore, ambipolar mobility has also been reported from water soluble copper Pcs substituted with sulfonic acid and methyl pyridnium groups. Fullerenes (e.g.  $C_{60}$ ), which are molecules composed entirely of carbon in the form of a hollow sphere, ellipsoid or tube as shown in Figure 2.5(a), and their derivatives, were reported as n-type organic semiconductors in 1993. Since then, mobilities as high as 0.56 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> have been reported for  $C_{60}$  films fabricated

by molecular beam deposition without breaking the vacuum [28]. A major problem of these materials is their strong instability with respect to oxygen, which acts as an electron trap within the C<sub>60</sub> lattice. Naphthalene-tetracarboxylic-dianhydride (NTCDA), perylene and tetacyanoquinodomethane (TCNQ) have also been studied as n-type organic semiconductors and the chemical structure of these materials are shown in Figure 2.5. Recently, perfluoroalkyl substituted oligothiophenes and trifluoromethylphenyl, electron withdrawing group, based oligomers have been reported as novel n-type organic semiconductors.

#### 2.4.3 Gate Dielectrics

The performance of OTFTs is determined by the charge carriers flowing at the interface between the active and gate dielectric layers. Consequently, the development of suitable insulating materials is an essential element in improving OTFTs. The operating voltage of the device, in particular, is determined directly by the thickness and permittivity of the gate dielectric.

In a MIS structure, the charge induced on the semiconductor surface as a function of applied voltage is given by

$$Q = CV = \left(\frac{\epsilon_0 \epsilon_r S}{d}\right) V \tag{2.6}$$

where S is the area, d is the distance between the electrode and the semiconductor,  $\epsilon_0$  and  $\epsilon_r$  are the permittivity of free space and the dielectric constant of the dielectric, respectively. Increasing the capacitance, C, through the dielectric constant,  $\epsilon_r$ , or reducing the film thickness, d, would reduce the voltage requirement necessary to induce the same amount of charge in the semiconductor. Besides the dielectric constant and the film thickness of the gate dielectric layer, the dielectric roughness (which is believed to reduce the mobility in organic semiconductors due to disorder induced at the accumulation layer), chemical/mechanical properties of the dielectric-semiconductor interface, ease of processing and reliability are also important factors to be considered for the selection and design of gate dielectric materials. To date, several classes of dielectric materials have been studied for OTFTs. These can be

Table 2.1: Overview of inorganic dielectric materials [2].

| Material                               | Preparation method | Deposition temperature [°C] | Dielectric constant |  |

|----------------------------------------|--------------------|-----------------------------|---------------------|--|

| $\mathrm{SiO}_2$                       | Thermally grown    | > 600                       | 3.9                 |  |

| $SiO_2$                                | Ion beam sputtered | 80                          | 3.9                 |  |

| $\mathrm{Al_2O_3}$                     | Sputtered          | Not given                   | $\sim 5.1$          |  |

| $\mathrm{Al_2O_3}$                     | Anodised           | Room temperature            | $\sim 4.2$          |  |

| ${ m TiO_2}$                           | Anodised           | Room temperature            | 21                  |  |

| $\mathrm{SiN}_x$                       | CVD                | $250 \sim 350$              | $6\sim7$            |  |

| $\mathrm{Ba}(\mathrm{ZrTi})\mathrm{O}$ | RF sputtered       | Room temperature            | 17.3                |  |

| Ba(SrTi)O                              | RF sputtered       | Room temperature            | 16                  |  |

| $Ta_2O_5$                              | Sputtered          | 300                         | 25                  |  |

classified into inorganic (conventional or high dielectric constant) materials, organic (polymeric) materials, ultra-thin self-assembled monolayers (SAMs), multilayer and nanocomposite dielectric materials.

### Inorganic Dielectrics

A wide range of inorganic dielectric materials have been studied and employed as the gate dielectric layer in OTFTs over the past decade. The availability of thermally grown silicon dioxide as the gate dielectric layer on heavily doped silicon (as the gate electrode) has made this the ideal system for the initial evaluation of almost all new organic semiconductors. Silicon dioxide has excellent insulating properties due to its large band gap (8.9 eV) and thermodynamic stability [27]. However, the advantages of organic electronics cannot be exploited fully with this material because thermally-grown silicon dioxide is not compatible with flexible substrates. As a result, a large number of other inorganic dielectric materials have been investigated. For example, silicon dioxide (SiO<sub>2</sub>), barium zirconate titanate (Ba(ZrTi)O) and barium strontium titanate (Ba(SrTi)O) have been deposited by sputtering on transparent plastic substrates at low temperature. As another approach, alternative higher dielectric constant materials such as titanium dioxide (TiO<sub>2</sub>) and tantalum oxide (Ta<sub>2</sub>O<sub>5</sub>), obtained via electrochemical anodisation of sputtered tantalum, are being considered. Some representative inorganic dielectric materials are listed in Table

Table 2.2: Overview of organic dielectric materials [27].

| Material                  | Preparation method | Capacitance [nF/cm <sup>-2</sup> ] | Dielectric constant |  |

|---------------------------|--------------------|------------------------------------|---------------------|--|

| Polystyrene               | Spin-coated        | 19                                 | 2.6                 |  |

| Poly(methyl methacrylate) | Spin-coated        | 19.5                               | 3.5                 |  |

| Poly(vinyl phenol)        | Spin-coated        | 7.4                                | 6.4                 |  |

| Poly(vinyl alcohol)       | Spin-coated        | 17.8                               | 10                  |  |

| Benzocyclobutene          | Spin-coated        | 47                                 | 2.65                |  |

| Parylene C                | Vapour deposited   | 2.2                                | 3.1                 |  |

| Cyanoethylpullulan        | Spin-coated        | Not given                          | 12                  |  |

2.1 [2].

## Polymer Dielectrics

Polymers that can be deposited by spin-coating, dip-coating or inkjet-printing present a second major class of materials for the gate dielectric, since most organic polymers are insulators by nature. It has been reported that several polymers show excellent insulating characteristics with very low leakage currents. Representative polymers are polystyrene (PS), poly(methyl methacrylate) (PMMA), poly(vinyl alcohol) (PVA), poly(vinyl phenol) (PVP), benzocyclobutene (BCB), parylene C and cyanoethylpullulan (CYEPL). These are listed in Table 2.2 and their chemical structures are shown in Figure 2.6. Common materials such as PS and PMMA were the first polymers to be used as gate dielectrics. However, PVA and PVP are two of the most widely used polymer dielectric materials. These can be deposited onto organic semiconductors because the solvents (aqueous for PVA and ethanol for PVP) for these materials are orthogonal to those used for the semiconductor. Furthermore, the robustness of these two materials can be enhanced by cross-linking, using chemical agents such as melamine-co-formaldehyde or hexamethylene tetraamine. Such materials generally show low capacitances and the corresponding OTFTs operate at relatively high voltages. In contrast, OTFTs with siloxane cross-linked ultra-thin polymeric films generated by spin coating have recently shown the encouraging results of high capacitance (300 nF cm<sup>-2</sup>), insolubility and low leakage currents (10<sup>-8</sup> A cm<sup>-2</sup>) [29–32]. A robust siloxane network formed by chemical agents (e.g. 1,6bis(trichlorosilyl)hexane) significantly improves the insulating quality, allowing films as thin as 10 nm to be produced.

Figure 2.6: Chemical structure of (a) polystyrene (PS), (b) poly(methyl methacrylate) (PMMA), (c) poly(vinyl phenol) (PVP), (d) poly(vinyl alcohol) (PVA), (e) benzocyclobutene (BCB) and (f) parylene.

## Self-assembled Monolayer (SAM) Dielectrics

Ultra-thin SAMs are also very promising dielectrics for low-voltage OTFTs because of the short chain length ( $\sim$ x nm) and dense packaging of the SAMs. The SAMs, which have been used as surface treatments, can function as a dielectric under careful preparative conditions. There are two approaches for generating molecular insulating layers: bottom-up and top-down. The former technique, where the final insulating layer is created by self-assembly from a precursor followed by one or more chemical modifications, shows excellent electrical characteristics but requires multiple chemical reactions. The other approach is the use of preliminarily modified molecules which can form dense SAMs such as alkyltrichlorosilane with an aromatic end-group. It has been reported that SAMs with a thickness of 2.5 nm provide a capacitance near 1  $\mu$ F cm<sup>-2</sup>. The leakage current density is less than  $10^{-9}$  A cm<sup>-2</sup> for fields up to 14 MV cm<sup>-1</sup> [33]. However, pathways for integration into large-volume

coating processes are less obvious because of defects in the SAMs arising from the imperfect surface of the target film.

### Multilayer and Nanocomposite Dielectrics

Multilayers, which are combinations of inorganic/organic dielectrics with organic/inorganic monolayers or thin polymer phases, have been investigated to modify the surface of dielectric materials. The additional layer normally helps to smooth the roughness of the dielectric surface and improve the crystalline grain growth of the active materials. Examples of additional SAMs are octadecyl-trichlorosilane (OTS) on silicon oxide dielectrics [34], alkyl phosphonic acid monolayers on alumina dielectrics [35] and octadecyl-trimethoxysilane (OTMS) on ziconium oxide dielectrics [36]. Polymers such as polystyrene [37] or poly( $\alpha$ -methylstyrene) [38] on oxide dielectrics have also been used to improve the performance of OTFTs. It has been reported that the use of an additional layer has a significant improvement on the device characteristics (e.g. field-effect mobility). However, the effect on the dielectric properties is less marked because the thickness of the additional layer is much less than the thickness of the gate dielectric.

A further method is to blend ceramic and polymeric materials on the nanoscale in order to generate nanocomposite dielectrics. For example, the value of the dielectric constant can be increased from 3.5 for the traditional polymer dielectric (PVP) to 5.4 for the nanocomposite dielectric containing 7 % nanoparticles (TiO<sub>2</sub>-PVP) [39].

#### 2.4.4 Contact Resistance