## **Durham E-Theses**

# Characterisation of crosstalk defects in submicron CMOS VLSI interconnects

Israsena, Pasin

#### How to cite:

Israsena, Pasin (1999) Characterisation of crosstalk defects in submicron CMOS VLSI interconnects, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/4387/

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

## Characterisation of Crosstalk Defects in Submicron CMOS VLSI interconnects

## Pasin ISRASENA

Thesis for qualification for degree of Master of Science

University of Durham

School of Engineering and Computer Science

January 1999

The copyright of this thesis rests with the author. No quotation from it should be published without the written consent of the author and information derived from it should be acknowledged.

#### **Abstract**

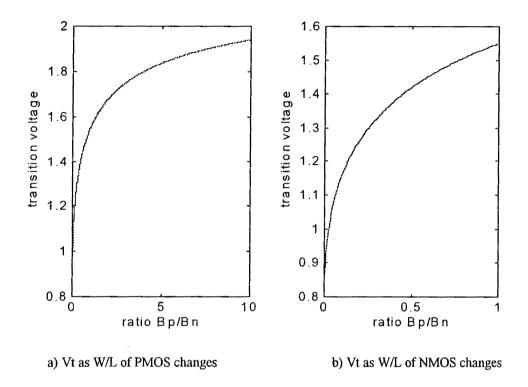

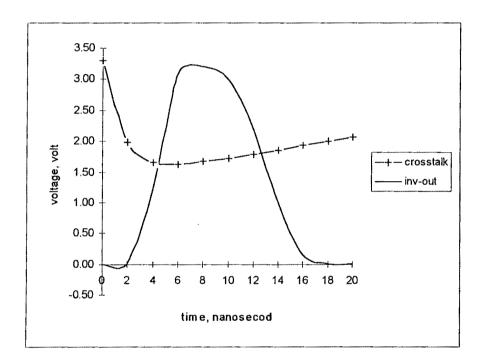

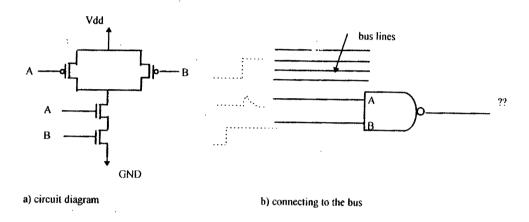

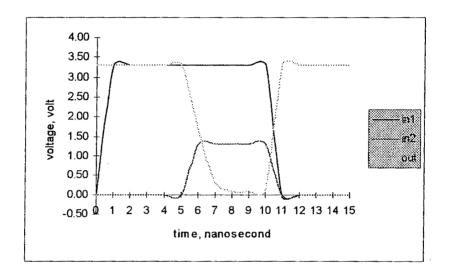

The main problem addressed in this research work is a crosstalk defect, which is defined as an unexpected signal change due to the coupling between signals or power lines. Here its characteristic under 3 proposed models is investigated to find whether such a noise could lead to real logic faults in IC systems. As a result, mathematical analysis for various bus systems was established, with 3 main factors found to determine the amount of crosstalk: i) how the input buffers are sized; ii) the physical arrangements of the tracks; and iii) the number of switching tracks involved. Minimum sizes of the width and separation lead to the highest crosstalk while increasing in the length does not contribute much variation. Higher level of crosstalk is also found in higher metal layers due mainly to the reduced capacitance to the substrate. The crosstalk is at its maximum when the track concerned is the middle track of a bus connected to a weak buffer while the other signal lines are switching. From this information, the worse-case analysis for various bus configurations is proposed for 0.7, 0.5 and 0.35  $\mu$  CMOS technologies. For most of conventional logic circuits, a crosstalk as large as about a half of the supply voltage is required if a fault is to occur. For the buffer circuits the level of crosstalk required depends very much on the transition voltage, which is in turn controlled by the sizing of its n and p MOS transistors forming the buffer. It is concluded that in general case if crosstalk can be kept to be no larger that 30% of the supply voltage the circuit can be said to be very reliable and virtually free from crosstalk fault. Finally test structures are suggested so that real measurements can be made to verify the simulation results

## Table of content s

| Chapter 1 Introduction                                                      | 1-1  |

|-----------------------------------------------------------------------------|------|

| 1.1 General introduction                                                    | 1-1  |

| 1.2 Introduction to important concepts in submicron CMOS circuits           | 1-1  |

| 1.3 Previous work in the field                                              | 1-6  |

| 1.4 Thesis outline                                                          | 1-6  |

| Chapter 2 Modelling of transistors and interconnects                        | 2-1  |

| 2.1 Modelling of the MOS transistor                                         | 2-2  |

| 2.2 Scaling of MOS transistor                                               | 2-2  |

| 2.3 Modelling of VLSI interconnects                                         | 2-5  |

| 2.3.1 The Lumped Capacitor Model                                            | 2-6  |

| 2.3.2 The Lumped Resistor-Capacitor Model                                   | 2-8  |

| 2.2.3 The Distributed RC Models                                             | 2-9  |

| 2.3.4 Transmission model                                                    | 2-11 |

| 2.4 Resistance, Capacitance and Induction Calculations                      | 2-15 |

| 2.4.1 Calculation of track resistance •                                     | 2-16 |

| 2.4.2 Calculations of self and mutual capacitances within the tracks        | 2-17 |

| 2.4.2.1 The parallel-plate capacitor model                                  | 2-17 |

| 2.4.2.2 The schwartz-Christoffel model                                      | 2-18 |

| 2.4.2.3 The Lewis model                                                     | 2-18 |

| 2.4.2.4 The Numerical Methods for Capacitance Calculation                   | 2-20 |

| 2.4.2.5 The Matthaei's Method for Capacitance Calculation                   | 2-22 |

| 2.4.3 Calculation of track inductance parameter                             | 2-24 |

| 2.5 Summary of the chapter                                                  | 2-26 |

| Chapter 3 Characterisation of crosstalk                                     | 3-1  |

| Crosstalk in Two Signal Lines                                               | 3-1  |

| 3.1 Crosstalk in Simple Two Paraflel Line System                            | 3-2  |

| 3.1.1 Crosstalk in Two Identical Lines With Identical Source Resistances    | 3-3  |

| 3.1.2 Crosstalk in Two Identical Lines with Different Source Resistance     | 3-9  |

| 3.1.3 Crosstalk in Two Parallel-Line System with Different Line Capacitance | 3-15 |

| 3.1.4 Crosstalk in An Arbitrary Two Parallel-Line System                    | 3-17 |

| 3.2 Crosstalk in Buffered-Line System                                       | 3-18 |

| 3.3 Influence of Different Tracks on The Crosstalk                          | 3-23 |

| 3.4 Crosstalk in An Irregular Structured Two-Line System                    | 3-27 |

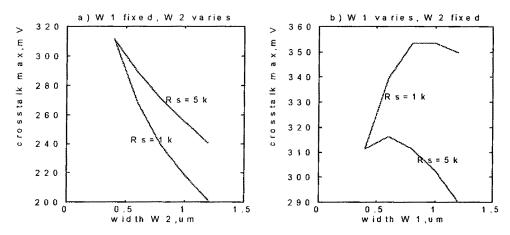

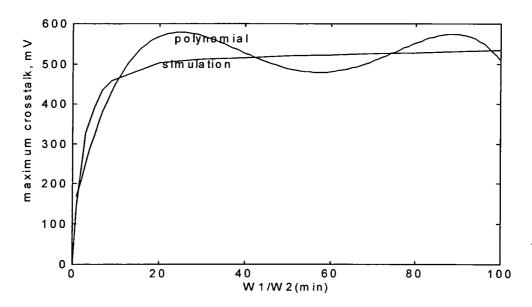

| 3.4.1 Crosstalk in Lines of Different Width                                 | 3-28 |

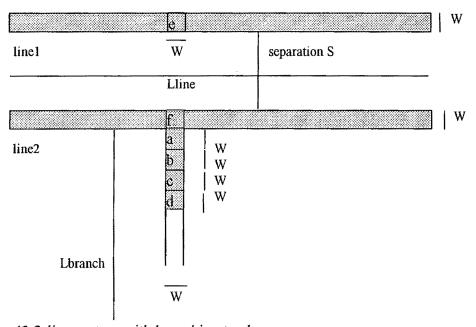

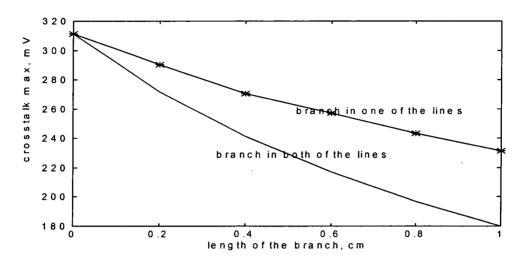

| 3.4.2 Crosstalk in Lines with Branches                                      | 3-30 |

| 3.5 Worst-case Analysis of Crosstalk in a Two Line System                   | 3-32 |

## CHAPTER 1 Introduction

#### 1.1 General Introduction

In the modern world, integrated circuits play a significant role in the electronics industry. The ability to integrate millions of transistors into a single chip offers enormous advantages in terms of yield and performances, allowing more complex systems to operate at higher speed with less power. In the earlier days circuit performance was mainly determined by the switching characteristics of its transistors. But as efforts have been made to increase circuit density by shrinking the transistor size further, undesired effects due to interconnections, which were regarded as insignificant in the past, must now be taken into account. These effects, as will be seen later, can be of various forms, such as delay or noise.

The main problem addressed in this research work is crosstalk defects, which are defects caused by one form of the noise called crosstalk. Generally, crosstalk is defined as an unexpected signal change due to the coupling between signal or power lines. For any engineer or designer designing an integrated circuit, the ability to predict or estimate the amount and nature of crosstalk likely to occur is desirable, at least from a reliability point of view. The scope of this research work is therefore to investigate the characteristics of the crosstalk which occurs in integrated circuits and to underline the effect of this on CMOS circuits. A test structure will also be suggested so that real measurements can be made to verify the simulation results.

## 1.2 Introduction to important concepts in submicron CMOS circuits

It is essential to understand the trend of CMOS technology in order to appreciate the reasons behind the emergence of this relatively new problem. The transistor has come a long way since it was first integrated into a semiconductor microchip in 1958. Generally it has now been accepted that the Complementary Metal Oxide

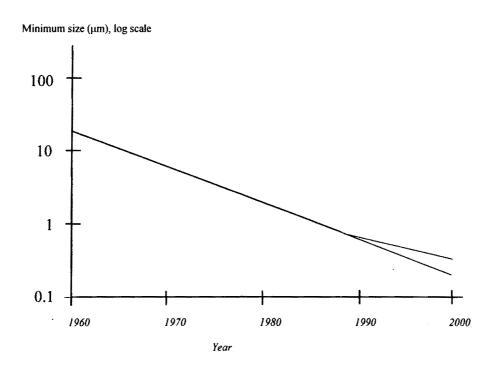

Semiconductor (CMOS) Field Effect Transistor is the technology of choice for digital circuits. This is largely due to its low power nature, as most of the power consumption occurs only during the switching period, and to the fact that its switching speed has been vastly improved to a level comparable to that offered by other families of transistors such as bipolar devices. There are actually several ways in which this improvement in speed can be achieved. One of the main method is by reducing the transistor size, which is measured in term of the minimum channel length. Figure 1 shows the technological trend of CMOS and its future prediction[41]. Features as small as 0.28 µm are being used in today consumer products such as the recently launched Intel's PentiumII and research is well underway for sub 0.1 µm devices, moving us into the nanotechnology and the era of ULSI (Ultra Large Scale Integration).

Figure 1. Technology trend in CMOS

To illustrate how this reduction in transistor size can result in speed increasing, table 1 shows the effects of *ideal* scaling, where the MOS device is equally scaled in five dimensions- the three physical dimensions, voltage supply level and doping concentration, on various transistor parameters. In this *ideal* scaling, the electric filed pattern of the smaller device is identical to that of the larger one.

| Parameter                                                                                  | Scaling Factor   |  |  |

|--------------------------------------------------------------------------------------------|------------------|--|--|

| Dimensions $(W,L,t_{ox},X_j)$                                                              | 1/S              |  |  |

| Substrate doping (N <sub>SUB</sub> )                                                       | S                |  |  |

| voltages $(V_{DD}, V_{TN}, V_{TP})$                                                        | 1/S              |  |  |

| Current per device( $I_{DS} \alpha \frac{W \varepsilon_{ox}}{L t_{ox}} (V_{DD} - V_t)^2$ ) | 1/S              |  |  |

| Gate capacitance $(C_g = \varepsilon_{ox} \frac{WL}{t_{gox}})$                             | 1/S              |  |  |

| Transistor on-resistance (R $_{\rm tr}$ $\alpha$ $\frac{V_{DD}}{I_{DS}}$ )                 | 1                |  |  |

| Intrinsic gate delay ( $\tau = \frac{C_g \Delta V}{I_{av}} = R_{tc} C_g$ )                 | 1/S              |  |  |

| Power-dissipation per gate $(P = IV)$                                                      | 1/S <sup>2</sup> |  |  |

| Power-delay product per gate ( $P \times \tau$ )                                           | 1/S <sup>3</sup> |  |  |

| Area per device ( A = WL)                                                                  | 1/S <sup>2</sup> |  |  |

| Power-dissipation density (P/A)                                                            | 1                |  |  |

## Table 1 Scaling of MOS transistor

It can be observed from the table that as the dimensions of the transistor are scaled down by a factor of S the intrinsic gate delay which dictates the speed of the circuit is also reduced by the same factor. Thus the circuit can potentially be operated at higher speed. Ideally, according to the table, the supply voltage is also scaled down and hence the circuit would consume less power. This is, however, not always the case as it would be difficult and costly in practise, even though possible, to have multiple supply voltages. The topic regarding transistor scaling will be discussed in more detail in the next chapter. It is sufficient enough here to appreciate the basic idea behind transistor scaling and its main benefits in terms of packing density and increasing in speed.

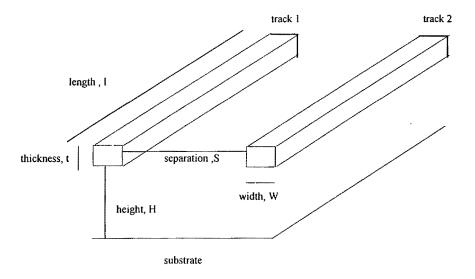

Digital integrated circuits, however, do not contain only transistors. There exist also the second basic components; the interconnections. The term interconnection in integrated circuits is generally used to describe metal tracks which connect the transistors together to form circuits. The basic tracks structures and parameters are as shown in figure 2. The fact that the tracks lie above the substrate and are separated from it by a dielectric, SiO<sub>2</sub> in a typical IC, means that they will possess a self capacitance (capacitance to the substrate). In earlier technology this wiring capacitance is much less than that of the gate capacitance. For example, 7 µm NMOS technology would typically have a gate capacitance of 20fF per minimum size of transistor. A transistor with W/L = 20 would therefore have a gate capacitance of 400fF. With the die size of the chip typically only a couple of mm<sup>2</sup>, a line longer than 1mm is not very likely. One millimetre of the track would contribute only 200fF, hence less than that of the transistor gate. Generally therefore for the older technology such as the 7 µm, circuit behaviour is dominated by the transistor gate capacitance. This is obviously not true for smaller technologies. A 0.7 µm technology would have its gate capacitance of only 40fF(W/L = 20), still much less than that of the line even though the wiring capacitance is also changed because of the change in t<sub>ox</sub>. The behaviour, especially the speed, of the circuit in this case is clearly dictated by the lines rather than the transistors themselves.

Figure 2 Basic interconnection parameters

When transistors are scaled down, all the interconnects will also be reduced by the same factor. It is interesting to note that even though the packing density is increased as a result of scaling, the actual die size is likely to be increased. This is due to the modern demand for much more complex circuits making it very difficult to retain the die size even with the improved packing density. This leads to two concepts of interconnections: a local interconnect where it obeys the scaling rule and a global interconnect where its length is actually increased by the same scale as the dimension of the die. Table 2 summarises the scaling effects on interconnects.

| Parameter                                                                                          | Scaling factor                     |  |  |  |

|----------------------------------------------------------------------------------------------------|------------------------------------|--|--|--|

| Cross sectional dimensions ( $W_{int}$ , $H_{int}$ , $t_{ox}$ )                                    | 1/S                                |  |  |  |

| Resistance per unit length( $R_{int} = \rho_{int} \frac{1}{W_{int} H_{int}}$ )                     | $S^2$                              |  |  |  |

| Capacitance per unit length( $C_{int} = \varepsilon_{ox} \frac{W_{int}}{t_{ox}}$ )                 | 1                                  |  |  |  |

| RC constant per unit length ( R <sub>int</sub> C <sub>int</sub> )                                  | $S^2$                              |  |  |  |

| Local interconnect length( l <sub>int</sub> )                                                      | 1/S                                |  |  |  |

| Local interconnection RC delay ( R <sub>int</sub> C <sub>int</sub> l <sup>2</sup> <sub>loc</sub> ) | 1                                  |  |  |  |

| Die size (D <sub>c</sub> )                                                                         | S <sub>C</sub> (chip scale factor) |  |  |  |

| Global interconnection length (lint)                                                               | $S_{C}$                            |  |  |  |

| Global interconnection RC delay ( $R_{int}C_{int}l_{int}^2$ )                                      | $S^2S_C^2$                         |  |  |  |

| Transmission line time flight ( $l_{int}/v_C$ )                                                    | $S_{C}$                            |  |  |  |

Table2 Ideal Scaling of Local and Global interconnections

It can be seen from the table that global interconnects which apply to any long bus lines in the circuit have their delays increased where as in the local interconnect case, the delay remains the same. The increase in delay will slow down the circuit and may even cause problems for some asynchronous designs. In addition to this, since the global interconnect delay  $S^2S_C^2$  is actually independent of driver size, it can not be solved by simply increasing the driver size.

The problem associated with scaling of interconnects is not only confined to signal delay. In reality vertical parameters such as the line thickness  $H_{int}$  and the height of the line above the substrate  $T_{ox}$  are not actually scaled down as much as that in the vertical plane due to difficulties in processing. The relatively larger  $H_{int}$  and  $T_{ox}$  make the capacitive coupling between the lines which were negligible in larger technologies more significant. The effects of these scaled interconnects and transistors on the capacitive coupling between lines are investigated in detail in the next chapters and it is the aim of this work to observe and explain the faults caused by such a noise.

#### 1.3 Previous work in the field

The problem of capacitive coupling between lines causing crosstalk is not new. It has long been studied extensively in microwave and RF circuits. A number of papers have also been reported for case of the crosstalk in digital TTL and ECL circuits [1][2] [3]. These results can not, however, be applied directly to the modern CMOS ICs as they tended to treat the interconnects as a lossless lines and to neglect the line capacitance. It is interesting to note that when it comes to VLSI circuits, research has been concentrated mainly on how to achieve an accurate model for the track. Some of the first papers which reported these modelling methods are [4][5][6][7]. Specialised textbook such as that by Goal[8] talks exclusively about modelling and simulation of VLSI interconnects. Research has also been carried out at the University of Durham on the modelling of interconnect and this project builds on the results presented by Mahoney [9]. Even the most recent papers such as those of N.D Arora or N.D. Delorme [10][11] still give an emphasis on accurate modelling of the tracks. The importance of theses papers to this research is that they provide a suitable track model which is required for accurate simulation of crosstalk.

#### 1.4 Thesis outline

The thesis is organised into 6 Chapters:

<u>CHAPTER</u> 1 is a general introduction. It provides the basic idea of crosstalk and its potentially damaging effects on integrated circuits. It also illustrates how the problem

has been raised and what kind of work has been going on regarding it. The chapter provides the aim of the thesis and it's organisation.

CHAPTER 2 It is very important to have accurate models for the transistors and tracks which are to be used for crosstalk measurements based on simulations. Chapter 2 therefore gives extensive discussion about various ways in which transistor and track models can be realised. This can be problematic especially for the modelling of tracks as the methods vary considerably depending on the school of thought. Suitable models are chosen and will be used throughout the research work.

CHAPTER 3 and 4 deal with the characterisation of crosstalk. Once suitable models have been established, investigations are carried out to observe how crosstalk can be influenced by physical parameters of the track such as its length or its thickness, and by transistor parameters such as its size or supply voltage. Various circuit layouts, investigating the number of lines and irregular line structures are also considered. As a result of these investigations, mathematical equations describing various relationships between the crosstalk and certain circuit parameters are given. Susceptibility analysis will also be disscussed as a useful first-hand analysis for any designer concerned with the crosstalk effects.

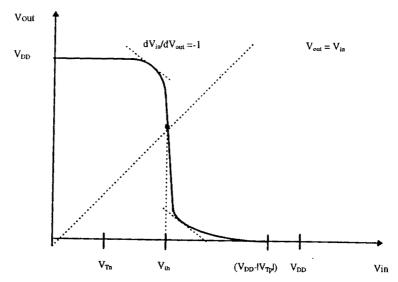

<u>CHAPTER</u> 5 Having established a knowledge of the characteristics of the crosstalk which may occur in CMOS circuits, the next step is to investigate whether this crosstalk can result in any serious logic faults. It will be seen that it is indeed possible under certain circumstances for logic faults to occur. Examples are given and ways to reduce this effect are discussed.

<u>CHAPTER</u> 6 All the work presented so far has been under simulations. It is, however quite important to verify the simulation results with the values obtained by real measurement if they are to be proved reliable. Measuring real crosstalk is not straight forward and a special test circuit may be needed. A simple yet effective test circuit is proposed here and its method is tested by SPICE simulation.

<u>CHAPTER</u> 7 is a conclusion. It concludes and summarise all the work done within this research. Further work which could complement and contribute more in depth regarding this topic are also suggested.

## **CHAPTER 2** Modelling of transistors and interconnects

Once it has been decided that crosstalk may have significant effect on integrated circuit reliability and that the understanding of its characteristics is desirable, a question is raised: How can we actually measure the crosstalk? One answer which seems quite straight forward at first is that this can be done by fabricating some real sample circuits of different parameters and then taking measurements from them. This method however would require a lot of sample circuits and is likely to be time consuming and high cost. Measuring the crosstalk directly from the sample chips itself may not even be as simple as it may seem and that special test circuit may be required. This method does not look after all to be very promising.

The alternative is to use simulation. Computer Aided Design (CAD) has been revolutionary to the electronic industries. With programmes such as SPICE (Simulation Programme with Integrated Circuit Emphasis), originally developed by the University of California in Berkeley, having proved to be a backbone for circuit designs. Using this programme, designers are provided with opportunities to try and test their circuits extensively to make sure that they function as expected before they are fabricated.

However, in order to use CAD simulation as a mean for initial design and verification of the circuit, it is necessary that the characteristics of all components within the circuits are correctly represented. In other words, this means that all the components must be correctly 'modelled' according to their real behaviour. For crosstalk simulation this implies that the two main components, the transistors and their interconnects must be correctly modelled. The next sections therefore discuss various methods under which transistor and interconnects models can be realised.

## 2.1 Modelling of the MOS transistor

The characteristics of any particular transistor depend greatly on its technology, or more precisely on how it has been processed. SPICE allows process and device parameters to be used to represent or 'model' any unique transistor. These parameters are normally obtained from measurements of the real device. They will provide a wide range of information about the device which can vary from any physical parameters such the oxide thickness to device characteristics such as its threshold voltage or mobility.

· 2:

There are actually several levels of accuracy/complexity at which transistors can be modelled. Level 1 is the starting level where a small number of parameters are required. This level should prove to be enough for a very basic transistor. Higher levels require additional parameters but will result in a more accurate simulation of circuit behaviour. These levels are therefore naturally suitable for more advanced transistors. Typically, LEVEL3 is adequate for most of the transistors including those from submicron processes. For a very deep sub-micron transistor such as  $0.1\mu m$ , new models are being developed. Table 3 shows typical CMOS device parameters and their SPICE correspondence.

## 2.2 Scaling of MOS transistor

Given the availability of any particular MOS transistor model, other smaller and more advanced models can in theory be derived using methods governed by scaling rules. Ideally, these new 'theoretically scaled' transistors would still maintain certain expected characteristics. Within each scaling rule, scaling of a MOS transistor is done by adjusting (i.e. dividing) some scaleable parameters of the transistor by certain values (scaling factors). Different scaling rules consist of different combination of scaling factors. The ideal scaling rule shown earlier, also known as the Constant Electric Field scaling, is actually just one of three popular rules currently used. Table 4 summarise the three methods, which are:

- 1. Constant Voltage scaling (CV) [12]

- 2. Constant Electric Field scaling (CE) [13]

- 3. Quasi-Constant Voltage scaling (QCV) [12]

| Parameter         | SPICE keyword | Description                               |

|-------------------|---------------|-------------------------------------------|

| -                 | LEVEL         | Model level                               |

| $V_{TO}$          | VTO           | Zero-bias threshold voltage               |

| t <sub>ox</sub>   | TOX           | Gate oxide thickness                      |

| $N_a$             | NSUB          | Substrate doping                          |

| $N_{FS}$          | NFS           | Surface fast state doping                 |

| $\mu_{o}$         | UO            | surface mobility                          |

| $v_{max}$         | VMAX          | Maximum drift velocity of carries         |

| η                 | ETA           | Static feedback on threshold voltage      |

| κ                 | KAPPA         | Saturation field factor                   |

| θ                 | THETA         | Mobility degradation factor               |

| δ                 | DELTA         | Width effect on threshold voltage         |

| $x_j$             | XJ            | Junction depth                            |

| $\hat{C_j}$       | CJ            | Zero-bias bulk junction capacitance       |

| $J_s$             | JS            | Bulk junction saturation current          |

| $J_{sw}$          | JSW           | Sidewall bulk junction saturation current |

| $M_{j}$           | MJ            | bulk junction grading coefficient         |

| $\varnothing_{j}$ | PB            | junction potential                        |

| $C_{jsw}$         | CJSW          | Zero-bias side wall capacitance           |

| $M_{jsw}$         | MJSW          | Sidewall capacitance grading coefficient  |

| $C_{GDO}$         | CGDO          | Gate-drain overlap capacitance            |

| $C_{GSO}$         | CGSO          | Gate-source overlap capacitance           |

| $C_{GBO}$         | CGBO          | Gate-bulk overlap capacitance             |

| -                 | RD            | Drain ohmic resistance                    |

| -                 | RS            | Source ohmic resistance                   |

| L <sub>d</sub>    | LD            | Lateral diffusion from drain to source    |

| $W_d$             | WD            | Lateral diffusion along the line          |

Table 3 Typical CMOS device parameters and their SPICE correspondence

| Parameter                                                                                   | СЕ               | CV                  | QCV                  |

|---------------------------------------------------------------------------------------------|------------------|---------------------|----------------------|

| Dimensions $(W,L,t_{ox},X_j)$                                                               | 1/S              | 1/S                 | 1/S                  |

| Substrate doping (N <sub>SUB</sub> )                                                        | S                | S                   | S                    |

| voltages $(V_{DD}, V_{TN}, V_{TP})$                                                         | 1/S              | 1                   | 1/S <sup>0.5</sup>   |

| Current per device( $I_{DS} \propto \frac{W \varepsilon_{ox}}{L t_{ox}} (V_{DD} - V_t)^2$ ) | 1/S              | S                   | S <sup>0.25</sup>    |

| Gate capacitance ( $C_g = \varepsilon_{ox} \frac{WL}{t_{gox}}$ )                            | 1/S              | 1/S                 | 1/S                  |

| Transistor on-resistance (R $_{\rm tr} \propto \frac{V_{DD}}{I_{DS}}$ )                     | 1                | 1/S                 | 1/S <sup>0.75</sup>  |

| Intrinsic gate delay ( $\tau = \frac{C_g \Delta V}{I_{av}} = R_{tc} C_g$ )                  | 1/S              | 1/S <sup>2</sup>    | 1/S <sup>0.875</sup> |

| Power-dissipation per gate (P = IV)                                                         | 1/S <sup>2</sup> | $S^{0.5}$           | 1/S <sup>0.25</sup>  |

| Power-delay product per gate ( $P \times \tau$ )                                            | 1/S <sup>3</sup> | 1/S <sup>0.75</sup> | 1/S <sup>2</sup>     |

| Area per device ( A = WL)                                                                   | 1/S <sup>2</sup> | 1/S <sup>2</sup>    | 1/S <sup>2</sup>     |

| Power-dissipation density (P/A)                                                             | 1                | S <sup>1.5</sup>    | S <sup>1.75</sup>    |

Table4 Scaling laws of MOS device

It can be seen that the Constant Electric Field scaling (CE) is termed 'ideal' largely from the device physics point of view. By scaling the device in both horizontal and vertical dimensions the device size is dramatically reduced by the factor of S<sup>2</sup> and the gate delay is also significantly improved. Practising the CE scaling, however, can be troublesome. Since each technology would require different supply voltage, any electronic system which comprises chips of different technologies such as the PC board would require multiple power supplies. This can prove to be very ineffective and costly.

The Constant Voltage scaling (CV), by contrast, offers a more practical solution. In this scheme, the dimensions are scaled while the voltages are kept constant allowing a single level supply source to be used. As a result, the Constant Voltage scaling has

actually been one of the most commonly used. It must be pointed out however that the normal operating voltage of 5 volts used in most electronics circuit can not be applied to any CMOS of technology smaller than 0.6 micron. This is due to the effects such as hot carriers, junction or oxide breakdown which would degrade the device reliability. For smaller devices therefore reduction in supply voltage is unavoidable. The other alternative, the Quasi-Constant Voltage scaling (QCV) scheme is regarded as an intermediate scheme between the CE and CV. Here the dimensions are scaled by 1/S while the voltages are by 1/S<sup>0.5</sup>.

In practise, scaling rules have been only used as a reference for development of new models. It would be unwise to create a new SPICE model directly based on an available model with the use of a certain scaling rule. Because there are a number of device parameters which are process dependent and not covered by the rule, using these in the new model could result in incorrect device characteristics. The SPICE models of transistors, therefore are normally obtained from direct measurements or provided by companies or research institutes who created them. The work done here was based on there models available at the department; the 0.7, 0.5 and 0.35 microns. All the simulation has been run using the PSpice package which is one of the commercial versions of the original SPICE. PSpice is a product of MicroSim.

## 2.3 Modelling of VLSI interconnects

The second component which needs to be modelled correctly is the interconnection. By convention it is generally assumed that wires in an integrated circuit are lossless. A lossless line is interpreted as having no capacitance, resistance or inductance. Hence, the voltage at all points in the wire are identical. At first glance the obvious compromise noticed here is that in reality a wire must at least possess some resistance, no matter how small it is. The value may be small enough to be negligible in most cases but it may not be accurate enough when considering a sub-micron VLSI circuit. The argument also applies to the capacitance and inductance inherent in the line. Apart from the self capacitance, the capacitive coupling between signal lines which is the main reason behind the problem of crosstalk must also be modelled correctly if the simulation results are to be valid. The next sections will discuss how interconnect can be

modelled. Effectively this results in various RCL circuits which can be used to represent the interconnect with different accuracy and simplicity.

## 2.3.1 The Lumped Capacitor model

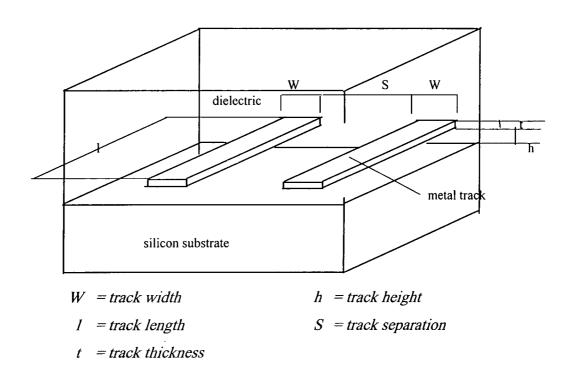

As mentioned earlier, the simplest way to model interconnect is as a lossless line, neglecting all the capacitive, resistive and inductive values. In actual VLSI circuits, however, track capacitance can have a significant effect on the performance of the circuit and its presence is unavoidable. To discuss the reason behind this, first a typical track structure in VLSI interconnect is shown in the following figure 3.

Figure 3 Typical track structure

As can be seen from the figure, interconnections in VLSI basically consist of metal layers deposited over the substrate and surrounded by some dielectric medium. Typically the metal used is Aluminium while the dielectric would be SiO<sub>2</sub>. According to the figure there are five physical parameters which can be used to represent the tracks; the width of the track(w), the track thickness(t), its height above the substrate(h), the length and the separation (s) between the tracks.

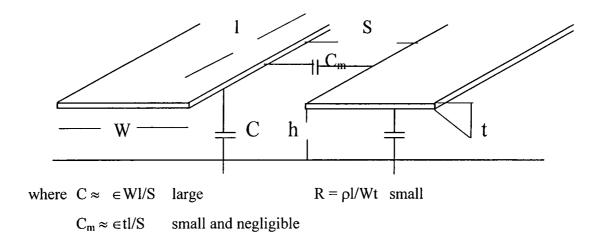

In its simplest form, with the width of the line being relatively large, the capacitive coupling between the lines can approximately be regarded as a result of the equivalent parallel plate capacitance of the cross section of the side of the lines plus some fringing capacitance. In this case the value can be relatively small and hence negligible. The resistance of the line will also be small as the cross-section is relatively large and the line's capacitance is dominated by the parallel plate capacitance between the line and substrate. The idea is summarised in figure 4.

Figure 4 Simplified case for larger tracks

This simplified view works well for larger technology. For the more modern chip however, this model can be insufficient. As the whole chip is being scaled to a smaller and smaller size, not only the transistors are scaled down but also their interconnects. The scaling of interconnect has actually been introduced in table 2 in the first chapter. The important point to note here is that while all of the horizontal parameters such as the width and separation are scaled properly, the thickness and the height which are vertical parameters are not. Due to difficulties in silicon processing it is common that vertically the chip is not scaled as aggressively as in the horizontal dimension. This results in the coupling capacitance having a relatively larger value when compared to the reduced track to substrate capacitance.

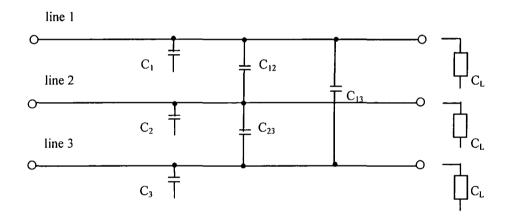

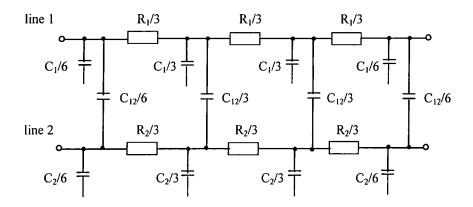

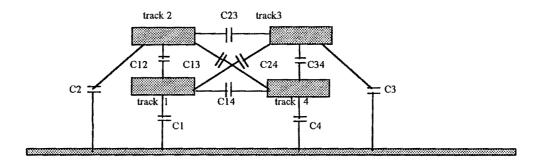

For these reasons, the simplest model which can be used to accurately represent small geometry interconnect must comprise the track capacitance and the coupling capacitance between the lines. The resistance of the track will increase as a result of the scaling. But if the source resistance is large enough the track's resistance may be omitted without any severe effect. The model which includes only capacitance of the tracks and the coupling capacitance is the lumped capacitor model. It is called lumped because, as the name suggests, the capacitors which represent the tracks and coupling capacitance are actually lumped together. Figure 5 shows how a 3-line system can be modelled. The ways by which the capacitive values and the resistance of the tracks, if necessary, are calculated can be quite complicated and will be treated separately in section 2.4.

Figure 5 Lumped Capacitor model for 3 lines system

## 2.3.2 The Lumped Resistor-Capacitor Model (Lumped RC)

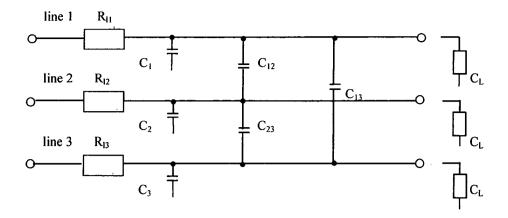

The lumped RC is almost similar to the lumped capacitor model. The only difference is that in this model the track resistance is also taken in to consideration. This is important, for example, if a long bus line is of interest, the longer the line the larger its resistance will be. Resistance per unit length also increases with scaling in more advanced technologies. This is because the size of the track is reduced its cross-sectional area is reduced and hence its resistance will actually increase. Sufficiently large resistance can introduce further problems such as the line delay and therefore its presence can not be neglected. Figure 6 shows an example of a lumped resistor-capacitor model of 3 bus lines.

Figure 6 Lumped Resistor Capacitor model for 3-line system

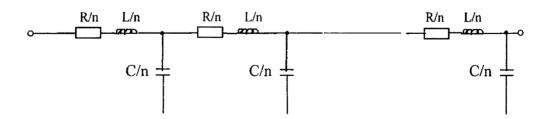

#### 2.3.3 The distributed RC models

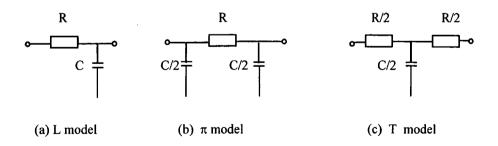

In the previous two models, all the capacitors and resistors which represent the capacitances and resistances of the lines are lumped at one node for each line. In reality, however, the capacitance and resistance of the line are actually distributed along the line and should not be assumed to be lumped at any particular point. This idea has resulted in the introduction of various 'distributed RC models'. The three most popular models are the  $\pi$ , T and L models. Generally speaking, distributed RC modelling can be done by dividing the capacitances and resistances similar to that obtained under the lumped RC model into subsections. Each of the  $\pi$ , L and T models will have its own way of modelling the sub-section. Figure 7 shows sub-section modelling using L,  $\pi$  and T configuration.

Figure 7 L,  $\pi$  and T sub-section models

Between the three models it has actually been shown by Sakurai[14] that the L configuration can results in an error of as much as 30 per cent. The  $\pi$  and T models are consideably better and produce almost identical results. The T model, however, requires

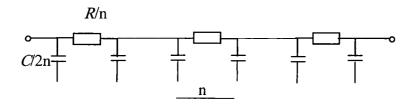

2 nodes per section compared to only one node required by the  $\pi$  model, as seen above. These extra nodes imply more computational activities and introduce unnecessary complexity to the SPICE simulation. Thus, the  $\pi$  model is preferred. Figure 8 shows how a single line can be modelled using n-section  $\pi$  configuration.

figure 8 n-section  $\pi$  model for a single track

According to figure 7, C and R are respectively the line capacitance and resistance used in the lumped model. The number n represent the number of sections the line is divided into. The larger the n the more accurate the model will be. It can actually be shown further that as the number of the subsection n approaches infinity, the line is governed by the equations:

$$\frac{dI}{dZ} = -C\frac{dV}{dt} \qquad \text{and} \qquad \frac{dV}{dZ} = -RI \tag{2-1}$$

Where V and I are voltage and current respectively and Z represent distance along the track. The two equations can actually be combined together to produce the diffusion equations describing voltage and current propagation along an RC line. The equations are:

$$\frac{d^2V}{dZ^2} = RC\frac{dV}{dt} \qquad \text{and} \qquad \frac{d^2I}{dZ^2} = RC\frac{dI}{dt}$$

(2-2)

These equations, even though they represent a more accurate way of modelling the tracks, are not realisable under the SPICE simulations. However it is possible to use large number of subsections so that the results achieved are comparable to that obtained directly from the equations. The problem with this is that it will make the circuit very

complex which may not be entirely desirable. Sakurai has shown that 3 state  $\pi$  model had an error of less than 3 per cent[14] compared to an analytical calculations.

When using the  $\pi$  model for crosstalk analysis, not only the lines are divided into subsections as shown earlier but also the coupling capacitance between them. The way in which the coupling or mutual capacitance can be modelled is exactly the same as the track or self capacitance shown previously. Figure 9 shows the example of a 3-section  $\pi$  modelling of 2-line bus. It can be imagined from the figure that the circuit can get very complex if a system involving multiple lines is of interest and as a result there must be some trade-off between accuracy and complexity. Further information about various distributed RC modelling can be found in [15]-[20]

Figure 9 3-section  $\pi$  model of 2-line bus

#### 2.3.4 Transmission line model

In previous sections, the interconnections were treated either as a lumped capacitive load for general cases or as a distributed RC lines in case of the lines having significant resistances due to the scaling effect. These models should prove to be sufficient for most cases. In an extreme case where the signal wavelength approaches the wire length, however, the transmission line properties of these on-chip interconnections must be observed. To have waveforms with sizes comparable to the lines requires that the lines are sufficiently long and that the circuit is operating at a very high speed. This is increasingly the case as the die size continues to increase and the

operating speed is being pushed higher and higher. Modern CMOS circuitry could require operation speed approaching or even exceeding giga hertz level. This can be very demanding of driving a large load.

The main difference between the models considered so far and the transmission line model is that it takes into the account the effect of inductance. The inductance becomes important as lines get longer and signal speed up causing an increase in *LdI/dt*. Because of the inductance, the current into the line can not be increased indefinitely by reducing the source resistance of the driver as inductors resist changes in the current by generating a reverse electromotive force. This limits the amount of current flowing into the line and introduces a fundamental limit to how fast a voltage/current waveform can travel down the line since a limited current can only charge up a certain length of a capacitive line at a given time period. As a result, the line is no longer equipotential but actually accommodates a travelling wave.

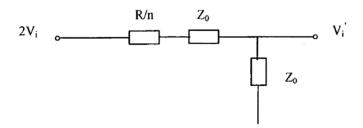

Generally, transmission line modelling is an established subject and has been carried out extensively for the analysis of other areas such as the microstrip in microwave circuits. The basic idea of transmission line calculation is given in appendix A. Here, the derivation of the attenuation along a resistive transmission line (lossy) is shown. Figure 10 illustrates the subsection of a lossy transmission line which has been modelled in a similar fashion to that given in appendix A.

Figure 10 Subsection of a lossy transmission line

In figure 10, R is the total line resistance between the source (x = 0) and the point of observation (x = 1), while n is the number of subsections. The voltage across a subsection can be expressed as:

$$V_{i}^{t} = \left(\frac{2Z_{0}}{2Z_{0} + R/n}\right)V_{i} \tag{2-3}$$

and the voltage at the point of observation is:

$$V(x=1) = \left(\frac{2Z_0}{2Z_0 + r/n}\right)^n V(x=0)$$

(2-4)

Given that:

$$\lim_{n \to \infty} \left( 1 + \frac{x}{n} \right)^n = e^x \tag{2-5}$$

The value of V(x = 1) can then be calculated as n goes to infinity as:

$$\frac{V(x=1)}{V(x=0)} = \lim_{n \to \infty} \left(\frac{2Z_0}{2Z_0 + r/n}\right)^n$$

$$= \lim_{n \to \infty} \frac{1}{\left(1 + \frac{R/2Z_0}{n}\right)^n}$$

$$= e^{-R/2Z_0} \tag{2-7}$$

Using a similar approach, a lossy transmission line can be modelled for the SPICE simulation as given in figure 11. Here  $z_0$  is equal to  $\sqrt{\frac{L}{C}}$

Figure 11 Approximate circuit for SPICE simulation of a lossy transmission line

It is a rule of thumb [39] that the transmission line phenomena become significant when

$$t_r < 2.5t_f \tag{2-8}$$

Where

$t_r$  is the rise time and

$t_f$  is the time-of-flight delay and is defined as

$$t_f = \frac{I}{\nu} \tag{2-9}$$

Where

is the length of the line and

$\nu$  is the propagation speed.

The line can act as a lumped capacitor when:

$$t_r > 5t_f \tag{2-10}$$

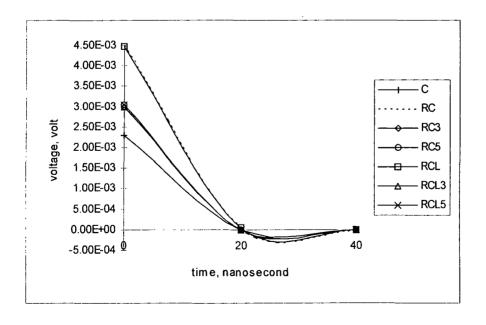

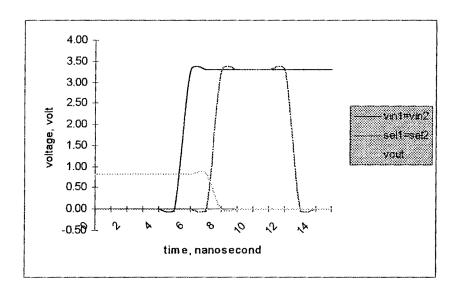

To summarise the effect of different modelling of the track on the waveform, figure 12 shows the output characteristics of tracks modelled using methods discussed previously. These are being driven by identical inverter buffers, with each of the inputs being switched from 0 to 1. The 0.7 micron CMOS transistors were used to realise the inverters while the track parameters were kept at 1 cm in length, 0.7um in thickness and height, and 1 um in width.

Figure 12 Switching characteristics of track differently modelled

From figure 12, it can be seen that the increase in the number of sub-sections in the distributed model at this level has little effect on the output waveform and may introduce unnecessary complexity to the simulation. Another interesting point is that the lumped capacitor model can have a significantly different result from the others if the line resistance is comparable to that of the source. The difference, however will start to get narrower as the source resistance increases and starts to dominate the whole circuit. The transmission line models, according to the figure, produce very similar results to the distributed RC models. This is to be expected as the circuit was operated at an appropriate speed for CMOS ICs which is too slow for the RCL model to start showing any significant effect on the output waveform.

## 2.4 Resistance, Capacitance and Inductance Calculations

Once it has been established which method of track modelling is to be used the next important procedure is to actually calculate the values of these total resistance, capacitance and inductance that the lines possess. These three quantities are dependent of the physical parameters of the tracks such as their thickness and can be difficult to find, especially in the capacitance and inductance cases where they can be influenced by the position and combination of the lines involved. Calculations of these values, especially the capacitance, have actually been the main research interest and several ways of achieving them have been proposed as a result. Generally, these methods can be characterised into two schools of thought. The first group tries to simplify the relationships between the physical parameters and the RCL values into simple equations by accepting to tolerate some error in the results. The other group, in contrast, aims to find the very accurate values of the resistance, capacitance and inductance. They achieve this by mean of numerical analysis which can be very complex. Hence there must be some trade-off when choosing any of these available methods. The next sections discuss ways in which these RCL values can be derived and the most suitable methods to be used in the project are proposed.

#### 2.4.1 Calculation of the track resistance

The calculation of the resistance of the track is probably the most straight forward. It is well known that a resistance of any conductor is directly proportional to its length and is inversely proportional to its cross-sectional area. For VLSI interconnection, the resistance of a track is given by:

$$R = \rho \frac{I}{Wt}$$

Where  $\rho$  is the resistivity of conductor material (2-11)

$W = \text{track width}, \not= \text{track thickness}, I = \text{track length}$

See figure 2, page 1-4

It can be seen from the equation that the resistance of the line increases as the line gets longer. Furthermore, scaling of the track means that the width of the line (W) will also be reduced, resulting in further increasing of the track resistance. High resistance is not desirable as it will introduce further delay which can seriously affect the operating speed of the circuit.

The problem of having large resistance, according to the equation, can ideally be solved to by increasing the thickness of the track. In reality, however, a resistance can only be reduced to some certain point where further increase in the thickness would no longer have any effect. This is due to the skin effect which is inherent in any alternating current. The critical value where the thickness still has effect on resistance is called the skin depth and is given by the equation:

$$\delta = \sqrt{\frac{\rho}{\pi \mu f}} \tag{2-12}$$

Where  $\delta$  is the skin depth,  $\mu$  is the permeability,  $\rho$  and f are the conductivity of the material and the sine wave frequency respectively. It can be seen from the equation that as the frequency increases the skin depth or the critical depth will be reduced. It should be noted, however, that for frequency less than 10GHz the skin depth is greater than the actual thickness of the line[21][22]. Since a real signal has a spectrum of sine wave components which extends up to its bandwidth, this means that only the components of very high frequencies will be affected by the skin depth and that the final resistive

characteristics of the line should not be significantly affected. The skin depth effect is therefore not included in the calculation of track resistance.

#### 2.4.2 Calculations of self and mutual capacitances within the tracks

Methods of calculating the values of the mutual and self capacitance of the interconnection are of great interest as these capacitances are the main factor which can determine the performance of the whole circuit. The following sections, starting from the very basic models, illustrate various methods by which capacitance of the lines can be extracted.

#### 2.4.2.1 The parallel-plate capacitor model

The simplest way of describing the capacitance of the interconnect is to treat it as a parallel plate capacitor. In this case, a capacitor with finite capacitance is formed between the track and the substrate, as shown in figure 13. According to the model, a uniform electric field is formed only between the bottom of the tracks and the substrate. This model omits several facts and so in reality, in order to have this model valid the tracks must be extremely thin so that all the fringe capacitances can be neglected. The lines must also be much closer to the substrate than to each others so that the self capacitance dominates. Having thin lines with relatively large separations and no electric field between them also means that there is no coupling capacitance between any of the line. The model is therefore, rather unrealistic and not ideally suitable for this work.

Figure 13 The parallel-plate model of track capacitance

#### 2.4.2.2 The Schwartz-Christoffel model

The Schwartz-Christoffel model is the improved version of the parallel-plate model. The difference is that it has also taken into account the effects of having an electric field coming from the top of the conductors. This model, however, still fails to recognise the presence of the coupling capacitance between the conductors. The reason behind this is that again the thickness of the tracks is assumed to be negligible. This is due to the fact that originally the model was derived for microstrips used in microwave circuits and that microstrips themselves have much larger width compared to their thickness.

Figure 14 The Schwartz-Christoffel Transformation

#### 2.4.2.3 The Lewis model

In addition to the previous two models, a number of other analytical models have been proposed, some of which were particularly developed for microelectronic structure. These models, as well as being able to calculate the coupling capacitance between the conductors, do not have limitations on the thickness, separation or width of the tracks. The normal procedure with these models would be to consider first the simplest case of two symmetric conductors and then to apply the results to the more general cases. Among the models, the simplest and most convenient way is to describe the wave propagation of a signal along a coupled pair of symmetric lines as a sum of an even and odd mode of propagation. The Lewis method is actually one of the simplest methods which applies the idea and can be used to demonstrate this idea.

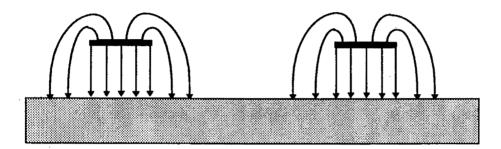

The method was first published in his paper[23]. It was built on the earlier work by K.C. Gupta[24]. Lewis showed that for two adjacent symmetrical conductor strips the propagation modes can be reduced to even and odd modes corresponding to an even and odd symmetry of the field lines. The idea is as shown in figures 15 and 16.

Figures 15-16 Field lines in even and odd modes coupled microstrips

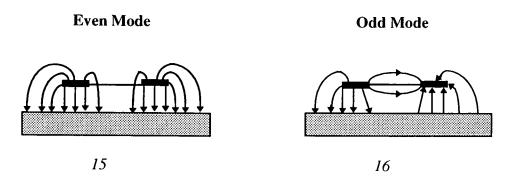

As can be seen from the figure, the difference between the two modes is that in the even mode where the conductors have the same voltage, the electric field exists only between the conductors and the substrate. In the odd mode, by contrast, each of the conductors actually has different voltages so the field lines are split between the substrate and the other conductor. The equivalent capacitance models for these 2 modes can be derived as shown below in figures 17-18.

Figures 17-18 Even and odd mode capacitance models

In the even mode,  $C_p$  is equivalent to the parallel-plate capacitance seen previously.  $C_f$  is the outer fringe capacitance which can be found as a half of the difference between capacitance derived from the Scwartz-Christoffel and simple parallel-plate models. The inner fringe capacitance  $C_f$  will have the value equal to  $C_f$

multiplied by the ratio of the height over the separation. The other two capacitors  $C_{g1}$  and  $C_{g2}$  which are required in the odd model can be extracted from two complex formulas given in the book by Gupta[24].

The Lewis model, even though having proved to be simple enough, has several limitations. One of the conditions is that all the conductors must be of the same size and have identical separations. This can be very impractical as it is more than likely that bus structure in integrated circuit would comprise several tracks of different sizes and separations. The others limitations, such as that it can only be applied to tracks on the same level or that the conductor width must be equal to or less than twice the height of the conductor for multi-conductors system, severely restrict the use of this model in modern conductor system. It is therefore necessary that a more accurate and flexible model should be founded.

## 2.4.2.4 The Numerical Methods for Capacitance Calculation

Numerical techniques can be used to model any arbitrary conductors with a high accuracy. As has been mentioned before, the trade-off would be that the model derived would be very complex and a powerful simulator is required. There are actually three principle numerical techniques which are used to calculate capacitances in arbitrary conductor system namely, the finite element method (FEM) [25][26], the boundary element method (BEM)[27][28] and the partial element equivalent circuit technique (PEEC) [29][30]

## - The finite element method (FEM)

Capacitances can be found under the finite element method by way of partitioning the tracks into a mesh of elements to model the electric field and hence determine its potential distribution. By the application of the electric field on the conductors or the use of a potential energy technique the charge on each conductor can be found and together with the potential distribution the capacitances are derived. The technique can be applied to any non homogeneous conductors, even with a curved geometry.

## - The boundary element method (BEM)

The boundary element method is the most commonly used technique for multiconductor system calculation of intensive capacitive and inductive matrices. This method is known as the Green's function. In many ways it is similar to the FEM. But instead of modelling the electric field as in the FEM case, it is the charges on the conductor that are preferred. The method works by actually replacing all conductor surfaces and dielectric interfaces with the charge distribution that exits in free space to create a potential distribution equivalent to the original system. The electric field of any given point is then calculated under the superposition principle as the cumulative effects of all the changes present in the system. A Green's function is then defined which gives the potential at any point based the distribution of the total charge in the system with the reference point normally being the infinite ground plane. Because only conductor surfaces are needed for the calculation the computational efficiency is dramatically improved.

## - The partial element equivalent circuit technique (PEEC)

Under the third method, the PEEC, the conductors are broken into rectangular cells where equivalent capacitances and inductances are calculated for each cell. The cells are then combined together to form a three-dimensional mesh of capacitors and inductors. The method promises a more efficient way of calculating the conductors parameters as they already inherit the three dimensional structure in each cell. The approximation of each cell to be rectangular is justifed as the metal conductors in ICs are almost always of rectangular form.

All the three techniques described here provide very accurate ways of calculating capacitance of the conductors. They may differ slightly on ways of achieving the results and the limitations which are posed upon them but for VLSI interconnect the results are mostly comparable, as discussed in [9]. The common feature of these methods, however, is the requirement of a powerful simulator as they are all very computational intensive. A further constrain is also imposed by the fact that the methods generally

require the inversion of extremely large matrices, needing therefore large memory resources. Any alternative method which require less computing while retaining or providing a similar level of accuracy given by these numerical methods is very much desirable. Such a method can actually be realised using Matthaei's model.

## 2.4.2.5 Matthaei's Method for capacitance calculation

The Matthaei's method can be said to be a method which actually combines the ideas of even-odd mode analysis as in the Lewis's case with the boundary element method. It was reported for the first time by Matthaei in his paper in 1992[31]. The idea is mostly similar to BEM. But instead of determining the charge distribution through the solution of the Green's function, a very complex procedure, it further simplifies the model by allowing two charge basic functions as a mean of modelling each side of the conductor. For the whole circuit therefore, a square matrix of only eight times the total number of conductors is required, significantly reducing the computational requirements.

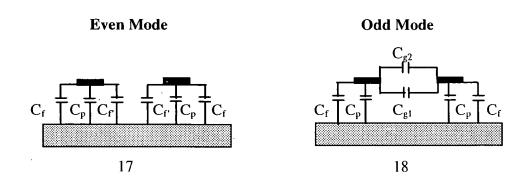

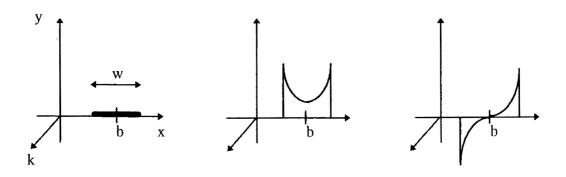

The two charge functions are almost similar to the even and odd mode functions used in Lewis's method. The only difference is that rather than describing the electric field or equivalent capacitance as in Lewis's method, they actually describe the charge distribution within the conductor. Figure 19a shows the cross-section of a conductor of width W in x-y plane. Its length is in the k plane with direction into and out off the paper. Figure 19b and c show the corresponding odd and even charge functions.

Figure 19 a) The cross-sectional trip b) Its even function c) Its odd function

2 - 22

According to the figure, it can be shown[40] that for the even-symmetric function the potential arising from the charge distribution at any point z in the complex plane is:

$$\phi_e(z,b,w) = q\left(\frac{1}{\varepsilon_0}H_e(z,b,w)\right)$$

(2-13)

where

$$H_e(z,b,w) = \left(-\frac{1}{2\pi}\right) \operatorname{Im}\left(\arcsin\frac{2(z-b)}{w}\right)$$

(2-14)

And for the corresponding odd function, a potential at any point Z is given by:

$$\phi_o(z,b,w) = g\left(\frac{1}{\varepsilon_0}H_o(z,b,w)\right)$$

(2-15)

where

$$H_o(z,b,w) = \operatorname{Re}\left((z-b) - \operatorname{sign}\left(\operatorname{Re}(z-b)\right)\sqrt{(z-b)^2 - \left(\frac{w}{2}\right)^2}\right)$$

(2-16)

In these equations, w is the width of the conductor, b is the position of the centre of the conductor and  $\varepsilon_0$  is the dielectric constant. The constant g in equation (2-15) will be cancelled out in later equations since the odd-symmetric distribution has a net charge of zero.

Matthaei's method has actually been studied extensively by P. Mahoney at the University of Durham and a MSc thesis has been produced as a result[9]. Comparisons between this model and others have been extensively discussed and Matthaei's method showed to be the favourable method for VLSI interconnection modelling. The method has proved to have reasonably accurate results while requiring only minimal amount of computations. It can also be applied to any arbitrary system consisting of tracks of different sizes lying on different levels, making it very versatile. The work here will therefore continue to use the Matthaei's method as a mean of calculating the capacitance of the tracks. The following table shows an example of a capacitive matrix derived using Matthaei's method. The capacitance matrix shown is for a system of 8 conductors,

each with 1  $\mu$ m width, 0.7  $\mu$ m thickness, 0.7  $\mu$ m height above the ground, 1 cm long and 1 um of separation. The symmetry of the matrix can be seen where  $C_{ij}$  is equal to  $C_{ji}$ . This should come as no surprise as they actually represent the same value. It can also be seen that the coupling capacitance between adjacent lines is the most significant capacitance in the system. This again is as expected since the places of these capacitances are directly next to each other with only the dielectric medium between them. It is these values which should dominate the characteristics of the crosstalk.

| j 🔪 i | 1      | 2      | 3      | 4      | 5      | 6      | 7      | 8      |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| 1     | 1690ff | 407.95 | 35.45  | 15.34  | 9.73   | 5.71   | 4.12   | 3.9    |

| 2     | 407.95 | 1820   | 397.37 | 31.04  | 12.9   | 7.18   | 4.68   | 4.12   |

| 3     | 35.45  | 397.37 | 1820   | 396.94 | 30.81  | 12.78  | 7.18   | 5.71   |

| 4     | 15.34  | 31.04  | 396.94 | 1820   | 396.87 | 30.81  | 12.90  | 8.73   |

| 5     | 9.73   | 12.9   | 30.81  | 396.84 | 1820   | 396.94 | 31.04  | 15.34  |

| 6     | 5.71   | 7.18   | 12.78  | 30.81  | 396.94 | 1820   | 397.37 | 35.44  |

| 7     | 4.12   | 4.68   | 7.18   | 12.90  | 31.04  | 397.37 | 1820   | 407.94 |

| 8     | 3.9    | 4.12   | 5.71   | 8.73   | 15.34  | 35.44  | 407.94 | 1690   |

$C_{ij}$  is a coupling capacitance between line i and j , in femto farad  $% \left\{ i\right\} =\left\{ i\right$

Table 5 Example of capacitance matrix derived under Mathaei's method

## 2.4.3 Calculation of track inductance parameter

The final components of interest are the equivalent inductors, even if they are only required in the transmission model. There are several ways to calculate directly the inductance matrix for multiple line interconnection systems. Alternatively the inductance matrix can simply be derived from the capacitance matrix. This is a very interesting alternative since the capacitance matrix is readily available from Mathaei's method, a lot of time and efforts can be spared. The relationship can be found by first consider the transmission line equations describing the voltage and current propagation through the line:

$$-\frac{d}{dZ}[V] = j\omega[L][I]$$

(2-17)

$$-\frac{d}{dZ}[I] = j\omega[C][V]$$

(2-18)

where [L] and [C] are respectively the inductance and capacitance matrices. Voltages and currents in the lines are also represented in vector forms of [v] and [I] respectively. Combining the two equations together would give:

$$\frac{d^2}{dZ^2} [V] = -\omega^2 [C] [V] [L]$$

(2-19)

If we further assume that neither [L] nor [C] are frequency dependent and that all nodes have the same propagation velocity  $\upsilon$  then:

$$[L] = \frac{1}{D^2} [C]^{-1} \tag{2-20}$$

It is quite obvious from the equation 2-20 that ideally the inductance matrix can therefore be found as an inverse matrix of the capacitance matrix multiplied by some constant  $1/v^2$ . This is not quite yet true for silicon-based microelectronics systems since they actually possess different field distributions are complicated due to the fact that different dielectric constants are present for substrate and dielectric. The differences in field distributions will actually result in variations of propagation velocities. Adjustment can be made by introducing a new matrix  $[C_0]$  which is a capacitance matrix derived by considering the system to be in free space with a relative dielectric constant of unity and propagation velocity of the speed of the light in free space c. Together with the fact that for a silicon-based circuits the dielectric materials can be ignored as there is a negligible difference in magnetic permeability between silicon and free space[32]. The inductance matrix is then given by:

$$[L] = \frac{1}{c^2} [C_0]^{-1}$$

(2-21)

The following table shows the resulting inductive matrix derived under these rules. The tracks physical parameters are similar to the ones used in the capacitive matrix example.

| j | 1      | 2      | 3      | 4      | 5      | 6      | 7      | 8      |

|---|--------|--------|--------|--------|--------|--------|--------|--------|

| 1 | 2740   | 662.97 | 219.12 | 93.37  | 48.74  | 29.58  | 20.09  | 15.13  |

| 2 | 662.97 | 2670   | 644.08 | 212.01 | 90.00  | 46.94  | 28.67  | 20.08  |

| 3 | 219.12 | 644.08 | 2670   | 641.71 | 210.91 | 89.50  | 49.44  | 29.58  |

| 4 | 93.37  | 212.01 | 64171  | 2670   | 641.34 | 210.94 | 90.00  | 48.73  |

| 5 | 48.74  | 90.00  | 210.91 | 641.34 | 2670   | 641.71 | 212.01 | 93.35  |

| 6 | 29.58  | 46.94  | 89.50  | 210.94 | 641.71 | 2670   | 644.08 | 219.21 |

| 7 | 20.09  | 28.67  | 49.44  | 90.0   | 212.01 | 644.08 | 2670   | 662.96 |

| 8 | 15.13  | 20.08  | 29.58  | 48.47  | 93.35  | 219.21 | 662.96 | 2740   |

|   | ı      |        |        |        |        |        |        |        |

Table 4 Example of inductance matrix, pH

# 2.5 Summary of the chapter

This chapter provides the theoretical analysis of the possible models for transistors and their interconnections. Accurate models are necessary for the circuit simulation to have its results valid. The scaling laws for MOS transistor can be used as guideline, but for a more accurate and reliable model, the transistor parameters must be extracted directly from real device. For the case of interconnections, modelling involves 2 steps. The first step is to decide how the tracks are best represented in term of RCL network. The results here actually suggest the 3-stage RC  $\pi$  model is the most suitable. Once the type of network is decided, the second step is to calculate the accurate values of these capacitances, inductances and resistances. Various techniques have been discussed with the Matthaie technique is chosen as the best compromise between the accuracy the numerical methods offer and the simplicity provided by several analytical techniques.

# CHAPTER 3 Characterisation of Crosstalk

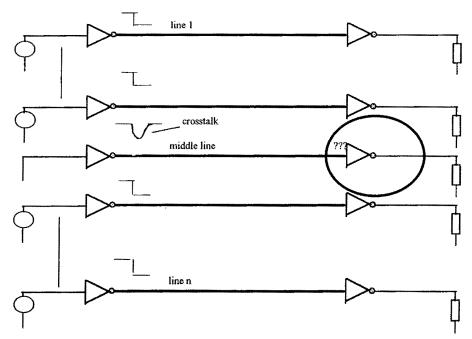

The previous chapter has seen the efforts of modelling the transistor and it interconnects resulting in several possible alternatives. Once suitable models have been identified the next step is to actually design sample circuits based on these models to study the resulted crosstalk through simulations. The ability to anticipate the characteristics of crosstalk that is likely to occur should prove to be a valuable asset when designing modern integrated circuits as any potential malfunctions caused by the crosstalk noise can be avoided. The behaviour of crosstalk depends on various factors. Circuit configurations and technology used can have enormous influence on the crosstalk generated. This chapter, by building up gradually from basic to more complex circuits, reveals relationships between circuits parameters and the associated crosstalk. Emphasis is given on both theoretical and practical points of view.

## Crosstalk in Two Signal Lines

The crosstalk in two signal lines represents the simplest situation where such noise can occur. The relationships involved in a system of two lines are easier to analyse, both mathematically and in simulation, than those produced by complex configurations such as a multiple line system. For these reasons the model can be used to illustrate the basic ideas behind the occurrence of crosstalk, before moving on to the more advanced models. The circuit configuration of a two signal lines system itself can be of various forms. The next sections will therefore analyse these possible configurations, starting from the most basic set-ups. Understanding gained from analysing these models will then be used as a basis for the more advanced set-ups.

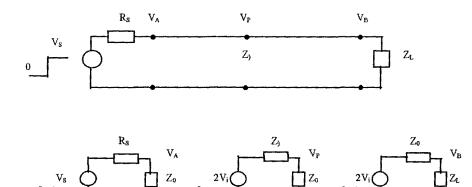

## 3.1 Crosstalk in a Simple Two Parallel Line System

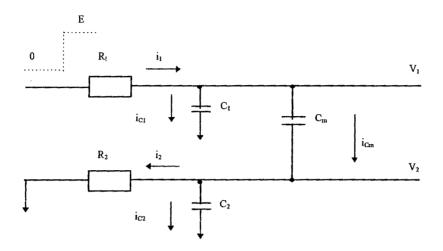

In any circuit where two signal lines are laid parallel a coupling capacitance is formed between them. If the signal in one of the line is switching the coupling capacitance will force the signal in the other line to face a sudden change for a short period of time. The idea is illustrated in the figure below.

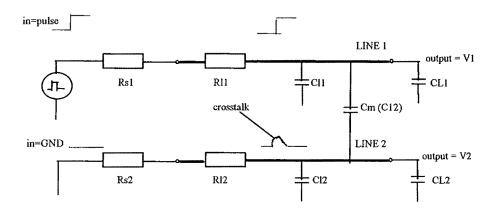

Figure 20 Crosstalk in 2-line system

According to the figure,  $R_{S1}$  and  $R_{S2}$  are the source resistances of line 1 and line 2 respectively. For simplicity both of the lines are shown here using a lumped RC model. Each of the lines has its own self (or line) capacitance  $C_1$  to the ground plane, and is driving a capacitive load  $C_L$ . The input of line 1 is connected to a pulse-signal source via  $R_{S1}$  while line 2 is grounded at its input. The presence of the mutual capacitance  $C_m$  (or  $C_{12}$ ) between the lines results in spike-like signal induced in line 2. The model can be analysed mathematically with varying complexity, depending on the type of the set-up of the parameters chosen. This can generally be divided into four main situations; The first and simplest situation is when the two lines as well as the two sources are identical. The second and the third situations are when only either the source resistances or the lines are identical. For the remaining situation all the parameters can be arbitrary.

#### 3.1.1 Crosstalk in Two Identical Lines With Identical Source Resistors

This case typifies the simplest situation where crosstalk can be analysed. The circuit is similar to that in figure 20, only now the lines and source resistances are required to be identical. Having identical lines implies that the impedances of the lines are equal, resulting in  $R_{11} = R_{12}$  and  $C_{11} = C_{12}$ . For most of the circuits discussed here, the capacitive loads  $C_{L1}$  and  $C_{L2}$  are assumed to be equal. This is done for simplicity reason given the fact that it is very likely that for many cases these buses would be driving identical buffers. If these conditions are met, then it can be shown, as given in appendix B, that the output voltages  $V_1$  and  $V_2$  are:

$$V_{1} = V_{DD} - \frac{V_{DD}}{2} \left[ e^{\frac{-t}{RC}} + e^{\frac{-t}{R(C+2C_{m})}} \right]$$

(3-1)

$$V_{2} = \frac{V_{DD}}{2} \left[ e^{\frac{-t}{RC}} - e^{\frac{-t}{R(C+2C_{m})}} \right]$$

(3-2)

In these equations,  $V_1$  is the response to the switching signal on line 1. It can be seen from the equation 3-1 that  $V_1$  switches from zero to supply voltage  $V_{DD}$  with some delay introduced by two exponential functions. The case can be compared to the normal situation of a lossy line driving a capacitive load. In that case the rise time is controlled by a decaying exponential with time constant of RC, giving  $V_1 = V_{DD} \left(1 - e^{t/RC}\right)$ . In this situation, however, there exits two exponentially decay functions with different time constants RC and R(C+2C<sub>m</sub>) and it is the summation of these which controls the overall switching characteristics of  $V_1$

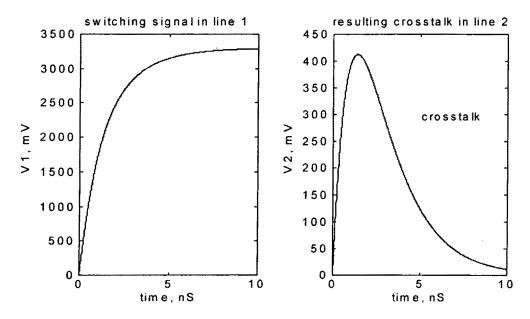

Ideally, if there was no crosstalk line 2 would see no change in the voltage  $V_2$  which would remain at ground. That is obviously not the case here according to equation 3-2. The voltage in line 2 is now actually proportional to the difference between the two exponential functions of equation 3.1. The size of crosstalk is also controlled by the amplitude of the supply voltage. Figure 21 shows the examples of  $V_1$  and  $V_2$  derived

from the equations. The signals are achieved by the use of the MATLAB which is an interactive, matrix-based programme for solving complex numerical problems. MATLAB software is a product of the Mathwork Co.

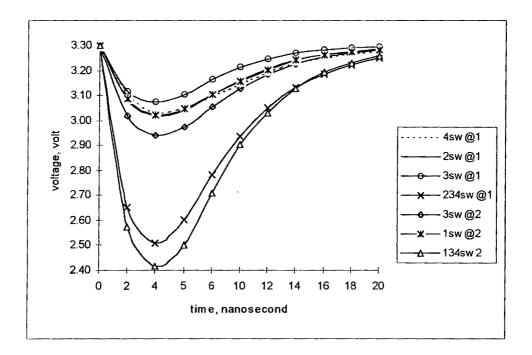

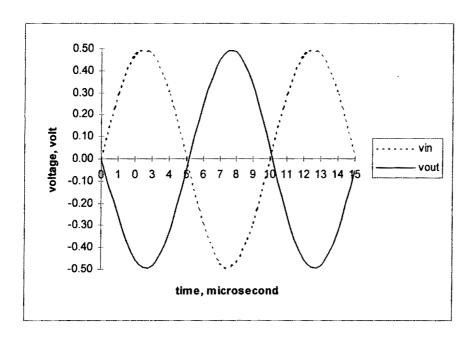

Figure 21 Switching characteristic of line 1 and its corresponding crosstalk in line 2

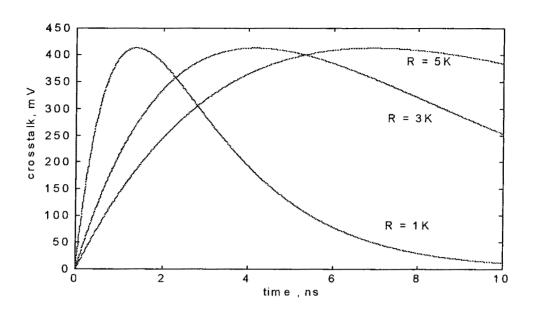

In this example the supply voltage is set at 3.3V. Each of the lines has the combined line and load capacitance of 1 pF, a reasonable value for a typical interconnect of around 1 cm long. The coupling capacitance C<sub>m</sub> is set at 0.5 pF, slightly exaggerated for a better demonstration. The crosstalk generated here has a maximum amplitude of 412.5 mV with it pulse period of around 5 ns. These two parameters are indeed the two major factors which can determine the level of severity of the problem that the crosstalk can cause in the circuit. The higher the amplitude and the wider the width, the more likely that the crosstalk will have significant effects. Normally, the width of the crosstalk is described in term of t<sub>50</sub> - a time taken between two points in the crosstalk where  $V = V_{DD}/2$ . It can be shown that by increasing the size of R, normally be mean of increasing the source resistance R<sub>s</sub>, the width of the crosstalk pulse will be increased. The effect is demonstrated in figure 22. It is understandable that such an effect arises since increasing R<sub>S</sub> means that the current through the capacitors is reduced - hence slowing down the charging and discharging activities. Alternatively it can also be interpreted that by increasing the R, the time constants RC and R(C+2Cm) are increased - resulting in two slower exponential functions.

Figure 22 Crosstalk under different R

It can be argued from the equation that it is not only an increase in R which can increase the width of the crosstalk pulse. Increasing C, the summation of line and load capacitance, will also result in larger time constants and hence the same effect would be expected. The difference, however, will be that by increasing C not only will the width be increased but significantly the amplitude will be reduced. It can be shown that the maximum crosstalk in this case (identical lines & sources) is independent of R, as indicated in figure 22. The derivation of maximum crosstalk amplitude together with its MATLAB functions are given in appendices B and C. Shown here is the final equation:

$$V_{2,\text{max}} = \frac{V_{DD}}{2} \left[ e^{\frac{-(C)}{2C_m} \ln \left[ \frac{C+2C_m}{C} \right]} - e^{\frac{-[C+2C_m]}{2C_m} \ln \left[ \frac{C+2C_m}{C} \right]} \right]$$

(3-3)

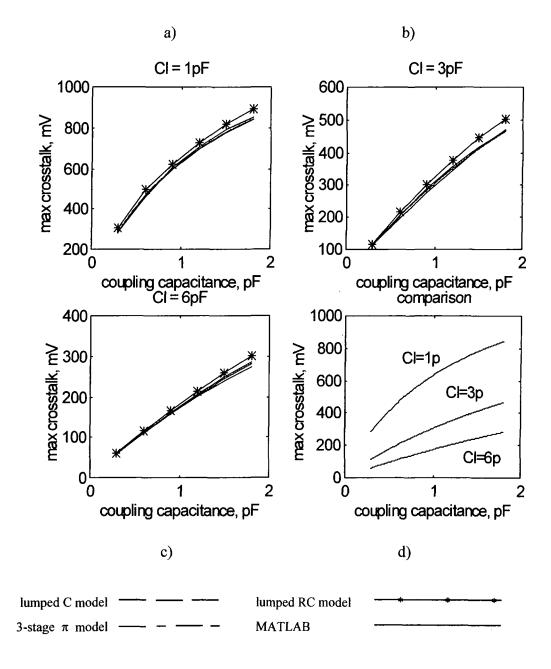

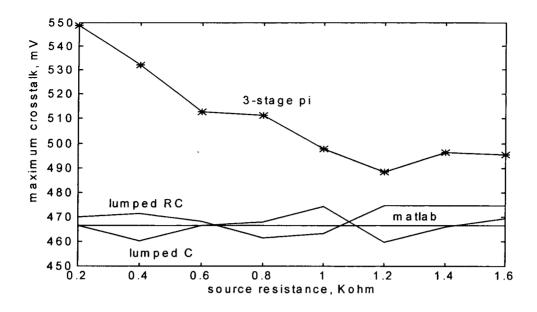

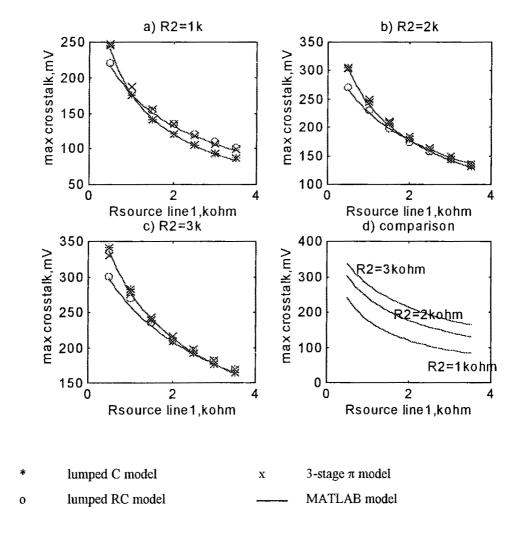

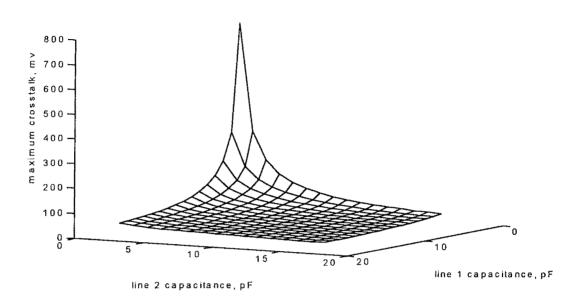

As can be seen from the equation, the only parameters which determine the maximum crosstalk are C,  $C_m$  and  $V_{DD}$ . The maximum crosstalk is clearly directly proportional to the supply voltage  $V_{DD}$ . The relationship between the maximum crosstalk and the two capacitance values C and  $C_m$ , however, can be harder to verify. Figure 23 shows how the maximum crosstalk varies with the coupling capacitance, given different line capacitance (for load capacitance  $C_L$  << line capacitance  $C_l$ , then  $C \approx C_l$ ). In each of

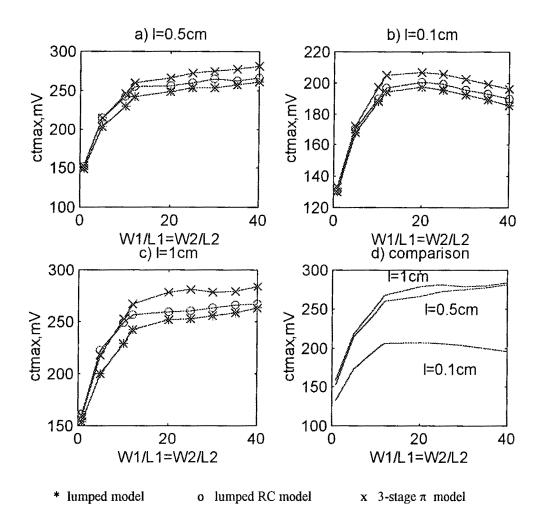

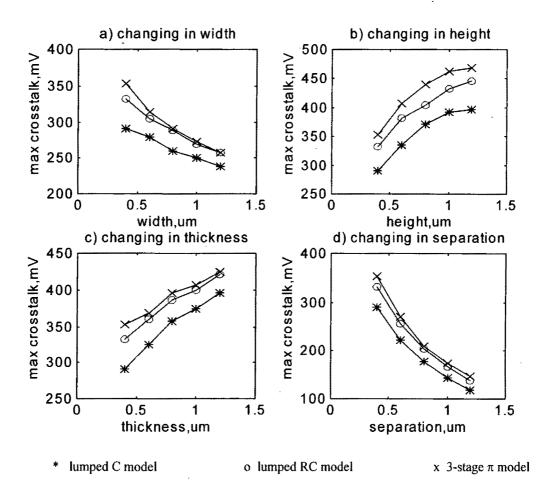

the figure 23 a), b), c) and d) the MATLAB result is plotted against the SPICE simulation results where the lines are modelled in the Lumped C, lumped RC and 3-stage  $\pi$  configurations. Here the source resistances are set at 1 k $\Omega$  and the resistance of the lines are 400  $\Omega$ .

Figure 23 The maximum crosstalk under different C and  $C_m$

It can be seen from the figures that the mathematical equation provides fairly accurate results compared to the simulations. The 3-stage  $\pi$  model tends to produce a slightly higher value of crosstalk. That is understandable since the mathematical model was derived under the assumption that the lines were modelled using the lumped

configuration. The difference, however, is only minimal and the mathematical model can still be a useful way of obtaining an initial prediction of maximum crosstalk.