### **Durham E-Theses**

# $Monte\ Carlo\ simulation\ of\ silicon-germanium\ transistors$

Yangthaisong, Anucha

#### How to cite:

Yangthaisong, Anucha (2002) Monte Carlo simulation of silicon-germanium transistors, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/4025/

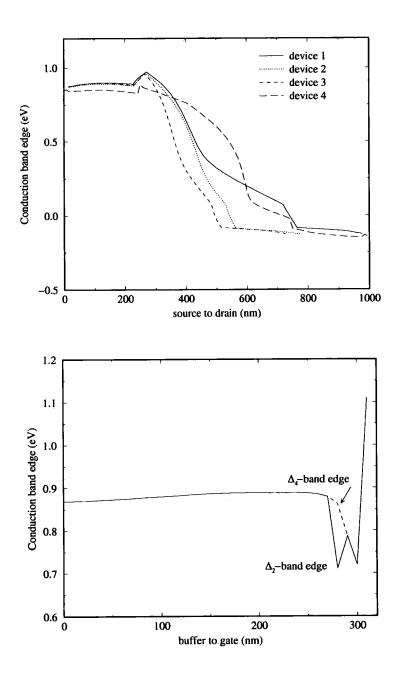

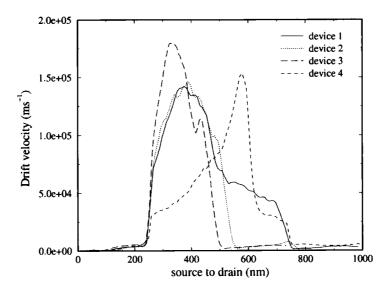

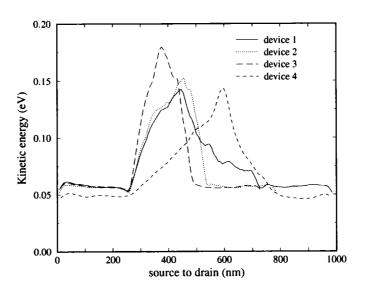

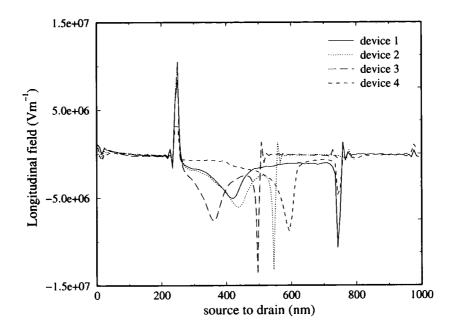

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

The copyright of this thesis rests with the author. No quotation from it should be published without his prior written consent and information derived from it should be acknowledged.

## Monte Carlo Simulation of Silicon-Germanium Transistors

Anucha Yangthaisong

A thesis submitted for the degree of Doctor of Philosophy at the University of Durham,

Department of Physics

1 4 APR 2003

October 2002

## **Declaration**

The work presented in this thesis has been carried out by the candidate (except where otherwise acknowledged) and has not been previously submitted for any degree.

The copyright of this thesis rests with the author. No quotation from it should be published without his prior written consent, and information derived from it should be acknowledged.

## Acknowledgements

I am indebted to the numerous friends and colleagues who have made this work possible and have contributed towards my enjoyment of the time spent at Durham. Special thanks go to Prof. Dick Abram for his supervision and encouragement during the course of my study, and for his comments on the first draft of this thesis. I am also very grateful to Gavin Crow for all his assistance. I would also like to thank Lydia Heck, Stuart Clark, Stuart Brand, Hadi Arabshahi, Daniel Harrison, Rick Coles, David Dugdale, Ian Bolland, Vicente Salinero and other members of Condensed Matter Theory Group (CMT) for discussion and practical help.

I gratefully acknowledge financial support for the period of my study from the Royal Thai Government (MOSTE).

I would also like to thank my family for their encouragement. I appreciate Ketesuda Panpho for her support, especially during the time spent writing this thesis. Last but not least, I would also like to thank Su Chen, Pattamaporn Chompoonutprapa, Pornsawan Amornsakchai, Mika Toronen, Ruchaboom Bunrawd, Auttakit Chattaraputi and others for helping me to take a regular break from my work to discuss on various topics.

"Hark, O Goddess! Some people in this world strive to get results for their endeavours even if they don't succeed. Hark, O Goddess! You do see clearly the results of actions, don't you? All the others have drowned in the ocean; we alone, are still swimming and have seen you hovering near us. As for us, we are going to endeavour further to the utmost of our ability; we are going to strive like a man should to reach the shores of the ocean."

His Majesty King Bhumibol Aduljadej

(The Story of Mahajanaka)

## **Abstract**

Self-consistent Monte Carlo simulation studies of n-channel Si/SiGe modulation doped field effect transistors (MODFETs) and silicon-on-insulator lateral bipolar junction transistors (SOI-LBJTs) are reported in this thesis.

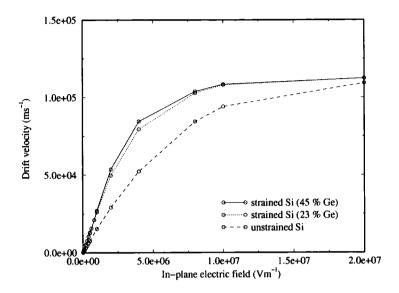

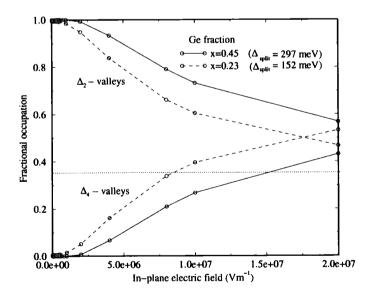

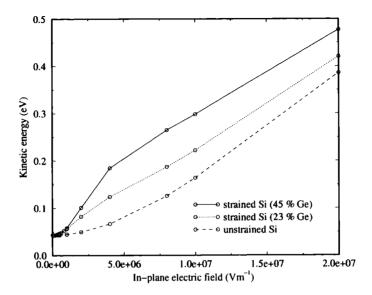

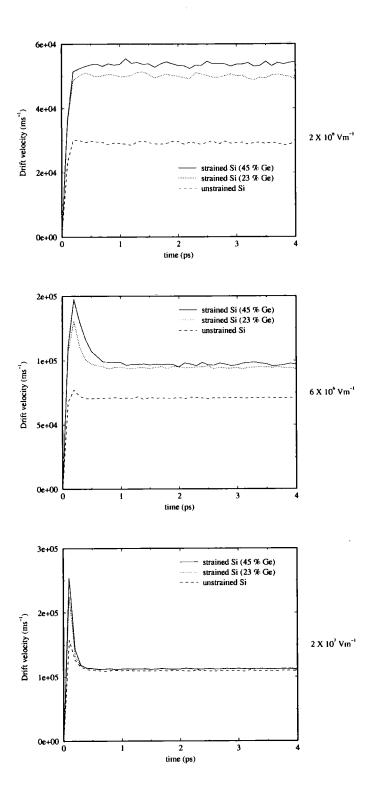

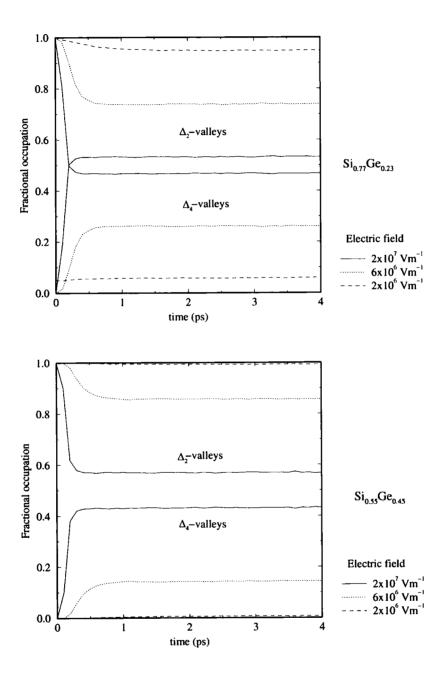

As a preliminary to the device studies Monte Carlo simulations of electron transport in bulk Si strained as if grown on  $Si_{0.77}Ge_{0.23}$  and  $Si_{0.55}Ge_{0.45}$  substrates have been carried out at 300 K, for field strengths varied from  $10^4$  to  $2 \times 10^7$  Vm<sup>-1</sup>. The calculations indicate an enhancement of the average electron drift velocity when Si is tensilely strained in the growth plane. The enhancement of electron velocity is more marked at low and intermediate electric fields, while at very high fields the velocity saturates at about the same value as unstrained Si. In addition the ensemble Monte Carlo method has been used to study the transient response to a stepped electric field of electrons in strained and unstrained Si. The calculations suggest that significant velocity overshoots occurs in strained material.

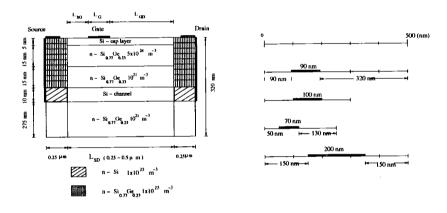

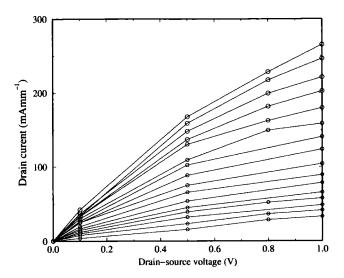

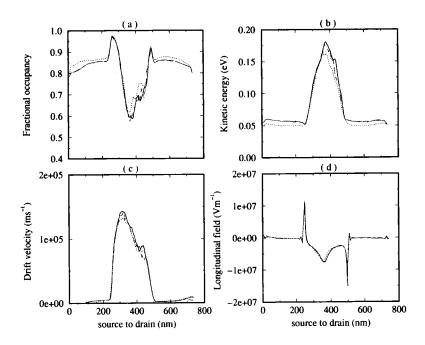

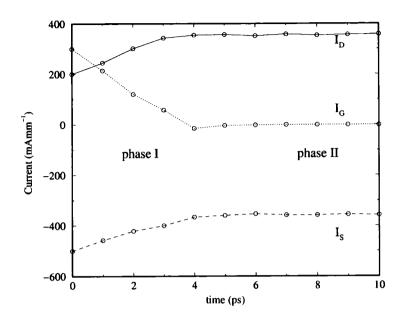

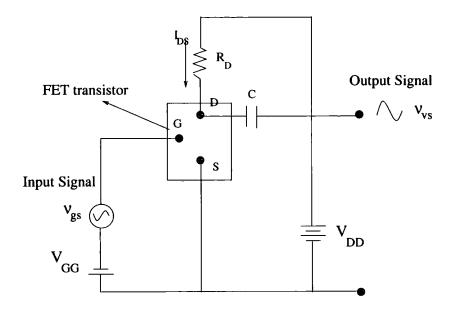

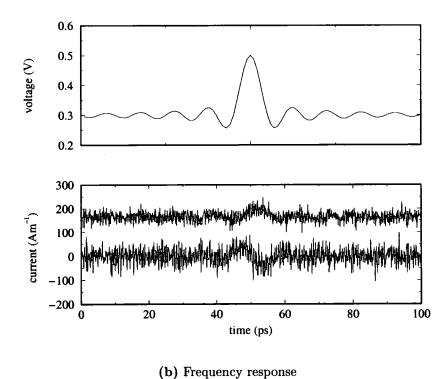

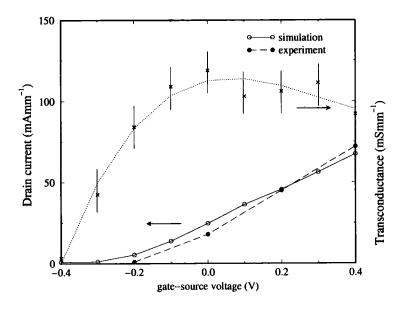

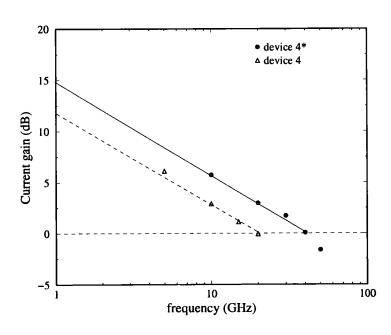

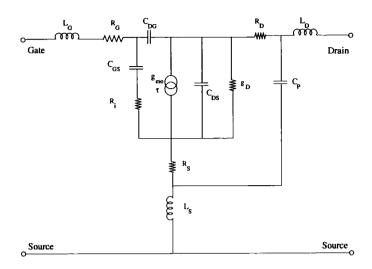

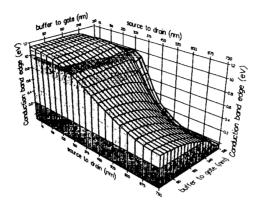

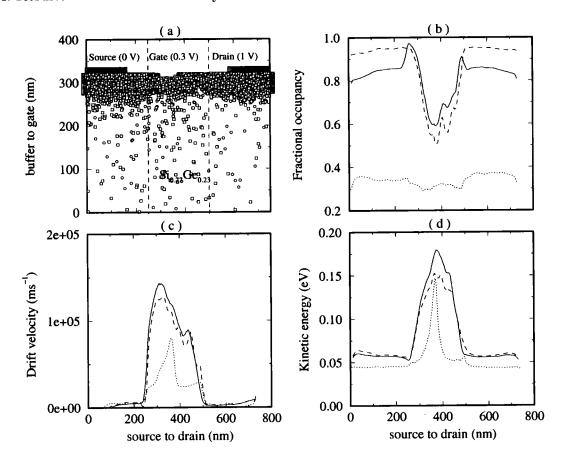

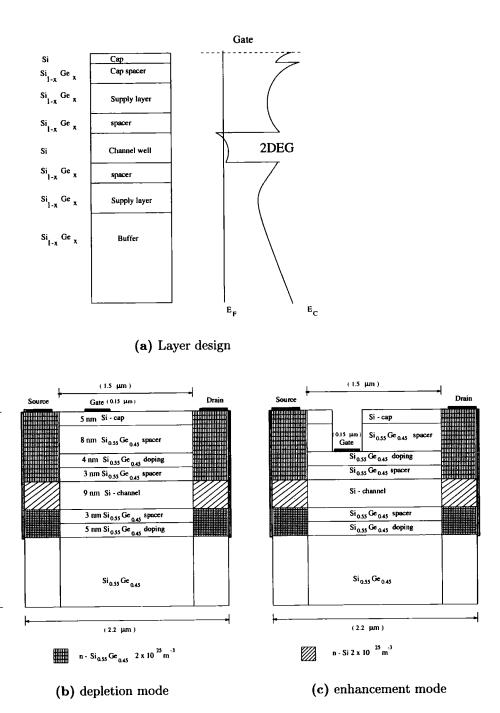

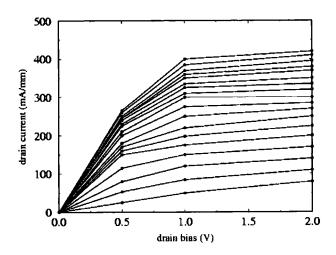

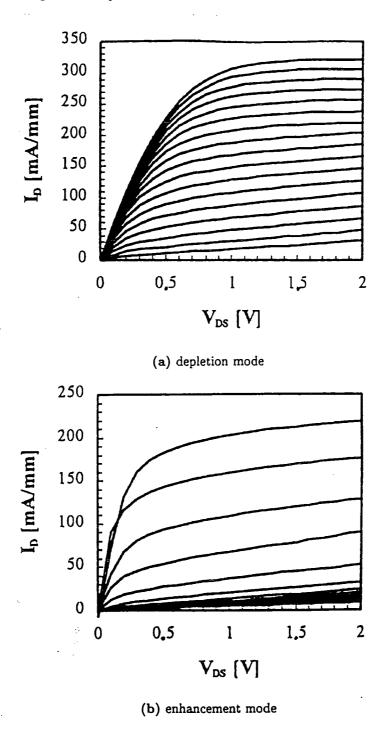

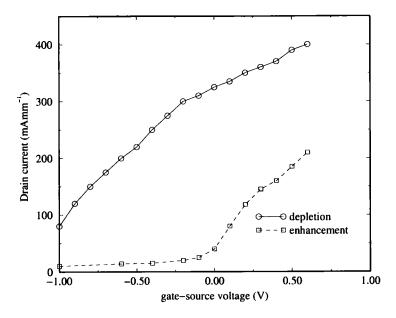

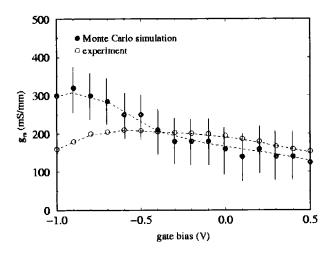

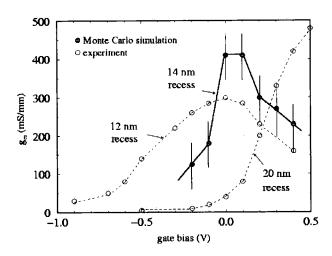

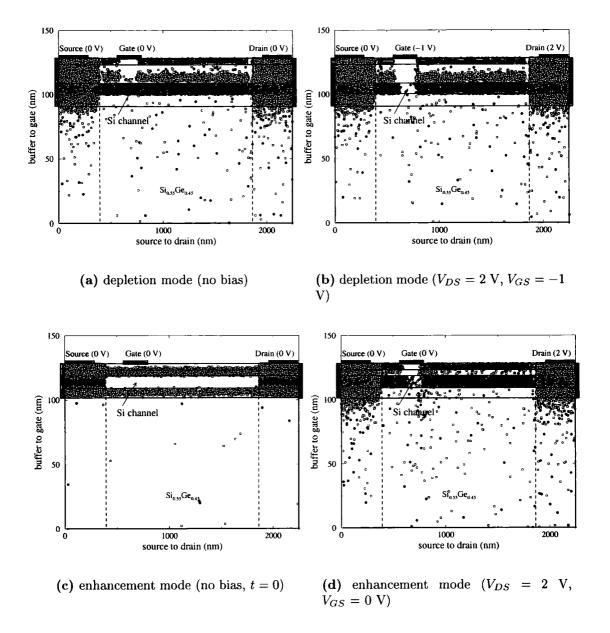

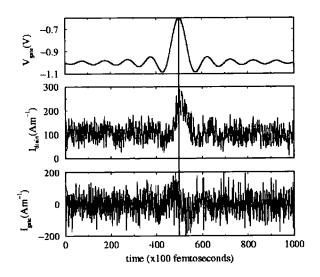

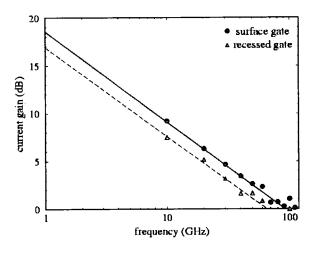

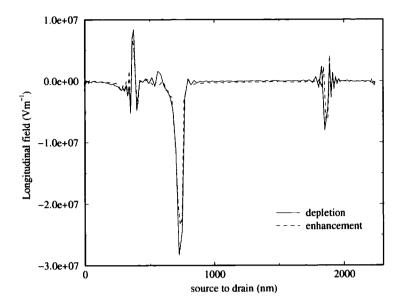

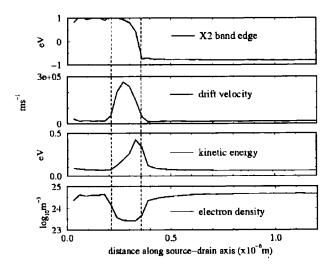

Simulations of n-channel Si/Si<sub>1-x</sub>Ge<sub>x</sub> MODFETs with Ge fractions of 0.23, 0.25, and 0.45 have been performed. Five depletion mode devices with x=0.23 and 0.25 were studied. The simulations provide information on the microscopic details of carrier behaviour, including carrier velocity, kinetic energy and carrier density, as a function of position in the device. Detailed time-dependent voltage signal analysis has been carried out to test device response and derive the frequency bandwidth. The simulations predict a current gain cut-off frequency of  $60 \pm 10$  GHz for a device with a gate length of 0.07  $\mu$ m and a channel length of 0.25  $\mu$ m. Similar studies of depletion and enhancement mode n-channel Si/Si<sub>0.55</sub>Ge<sub>0.45</sub> MODFETs with a gate length of 0.18  $\mu$ m have been carried out. Cut-off frequencies of  $60 \pm 10$  GHz and  $90 \pm 10$  GHz are predicted for the depletion and enhancement mode devices respectively.

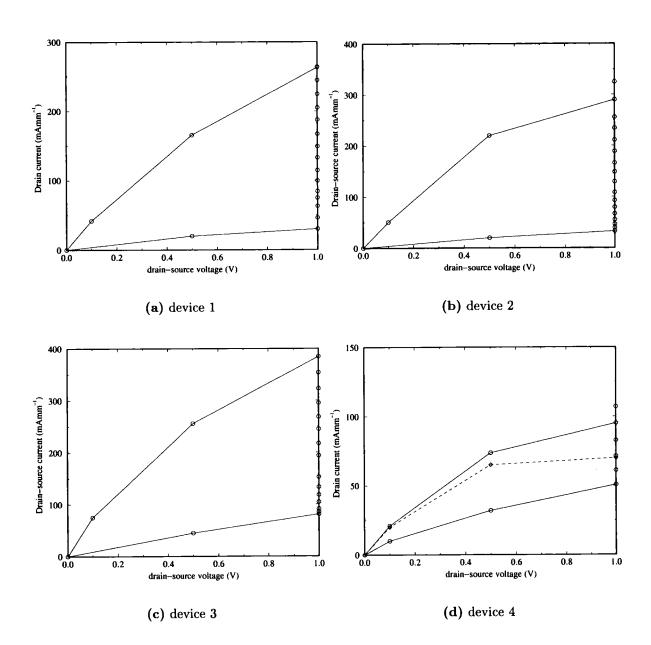

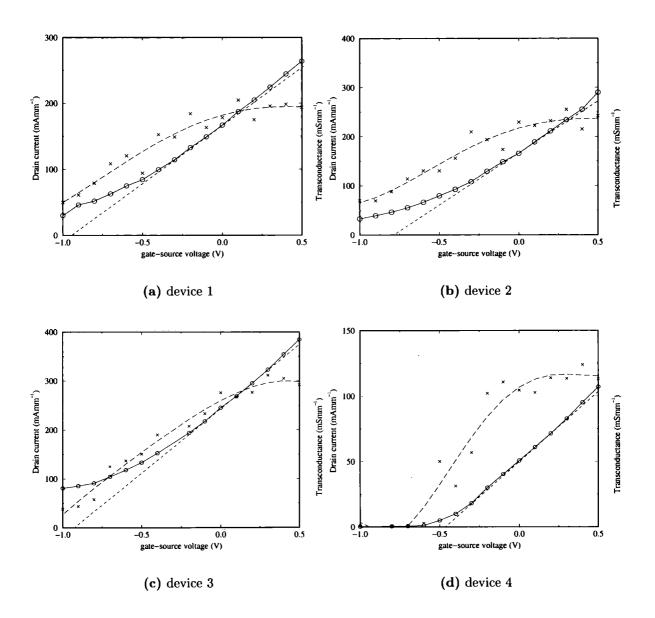

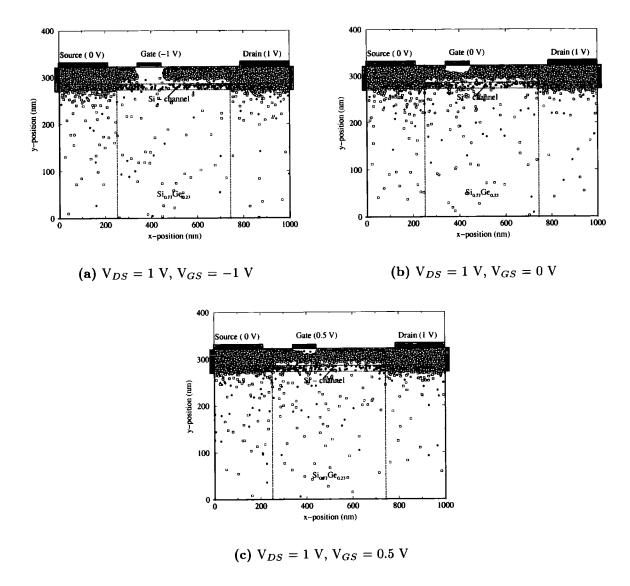

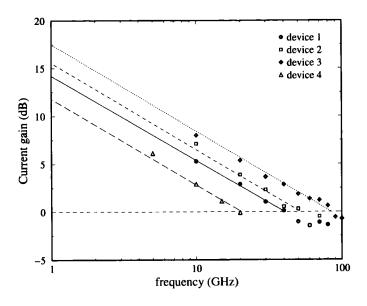

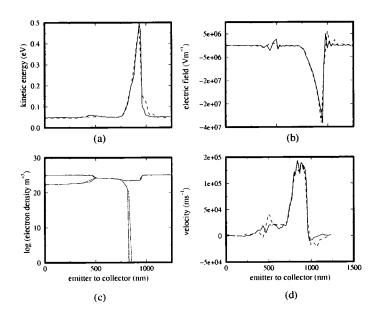

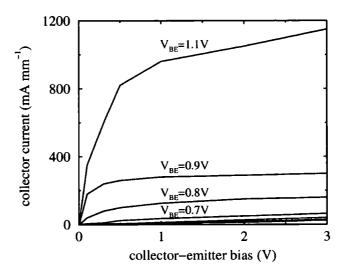

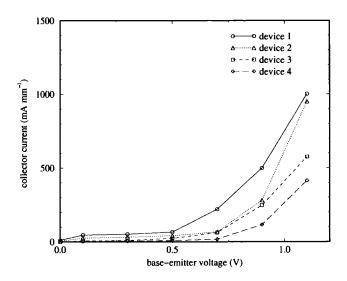

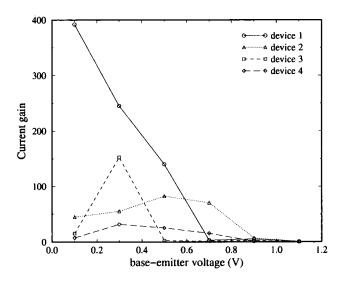

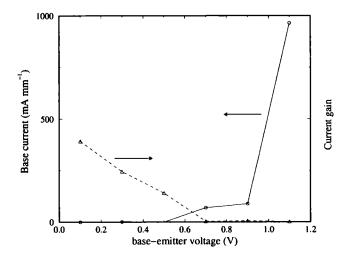

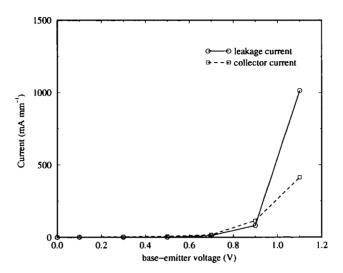

A Monte Carlo model has also been devised and used to simulate steady state and transient electron and hole transport in SOI-LBJTs. Four devices have been studied and the effects of junction depth and silicon layer thickness have been investigated. The advantage of the silicon-on-insulator technology SOI device is apparent in terms of higher collector current, current gain, and cut-off frequency obtained in comparison with an all-silicon structure. The simulations suggest that the common-emitter current gain of the most promising SOI-LBJT structure considered could have a cut-off frequency approaching  $35 \pm 5$  GHz.

## Contents

| 1 | Introduction |                                                                                                                                                                    |    |  |  |  |  |  |

|---|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|--|

|   | 1.1          | Structure of the thesis                                                                                                                                            | 3  |  |  |  |  |  |

| 2 | Si/0         | Si/Ge Materials                                                                                                                                                    |    |  |  |  |  |  |

|   | 2.1          | Introduction                                                                                                                                                       | 6  |  |  |  |  |  |

|   | 2.2          | Properties of $Si/Si_{1-x}Ge_x$ structures                                                                                                                         | 7  |  |  |  |  |  |

|   |              | 2.2.1 Pseudomorphic epitaxial layers                                                                                                                               | 8  |  |  |  |  |  |

|   |              | 2.2.2 Critical Thickness                                                                                                                                           | ç  |  |  |  |  |  |

|   |              | 2.2.3 Effect of strain on band structure                                                                                                                           | 12 |  |  |  |  |  |

|   |              | 2.2.4 Effect of strain on effective masses                                                                                                                         | 18 |  |  |  |  |  |

|   |              | 2.2.5 Effect of strain on mobilities                                                                                                                               | 18 |  |  |  |  |  |

|   |              | 2.2.6 Band offset and band alignment                                                                                                                               | 19 |  |  |  |  |  |

|   | 2.3          | Field Effect Transistor                                                                                                                                            | 22 |  |  |  |  |  |

|   | 2.4          | Concept of Modulation doping                                                                                                                                       | 24 |  |  |  |  |  |

|   | 2.5          | $\text{n-Si/Si}_{1-x}\text{Ge}_x \text{ MODFET} \dots \dots$ | 28 |  |  |  |  |  |

|   | 2.6          | npn-Si SOI LBJT                                                                                                                                                    | 30 |  |  |  |  |  |

|   | 2.7          | Summary                                                                                                                                                            | 33 |  |  |  |  |  |

| 3 | Mo           | nte Carlo Simulation                                                                                                                                               | 36 |  |  |  |  |  |

|   | 3.1          | Introduction                                                                                                                                                       | 36 |  |  |  |  |  |

|   | 3.2          | The Boltzmann transport equation                                                                                                                                   | 37 |  |  |  |  |  |

*CONTENTS* ii

|                                                                 | 3.3                                                | Monte                                                  | Carlo simulation                    | 39         |  |  |  |  |  |

|-----------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------|-------------------------------------|------------|--|--|--|--|--|

|                                                                 | 3.4                                                | Band Structure                                         |                                     |            |  |  |  |  |  |

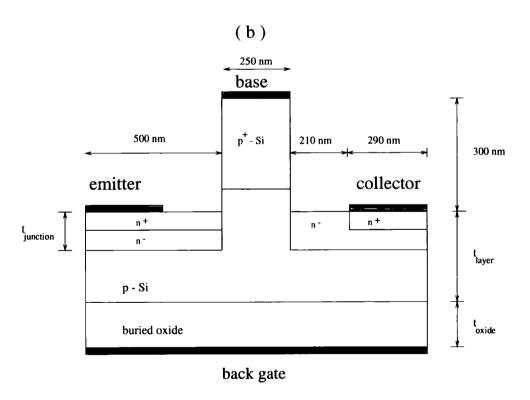

|                                                                 | 3.5                                                | Scatte                                                 | ring Mechanisms                     | 46         |  |  |  |  |  |

|                                                                 |                                                    | 3.5.1                                                  | Lattice Scattering                  | 47         |  |  |  |  |  |

|                                                                 |                                                    | 3.5.2                                                  | Ionised impurity scattering         | 52         |  |  |  |  |  |

|                                                                 |                                                    | 3.5.3                                                  | Alloy scattering                    | 53         |  |  |  |  |  |

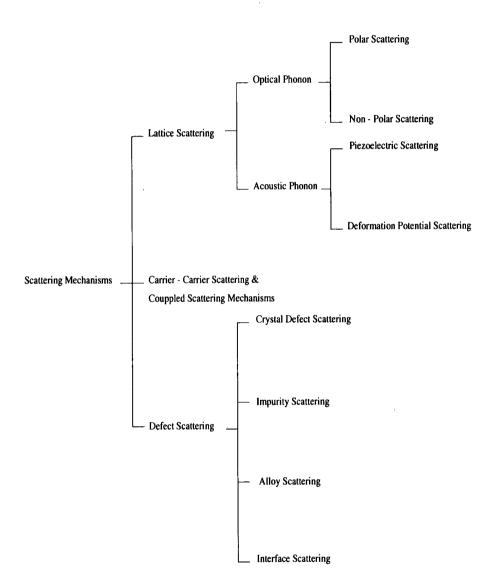

|                                                                 | 3.6                                                | Types                                                  | of Monte Carlo simulation           | 54         |  |  |  |  |  |

|                                                                 |                                                    | 3.6.1                                                  | One-particle simulation             | 54         |  |  |  |  |  |

|                                                                 |                                                    | 3.6.2                                                  | Ensemble simulation                 | 54         |  |  |  |  |  |

|                                                                 |                                                    | 3.6.3                                                  | Self-consistent simulation          | 55         |  |  |  |  |  |

|                                                                 | 3.7                                                | Device                                                 | e Simulation Model                  | 55         |  |  |  |  |  |

|                                                                 | 3.8                                                | Transp                                                 | oort Model                          | 65         |  |  |  |  |  |

|                                                                 |                                                    | 3.8.1                                                  | Band structure                      | 65         |  |  |  |  |  |

| 4                                                               | МО                                                 | DFET                                                   | ' Simulations                       | 39         |  |  |  |  |  |

|                                                                 | 4.1                                                |                                                        |                                     | 69         |  |  |  |  |  |

| 4.2 Simulation of electron transport in bulk Si and strained Si |                                                    |                                                        |                                     |            |  |  |  |  |  |

|                                                                 |                                                    | 4.2.1                                                  | •                                   | 71         |  |  |  |  |  |

|                                                                 |                                                    | 4.2.2                                                  | ·                                   | <b>7</b> 5 |  |  |  |  |  |

|                                                                 | 4.3                                                | Device                                                 |                                     | 77         |  |  |  |  |  |

|                                                                 | 4.4                                                | s for moderate tensilely strained Si n-channel MODFETs | 81                                  |            |  |  |  |  |  |

|                                                                 |                                                    | 4.4.1                                                  | Layer design                        | 81         |  |  |  |  |  |

|                                                                 |                                                    | 4.4.2                                                  | Device Characteristics and Analysis | 86         |  |  |  |  |  |

|                                                                 | s for high tensilely strained Si n-channel MODFETs | 14                                                     |                                     |            |  |  |  |  |  |

|                                                                 |                                                    | 4.5.1                                                  | Layer design                        | 14         |  |  |  |  |  |

|                                                                 |                                                    | 4.5.2                                                  | Device Characteristics and Analysis | 17         |  |  |  |  |  |

|                                                                 | 4.6                                                | Summ                                                   | nary and Conclusion                 |            |  |  |  |  |  |

|                                                                 |                                                    |                                                        |                                     |            |  |  |  |  |  |

| CONTENTS   | iii |

|------------|-----|

| CONTIDIATO | *** |

| 5          | SOI | SOI-LBJT Simulations     |                                               |     |  |  |  |  |  |  |  |

|------------|-----|--------------------------|-----------------------------------------------|-----|--|--|--|--|--|--|--|

|            | 5.1 | Introd                   | uction                                        | 130 |  |  |  |  |  |  |  |

|            | 5.2 | Device                   | Simulation                                    | 132 |  |  |  |  |  |  |  |

|            | 5.3 | Device                   | Characteristics and Analysis                  | 137 |  |  |  |  |  |  |  |

|            |     | 5.3.1                    | DC characteristics                            | 137 |  |  |  |  |  |  |  |

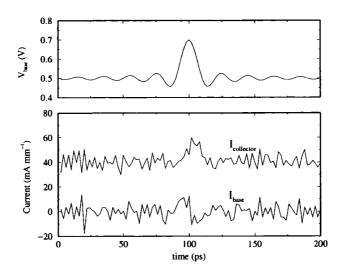

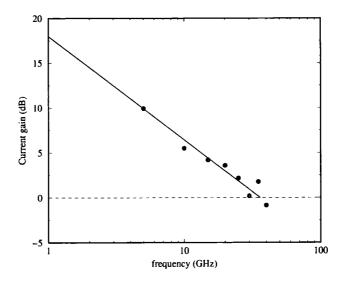

|            |     | 5.3.2                    | Signal Analysis                               | 140 |  |  |  |  |  |  |  |

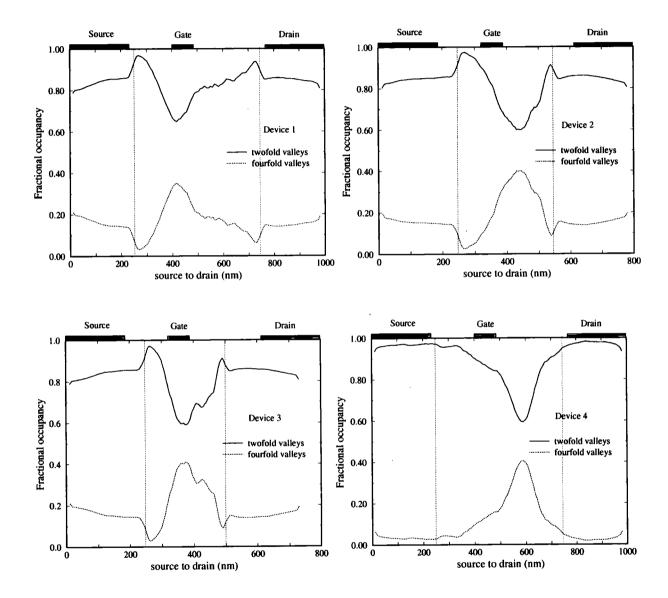

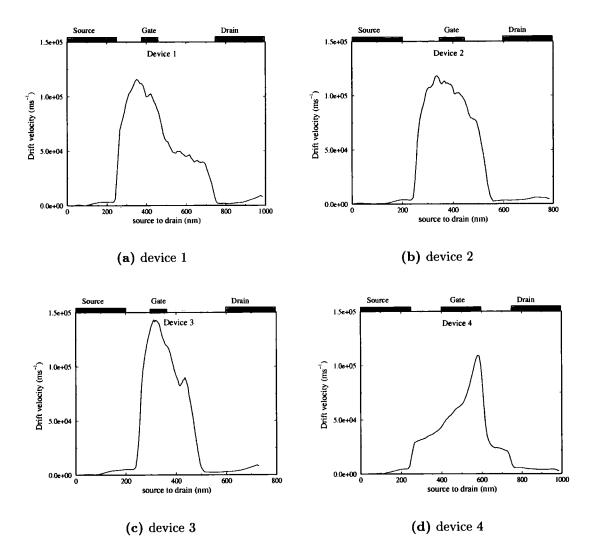

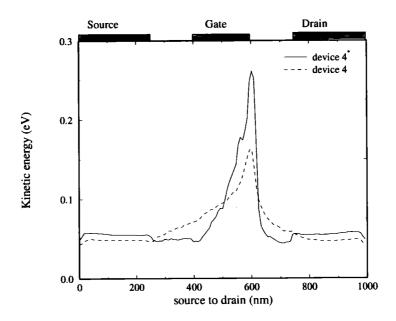

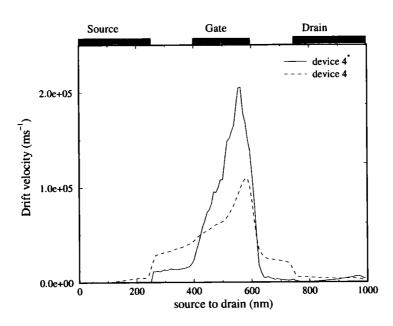

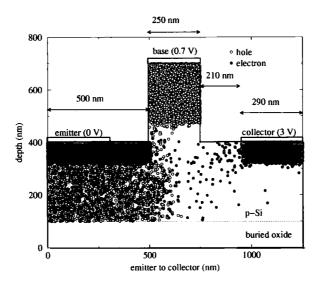

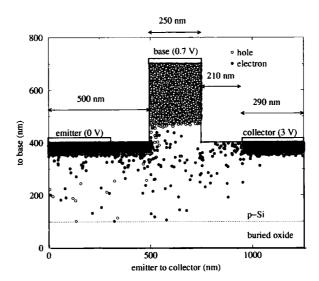

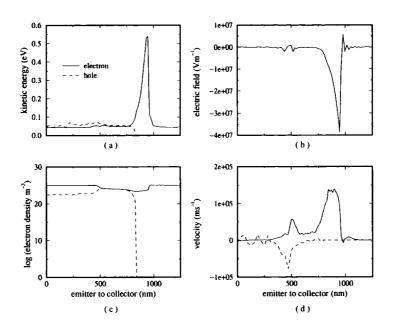

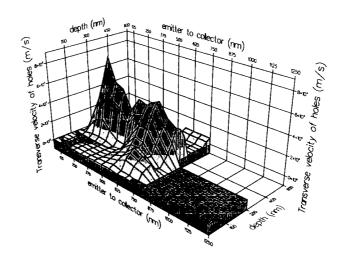

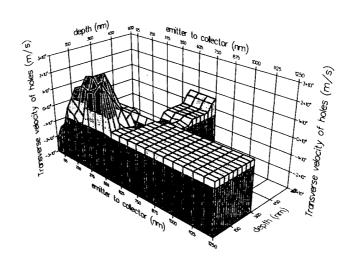

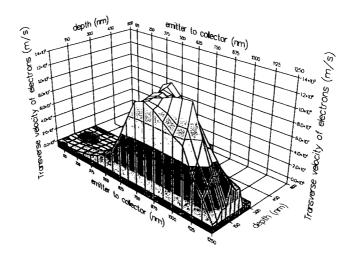

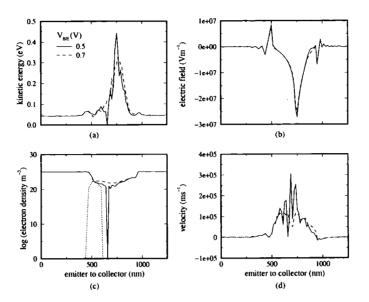

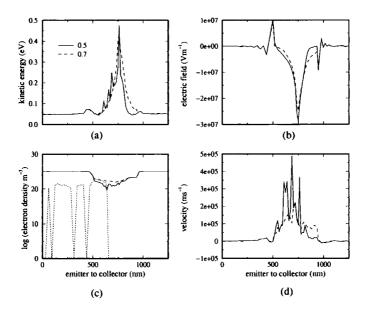

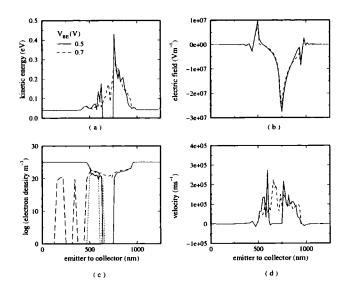

|            |     | 5.3.3                    | Microscopic Analysis                          | 142 |  |  |  |  |  |  |  |

|            | 5.4 | 4 Summary and Conclusion |                                               |     |  |  |  |  |  |  |  |

| c          |     |                          |                                               |     |  |  |  |  |  |  |  |

| 6          | Sun | ımary,                   | Conclusions and Suggestions for Further Works | 157 |  |  |  |  |  |  |  |

|            | 6.1 | 1 Summary & conclusions  |                                               |     |  |  |  |  |  |  |  |

|            | 6.2 | Sugges                   | tions for Further work                        | 160 |  |  |  |  |  |  |  |

| References |     |                          |                                               |     |  |  |  |  |  |  |  |

## Chapter 1

## Introduction

Despite the superior high-speed performance of transistors based on III-V materials, silicon is still the dominant semiconductor in modern microelectronics, with applications that can be found in both discrete devices and monolithic integrated circuits (ICs). A metal-oxide-semiconductor field-effect transistor (MOSFET) is a building block of VLSI circuits in microprocessors and dynamic memories. The n-type device involves controlling the current flow through a channel whilst a thin layer of SiO<sub>2</sub> is used to separate the gate electrode and p-silicon. Complementary MOSFET (CMOS) technology, which combines both n-channel and p-channel MOSFETs, provides very low power consumption combined with high speed. The performance and packing density of VLSI circuits is still improving as a result of the continuing miniaturisation of MOSFETs and advances in circuit fabrication techniques. However, enhancement of submicron device performance by reducing device size is facing more and more difficulties [1,2]. As a result, several new device concepts and new technologies have been developed in recent years in order to overcome or circumvent the problems. Two devices are investigated in this thesis, which might play an important role when the down-scaling of critical device dimensions is no longer an affordable option for bulk production.

Strain has the effect of changing the band structure and other parameters of a material so that it has different electronic properties and this provides a method of tailoring

device performance. It is possible to fabricate an n-channel MODFET structure, in which a thin silicon channel is under tensile strain as a result of growing it in a thin layer on a silicon-germanium alloy. The tensile strained Si provides a confining channel for the electrons. In addition the strain-induced splitting of the Si conduction band valleys means that the conductivity effective mass is effectively reduced and intervalley scattering is suppressed, resulting in an enhanced electron mobility. It is also possible to achieve spatial separation of the electrons from the ionised donors which supply them by only doping the structure away from the channel. This has the advantage of reducing ionised impurity scattering of the electrons. Due to these effects, modulation doped and strained  $Si/Si_{1-x}Ge_x$  (x < 0.5) structures have been shown to exhibit high-electron mobility, and hence have considerable potential for the development of fast Si-based MODFETs.

Field-effect transistors are used in the majority of VLSI circuits, but bipolar transistors are valuable in applications requiring high speed, high current and lower integration levels than state of the art circuits. Devices that take advantage of both the high current-drive capability of high speed bipolar transistors and the mass production techniques of CMOS technology are particularly attractive. Bipolar junction transistors with an unconventional lateral geometry can be incorporated into integrated circuits with only minor modifications to CMOS processing. In particular the use of silicon-on-insulator for lateral bipolar devices permits simple circuit integration and results in very small junction capacitances, ease of isolation, and a CMOS-like device area. These features are particularly attractive for dense high-performance CMOS-type applications.

Carrier transport in submicron semiconductor devices is complicated by the rapid spatial and temporal variations in electric fields and associated carrier dynamics that can occur. The modelling of such devices requires physics-based simulators that can provide a realistic description of non-equilibrium carrier transport. The advantage of

accurate device simulation based on firm physical foundations is that it can be considered as a form of experiment, which can be carried out much faster and with less expense than real experimental investigation. Furthermore, computer simulation provides a wealth of microscopic detail and the potential for a deep physical interpretation of the results that can point the way to enhancements in device performance.

This thesis is concerned with the modelling of electron transport in n-channel strained  $Si/Si_{1-x}Ge_x$  MODFETs with Ge contents of 0.23, 0.25, and 0.45 and electron and hole transport in silicon-on-insulator lateral bipolar transistors (SOI-LBJTs). For both types of device the self-consistent ensemble Monte Carlo method is used. The thesis is organised as follows:

#### 1.1 Structure of the thesis

#### Chapter 2

Chapter 2 describes the elastic and electronic properties of Si and SiGe alloys, with particular emphasis on the effects of strain on the electronic band structure, and the transport properties of carriers, and how the effects can be utilised in high performance devices. The two types of transistors which are the subject of study, the modulation doped field-effect SiGe transistor (MODFET) and the lateral bipolar junction transistor (LBJT), are also introduced.

#### Chapter 3

In this chapter, the Boltzmann transport equation (BTE) is introduced as a semiclas-

sical description of charge carrier transport in semiconductors. The Monte Carlo (MC) method is also introduced as a numerical method of solving the BTE by tracking the trajectories of particles representative of electrons and holes which move through a device under the influence of the local electric field and the stochastic scattering by phonons, impurities and alloy disorder. The chapter concludes with a description of the use of the Monte Carlo model for the device simulations which produce the results presented in Chapter 4 and 5.

#### Chapter 4

Chapter 4 presents the results of simulations of n-channel strained Si/Si<sub>1-x</sub>Ge<sub>x</sub> MOD-FETs using the self-consistent ensemble Monte Carlo method. The devices studied can be categorised as being in two groups according to their Ge content. The moderately strained devices have a Ge fraction x = 0.23 or 0.25 and the highly strained devices have x = 0.45. Macroscopic device characteristics and parameters, such as the drain current-drain voltage curve and, the transconductance  $(g_m)$  are obtained from the simulations. The simulations also provide information on the microscopic details of carrier behaviour, including carrier velocity, kinetic energy and density as a function of position in the device, facilitating a thorough analysis of the mechanisms determining device performance. The device response to a time-dependent voltage signal has also been simulated to derive the frequency bandwidth for various geometries.

#### Chapter 5

In this chapter, we report how a Monte Carlo simulation has been devised and used to model steady state and transient electron and hole transport in SOI-LBJTs. Four devices are studied in order to investigate the effects of junction depth and silicon layer thickness. Simulations have also been carried out to investigate the high frequency performance of the devices.

### Chapter 6

Conclusions drawn from this work are presented in Chapter 6 and suggestions are made for further study.

## Chapter 2

## Si/Ge Materials

#### 2.1 Introduction

To overcome the physical limits on the speed of the field effect transistor while maintaining compatibility with conventional integrated circuit fabrication processes, several innovations have been developed in recent years. In particular Si/SiGe heterostructures have been introduced as a promising method for improving device speed without reduction of device size while solving a number of other problems encountered in MOSFETs [1,2]. Much recent research in  $Si/Si_{1-x}Ge_x$  heterostructures has had the aim of obtaining higher hole and electron mobilities through strain-induced band splitting, and enhanced mobilities in both n-channel and p-channel devices have been reported in recent years [3,4]. Fabrication processes for Si/SiGe devices are quite compatible with those routinely used in Si ICs, in contrast to the situation with III-V compound devices [5]. Hence, mobility-enhanced field-effect transistors based on SiGe could not only fit well into the area of mainstream microelectronics, but might also provide the performance advantage that may ultimately be decisive when the down-scaling of critical device dimensions is no longer an affordable option for bulk IC production.

The physics of Si/SiGe materials that is relevant to the operation of the devices and to the simulation model that we use to investigate them is presented in this chapter.

In Section 2.2 the basic properties of Si, Ge and the alloy  $Si_{1-x}Ge_x$  in the bulk are briefly introduced and then the effect of strain on the band structure, effective masses, and mobilities of Si and  $Si_{1-x}Ge_x$  are described. A knowledge of the band alignment of a  $Si/Si_{1-x}Ge_x$  heterojunction is also required to describe in quantitative terms the control of carrier transport in the heterostructures, and information on this is also given in Section 2.2. The basic concept of the field-effect transistor and the technique of modulation doping are introduced in Sections 2.3 and 2.4 respectively. Also in Section 2.4, we describe how the changes due to the strain-induced band structure can be used to tailor device performance. Section 2.5 deals with the use of heterojunctions and strain in specific n-Si/Si<sub>1-x</sub>Ge<sub>x</sub> MODFETs. The basic operation of the silicon-on-insulator bipolar transistor (SOI LBJT) is described in Section 2.6.

### 2.2 Properties of $Si/Si_{1-x}Ge_x$ structures

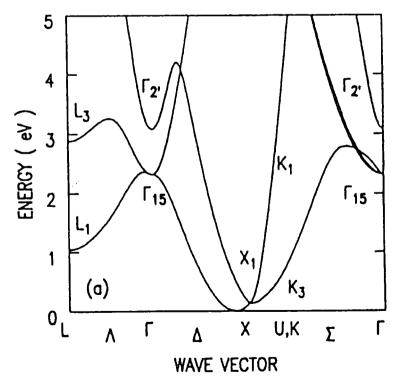

Si and Ge are indirect bandgap materials and the fundamental bandgap of  $Si_{1-x}Ge_x$  alloys is also indirect for all compositions. The conduction band edge minima are sixfold degenerate in Si, where they are located along the [100] directions near the X-points of the Brillouin zone and are referred to as  $\Delta$ -minima. In Ge, the conduction band edge minima are located right at the Brillouin-zone edge in the [111] directions (L-minima). In Si, the six equivalent minima of the conduction band are ellipsoids of revolution and therefore are characterised by different effective masses in the various directions. There is a longitudinal mass  $m_l = 0.91m_0$ , which describes the curvature in the major axis direction, and a transverse mass  $m_t = 0.19m_0$ , which relates to the two minor axes. For Ge, there are eight half ellipsoids equivalent to four complete ellipsoids in the periodic zone scheme, which have a transverse mass of  $m_t = 0.82m_0$  and a longitudinal mass of  $m_t = 1.64m_0$ . According to the work of Braunstein et al. [6], the lowest lying conduction bands cross over in the alloy from the  $\Delta$  Si-like states to the L Ge-like states for a Ge content of 85 %. Consequently, the conduction band structure of bulk

8

SiGe alloy is Si-like for a wide range of alloy compositions.

According to Vegard's law, the lattice constant of unstrained  $Si_{1-x}Ge_x$  is given by

$$a(x)_{Si_{1-x}Ge_x} = (1-x)a_{Si} + xa_{Ge}$$

(2.1)

That is, the lattice constant of  $\mathrm{Si}_{1-x}\mathrm{Ge}_x$  can then be varied in a continuous fashion from that of Si to Ge. Note that the lattice constant a(x) of the  $\mathrm{Si}_{1-x}\mathrm{Ge}_x$  alloy is bigger than that of Si since  $a_{Si}=5.430$  Å and  $a_{Ge}=5.650$  Å.

#### 2.2.1 Pseudomorphic epitaxial layers

Consider the effect of attempting to grow an epilayer of a material with cubic crystal structure and lattice constant  $a_{epi}$  on a substrate with the same type of crystal structure but a different lattice constant  $a_{sub}$ . Our attention is restricted to the growth along the (100) axis of the crystal. The lattice mismatch is described by a misfit parameter  $f_m$  as:

$$f_m = \frac{a_{epi} - a_{sub}}{a_{sub}} \tag{2.2}$$

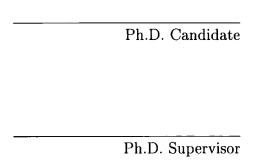

where  $a_{epi}$  is the lattice constant of the epitaxial layer (or epilayer) and  $a_{sub}$  is the lattice constant of the substrate. A match between the two crystalline structures can be achieved only if one or both crystals are elastically strained. In general, the substrate is much thicker than the growing epitaxial film, and then it is the atoms of the epitaxial layer that must be displaced. If  $f_m < 0$  there is an in-plane (biaxial) tensile strain in the epilayer and also the lattice constant normal to the plane is reduced. Alternatively, if  $f_m > 0$  there is an in-plane (biaxial) compression of the epilayer and tensile strain normal to the plane. In both cases there is a tetragonal distortion of the cubic unit cell of the epilayer crystal structure as schematically illustrated in Figure 2.1. When the epilayer grows with this type of simple elastic distortion of the crystal structure, without the appearance of dislocations, the growth is said to be pseudomorphic.

#### 2.2.2 Critical Thickness

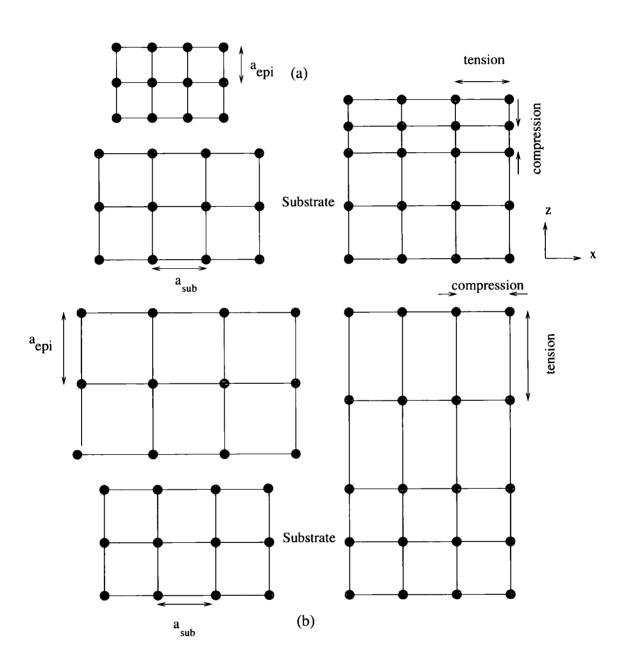

The basic understanding of the growth of pseudomorphic layers was first provided by Frank and van der Merwe [7] but a more complete analysis of the growth of lattice-mismatched layers was performed by Matthews and Blakeslee [8]. They pointed out that the growth of a sufficiently thin epitaxial layer, whose lattice constant is close to but not equal to the lattice constant of the substrate, may give rise to a coherently strained layer as opposed to a polycrystalline or amorphous layer. In particular, there exists a critical thickness  $(h_c)$  of the epilayer below which the film is thermodynamically stable and no misfit dislocations exist in the interface. For layers with thickness above  $h_c$ , misfit dislocations become energetically favourable and provide partial strain relaxation of the film, the degree of which increases with increasing layer thickness. According to the theory of Matthews and Blakeslee (MB) [8], the critical thickness can be calculated from [9]:

$$h_c = \frac{b^2 (1 - \nu \cos^2 \beta)}{8\pi f_m (1 + \nu) b_1} \ln \frac{\rho_c h_c}{q}$$

(2.3)

where b is the Burgers vector,  $\nu$  is Poisson's ratio,  $\beta$  is the angle between the dislocation line and the Burgers vector,  $b_1 = b \cos \beta$ , q is the core cut-off parameter, which is taken to be equal to  $b_1$ , and  $\rho_c$  is the core energy parameter. Note that the formula does not take account of the interactions between dislocations and a more rigorous calculation of  $h_c$  has been performed by Jain et al. [9]. Nonetheless, accurate predictions of  $h_c$  differ only slightly from the values obtained from Equation 2.3.

Thus, when a layer of  $Si_{1-x}Ge_x$  is grown on a Si substrate, it becomes compressively strained with the lattice symmetry changing from cubic to tetragonal if the growth is pseudomorphic. On the other hand, if the layer thickness is above the critical thickness, there are misfit dislocations and other defects and the carrier mobility in the material

Figure 2.1: A material with a lattice constant  $a_{epi}$  grown on a substrate with a lattice constant  $a_{sub}$ : a)  $a < a_{sub}$  b)  $a > a_{sub}$

Figure 2.2: Schematic illustration of (a) Separate layers at equilibrium. There is a 4.2% difference in the lattice constant of Si and Ge. Thus when a layer of  $Si_{1-x}Ge_x$  is grown on top of Si, it has a bulk relaxed lattice constant which is larger than Si. (b) If a layer grown is below the critical thickness it becomes strained with the lattice symmetry changing from cubic to tetragonal. (c) If the layer thickness is above the critical thickness, misfit dislocations appear, which act to relieve the strain in the epitaxial film.

12

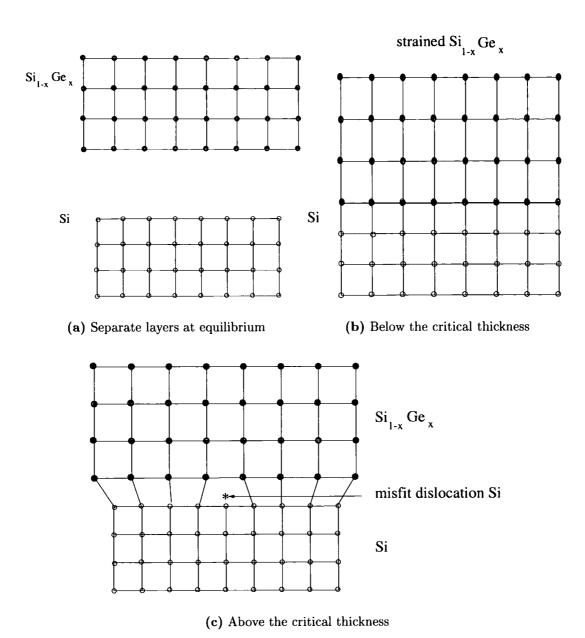

is reduced by the high defect density, making it unsuitable for device applications. These two cases are illustrated in Figure 2.2. Figure 2.3 illustrates the opposite to Figure 2.2(b) in the sense that an epilayer of Si is grown on a SiGe substrate resulting in biaxial tensile strain.

#### 2.2.3 Effect of strain on band structure

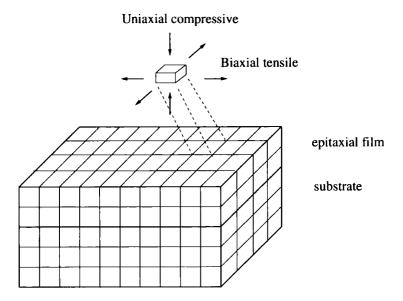

In this section, we examine the effect that strain in an epitaxial layer has on the electronic properties of the semiconductor. To this end, it is important to know the strain tensor for the epitaxial layer. Once the strain tensor is known, the effect of strain on the band structure can be obtained from deformation potential theory. In the present work, the epitaxial semiconductor layer is biaxially strained in the plane of the substrate by an amount  $\epsilon$ , and uniaxially strained in the normal direction by an amount  $\epsilon_{\perp}$ .

The definition of stress, strain and their relationship are discussed in many text-books, e.g. Kittel [10], and only the essential points will be presented here. A strain within the elastic limit is defined by the components of a symmetric second-rank tensor  $\varepsilon$ :

$$\varepsilon_{ij} = \frac{1}{2} \left( \frac{\partial u_i}{\partial x_j} + \frac{\partial u_j}{\partial x_i} \right), \text{ where } i, j = 1, 2, 3$$

(2.4)

Note that the diagonal part  $\varepsilon_{ii}$  is the specific increment of length in direction i and the dilation  $\theta$  (the specific increment of the volume V) is simply the trace of  $\varepsilon$

$$\theta = \frac{\Delta V}{V} = \varepsilon_{11} + \varepsilon_{22} + \varepsilon_{33} = Tr(\varepsilon)$$

(2.5)

The nondiagonal elements of  $\varepsilon_{ij}$   $(i \neq j)$  correspond to shearing deformations. The stress-tensor  $\sigma$  is defined by its components  $\sigma_{ij}$ , where i, j = 1, 2, 3. According to

**Figure 2.3:** Schematic diagram of an epitaxial film of Si grown on  $Si_{1-x}Ge_x$  under tetragonal distortion with in-plane biaxial tensile strain and out-of-plane uniaxial compressive strain.

Hooke's law, the stress-strain relations are

$$\varepsilon_{\mu} = \sum_{\eta=1}^{6} s_{\mu\eta} \sigma_{\eta} \tag{2.6}$$

where in the conventional reduced notation the values of  $\mu$  and  $\eta$  have the meaning  $1 \equiv xx$ ,  $2 \equiv yy$ ,  $3 \equiv zz$ ,  $4 \equiv yz$ ,  $5 \equiv zx$ ,  $6 \equiv xy$  and  $s_{\mu\eta}$  are the elastic compliance constants. The stress components can be written as a function of the strain components:

$$\sigma_{\mu} = \sum_{\eta=1}^{6} c_{\mu\eta} \varepsilon_{\eta} \tag{2.7}$$

where  $c_{\mu\eta}$  are the elastic stiffness constants. The energy is a quadratic function of the strain, and can be written as

$$U = \frac{1}{2} \sum_{\lambda=1}^{6} \sum_{\mu=1}^{6} \tilde{c}_{\lambda\mu} e_{\lambda} e_{\mu}$$

(2.8)

14

where  $\tilde{c}_{\lambda\mu}$ 's are related to the c's. For cubic systems, the elastic energy U simplifies to

$$U = \frac{1}{2}c_{11}(e_{xx}^2 + e_{yy}^2 + e_{zz}^2) + \frac{1}{2}c_{44}(e_{yz}^2 + e_{zx}^2 + e_{xy}^2) + c_{12}(e_{yy}e_{zz} + e_{zz}e_{xx} + e_{xx}e_{yy})$$

$$(2.9)$$

The non-vanishing components of the stress tensor  $(\sigma(epi))$  of the epitaxial layer are  $\sigma_{xx}(epi)$  and  $\sigma_{yy}(epi)$  with  $\sigma_{xx}(epi) = \sigma_{yy}(epi)$ . The independent stress-strain relations for the epitaxial layer are

$$\sigma_{xx}(epi) = c_{11}(epi)\varepsilon_{xx}(epi) + c_{12}(epi)[\varepsilon_{yy}(epi) + \varepsilon_{zz}(epi)],$$

$$\sigma_{zz}(epi) = c_{11}(epi)\varepsilon_{zz}(epi) + c_{12}(epi)[\varepsilon_{xx}(epi) + \varepsilon_{yy}(epi)]$$

(2.10)

with  $c_{11}(epi)$  and  $c_{12}(epi)$  being the elastic stiffness constants of the epitaxial layer. The in-plane strain  $\varepsilon_{\parallel}$  (=  $\varepsilon_{xx} = \varepsilon_{yy}$ ) is defined for the epitaxial layer

$$\varepsilon_{\parallel} = \frac{a_{sub}}{a_{epi}} - 1 \tag{2.11}$$

Since there is no stress along the perpendicular direction, the perpendicular strain  $\varepsilon_{\perp}$  ( $\varepsilon_{zz}$ ) can be written as

$$\varepsilon_{\perp} = -2\frac{c_{12}}{c_{11}}\varepsilon_{\parallel}$$

$$= \frac{-2\sigma}{1-\sigma}\varepsilon_{\parallel} \qquad (2.12)$$

where  $\sigma$  is Poisson's ratio.

Once the strain tensor is known, deformation potential theory can be used to calculate the effect of the strain on the electronic band structure. Deformation potential theory describes the effect of strain in terms of deformation potentials which are obtained for each band by experimental measurements of the band structure with applied stress. The strain perturbation Hamiltonian is defined and its effects are calculated in first order perturbation theory. Here, we will summarise the relevant results of that formalism.

There are three basic elements significantly affecting the band structure in strained films [11–14];

- 1) changes in bandgaps due to hydrostatic strain,

- 2) removal of the degeneracy of states due to uniaxial strain,

- 3) shift in the spin orbit split off  $(\Delta_{so})$  band.

Hydrostatic strain shifts the average position of the conduction band,  $\Delta E_{c,av}$ , according to the formula

$$\Delta E_{c,av} = a_c \frac{\Delta V}{V} \tag{2.13}$$

where the net change in volume of the unit cell  $\Delta V/V = Tr(\vec{\varepsilon}) = 2\varepsilon_{\parallel} + \varepsilon_{\perp}$  and  $a_c$  is the hydrostatic deformation potential for the conduction band. Hydrostatic strain also shifts the average position of valence band, which can be expressed in a similar form to Equation 2.13. The general effect of hydrostatic strain is to increase the band gap with compressive strain and to decrease the gap with tensile strain.

However, the strain in a pseudomorphic epitaxial layer has both hydrostatic and uniaxial components. For example, if silicon is grown pseudomorphically on  $\operatorname{Si}_{1-x}\operatorname{Ge}_x$ , the in-plane lattice constant changes by  $\Delta a$  while the lattice constant in the growth direction changes by  $\Delta a_{\perp}$  where  $\Delta a_{\perp} = -\Delta a_{\parallel}/\sigma$ . The deformation does not retain the symmetry of the material as in the hydrostatic case, and the strain can be considered to be the sum of hydrostatic and uniaxial components. The effect of uniaxial strain on the six-fold  $\Delta$  valleys of the degenerate conduction band of Si (and SiGe with a Si-like lower conduction band) is that the valley degeneracy is partly removed. The valleys split into two sets, one set being a doublet and the other a quadruplet as shown in Figure 2.4. Denoting the four equivalent in-plane axes by  $\Delta_4$  and the two valleys on the axis parallel to the growth direction by  $\Delta_2$ , the energy shifts are

$$\Delta E_c^{\Delta} = \begin{cases} +\frac{2}{3}\Xi_u^{\Delta}(\varepsilon_{\perp} - \varepsilon_{\parallel}) & \text{for the } \Delta_2 \text{ valleys} \\ -\frac{1}{3}\Xi_u^{\Delta}(\varepsilon_{\parallel} - \varepsilon_{\perp}) & \text{for the } \Delta_4 \text{ valleys} \end{cases}$$

(2.14)

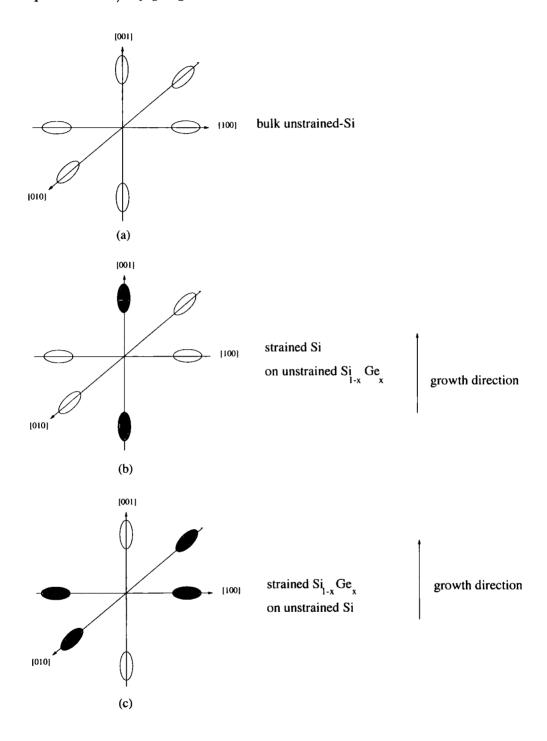

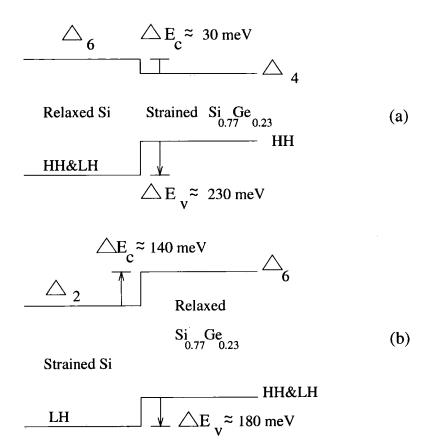

Figure 2.4: (a) The constant energy surfaces of the conduction bands of silicon. There are six equivalent conduction bands located along the [100], [010], and [001] directions. (b) The constant energy surfaces of strained Si grown on a [001]  $Si_{1-x}Ge_x$  virtual substrate. The [001] conduction bands have shifted downwards in energy relative to the [010] and [100] bands. (c) The constant energy surfaces of strained  $Si_{1-x}Ge_x$  grown on a [001] Si substrate. The [010] and [100] bands have shifted downwards in energy relative to the [001] bands.

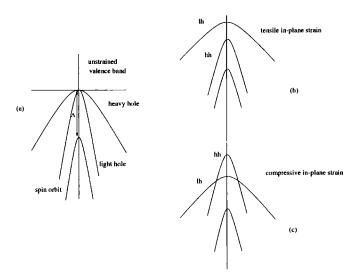

Figure 2.5: (a) Valence band structure in the absence of strain, (b) effect of tensile in-plane strain, (c) as (b) but for compressive in-plane strained band structure

where  $\Xi_u^{\Delta}$  is the  $\Delta$ -valley deformation potential. If Si is grown on  $\mathrm{Si}_{1-x}\mathrm{Ge}_x$ , the Si is under biaxial tensile and uniaxial compressive strain and the two valleys in black in Figure 2.4(b) have the lower energy. Note that the Ge content dependence of  $\Xi_u^{\Delta}$  (in eV) for  $\mathrm{Si}_{1-x}\mathrm{Ge}_x$  is parameterised as [14]

$$\Xi_u^{\Delta} = 9.29 + 0.2188x + 0.6912x^2 \tag{2.15}$$

The conduction band offset  $\Delta E_c$  is about 0.12 - 0.3 eV for a Ge fraction of 0.2 - 0.5. Figure 2.4(c) shows the opposite case of the alloy epilayer on a Si substrate.

The effect of the strain in an epilayer on the valence band is to remove the heavy-hole and light-hole band degeneracy as illustrated in Figure 2.5. If the strain in the plane of the layer is compressive, the heavy-hole band is raised relative to the light-hole band; if tensile, the reverse occurs. For the former case, the in-plane effective mass of the heavy-hole band is relatively light [15], resulting in an improved hole mobility. In addition the interband scattering is reduced due to the lifting of the heavy hole-light

hole band degeneracy. On the other hand, it is expected that the tensile in-plane strain will also increase the low-field hole mobility since most holes reside in the heavy-hole band in the bulk and interband scattering is suppressed when the bands are split by strain.

#### 2.2.4 Effect of strain on effective masses

There are no experimental data available on electron masses of SiGe alloys [16]. The theoretical investigation using non-local pseudopotential calculations performed by Rieger et al. [14] shows that there are only small changes of the X-valley mass parameters due to strain and Ge content. Hence, the effect of strain on effective mass is not included in our Monte Carlo transport model.

#### 2.2.5 Effect of strain on mobilities

The carrier mobility is one of the most important parameters of a semiconductor material since the carrier velocity is proportional to the mobility for low electric fields. All other things being equal a transistor made from a higher mobility material will have a higher frequency response since carriers take less time to travel through the device. In addition, higher mobility materials imply lower resistances and lower RC time constants, again resulting in a higher frequency response.

We have already noted that the strain in Si grown on SiGe removes some of the degeneracy of the  $\Delta$  valleys in unstrained Si. A typical value for the splitting is 0.18 eV which is greater than  $6k_BT$  at room temperature. As a result, electrons preferentially occupy the two lower valleys (shown in black in Figure 2.4(b)) which have low in-plane masses. As the in-plane mass is much lower than the conductivity mass of bulk Si we might expect a substantial enhancement in mobility. In addition, the lower density of

states of the two valleys compared to the original six reduces the intervalley scattering and also acts to increase the electron mobility.

The initial experimental attempts to realise the predicted enhancement of electron mobility due to the effects of strain on the band structure were severely impeded by the quality of the strain-adjusting buffer layers used in an effort to produce a SiGe substrate by growing relaxed material on a Si substrate. The best mobilities achieved as a result of these initial efforts reached a value close to 17 000 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> [17]. With better growth conditions and a breakthrough in reducing the defect densities of the  $Si_{1-x}Ge_x$  buffer layer, electron mobilities now exceed 500 000 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> at low temperature [18]. The mobilities at room temperature have also been increased to almost 3000 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> [3], which is more than a factor of 3 higher than that in conventional Si MOSFETs [19,20], and a factor of 2 higher than the (3D) mobility of intrinsic bulk Si.

#### 2.2.6 Band offset and band alignment

A knowledge of band alignments is essential for informed device design. As well as the normal space charge effects that occur as a result of doping we must consider the band offsets that result from the use of different materials. In the lattice-matched case, it is necessary to know just the valence-band and conduction-band offsets,  $\Delta E_v$  and  $\Delta E_c$  respectively. When there is a lattice mismatch, as for  $\text{Si-Si}_{1-x}\text{Ge}_x$  heterostructures, we also need to know the shifts in bands that occur as a result of strain, including the strain splitting of the valence and conduction bands. In fact this information is often required for a range of different strain conditions, since there is generally some flexibility in the alloy compositions used in a particular device.

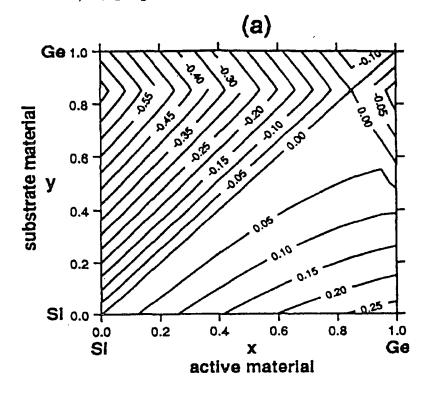

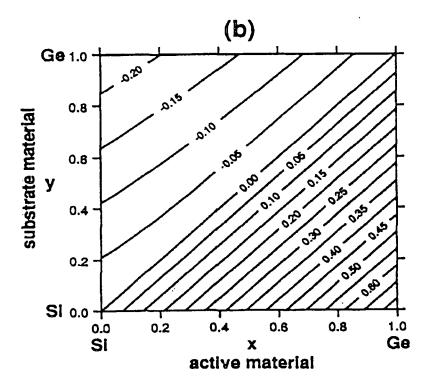

To determine the band alignment for a given  $Si_{1-y}Ge_y$ -Si heterointerface it is necessary to know the band gaps of the strained layer constituents and either  $\Delta E_c$  or

Figure 2.6: Band offsets in (a) conduction band and (b) in valence band between a substrate of  $Si_{1-y}Ge_y$  and an active layer of  $Si_{1-x}Ge_x$  that is strained to match the substrate [14].

$\Delta E_v$  [21]. The energy gap of strained  $\mathrm{Si}_{1-x}\mathrm{Ge}_x$  is given by [21]:

$$E_g(\mathrm{Si}_{1-x}\mathrm{Ge}_x)_{strained} = E_g(\mathrm{Si}_{1-x}\mathrm{Ge}_x)_{unstrained}$$

(2.16)

$$-\frac{2}{3}(c_{11} + 2c_{12}) \times (1 - (c_{12}/c_{11}))\frac{dE_g}{dP} \times \varepsilon_{xx} \qquad (2.17)$$

where  $c_{11}$ ,  $c_{12}$  are elastic constants of unstrained  $\mathrm{Si}_{1-x}\mathrm{Ge}_x$  and  $dE_g/dP$  is the hydrostatic pressure coefficient of the energy gap of unstrained  $\mathrm{Si}_{1-x}\mathrm{Ge}_x$ . According to the calculation of Rieger and Vogl [14], the offset between the average energy of the valence-band edge in a strained  $\mathrm{Si}_{1-x}\mathrm{Ge}_x$  layer and an unstrained  $\mathrm{Si}_{1-y}\mathrm{Ge}_y$  layer can be expressed as:

$$\Delta E_{v,av} = (0.47 - 0.067y)(x - y) \tag{2.18}$$

The energy gap of the alloy  $Si_{1-y}Ge_y$  can be obtained by interpolating the energy gap of Si and Ge as:

$$E_g(Si_{1-y}Ge_y) = yE_g(Ge) + (1-y)E_g(Si) + y(1-y)b(SiGe)$$

(2.19)

where  $E_g(Si) = 1.12 \text{ eV}$ ,  $E_g(Ge) = 0.975 \text{ eV}$  and b is the bowing parameter for the ternary alloy, which is taken to have the value -0.19 eV [22]. Once we know the valence band offset, we can use our knowledge of the bandgap in the unstrained alloy, combined with deformation potential theory, to obtain the conduction-band offset according to

$$\Delta E_c = E_g(\mathrm{Si}_{1-y}\mathrm{Ge}_y) + \Delta E_v(\mathrm{Si}_{1-x}\mathrm{Ge}_x/\mathrm{Si}) - E_g(\mathrm{Si}_{1-x}\mathrm{Ge}_x)_{strained}$$

(2.20)

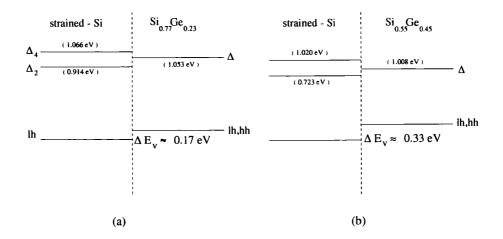

for the strained  $Si_{1-x}Ge_x$  grown on unstrained  $Si_{1-y}Ge_y$ . Figure 2.6 shows the calculated band offsets for a layer of  $Si_{1-x}Ge_x$  on a  $Si_{1-y}Ge_y$  substrate. Note there are sharp changes in the way the conduction band offset  $\Delta E_c$  varies with composition, which are due to the changes in the nature of the lowest minima of the conduction band in the two materials. Figure 2.7(a) relates to a strained  $Si_{0.77}Ge_{0.23}$  layer on a silicon substrate. Note most of the offset is in the valence band. The type I band alignment shown is favourable for hole confinement and can be exploited in several

novel heterostructure devices. For example, pseudomorphic  $Si_{1-x}Ge_x$  grown on (001) Si is used in the base region of n-p-n heterojunction bipolar transistors (HBTs), which show good high-frequency performance. In fact Si/SiGe HBTs, with cut-off frequencies and maximum oscillation frequencies well beyond 100 GHz have been reported [23]. On the other hand, Si forms the epilayer on a  $Si_{0.77}Ge_{0.23}$  substrate in Figure 2.7(b). The Si is now under biaxial tension, the band alignment is type II, and there is a bigger discontinuity in the conduction band. This arrangement facilitates electron and hole confinement in different layers. Thus, it is useful for both n- and p-type devices for strained Si/SiGe-based CMOS technology.

Figure 2.8 shows the conduction ( $\Delta E_c$ ) and valence band ( $\Delta E_v$ ) offsets for strained Si-Si<sub>0.77</sub>Ge<sub>0.23</sub> and strained Si-Si<sub>0.55</sub>Ge<sub>0.45</sub> heterojunctions. Note that a  $\Delta E_c$  of 0.139 eV is obtained for the former and 0.285 eV for the latter.

#### 2.3 Field Effect Transistor

The concept of a field-effect transistor (FET) was first proposed by Lilienfeld and Heil in the 1930s [24,25], but only in the 1950s had semiconductor-material processing technology progressed enough that Dacay and Ross [26] were able to demonstrate working devices. Currently FET technology plays the dominant role in microelectronics, and FET devices and integrated circuits are made in a variety of designs and with many different semiconductor materials. The tremendous versatility of the device combined with high manufacturing yield and operational reliability have allowed it to become the industry workhorse for a variety of applications.

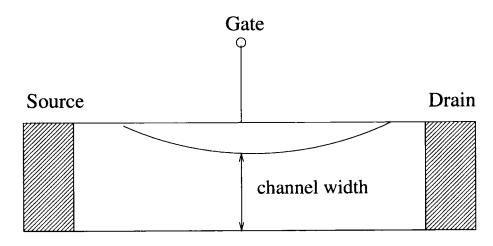

The device operates as a conducting semiconductor channel between source and drain ohmic contacts, in which the number of charge carriers is controlled by a third contact called the gate. Carriers flow from the source to the drain while the width of the channel is modulated by a potential applied to the gate as depicted in Figure 2.9(a).

**Figure 2.7:** Band alignments between Si and  $Si_{0.77}Ge_{0.23}$  on two substrates (a) Si and (b)  $Si_{0.77}Ge_{0.23}$

**Figure 2.8:** Band alignments between Si and  $Si_{0.77}Ge_{0.23}$  (a), Si and  $Si_{0.55}Ge_{0.45}$  (b) as grown on  $Si_{0.77}Ge_{0.23}$  and  $Si_{0.55}Ge_{0.45}$  virtual substrates, respectively.

The basic principle has been implemented in a variety of different devices, such as the Metal Oxide Semiconductor FET (MOSFET), or Metal Insulator Semiconductor FET (MISFET), Metal Semiconductor FET (MESFET) and Heterostructure FET (HFET) as illustrated in Figure 2.9(b).

#### 2.4 Concept of Modulation doping

The purpose of semiconductor(s) doping is generally to change the free carrier density in a controllable fashion. This requires that the dopant centres be ionised, leaving positively charged donor centres in the case of n-doping. These fixed charged centres have a screened Coulomb interaction with the free electrons and the resultant ionised impurity scattering is usually an important scattering mechanism of low energy carriers in semiconductors. In a conventional transistor, the impurities and carriers exist in the same regions of the device and the detrimental impurity scattering cannot be avoided. However, the quality of carrier transport in the device can be enhanced by

(a) Basic principle of FET

(b) Conventional FET structure

Figure 2.9: (a) Schematic FET structure. Device operation involves the use of a gate to modulate the charge in the channel and hence in the current flow between source and drain. (b) Conventional FET structure. The gate isolation is achieved in a variety of ways (p-n junction, Schottky gate, heterostructure) resulting in a number of different versions of the device.

removing the dopants from the regions where the critical carrier transport processes occur. This is the modulation doping concept, which can be realised by the use of spatially-dependent doping and the use of heterojunctions to control the location of the carriers.

Stern and Howard first formulated a theory of two-dimensional electron transport in Si inversion layers in 1967 [27]. In 1969 Esaki and Tsu [28] proposed that the high electron concentration and the spatial separation of donors diminishes the effects of impurity scattering in the two-dimensional electron gas, thereby enhancing the electron mobility. The effect of mobility enhancement was first experimentally observed in an AlGaAs/GaAs heterostructure by Dingle et al. [29].

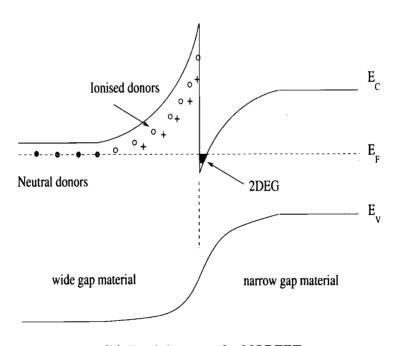

The basic idea behind modulation doping is illustrated in Figure 2.10 for a heterojunction between a wide bandgap material (e.g AlGaAs) and narrow bandgap material (e.g GaAs) in a FET-type structure. Note that a layer of the wide gap material immediately adjacent to the interface is left undoped, and is referred to as the spacer layer. As a result of the conduction band offset there is a discontinuity in the band profile through the device and a layer of electrons is formed at the heterointerface. Note that the spatial separation of free carriers from their parent-dopant centres could not be realised in bulk material since there is a large electrostatic restoring force on the electrons after the separation. In the heterostructure the band discontinuity prevents the electric field from returning the electrons to the vicinity of the donors. In fact the field can only squeeze the electrons against the interface, where they are trapped in a roughly triangular potential well. The net result of the modulation doping is that carriers in the undoped heterointerface region are spatially separated from the doping centres and can have a substantially enhanced mobility due to the reduced impurity scattering. This is despite the fact that interface roughness scattering at the heterointerface(s) appears as an additional scattering mechanism.

The first transistor based on the modulation doping concept was a GaAs/AlGaAs

(a) General structure of a MODFET

(b) Band diagram of n-MODFET

Figure 2.10: (a) General structure of a MODFET. The wide-bandgap material is doped and the carriers diffuse to the undoped narrow-bandgap material. (b) The band profile of an n-MODFET showing band bending leading to a roughly triangular quantum well at the heterostructure interface. Mobile electrons generated by the donors diffuse into the small band gap material, and are prevented from returning by the potential barrier at the interface.

device demonstrated by Mimura et al. [30] in 1980, which showed a dramatic enhancement in the drain current and transconductance. Since then attention has focused on the use of modulation-doped heterostructures for the realisation of high speed field-effect transistors. A field-effect transistor that takes advantage of the superior carrier transport properties of modulation-doped heterostructures is called a modulation-doped field-effect transistor (MODFET). MODFETs based on the GaAlAs/GaAs heterostructures have very successfully driven microelectronics to higher speeds for specialist applications. However, the drawback of III-V compound devices is their incompatibility with the well established Si-based integrated circuit technology. As a result there is interest in devices which exploit the properties of the strained SiGe/Si system, and can be thought of as a natural extension of the Si homosystem.

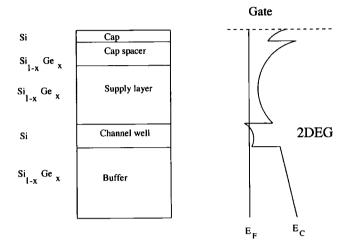

# 2.5 $n-Si/Si_{1-x}Ge_x$ MODFET

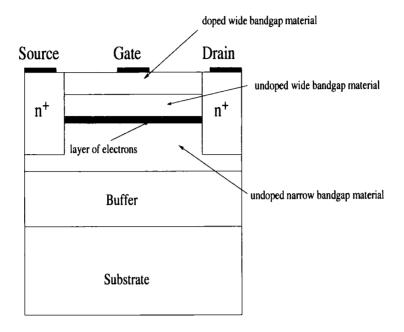

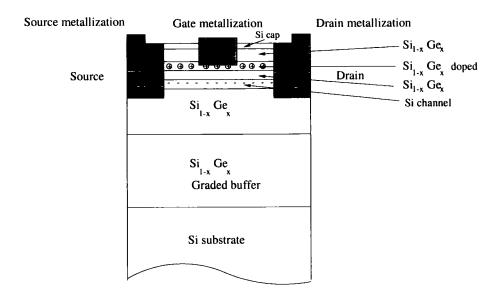

Figure 2.11 illustrates an n-channel  $Si/Si_{1-x}Ge_x$  MODFET, in which a channel for the electrons is formed by the tensile strained silicon layer with a  $Si_{1-x}Ge_x$  alloy barrier. A  $Si_{1-x}Ge_x$  alloy spacer layer separates the doped region of the layer from the silicon channel to form a modulated doped structure.

The device is based on the ability to grow a thick relaxed SiGe layer on a silicon substrate. The upper part of the SiGe layer has the lattice constant of bulk material and can be used as a substrate to grow a strained pseudomorphic Si layer and produce a heterostructure with the band alignments shown in Figure 2.7(b). The most widely used technique is the initial growth of a SiGe buffer layer on the Si substrate, with a Ge content which is graded from zero up to the final concentration of typically 20-30 %, followed by the growth of a constant composition buffer and then the active layers of the device [31]. This graded SiGe buffer concept provides what are called virtual substrates with low defect densities at arbitrary Ge content [31,32].

Figure 2.11: n-channel  $Si/Si_{1-x}Ge_x$  MODFET.

In recent years the electron mobility in the strained Si channel of n-type modulation doped quantum well structures (MODQW) has reached a high level. For example, a room temperature mobility in excess of 2500 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> was reported by Nelson *et al.* [3], which is almost twice that of bulk Si and three times higher than in conventional MOSFETs. (Note that the peak electron mobility in intrinsic bulk Si is about  $1400 \text{ cm}^2\text{V}^{-1}\text{s}^{-1}$  [33]). The first n-channel modulation-doped SiGe/Si heterostructure field-effect transistors based on this type of structure were then fabricated by Daenbkes *et al.* [34] by the use of molecular-beam epitaxial (MBE) growth. The first transistor they reported exhibited an extrinsic transconductance of 40 mS mm<sup>-1</sup> for a gate length of 1.6  $\mu$ m, which is higher than that of comparable conventional Si MOSFETs.

Ismail et al. [35] have grown devices in two successive UHV-CVD processes and reported a carrier density of  $2.5 \times 10^{12}$  cm<sup>-2</sup> as well as a high mobility of 1500 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> at room temperature. Also, MBE-grown n-MODFETs, with Hall mobilities of 2200 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> at room temperature, have been reported by König et al. [36]. A current gain cut off frequency  $f_T$  as high as 62 GHz for a n-Si/Si<sub>0.75</sub>Ge<sub>0.25</sub> MODFET has been

recently reported by the IBM group [37]. Similar high values of  $f_T$  have been achieved in high Ge content (45 %) n-MODFETs that have been investigated experimentally by the Daimler-Chrysler group [36].

P-channel MODFETs can be produced by growing a pseudomorphic  $Si_{1-x}Ge_x$  layer on Si. In this case nearly all the band offset occurs in the valence band and holes are confined to the  $Si/Si_{1-x}Ge_x$  interface. In addition, the strain lifts the degeneracy of the light- and heavy-hole valence band; a  $Si_{1-x}Ge_x$  layer on Si is in biaxial compression and the heavy-hole band is raised relative to the light hole band as shown in Figure 2.5(c). Since the heavy hole band has the smaller in-plane effective mass, the strained  $Si_{1-x}Ge_x$  film can be expected to exhibit a higher hole mobility than bulk Si. The reduced interband scattering that results from the lifting of the heavy hole-light hole band degeneracy also acts to increase hole mobility. A novel method for the fabrication of high hole mobility structures is the growth of a Gi channel on a relaxed graded  $Si_{1-x}Ge_x$  buffer. The Gi channel, being under an in-plane biaxial compressive strain, provides a hole effective mass lower than  $0.1m_0$  in strained Gi. (Note that the hole density-of-states effective mass in bulk Gi is much higher with a value of  $0.29m_0$ ). As a consequence high hole mobilities at 4.2 K of  $55000 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  have been observed [38].

# 2.6 npn-Si SOI LBJT

Devices that combine the field effect and bipolar effect are very attractive for some applications since they can offer the advantages of high current driving capability and high current gain together with low power consumption. By combining both technologies on the same chip, one can optimise the tradeoff between the speed and power dissipation, and attain digital/analog systems with a performance which may exceed that of circuits based on either technology alone.

Bipolar transistors are normally fabricated in a vertical geometry; that is with

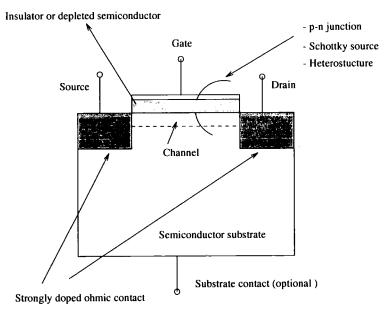

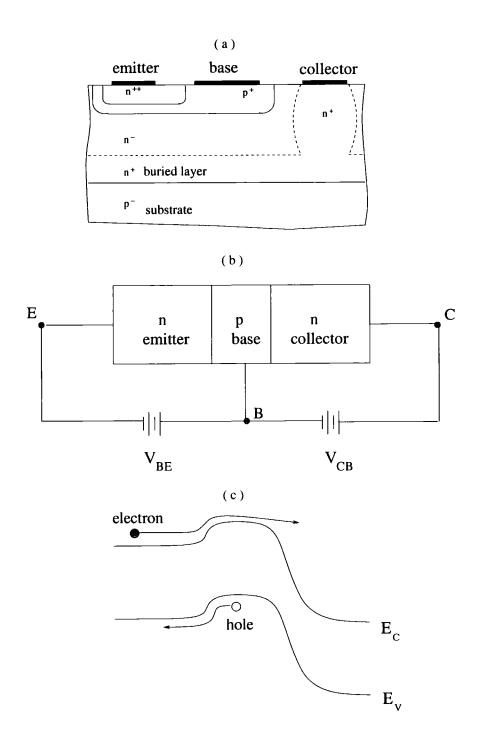

Figure 2.12: (a) Two-dimensional representation of the structure of a vertical npn BJT. (b) Schematic diagram illustrating the applied voltages in normal operation, (c) Corresponding band-diagram with carrier flows indicated.

emitter, base and collector formed by adjacent layers of the structure as illustrated in Figure 2.12(a). However, it is possible to produce lateral transistors where different parts of the device are fabricated using lithographic methods. Since the vertical dimensions can be made smaller than the lateral dimensions, vertical transistors are preferable for high-speed applications. However, lateral bipolar junction transistors (LBJTs) can be incorporated into a MOSFET-based integrated circuit with minor modifications to processing methods. A Si lateral bipolar junction transistor can be derived from a standard Si n-channel MOSFET by using an ohmic gate electrode to make contact to the p-Si channel which is used to form a base. In addition the use of thin-film silicon-on-insulator (SOI) technology for LBJTs permits simple circuit integration. An LBJT using SOI technology is an attractive device because of its low parasitic capacitances and simple fabrication process. In principle, it provides a good alternative to the MOSFET since, for extremely thin gate oxides, the gate leakage current of a MOSFET become comparable to the base current of an LBJT. At the same time, the LBJT could offer a highly scalable approach for CMOS circuits.

There are two types of bipolar devices; the n-p-n type, which has a p-type base and n-type emitter and collector, and the p-n-p type, which has an n-type base and p-type emitter and collector. We will concentrate on the n-p-n transistor operating in the active mode as illustrated in Figure 2.12(b). The emitter-base junction is forward biased, resulting in holes being injected from the base into the emitter, and electrons being injected from the emitter into the base. However, since the emitter is more heavily doped than the base, the electron current dominates and depends exponentially on the forward bias of the junction. The base-collector is reverse biased and so in the absence of any other effects there would be only a small leakage current flow at the base-collector junction. However, essentially all the electrons injected from the emitter into the base reach the collector, and give rise to a collector current, since the base width (typically  $0.1~\mu m$  or less) is much less than the electron diffusion length. The

2.7. Summary 33

holes injected from the base into the emitter give rise to a base current. The current gain of a bipolar transistor is defined as the ratio of its collector current to its base current. Thus one basic objective in bipolar transistor design is to achieve a collector current significantly larger than the base current and hence obtain current amplification.

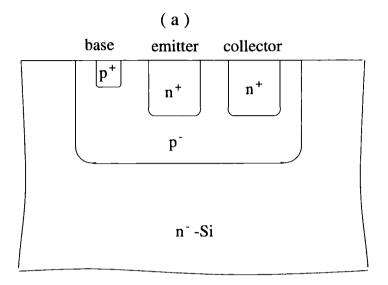

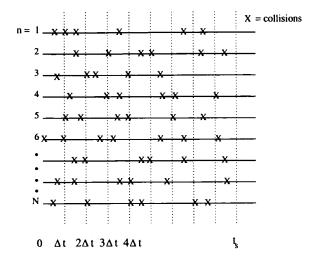

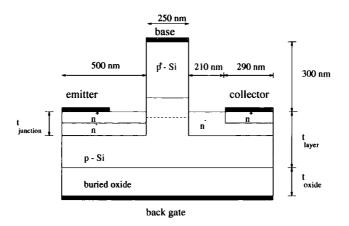

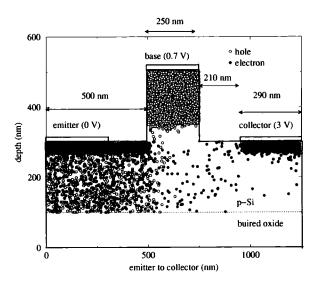

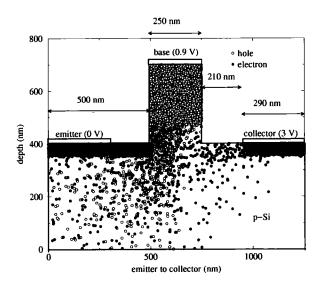

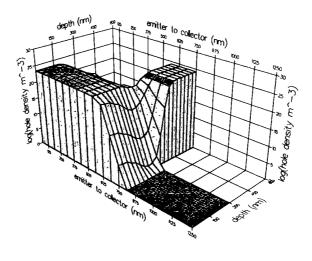

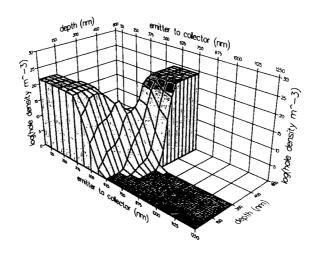

Figure 2.13(a) shows a schematic cross-section of a lateral npn transistor, available in a typical CMOS process. Figure 2.13(b) illustrates the modelled lateral SOI bipolar transistor whose simulation results are reported and analysed in Chapter 5. The emitter, intrinsic base, and collector region are laterally formed in thin-film SOI. Note from Figure 2.13(b) that the heavy p<sup>+</sup> doping at the top of the base pedestal provides a low-resistance ohmic contact and a built-in electric field which repels electrons in the base away from the metal base contact [39].

## 2.7 Summary

In this chapter, we have described the relevant properties of Si and SiGe alloys. The effects of strain on the band structure and the electron transport properties have been explained. In particular, we have pointed out that the strain present in a Si/Si<sub>1-x</sub>Ge<sub>x</sub> heterostructure breaks the six-fold degeneracy of the Si  $\Delta$  valleys, resulting in an improved conduction band offset, a low in-plane effective mass at the conduction band edge, and reduced intervalley scattering. Thus, the strain provides an additional variable parameter, which can be used to tailor the device parameters discussed in Section 2.4. Specifically, a combination of bandgap engineering and strain can be used to produce an n-channel MODFET structure, in which a thin silicon channel is placed under tensile strain as discussed in Section 2.5. In Chapter 4 we shall present simulation results of n-strained Si channel MODFETs. In addition, the npn-SOI LBJT, which could be particularly suitable in dense high performance CMOS technology, has been introduced and the basic operation described. Chapter 5 of this thesis is devoted

Figure 2.13: (a) Lateral bipolar junction transistor (LBJT) [40]. (b) Twodimensional representation of the structure of a npn SOI-LBJT whose simulation results are reported in Chapter 5.

to simulations of npn-SOI LBJTs.

# Chapter 3

# Monte Carlo Simulation

### 3.1 Introduction

In order to describe the behaviour of carriers in a semiconductor device at a microscopic level, we have to solve the Boltzmann transport equation (BTE) for the structure. The BTE describes the time evolution of the carrier distribution in real and reciprocal space through the motion of particles, the forces acting on them and their scatterings. Since the Boltzmann equation is a nonlinear integro-differential equation, it can only be solved analytically in certain simple cases, and practical problems require the use of approximations or numerical methods. Monte Carlo (MC) simulation is one such numerical method and is the approach used in the research reported in this thesis. In Monte Carlo simulation [22,41-44], a computer is used to predict the trajectories in real and reciprocal space of typically tens of thousands of particles which are representative of electrons and holes in the real device. As a result, microscopic and macroscopic quantities (such as the carrier distribution functions, carrier mean velocity, device current, cut-off frequency, etc.) can be predicted. Monte Carlo simulation is extremely powerful because it is possible to incorporate detailed band structure information, band and wavevector-dependent carrier scattering events and realistic device geometries in a device model. The method is well suited to the analysis of non-stationary carrier transport in submicron semiconductor devices, in which the electric field varies appreciably over distances comparable with the electron mean free path or on time scales which are comparable to mean free flight times. Hence it is possible to include many new and interesting non-equilibrium carrier dynamics such as ballistic transport and velocity overshoot which become important as device dimensions shrink to the deep sub-micrometer scale. In many cases, Monte Carlo simulation is in fact the most accurate technique available for analysing transport in devices [45].

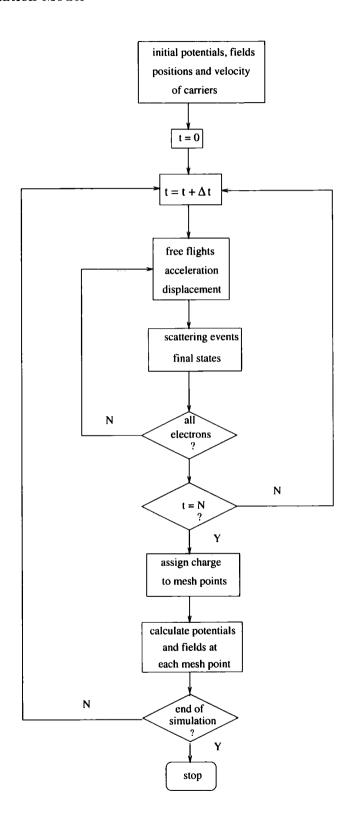

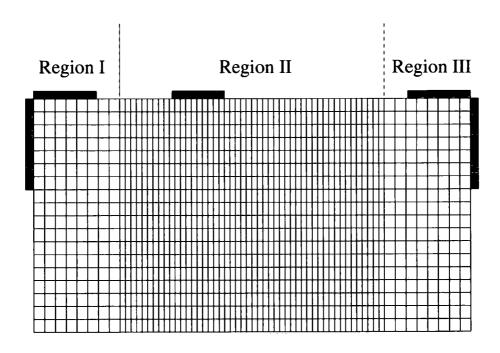

This chapter is devoted to the description of the ensemble Monte Carlo method used in the device simulations described in Chapters 4 and 5. First, the Boltzmann transport equation is introduced and some common methods of solution are mentioned. The general methodology of the Monte Carlo simulation of carrier transport in bulk material is described in Section 3.3. Section 3.4 presents the band structure model used in the simulations. The carrier scattering mechanisms relevant to Si and SiGe alloys are described in Section 3.5. The application of the Monte Carlo method to the analysis of semiconductor devices is discussed in Section 3.6.

# 3.2 The Boltzmann transport equation

The quantum mechanical state of an electron in a crystal is specified by a band index and a wavevector  $\mathbf{k}$  in the first Brillouin zone. For each band there is a definite relationship between the electron energy E and the wavevector. In the semiclassical model the electron can also be ascribed a position  $\mathbf{r}$  in real space. (Note this is not possible in a fully quantum mechanical theory since the specification of both  $\mathbf{r}$  and  $\mathbf{k}$  is a contradiction of the Heisenberg Uncertainty Principle). Hence the dynamics of each electron can be represented by a moving point in a six-dimensional phase space  $(\mathbf{r}, \mathbf{k})$ .

38

The equation of motion for the particle is given by

$$\hbar \dot{\mathbf{k}} = -e\mathbf{F} \tag{3.1}$$

$$\dot{\mathbf{r}} = \mathbf{v} = \frac{1}{\hbar} \nabla_k E(\mathbf{k}) \tag{3.2}$$

where e is the magnitude of electronic charge, and  $\mathbf{F}$  is the electric field. Equations 3.1 and 3.2 are the equation of motion of free electrons in a perfect crystal. In reality, this so called ballistic motion is interrupted by collisions with impurities, phonons, defects, etc. If a collision is instantaneous, it may be visualised as the electron disappearing and instantaneously reappearing at a different value of  $\mathbf{k}$  of the phase space.

We can define a distribution  $f(\mathbf{r}, \mathbf{k}, t)$  that represents the probability of finding an electron at position  $\mathbf{r}$ , with vector  $\mathbf{k}$  and at time t.  $f(\mathbf{r}, \mathbf{k}, t)$  describes the distribution of carriers in both the position and the momentum and can be used to obtain various quantities of interest such as the mean carrier density, kinetic energy, and so forth. The equation for the distribution function f is called the Boltzmann transport equation:

$$\frac{\partial f}{\partial t} + \mathbf{v} \cdot \nabla_{\mathbf{r}} f + \dot{\mathbf{k}} \cdot \nabla_{\mathbf{k}} f = \left(\frac{\partial f}{\partial t}\right)_{coll} \tag{3.3}$$

where  $\partial f/\partial t_{coll}$  represents the change in f due to electron scattering, and can be expressed as:

$$\left(\frac{\partial f}{\partial t}\right)_{coll} = \int [S(\mathbf{k}', \mathbf{k}) f_{\mathbf{k}'} (1 - f_{\mathbf{k}}) - S(\mathbf{k}, \mathbf{k}') f_{\mathbf{k}} (1 - f_{\mathbf{k}'})] dV_{\mathbf{k}'}$$

(3.4)

where the integration is over the first Brillouin zone.  $S(\mathbf{k}, \mathbf{k}')dV_{\mathbf{k}'}$  is the conditional rate of transitions from the state  $\mathbf{k}$  to the states  $\mathbf{k}'$  in  $dV_{\mathbf{k}'}$  given that there is initially an electron in state  $\mathbf{k}$  and state  $\mathbf{k}'$  is empty.

The Boltzmann equation is generally difficult to solve. However, some analytical approaches to achieve approximate closed-form solutions have been developed for the case of carrier transport in bulk material. For example, in low electric fields a solution may be based on the fact that the distribution function will not be very different

from the equilibrium Fermi-Dirac distribution function. For elastic scattering (such as impurity, acoustic phonon, or piezoelectric scattering) one may use a relaxation time approximation (RTA) where  $\partial f/\partial t_{coll}$  is taken equal to  $-(f-f_0)/\tau$ , where  $f_0$  is the equilibrium distribution function, and  $\tau$  is the relaxation time constant. However, for most semiconductors, all the scattering processes are not elastic and the relaxation time approximation usually fails to provide adequate accuracy for calculating the transport properties. Rode's iterative procedure [46] is a numerical method to calculate the distribution function, but is straightforward to implement and is not demanding on computer resources. However, this method is limited to cases where the carriers remain in one band and to low electric fields where linear response is valid.

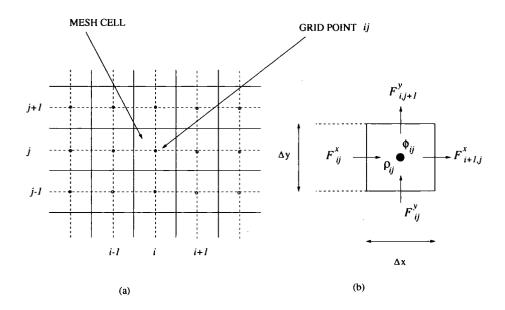

The Monte Carlo method is a more general numerical but computationally intensive approach which is based on the simulation of the carriers dynamics in a semiconductor. It provides numerical solutions to the Boltzmann transport equation by stochastically tracking the movements of a set of representative particles in phase space under the action of the electric field and the various carrier scattering processes. When coupled with a self-consistent numerical solver for Poisson's equation, the Monte Carlo method permits the exploration of the properties of realistic two- and three-dimensional models of semiconductor devices and the investigation of the microscopic detail underlying the device behaviour. It is Monte Carlo simulation which is used for device modelling in the research reported here, and the rest of this chapter is devoted to an outline of the simulation method.

## 3.3 Monte Carlo simulation

The Monte Carlo (MC) method solves the Boltzmann transport equation by simulating the motion of electrons and holes in the bulk semiconductor medium or device structure. The main feature of the MC method is that a carrier is treated as a point-like

semiclassical particle moving under the action of the local electric field and the scattering processes. The individual trajectories of carriers are computed by the following steps:

- 1. Each carrier is moved in real and reciprocal space in the "free flight" between collisions under the action of the electric field. This is done by solving Equations 3.1 and 3.2 in the crystal.

- 2. The carriers scatter conditionally at the end of their free flights. The duration of a free flight and the new state after scattering are chosen stochastically in accordance with quantum mechanical theory.

Such an approach requires a knowledge and appropriate description of the band structure of the semiconductor.

### 3.4 Band Structure

In the absence of applied electric field, carriers reside close to the edges of the bands on either side of the fundamental gap. The relationship between the momentum  $\mathbf{k}$  and the energy  $E(\mathbf{k})$  of an electron close to the minimum of the conduction band can be described by various models at different levels of complexity.

#### (a) Parabolic Bands

The simplest model of a valley in the conduction band is to assume a parabolic and isotropic relation between energy and wavevector. Specifically

$$E(\mathbf{k}) = \frac{\hbar^2 |\mathbf{k}|^2}{2m_*^*} \tag{3.5}$$

where  $m_o^*$  is the effective mass at the conduction band minimum. The particle velocity is evaluated as

$$\mathbf{v} = \frac{1}{\hbar} \nabla_k E(\mathbf{k}) = \frac{\hbar \mathbf{k}}{m_o^*} \tag{3.6}$$

and gives the simple relation for the electron momentum

$$\mathbf{p} = \hbar \mathbf{k} = m_o^* \mathbf{v} \tag{3.7}$$

#### (b) Non-parabolic Bands

In general conduction band valleys are not parabolic but for sufficiently small  $\mathbf{k}$  may often be described by the approximate formula

$$E(\mathbf{k})(1 + \alpha E(\mathbf{k})) = \frac{\hbar^2 |\mathbf{k}|^2}{2m_o^*}$$

(3.8)

where  $\alpha$  is the coefficient of nonparabolicity and has the dimensions of an inverse energy [47]. The solution of equation (3.8) for the energy in terms of wavevector is

$$E(\mathbf{k}) = \frac{1}{2\alpha} \left( \sqrt{1 + \frac{4\alpha\hbar^2 |\mathbf{k}|^2}{2m_o^*}} - 1 \right)$$

(3.9)

The particle velocity is

$$\mathbf{v} = \frac{1}{\hbar} \nabla_k E(\mathbf{k}) = \frac{\hbar \mathbf{k}}{m_o^*} \left( 1 + 4\alpha \frac{\hbar^2 |\mathbf{k}|^2}{2m_o^*} \right)^{-1/2}$$

(3.10)

which, using (3.9), can be written as

$$\mathbf{v} = \frac{\hbar \mathbf{k}}{m_o^* [1 + 2\alpha E(\mathbf{k})]} \tag{3.11}$$

So far, a spherically symmetric band (or isotropic effective mass) has been assumed. This is normally a good approximation for the  $\Gamma$  valley of GaAs, which is at the centre of the Brillouin zone. In the cases of Si and Ge, a number of degenerate valleys

away from the zone centre form the conduction band edge and the constant energy surfaces for these valleys are ellipsoids rather than a sphere. Ge has eight valleys with their minima at the edge of the Brillouin zone in the [111] directions, called the L-points. Si has six valleys with minima at approximately  $\mathbf{k} = (2\pi/a)(0.85, 0, 0)$ , and the equivalent points, which are close to the X-points at the edge of the Brillouin zone. In an ellipsoidal valley the mass is not isotropic, and is instead described by a tensor with components

$$m_{ij}^* = \hbar^2 \left( \frac{\partial^2 E}{\partial k_i \partial k_j} \right)^{-1} \tag{3.12}$$

where i, j denote the Cartesian axes. The  $E - \mathbf{k}$  relation for an ellipsoidal constant energy surface is

$$E = \frac{\hbar^2}{2} \left( \frac{k_x^2}{m_x} + \frac{k_y^2}{m_y} + \frac{k_z^2}{m_z} \right) \tag{3.13}$$

where  $k_x, k_y, k_z$  are the components of  $\mathbf{k}$  along the principal axes of the ellipsoid measured from the position of the minimum, and  $m_x, m_y, m_z$  are the corresponding effective masses. For Si, the surfaces of constant energy are ellipsoids of revolution and the  $E-\mathbf{k}$  relation in the conduction band can be expressed as