## **Durham E-Theses**

## Just-in-time Hardware generation for abstracted reconfigurable computing

Grocutt, Thomas Christopher

How to cite:

Grocutt, Thomas Christopher (2005) Just-in-time Hardware generation for abstracted reconfigurable computing, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/2704/

#### Use policy

$The full-text\ may\ be\ used\ and/or\ reproduced,\ and\ given\ to\ third\ parties\ in\ any\ format\ or\ medium,\ without\ prior\ permission\ or\ charge,\ for\ personal\ research\ or\ study,\ educational,\ or\ not-for-profit\ purposes\ provided\ that:$

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

Academic Support Office, The Palatine Centre, Durham University, Stockton Road, Durham, DH1 3LE e-mail: e-theses.admin@durham.ac.uk Tel: +44 0191 334 6107 http://etheses.dur.ac.uk

# Just-In-Time Hardware Generation For Abstracted Reconfigurable Computing

## **Thomas Christopher Grocutt**

The copyright of this thesis rests with the author or the university to which it was submitted. No quotation from it, or information derived from it may be published without the prior written consent of the author or university, and any information derived from it should be acknowledged.

A Thesis presented for the degree of Doctor of Philosophy

Centre for Electronic Systems

School of Engineering

University of Durham

England

1.4

2005

1 1 OCT 2006

# Declaration

The work in this thesis is based on research carried out in the Centre for Electronic Systems, School of Engineering, University of Durham, England. No part of this thesis has been submitted elsewhere for any other degree or qualification and it is all my own work unless otherwise referenced to the contrary in the text.

## Copyright © 2005 by Thomas Christopher Grocutt.

The copyright of this thesis rests with the author. No quotation from it should be published in any format, including electronic and the Internet, without the author's prior written consent. All information derived from this thesis must be acknowledged appropriately.

# Acknowledgements

I would like to thank my project supervisor, Simon Johnson, for his time, help and encouragement; the staff in the engineering department for their continued help and the AIG group in the department of physics for allowing me to use their Cray XD1. In particular, I would like to thank my father for his patience whilst proof reading this thesis. I would also like to thank the open source programming team that created LATEX and thus saving me from Word.

. . 3-12

## Abstract

This thesis addresses the use of reconfigurable hardware in computing platforms, in order to harness the performance benefits of dedicated hardware whilst maintaining the flexibility associated with software. Although the reconfigurable computing concept is not new, the low level nature of the supporting tools normally used, together with the consequent limited level of abstraction and resultant lack of backwards compatibility, has prevented the widespread adoption of this technology. In addition, bandwidth and architectural limitations, have seriously constrained the potential improvements in performance. A review of existing approaches and tools flows is conducted to highlight the current problems being faced in this field.

The objective of the work presented in this thesis is to introduce a radically new approach to reconfigurable computing tool flows. The runtime based tool flow introduces complete abstraction between the application developer and the underlying hardware. This new technique eliminates the ease of use and backwards compatibility issues that have plagued the reconfigurable computing concept, and could pave the way for viable mainstream reconfigurable computing platforms. An easy to use, cycle accurate behavioural modelling system is also presented, which was used extensively during the early exploration of new concepts and architectures. Some performance improvements produced by the new reconfigurable computing tool flow, when applied to both a MIPS based embedded platform, and the Cray XD1, are also presented. These results are then analyzed and the hardware and software factors affecting the performance increases that were obtained are discussed, together with potential techniques that could be used to further increase the performance of the system.

Lastly a heterogenous computing concept is proposed, in which, a computer system, containing multiple types of computational resource is envisaged, each having their own strengths and weaknesses (e.g. DSPs, CPUs, FPGAs). A revolutionary new method of fully exploiting the potential of such a system, whilst maintaining scalability, backwards compatibility, and ease of use is also presented.

# Contents

|   | Ack  | knowledgements                       | iii |  |  |  |

|---|------|--------------------------------------|-----|--|--|--|

|   | Abs  | stract                               | iv  |  |  |  |

|   | List | t of Figures                         | xvi |  |  |  |

|   | List | t of Tables                          | xix |  |  |  |

|   | List | t of Listings                        | xx  |  |  |  |

|   | Glo  | ossary                               | 1   |  |  |  |

| 1 | Intr | roduction                            | 4   |  |  |  |

|   | 1.1  | Conventional Computing Architectures | 4   |  |  |  |

|   |      | 1.1.1 Instruction Set Expansion      | 4   |  |  |  |

|   |      | 1.1.2 Dedicated Hardware             | 5   |  |  |  |

|   | 1.2  | Reconfigurable Computing             |     |  |  |  |

|   |      | 1.2.1 Hardware Implementations       | 7   |  |  |  |

|         |     |        | 1.2.1.1   | Direct Processor Integration                                                                                            | 7 |

|---------|-----|--------|-----------|-------------------------------------------------------------------------------------------------------------------------|---|

|         |     |        | 1.2.1.2   | External RC Area                                                                                                        | 9 |

|         |     | 1.2.2  | Tools Fl  | ows                                                                                                                     | 1 |

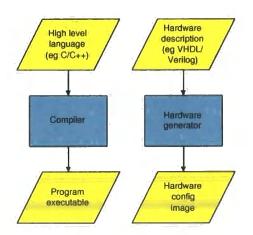

|         |     |        | 1.2.2.1   | Separate SW And HW Tool Flows                                                                                           | 1 |

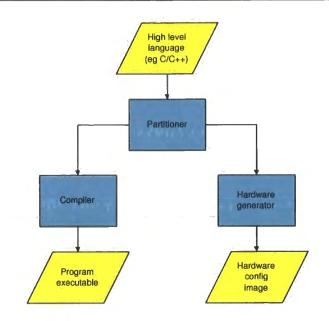

|         |     |        | 1.2.2.2   | Common High Level Language                                                                                              | 2 |

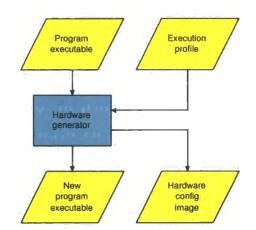

|         |     |        | 1.2.2.3   | Low Level Tool Flows                                                                                                    | 5 |

|         |     | 1.2.3  | Scheduli  | $ng \ldots 10$ | 6 |

|         |     | 1.2.4  | Floating  | Point Maths                                                                                                             | 7 |

|         | 1.3 | Resear | rch Condu | $\mathbf{r}$                                                                                                            | 8 |

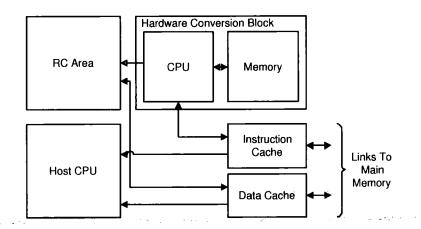

|         | 1.4 | Warp   | Processin | g                                                                                                                       | 0 |

|         |     | 1.4.1  | Hardwar   | re Platforms                                                                                                            | 0 |

|         |     | 1.4.2  | Tool Flo  | w                                                                                                                       | 1 |

|         |     | 1.4.3  | Perform   | ance Improvements                                                                                                       | 2 |

|         | 1.5 | Summ   | ary       |                                                                                                                         | 3 |

| 2       | Beh | aviour | al Simul  | ation 2                                                                                                                 | 5 |

|         | 2.1 | Backg  | round .   |                                                                                                                         | 5 |

|         | 2.2 | CPUS   | im        |                                                                                                                         | 7 |

| •• • •• |     | 2.2.1  | Concurr   | ency                                                                                                                    | 7 |

|         |     | 2.2.2  | Flexibili | ty                                                                                                                      | 0 |

.

|      | 2.2.3    | Instantiation and Connection          | 32 |

|------|----------|---------------------------------------|----|

|      | 2.2.4    | Visualisation and Statistics          | 34 |

| 2.3  | 8 Summ   | ary                                   | 35 |

| 3 EI | PIC Sim  | ulation                               | 37 |

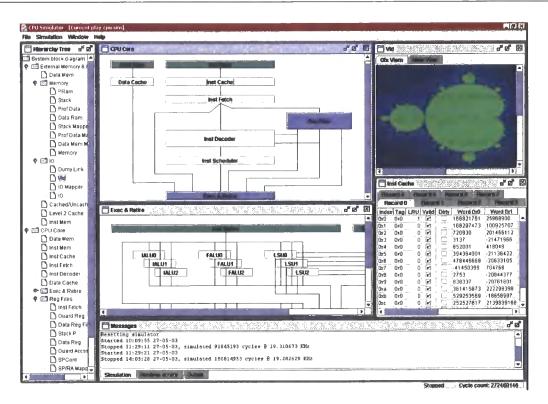

| 3.1  | . CPU /  | Architecture                          | 37 |

|      | 3.1.1    | Additional RC Hardware Blocks         | 38 |

|      |          | 3.1.1.1 Code Profiler                 | 39 |

|      |          | 3.1.1.2 Reconfigurable Execution Unit | 39 |

| 3.2  | RC Co    | onversion Algorithms                  | 40 |

|      | 3.2.1    | Instruction Combination               | 40 |

|      | 3.2.2    | Loop Conversion                       | 43 |

|      |          | 3.2.2.1 Data Flow Pipeline            | 44 |

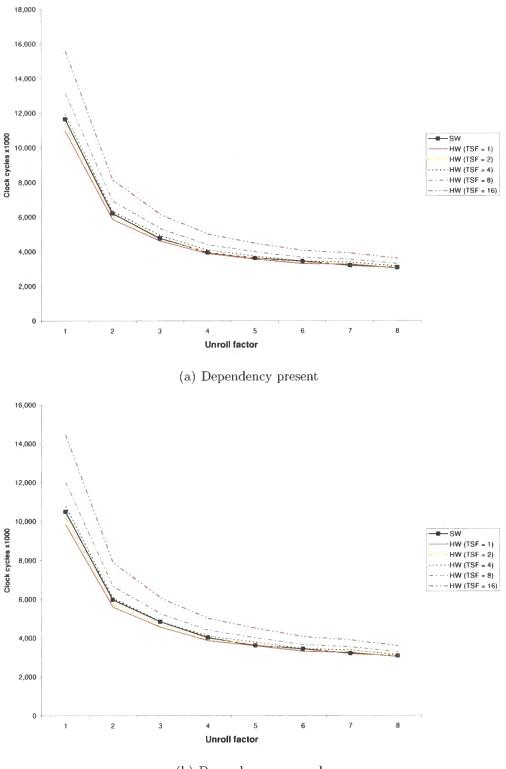

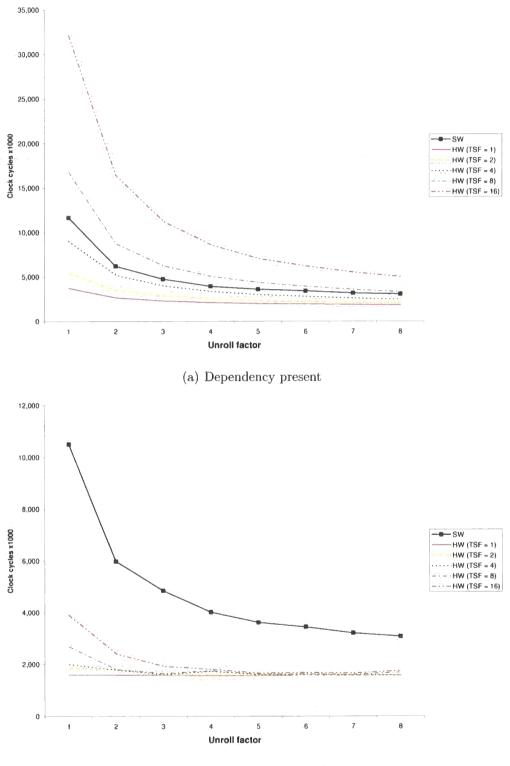

| 3.3  | 8 Perfor | mance evaluation                      | 46 |

|      | 3.3.1    | Test Algorithms                       | 46 |

|      |          | 3.3.1.1 Copy algorithm                | 47 |

|      |          | 3.3.1.2 Half Brightness Algorithm     | 47 |

|      |          | 3.3.1.3 Mandelbrot Algorithm          | 47 |

|      | 3.3.2    | Loop Dependencies                     | 47 |

| 3.4  | l Result | 8                                     | 48 |

|       |                    | 3.4.1  | Copy algorithm               | 48 |

|-------|--------------------|--------|------------------------------|----|

|       |                    | 3.4.2  | Half Brightness Algorithm    | 49 |

|       |                    | 3.4.3  | Mandelbrot Algorithm         | 51 |

|       |                    | 3.4.4  | HW Pipeline Implementation   | 54 |

|       |                    | 3.4.5  | Summary                      | 57 |

| 4     | Loo                | p Con  | version                      | 58 |

|       | 4.1                | Abstra | act Instruction Model        | 60 |

|       |                    | 4.1.1  | Supporting Additional ISAs   | 61 |

|       | 4.2                | Target | ing The Hardware Pipeline    | 62 |

|       | 4.3                | Loop ] | Identification               | 63 |

|       | 4.4                | Instru | ction Linearization          | 64 |

|       |                    | 4.4.1  | MUX Insertion                | 65 |

|       |                    | 4.4.2  | Instruction Guarding         | 66 |

|       | 4.5                | Optim  | ization                      | 66 |

|       |                    | 4.5.1  | Hardware Dependency Removal  | 67 |

|       |                    | 4.5.2  | Stack Removal                | 67 |

|       |                    | 4.5.3  | Iteration Dependency Removal | 68 |

| ·. •. | u e s une sour fer | 4.5.4  | Instruction Removal          | 69 |

|       |                    | 4.5.5  | Tree Re-balancing            | 70 |

and the second second

|   | 4.6 | Pipelin | ne Generation                     | L |

|---|-----|---------|-----------------------------------|---|

|   |     | 4.6.1   | Operation Scheduling              | L |

|   |     |         | 4.6.1.1 Pointer Aliasing          | 3 |

|   |     | 4.6.2   | Data Forwarder Addition           | 1 |

|   |     | 4.6.3   | Register Remapping                | 1 |

|   | 4.7 | Target  | Implementation                    | 5 |

|   |     | 4.7.1   | Pipeline configuration generation | 5 |

|   |     | 4.7.2   | Program modification              | 3 |

| 5 | MIF | PS Test | t Platform 78                     | 3 |

|   | 5.1 | Platfor | rm Details                        | 3 |

|   |     | 5.1.1   | RC Area Integration               | • |

|   |     | 5.1.2   | Hardware                          | ) |

|   |     |         | 5.1.2.1 CPU/RC Area Interface     | 1 |

|   | 5.2 | Softwa  | re                                | 3 |

|   |     | 5.2.1   | Console Software                  | 3 |

|   |     | 5.2.2   | Data Transfer Software            | 7 |

|   | 5.3 | Test A  | lgorithms                         | 7 |

|   |     | 5.3.1   | PRBS Generator                    | 3 |

|   |     | 5.3.2   | FFT                               | 1 |

|     | 5.3.3   | Low Pass Filter                | 1 |

|-----|---------|--------------------------------|---|

|     | 5.3.4   | Normalization                  | 2 |

|     | 5.3.5   | Block Search                   | 2 |

|     | 5.3.6   | Mandelbrot                     | 4 |

|     | 5.3.7   | Half Brightness                | 4 |

|     | 5.3.8   | Factorial and Series Sum       | 5 |

|     | 5.3.9   | Сору                           | 6 |

|     | 5.3.10  | Sort                           | 6 |

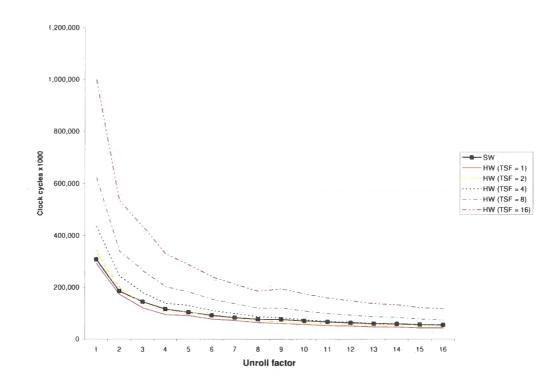

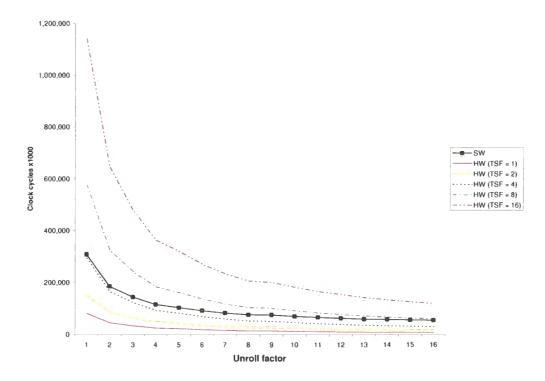

| 5.4 | Perform | mance Scalability              | 7 |

|     | 5.4.1   | Bandwidth                      | 7 |

|     | 5.4.2   | Parallelism                    | 3 |

|     | 5.4.3   | Algorithm Complexity           | 0 |

|     |         | 5.4.3.1 Increased section size | 1 |

|     |         | 5.4.3.2 Increased complexity   | 2 |

| 5.5 | Platfor | rm Evaluation                  | 3 |

|     | 5.5.1   | Abstraction                    | 3 |

|     | 5.5.2   | Automatic conversion           | 3 |

|     | 5.5.3   | Low conversion time            | 4 |

|     | 5.5.4   | Large performance increase     | 4 |

|   | 5.6 | Summ   | ary                                                                                                                         |

|---|-----|--------|-----------------------------------------------------------------------------------------------------------------------------|

| 6 | Cra | y XD1  | Platform 106                                                                                                                |

|   | 6.1 | Cray Z | XD1 Overview $\ldots \ldots 106$ |

|   | 6.2 | Platfo | rm Details                                                                                                                  |

|   |     | 6.2.1  | Execution                                                                                                                   |

|   |     | 6.2.2  | Tool flow                                                                                                                   |

|   |     | 6.2.3  | Memory Access                                                                                                               |

|   | 6.3 | Perfor | mance Evaluation                                                                                                            |

|   |     | 6.3.1  | PRBS Generator                                                                                                              |

|   |     | 6.3.2  | Half Brightness                                                                                                             |

|   |     | 6.3.3  | Low Pass Filter                                                                                                             |

|   |     | 6.3.4  | Normalization                                                                                                               |

|   |     | 6.3.5  | Copy                                                                                                                        |

|   |     | 6.3.6  | Series Sum                                                                                                                  |

|   | 6.4 | MIPS   | RC Platform Comparison                                                                                                      |

|   | 6.5 | Summ   | ary                                                                                                                         |

|   |     | 6.5.1  | Cray XD1 Platform Limitations                                                                                               |

|   |     | 6.5.2  | Clock Speeds                                                                                                                |

|   |     | 6.5.3  | Performance Improvements                                                                                                    |

| 7 | Opt | imisat  | ions Of The Reconfigurable Computing System 1 | <b>25</b> |

|---|-----|---------|-----------------------------------------------|-----------|

|   | 7.1 | Hardw   | vare Conversion Tools                         | .25       |

|   |     | 7.1.1   | Loop Extraction                               | .25       |

|   |     | 7.1.2   | Floating Point Operations                     | .27       |

|   |     | 7.1.3   | Optimization                                  | .27       |

|   |     | 7.1.4   | Scheduling                                    | .28       |

|   |     |         | 7.1.4.1 Operation Variants                    | .28       |

|   |     |         | 7.1.4.2 Local Feedback                        | .29       |

|   |     |         | 7.1.4.3 DMA Operation Scheduling              | .30       |

|   |     |         | 7.1.4.4 FPGA Tool Integration                 | .30       |

|   |     | 7.1.5   | Hardware Software Integration                 | .31       |

|   | 7.2 | Platfo  | rms                                           | .32       |

|   |     | 7.2.1   | MIPS                                          | .32       |

|   |     | 7.2.2   | XD1                                           | .33       |

|   |     | 7.2.3   | Benchmark Algorithms                          | .34       |

|   | 7.3 | An Id   | eal Reconfigurable Computing Platform         | .35       |

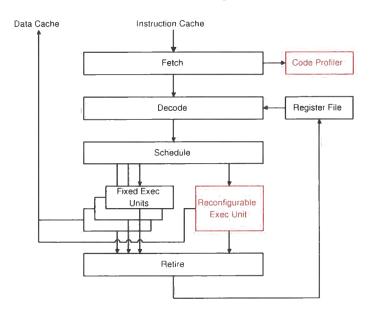

|   |     | 7.3.1   | Processor Integration                         | .35       |

|   |     | 7.3.2   | Homogeneous RC Area                           |           |

|   |     | . 1.1 × | 7.3.2.1 Partial Reconfigurability             |           |

## xiii

|   |     |         | 7.3.2.2    | Homogeneous Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 138 |

|---|-----|---------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|   |     |         | 7.3.2.3    | Configuration Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 139 |

|   |     |         | 7.3.2.4    | Specialized Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 139 |

|   |     |         | 7.3.2.5    | Design For Place And Route                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 140 |

|   |     |         | 7.3.2.6    | Clock Domains                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 140 |

|   |     | 7.3.3   | Memory     | Sub-System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 141 |

|   |     | 7.3.4   | Code Pr    | ofiling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 142 |

|   |     | 7.3.5   | Hardwar    | e Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 143 |

|   | 7.4 | Hetero  | geneous (  | Computing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 144 |

|   | 7.5 | Future  | e Research | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 147 |

|   | 7.6 | Summ    | ary        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 148 |

| 8 | Con | nclusio | n          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 150   |

|   | Bib | liograp | ohy        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 156   |

| Α | MI  | PS Tes  | t Algori   | thms Source Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 172   |

|   | A.1 | PRBS    | Generato   | or (Standard)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 172 |

|   | A.2 | PRBS    | Generato   | or (Unrolled)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 173 |

|   |     |         |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

|   |     |         |            | <pre>// constraints and constr</pre> |       |

| A.5  | Normalization            |

|------|--------------------------|

| A.6  | Block Search (Planar)    |

| A.7  | Block Search (Packed)    |

| A.8  | Mandelbrot               |

| A.9  | Half Brightness          |

| A.10 | Factorial and Series Sum |

| A.11 | Сору                     |

| A.12 | Sort                     |

# List of Figures

| 1.1 | Separate SW and HW tool chains                                                                                                                                                        | 11 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Common high level language                                                                                                                                                            | 13 |

| 1.3 | Low level tool chain                                                                                                                                                                  | 15 |

| 1.4 | Warp processor architecture                                                                                                                                                           | 21 |

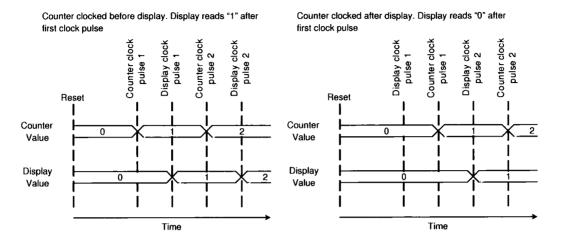

| 2.1 | Single function clocking                                                                                                                                                              | 29 |

| 2.2 | Dual function clocking                                                                                                                                                                | 29 |

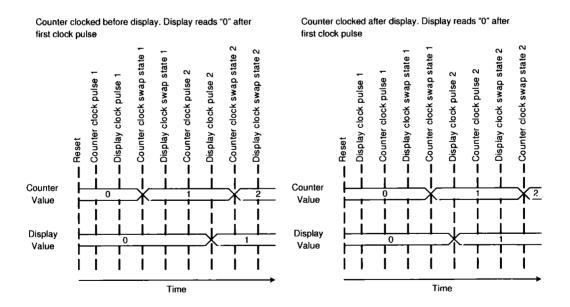

| 2.3 | CPUSim simulating an experimental processor, showing the contents<br>of the instruction cache and a Mandelbrot fractal generated by soft-<br>ware running on the simulated processor. | 35 |

| 3.1 | EPIC CPU core with additional RC blocks shown in red                                                                                                                                  | 38 |

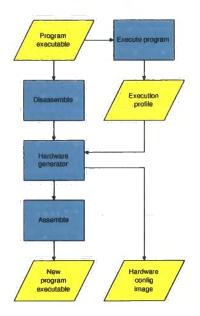

| 3.2 | EPIC CPU RC tool flow                                                                                                                                                                 | 41 |

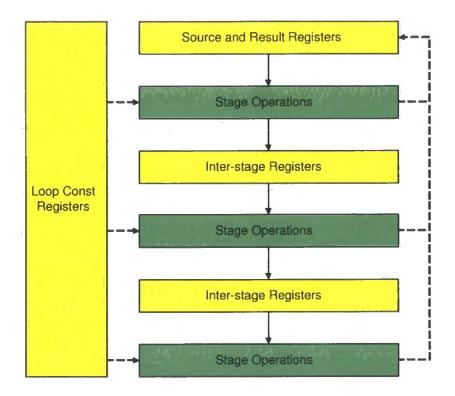

| 3.3 | Example RC data flow pipeline                                                                                                                                                         | 44 |

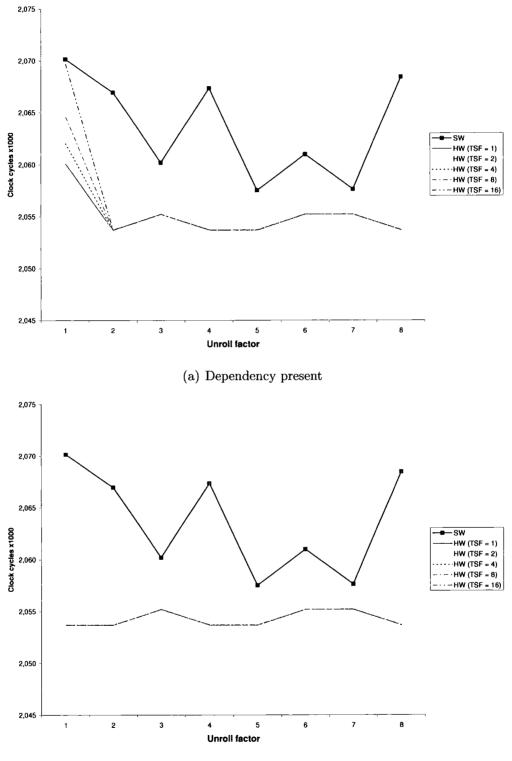

| 3.4 | Performance improvement of copy algorithm with loop extraction                                                                                                                        | 50 |

|   | 3.5 | Performance improvement of half brightness algorithm with instruc-                                         |     |

|---|-----|------------------------------------------------------------------------------------------------------------|-----|

|   |     | tion combination $\ldots$ | 52  |

|   | 3.6 | Performance improvement of half brightness algorithm with loop ex-                                         |     |

|   |     | traction                                                                                                   | 53  |

|   | 3.7 | Performance improvement of Mandelbrot algorithm with instruction                                           |     |

|   |     | combination                                                                                                | 55  |

|   | 3.8 | Performance improvement of Mandelbrot algorithm with loop extrac-                                          |     |

|   |     | tion                                                                                                       | 55  |

|   | 3.9 | FPGA tiles used to implement real hardware data flow pipeline                                              | 56  |

|   |     |                                                                                                            |     |

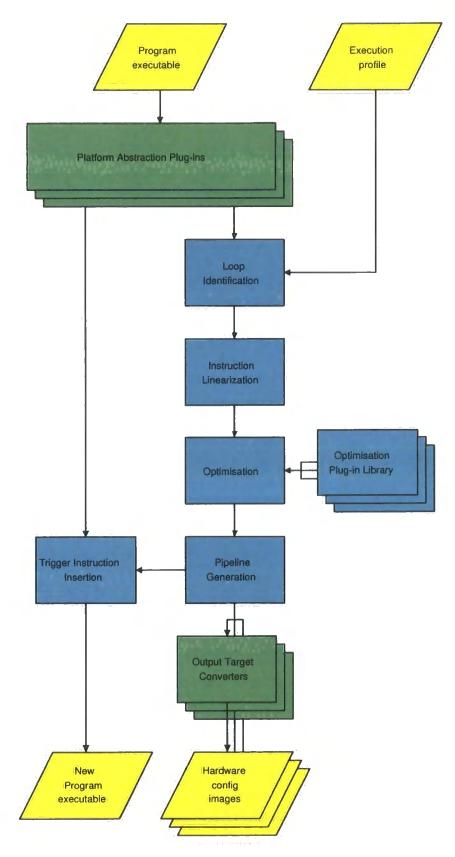

|   | 4.1 | Simplified Loop conversion block diagram                                                                   | 59  |

|   | 4.2 | Example operation scheduling onto data flow pipeline                                                       | 72  |

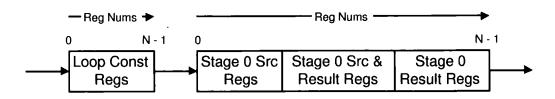

|   | 4.3 | Loop constant and stage 0 shift register arrangement                                                       | 75  |

|   |     |                                                                                                            |     |

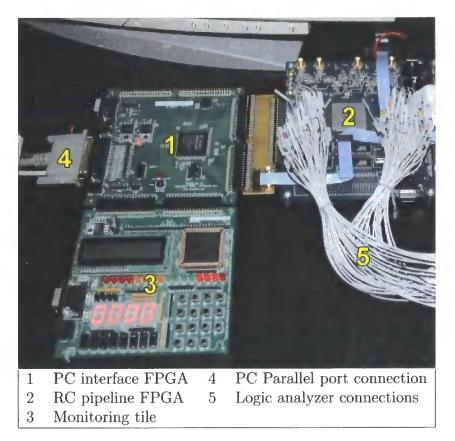

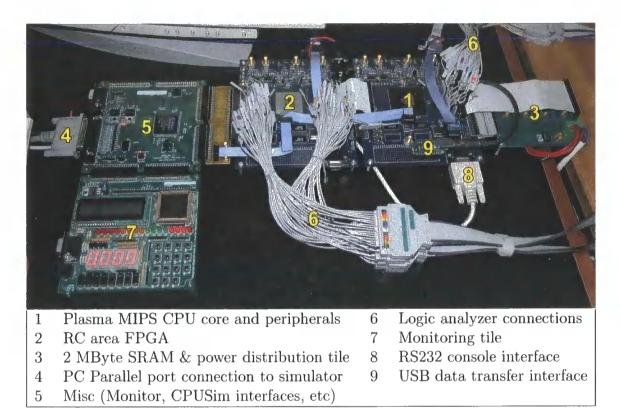

|   | 5.1 | FPGA tiles used to implement MIPS CPU, RC pipeline, and peripherals                                        | 82  |

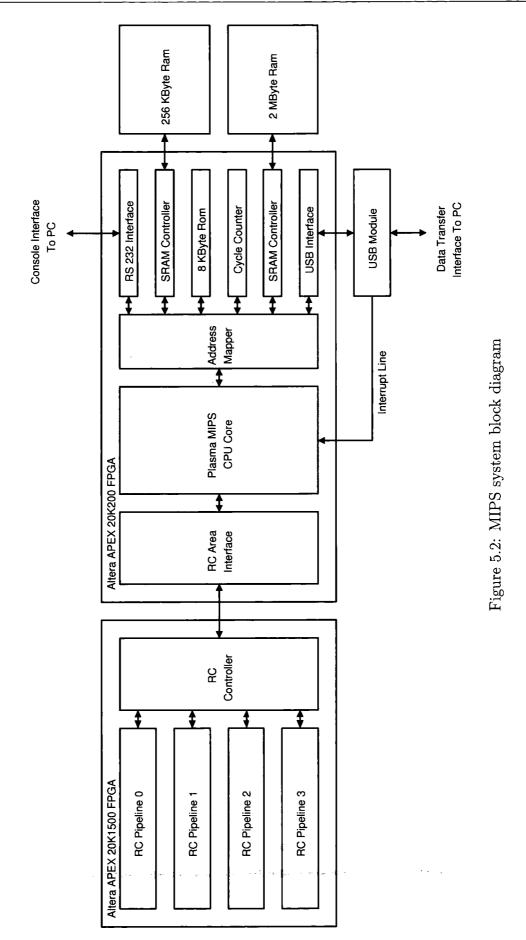

|   | 5.2 | MIPS system block diagram                                                                                  | 83  |

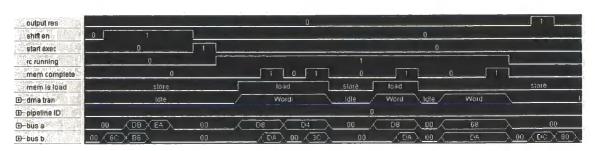

|   | 5.3 | Example logic analyzer trace showing RC pipeline execution $\ldots$ .                                      | 84  |

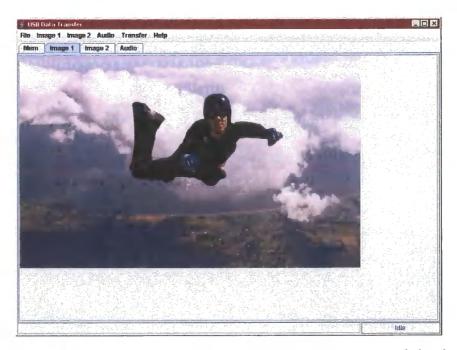

|   | 5.4 | USB data transfer application displaying the contents of the data                                          |     |

|   |     | buffer as an image                                                                                         | 87  |

|   | 5.5 | Logic analyzer trace showing RC pipeline execution of FFT algorithm                                        | 91  |

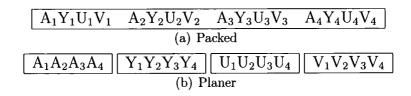

|   | 5.6 | Pixel graphics formats                                                                                     | 93  |

| , | 5.7 | Logic analyzer trace showing RC pipeline execution of half brightness                                      | ÷ . |

|   |     | algorithm                                                                                                  | 95  |

. . . . . . . .

| 5.8  | Logic analyzer trace showing RC pipeline execution of quick sort al-  |

|------|-----------------------------------------------------------------------|

|      | gorithm                                                               |

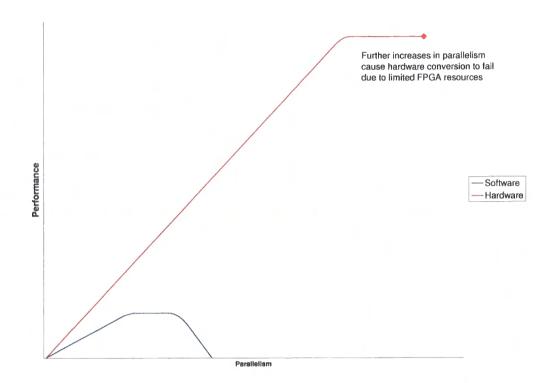

| 5.9  | Generalized effects of parallelism on performance (Software vs Hard-  |

|      | ware)                                                                 |

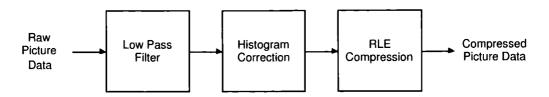

| 5.10 | Picture processing and compression                                    |

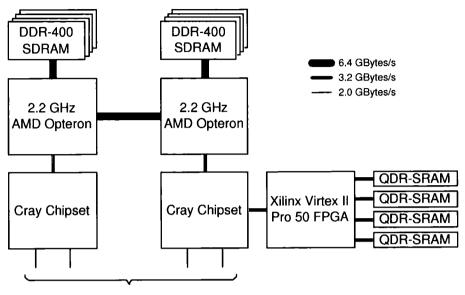

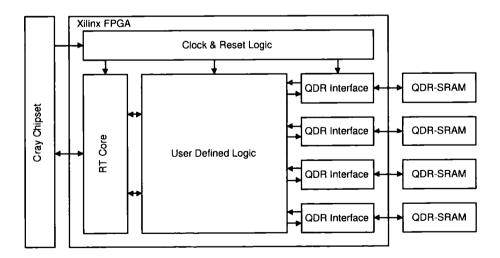

| 61   | Cray XD1 blade architecture                                           |

| 6.1  | Cray AD1 blade architecture                                           |

| 6.2  | Cray FPGA interface cores                                             |

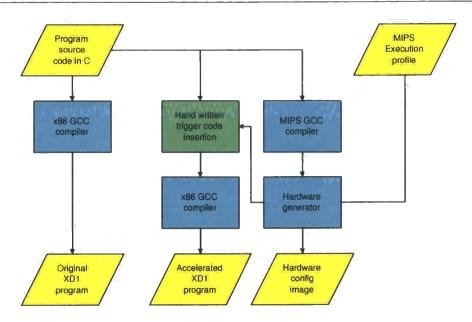

| 6.3  | Hardware conversion tool flow for Cray XD1                            |

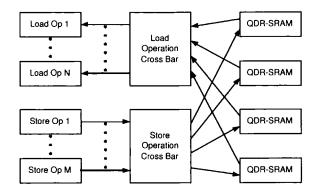

| 6.4  | Cross bar architecture for QDR memory interface                       |

| 6.5  | Operations on the hardware data flow pipeline for the low pass filter |

|      | algorithm                                                             |

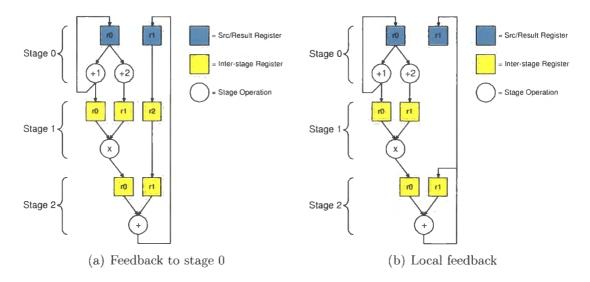

| 7.1  | Example data flow pipelines with and without the local feedback op-   |

|      | timization                                                            |

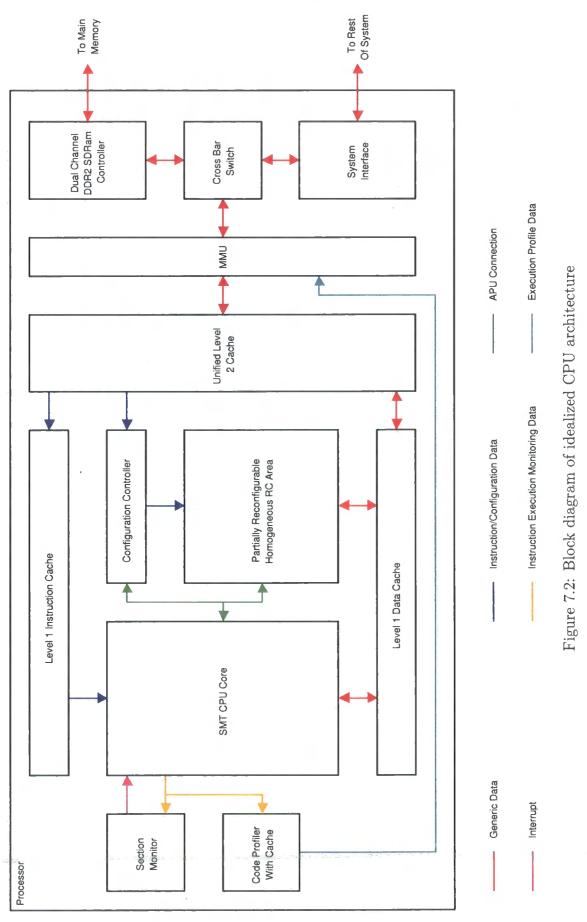

| 7.2  | Block diagram of idealized CPU architecture                           |

. ...

. . . . . .

-

# List of Tables

| 1.1 | Warp processing test platforms                                     |  |

|-----|--------------------------------------------------------------------|--|

| 3.1 | EPIC CPU specification                                             |  |

| 3.2 | Test algorithms and characteristics                                |  |

| 3.3 | Test cases implemented in FPGA hardware                            |  |

| 5.1 | MIPS platform summary                                              |  |

| 5.2 | Test algorithms used on MIPS test platform                         |  |

| 6.1 | Test algorithms used on the Cray XD1                               |  |

| 6.2 | Predicted performance improvement after resolving current Cray XD1 |  |

|     | limitations                                                        |  |

# List of Listings

| 3.1  | Sample code before instruction combination     | 42 |

|------|------------------------------------------------|----|

| 3.2  | Sample code after instruction combination code | 42 |

| 3.3  | Example code loop with dependency              | 48 |

| 3.4  | Example code loop without dependency           | 48 |

| 4.1  | If-else statement implemented with branches    | 65 |

| 4.2  | If-else statement implemented with MUXs        | 65 |

| 4.3  | Conditional store implemented with branching   | 66 |

| 4.4  | Conditional store implemented with guarding    | 66 |

| 4.5  | Hardware dependency present                    | 67 |

| 4.6  | Hardware dependency removed                    | 67 |

| 4.7  | Stacking ("push" first)                        | 68 |

| 4.8  | Stack operations removed ("push" first)        | 68 |

| 4.9  | Stacking ("pop" first)                         | 69 |

| 4.10 | Stack operations removed ("pop" first)         |    |

| 4.11 | Before instruction removal                   | 70 |

|------|----------------------------------------------|----|

| 4.12 | After instruction removal                    | 70 |

| 4.13 | Sequential value combination                 | 70 |

| 4.14 | Balanced value combination                   | 70 |

| 4.15 | Program before trigger instruction insertion | 77 |

| 4.16 | Program after trigger instruction insertion  | 77 |

| 5.1  | Example RC trigger instruction sequence      | 80 |

| 7.1  | Example code with multiple nested loops      | 26 |

# Glossary

| AIM            | Abstract Instruction Model                |

|----------------|-------------------------------------------|

| AMD            | Advanced Micro Devices                    |

| API            | Application Programming Interface         |

| ASIC           | Application Specific Integrated Circuit   |

| BSD            | Berkeley Software Distribution            |

| CISC           | Complex Instruction Set Computer          |

| CMS            | Code Morphing Software                    |

| CPU            | Central Processing Unit                   |

| DDR            | Double Data Rate                          |

| DMA            | Direct Memory Access                      |

| DSP            | Digital Signal Processing                 |

| EPIC           | Explicitly Parallel Instruction Computing |

| $\mathbf{FFT}$ | Fast Fourier Transform                    |

| FIFO           | First In First Out                        |

| FIR            | Finite Impulse Response                   |

| FPGA           | Field Programmable Gate Array             |

| GCC            | GNU Compiler Collection                   |

| GNU            | GNU's Not UNIX                            |

| GUI            | Graphical User Interface                  |

| HDL            | Hardware Description Language             |

| HPC            | High Performance Computing                |

. ...

| HSI  | Hardware Software Interface                    |

|------|------------------------------------------------|

| HW   | Hardware                                       |

| IEEE | Institute of Electrical & Electronic Engineers |

| ILP  | Instruction Level Parallelism                  |

| ΙΟ   | Input/Output                                   |

| IP   | Intellectual Property                          |

| ISA  | Instruction Set Architecture                   |

| JIT  | Just In Time                                   |

| JPEG | Joint Photographic Experts Group               |

| LFSR | Linear Feedback Shift Register                 |

| LOG  | Logarithm                                      |

| LPF  | Low Pass Filters                               |

| LRU  | Least Recently Used                            |

| LUT  | Look Up Table                                  |

| MAC  | Multiply and Accumulate                        |

| MMU  | Memory Management Unit                         |

| MMX  | Multi-Media Extensions                         |

| MPEG | Motion Pictures Experts Group                  |

| MUX  | Multiplexer                                    |

| NRE  | Non-Recurring Expenditure                      |

| OS   | Operating System                               |

| PAR  | Place And Route                                |

| PC   | Personal Computer                              |

| PCB  | Printed Circuit Board                          |

| PCI  | Peripheral Component Interconnect              |

| PNG  | Portable Network Graphics                      |

| PRBS | Pseudo Random Binary Sequence                  |

| QDR  | Quad Data Rate                                 |

| RAM   | Random Access Memory                                    |

|-------|---------------------------------------------------------|

| RLE   | Run Length Encoding                                     |

| ROM   | Read Only Memory                                        |

| RC    | Reconfigurable Computing                                |

| RGB   | Red Green and Blue                                      |

| RS232 | Serial Interface                                        |

| SAD   | Sum of Absolute Differences                             |

| SIMD  | Single Instruction Multiple Data                        |

| SMT   | Simultaneous Multi-Threading                            |

| SoC   | Systems On a Chip                                       |

| SDRAM | Synchronous Dynamic RAM                                 |

| SRAM  | Static RAM                                              |

| SW    | Software                                                |

| TSF   | Technology Scale Factor                                 |

| TV    | Television                                              |

| USB   | Universal Serial Bus                                    |

| WAV   | Waveform Audio                                          |

| VHDL  | VHSIC Hardware Description Language                     |

| VHSIC | Very High Speed Integrated Circuit                      |

| VLIW  | Very Long Instruction Word                              |

| VU    | Vertical Unit                                           |

| YUV   | Y = Luminance, $U =$ Normalised BY, $V =$ Normalised RY |

|       |                                                         |

## Chapter 1

# Introduction

## **1.1** Conventional Computing Architectures

Since the birth of the "Von Neumann architecture" [1] the performance of computers has continued to increase. In 1965 Gordon Moore made the observation [2] that the number of components on an integrated circuit doubles every 18 months, leading in turn to a doubling in processor performance over the same time period. Despite this dramatic and ongoing increase in computational speed, there are applications such as games, computational fluid dynamics and realtime multimedia applications that tax even the fastest modern computers. This problem has been addressed in the past by expanding the instruction set and also adding dedicated hardware.

## 1.1.1 Instruction Set Expansion

Although central processing unit (CPU) instruction sets allow the programmer to perform almost any task, it can require many 10's of instructions to perform some relatively simple tasks. If an operation frequently occurs it may, under certain cir-

### 1. Introduction

cumstances, be added into the instruction set to advantage. A good example of this is floating point maths. Many early instruction sets (e.g. x86, 68k, MIPS) didn't include this functionality, requiring it to be emulated using numerous integer operations. Floating point instructions were added when applications required the performance boost that they provided and when the available transistor count increased to the point where this became a practical solution.

Many modern CPU instruction sets have been extended to include single instruction multiple data (SIMD) instructions [3, 4]. This allows multiple arithmetic operations to be performed by a single instruction, by packing multiple values into a single register. An example of this would be a 32bit CPU that has a SIMD instruction that performs 4x8bit additions. This is implemented in hardware by disabling the carry propagation between the 8 bit groups which results in a significant performance improvement with very little additional hardware.

Although extending the instruction set can speedup a wide range of applications, the performance gain will always be limited by the instruction pipeline, register file and other fundamental components of the Von Neumann architecture.

## 1.1.2 Dedicated Hardware

As the execution units of a processor occupy only a small proportion of the total die area, CPUs are very inefficient in terms of both hardware utilization and power consumption. A popular way to address this and overcome the limitations of the Von Neumann architecture is to create dedicated hardware for specific tasks. As this solution doesn't require many of the hardware blocks found in a processor, (e.g. instruction fetch/decode, register files, etc) a larger proportion of the hardware is used to perform useful calculations.

A common example of this approach can be found in the current generation of

#### 1. Introduction

personal computers (PCs). Since the computational power required by modern 3D computer games is far greater than that available from even the fastest processors, dedicated hardware on the graphics card [5, 6] is used to render the 3D scenes. This releases the CPU to perform all the other tasks that are required in order to create the game environment. This "offloading" of computationally intensive tasks to hardware is even more frequently employed in embedded systems (e.g. set top boxes [7], mobile phones [8], etc) where CPU resources are often limited. Other common examples of hardware acceleration are cryptography, MPEG compression/decompression, and image improvement algorithms.

Using dedicated hardware is extremely powerful, however, it is only a practical solution where a task needs to be performed very frequently as such hardware is only capable of performing the specific task that it was designed to do. If that task doesn't need to be performed then the dedicated hardware will be idle. Rising mask costs and other non-recurring expenditures (NREs) are forcing manufacturers, especially in the embedded markets, to create devices for a much larger market segment. Consequently it is not always economically viable to design and implement hardware that is specific to only a small section of the market. A popular technique to reduce the amount of application specific hardware in these types of devices is to use one or more digital signal processing (DSP) cores [7, 8]. However there is a limit to how much processing power can be provided by this approach.

## 1.2 Reconfigurable Computing

By adding reconfigurable logic to a system it is possible to obtain a substantial performance improvement [9]. Although the performance achieved is very dependent on the application, speedups of 50 times or greater are not uncommon, whilst maintaining most of the flexibility associated with software [10, 11, 12, 13, 14].

In general algorithms with the characteristics listed below will benefit the most from the use of reconfigurable computing. Algorithms that possess all of these characteristics (e.g. encryption) achieve speed up factors of 1000 or more [15, 16].

- High levels of instruction level parallelism (ILP) The greater the amount of ILP the more data can be processed in parallel.

- Inherently parallel algorithms Some algorithms are inherently parallel in nature, as such different parts of the computation can be done in parallel (this parallelism is orthogonal to ILP). One example of this kind of parallelism is a simple brightness reduction algorithm, the calculation of the values of the pixels are independent from one another.

- **Simple operations** Some classes of operation (e.g. bitwise AND, OR, etc) require minimal hardware resources to implement. The lower the number of resource required my an algorithm, the more instances of that algorithm can be implemented in the reconfigurable hardware.

- Low memory bandwidth requirements Since the core algorithm will be instantiated many times in the FPGA, the total bandwidth required can become considerable. Since the amount of "off chip" bandwidth is restricted by physical factors (i.e. number of pins and maximum frequency) the amount of memory bandwidth available can severely limit the overall performance of a reconfigurable computing system.

## 1.2.1 Hardware Implementations

### **1.2.1.1** Direct Processor Integration

In some systems reconfigurable logic is an integral part of the processor [12, 13]. In these cases there are usually two communication channels. The first channel allows instructions to be issued to the reconfigurable computing (RC) area, enabling the software to control the execution and setup initial parameters. The second channel gives access to memory allowing the RC area to perform direct memory access (DMA) operations, independently of the rest of the CPU core. This approach has several advantages:-