### **Durham E-Theses**

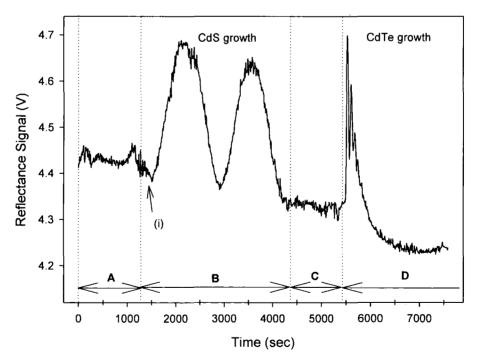

## Studies of CdTe Thin Films and Solar Cells Grown by MOCVD

Zoppi, Guillaume

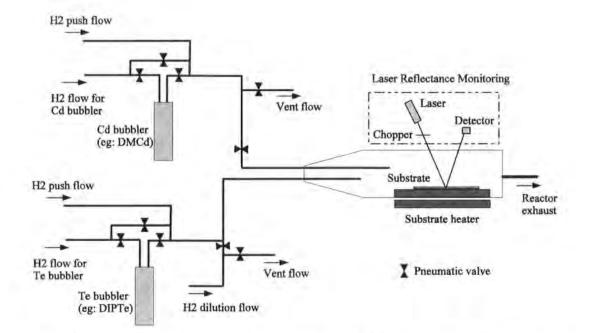

#### How to cite:

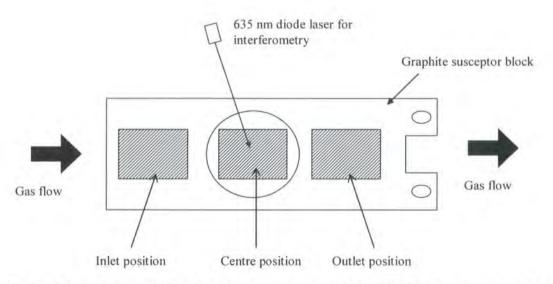

Zoppi, Guillaume (2005) Studies of CdTe Thin Films and Solar Cells Grown by MOCVD, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/2616/

#### Use policy

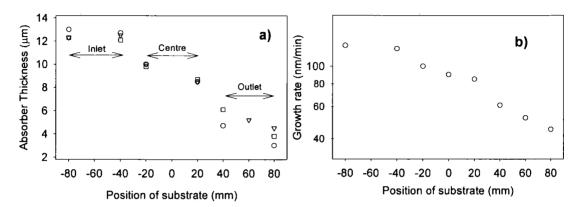

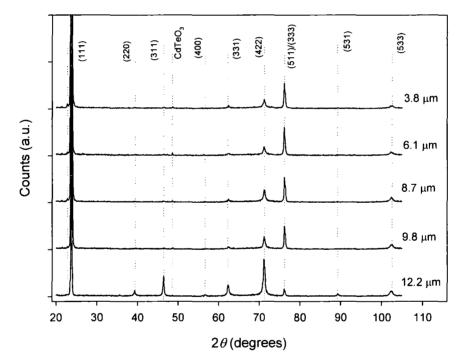

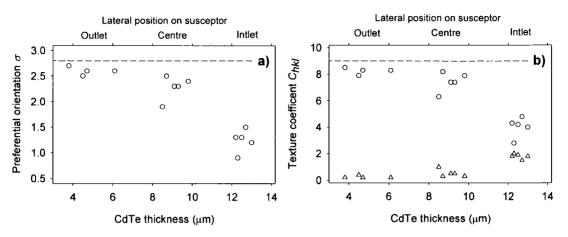

$The full-text\ may\ be\ used\ and/or\ reproduced,\ and\ given\ to\ third\ parties\ in\ any\ format\ or\ medium,\ without\ prior\ permission\ or\ charge,\ for\ personal\ research\ or\ study,\ educational,\ or\ not-for-profit\ purposes\ provided\ that:$

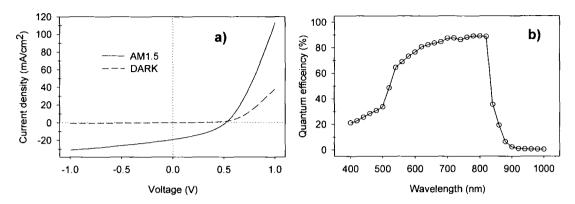

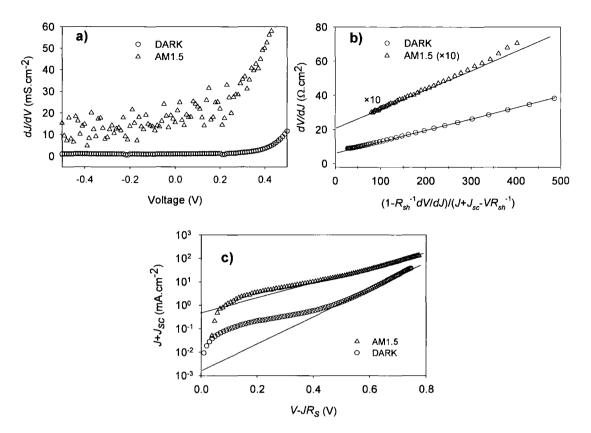

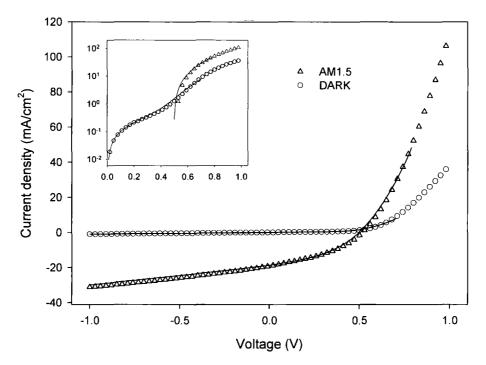

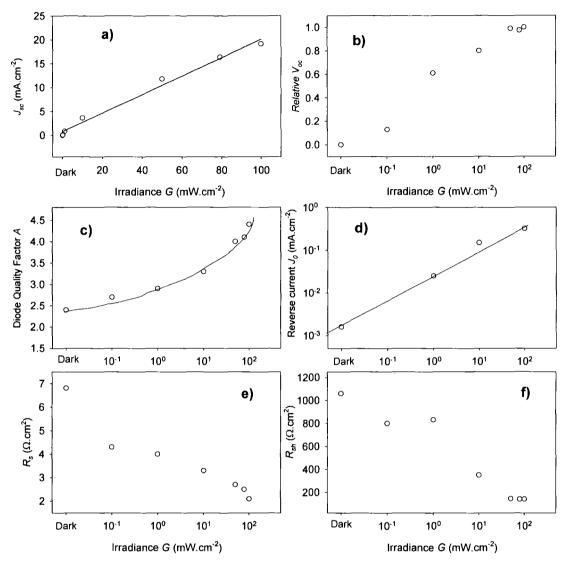

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders. Please consult the full Durham E-Theses policy for further details.

> Academic Support Office, The Palatine Centre, Durham University, Stockton Road, Durham, DH1 3LE e-mail: e-theses.admin@durham.ac.uk Tel: +44 0191 334 6107 http://etheses.dur.ac.uk

# Studies of CdTe Thin Films and Solar Cells Grown by MOCVD

A copyright of this thesis rests with the author. No quotation from it should be published without his prior written consent and information derived from it should be acknowledged.

By

Guillaume ZOPPI, BSc, MSc

A thesis presented in candidature for the degree of Doctor of Philosophy in the University of Durham

Department of Physics October 2005

0 7 DEC 2005

## ABSTRACT

This thesis presents the results of investigation of arsenic doped CdTe thin films and CdTe/CdS solar cells grown by MOCVD. Particular emphasis has been placed on the electrical and microstructural characterisation of layers and structures, and the effects of the post-deposition heat treatment of the materials and devices.

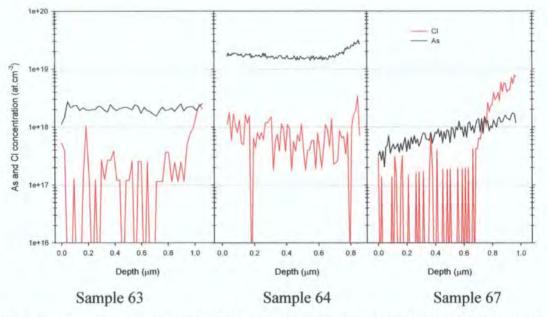

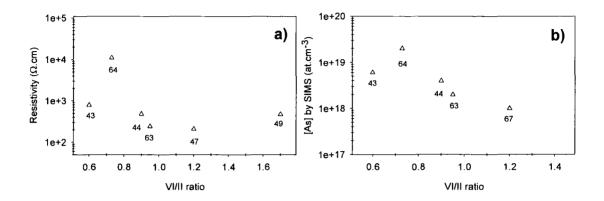

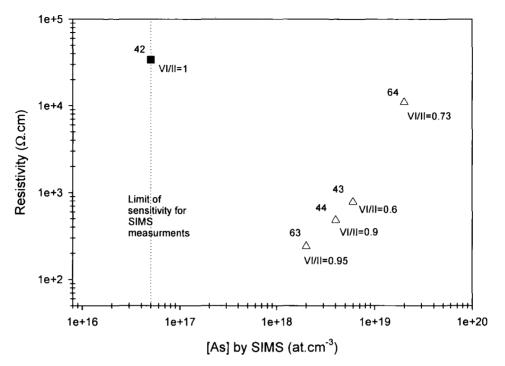

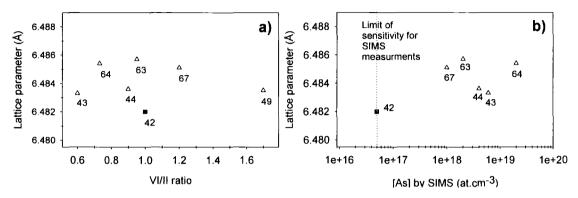

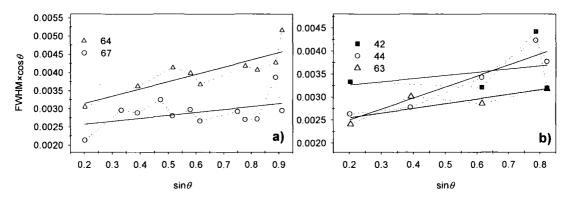

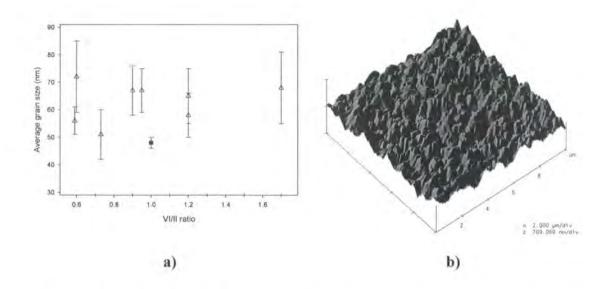

For a growth temperature of 400°C, using dimethylcadmium, diisopropyltelluride and dimethylamino arsine as precursors, the incorporation of arsenic in thin films of CdTe is dependent on the ratio of organometallics partial pressures in the growth ambient (VI/II ratio) with concentration of up to  $2 \times 10^{19}$ at.cm<sup>-3</sup> for a VI/II ratio of 0.73. The dependency of the lateral resistivity upon arsenic incorporation was investigated and found to increase for higher arsenic concentrations. The influence of the growth temperature and VI/II ratio on the texture and lattice parameter of the films is also examined.

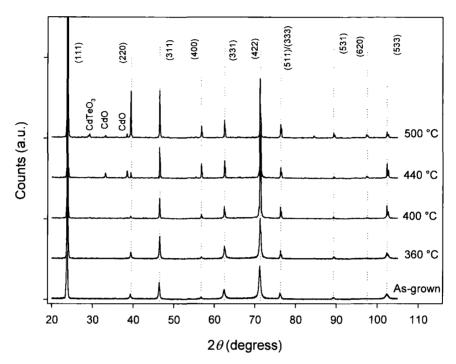

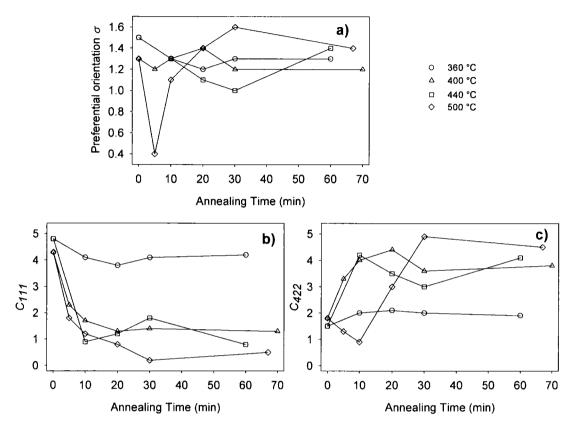

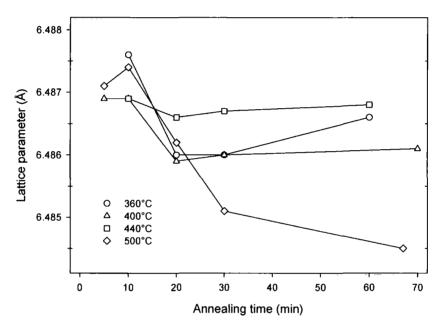

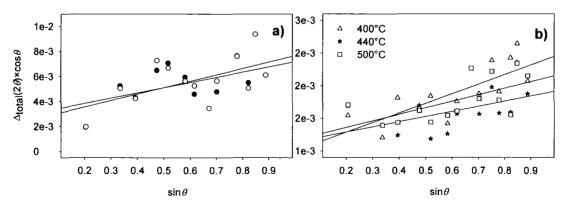

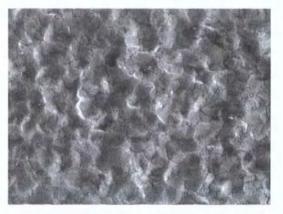

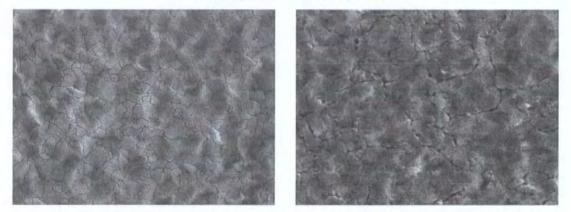

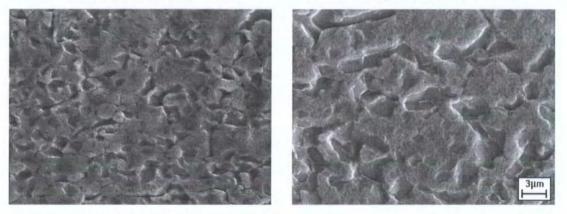

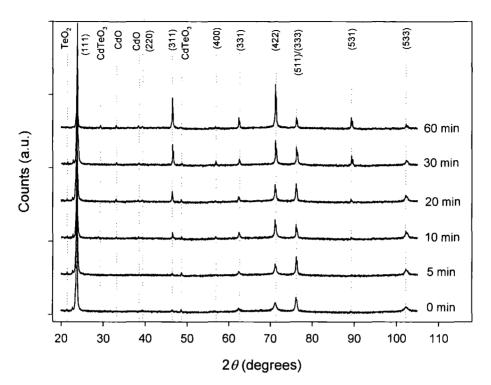

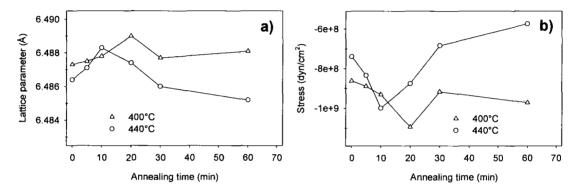

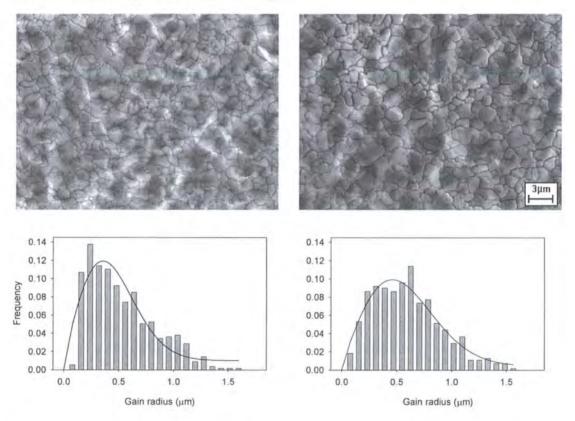

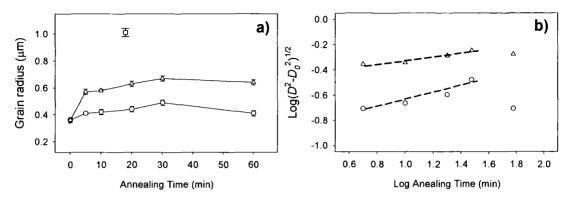

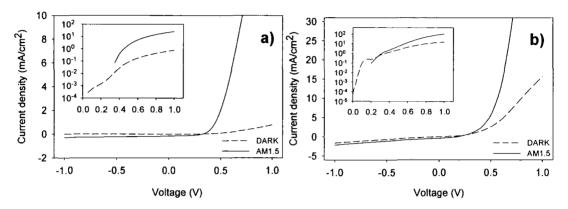

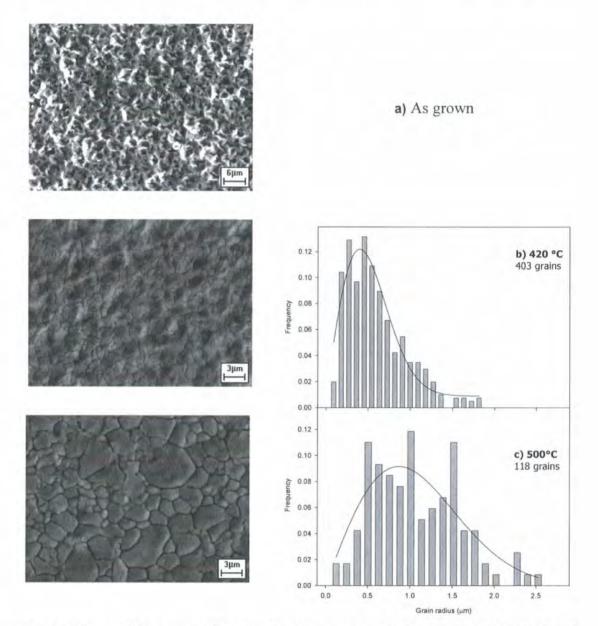

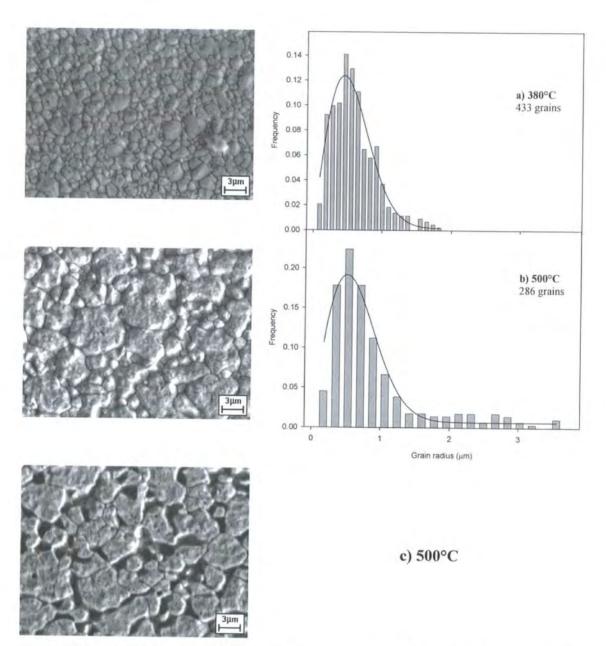

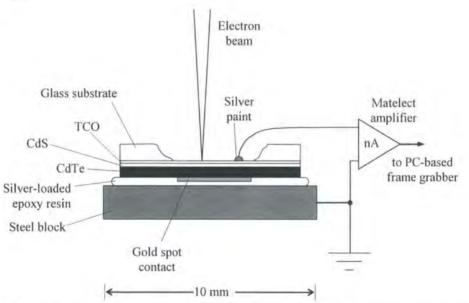

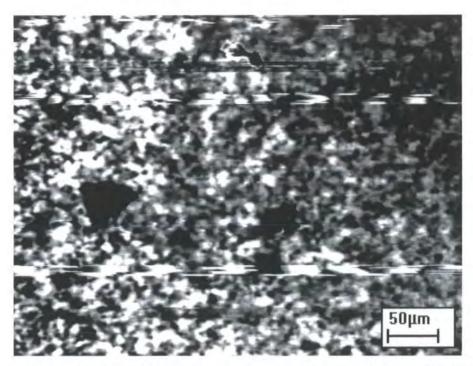

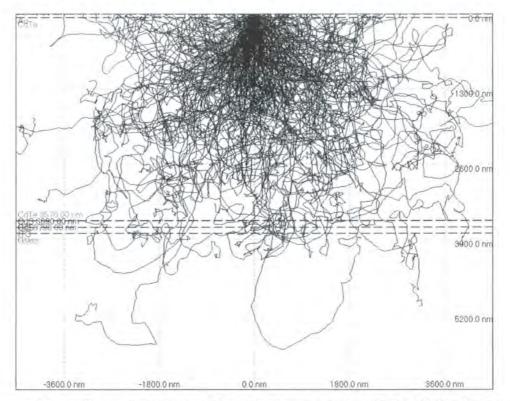

Investigations of the microstructure of absorber layers of CdTe/CdS bi-layers revealed that grain size and preferred orientation are dependent on the thickness of the films which is itself a function of the substrate position on the susceptor block. The influence of the post-deposition heat treatment with and without CdCl<sub>2</sub> was investigated by means of XRD and SEM. In both cases annealing causes a recrystallisation from the [111] into the [422] direction and a reduction in the inplane lattice stress of the CdTe layers. The grain size increases from 0.7 to 1.3  $\mu$ m only in the presence of CdCl<sub>2</sub> and Burke and Turnbull's grain growth exponents of 7 and ~4 are derived for ~8  $\mu$ m thick films treated at 440°C and 400°C.

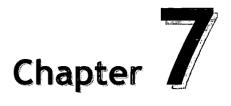

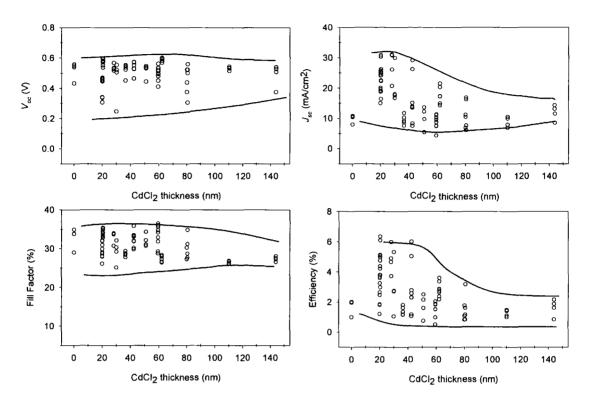

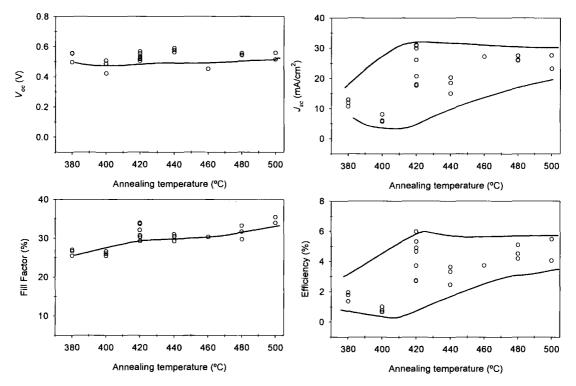

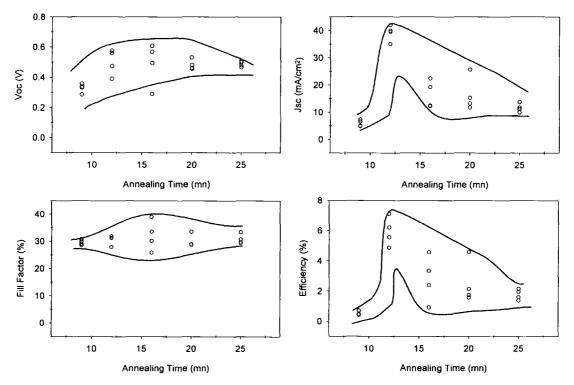

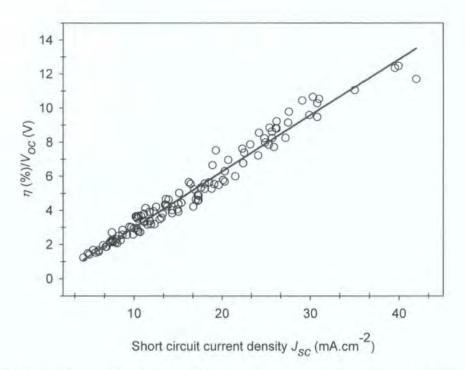

The activation of CdTe/CdS bi-layers using the CdCl<sub>2</sub> heat treatment shows that only devices with ~4  $\mu$ m CdTe can be made into efficient solar cells. Thinner and thicker structures produce cells exhibiting no photoresponse due to the lack of sustainability of the thin layers during treatment and the particularly low conductivity of the thicker layers. Optimisation of the CdCl<sub>2</sub> treatment indicates that best devices are produced following an 18 min annealing at 420°C for structures coated with a 30 nm layer of CdCl<sub>2</sub>. The cells are limited by a poor fill factor arising from low shunt and high series resistances indicated by a high reverse saturation current and diode quality factor.

## DECLARATION

I declare that with the exception of those procedures listed below all the work presented in this thesis was carried out by the candidate. I also declare that none of this work has previously been submitted for any degree and that it is not being submitted for any other degree.

Samples were provided by Dr A. Stafford and Dr V. Barrioz, Department of Chemistry, University of Wales, Bangor.

SIMS measurements included in Chapter 5 were performed by MATS-UK.

K Durose.

Dr K. Durose Supervisor

G. Zoppi Candidate

The copyright of this thesis rests with the author. No quotation from it should be published without their prior written consent and information derived from it should be acknowledged.

## ACKNOWLEDGMENTS

I would like to express my gratitude to the following people who have helped me during the course of my PhD. Thanks are due in particular to Dr Ken Durose for his patience and encouraging supervision of the project.

I would also like to acknowledge Prof Stuart Irvine, Dr Anne Stafford and Dr Vincent Barrioz at the University of Wales for providing the layers and solar cell structures used for this work, but also for the many discussions and advice given.

I wish to extend my gratitude to the technical staff of the physics department, especially Norman Thompson and David Pattinson for their expertise and friendly technical support. I also acknowledge Dr Tom Hase from this department and Dr John Evans from the department of chemistry for allowing me to carry out the XRD work.

I also thank all the past and present members of the research group, Martin Archbold, Arnab Basu, Nick Boyall, Ben Cantwell, Mahieddine Emziane, Tom Hindmarch, Chris Hodgson, Jon Major, Keriya Mam, Yuri Proskuryakov, and Andrew Yates for discussions, help and for providing a good atmosphere in the labs.

Finally, I would like to thank my family and Joanna for their love and support.

This work was funded by the Engineering and Physical Sciences Research Council.

## CONTENTS

.

| ACKNO  | ACT<br>RATION<br>WLEDGMENTS<br>F SYMBOLS           | ii<br>iii<br>iv<br>x |

|--------|----------------------------------------------------|----------------------|

| 1 Intr | oduction                                           | 1                    |

| 1.1 Re | ferences for Chapter 1                             | 5                    |

| 2 Fun  | damentals of Solar Cell Devices                    | 6                    |

| 2.1 In | troduction                                         | 6                    |

| 2.1.1  | Historical Development                             | 6                    |

| 2.1.2  | The Photovoltaic Effect                            | 7                    |

| 2.2 So | lar Cell Configurations                            | 8                    |

| 2.2.1  | Schottky Junction                                  | 8                    |

| 2.2.2  | Homojunction                                       | 9                    |

| 2.2.3  | Heterojunction                                     | 10                   |

| 2.3 Di | ode Physics and Cell Parameters                    | 12                   |

| 2.3.1  | The Diode Equation                                 | 12                   |

| 2.3.2  | Current-Voltage Characteristic and Cell Parameters | 14                   |

| 2.3.3  | Efficiency Limits and Losses                       | 17                   |

| 2.3.3  | .1 Short Circuit Current                           | 18                   |

| 2.3.3  | .2 Open Circuit Voltage                            | 19                   |

|        | .3 Fill Factor                                     | 19                   |

| •      | pes of Solar Cells                                 | 20                   |

| 2.4.1  | Single Crystal and Polycrystalline Silicon         | 20                   |

| 2.4.2  | Group III-V Technologies                           | 21                   |

| 2.4.2  | .1 Gallium Arsenide                                | 21                   |

|          | Indium Phosphide                      | 22 |

|----------|---------------------------------------|----|

| 2.4.3    | Thin Film Solar Cell                  | 22 |

| 2.4.3.1  | Hydrogenated Amorphous Silicon a-Si:H | 22 |

| 2.4.3.2  | Copper Indium Diselenide (CuInSe2)    | 23 |

| 2.4.3.3  | Cadmium Telluride (CdTe)              | 24 |

| 2.5 Refe | erences for Chapter 2                 | 25 |

| 3 T                    | hin Film CdTe/CdS Solar Cells        | 29 |

|------------------------|--------------------------------------|----|

| 3.1                    | Introduction                         | 29 |

| 3.2                    | Solar Cell Structure                 | 30 |

| 3.2.                   | 1 The substrate                      | 31 |

| 3.2.                   | 2 The Front Contact                  | 31 |

| 3.2.                   | 3 The CdS Window Layer               | 32 |

| 3.2.                   | 4 The CdTe Absorber Layer            | 32 |

| 3.2.5 The Back Contact |                                      | 33 |

| 3.3                    | Material Deposition Techniques       | 35 |

| 3.3.                   | 1 Chemical Vapour Deposition         | 35 |

| 3.3.                   | 2 Other Deposition Techniques        | 39 |

| 3.4                    | Post-Deposition Treatment            | 42 |

| 3.5                    | Typical Device Characteristics       | 45 |

| 3.6                    | Defects and Doping in CdTe Materials | 47 |

| 3.7                    | Concluding Remarks                   | 50 |

| 3.8                    | References for Chapter 3             | 52 |

| 4 S  | ample Preparation and Characterisation Techniques | 60 |

|------|---------------------------------------------------|----|

| 4.1  | Introduction                                      | 60 |

| 4.2  | MOCVD Growth of CdS, CdTe and CdTe:As             |    |

| 4.3  | 3 Post-Deposition Treatment                       |    |

| 4.4  | Solar Cell Characterisation                       | 66 |

| 4.4. | 1 Solar Radiation and Solar Simulator             | 66 |

| 4.4. | 2 Current-Voltage Measurements                    | 69 |

| 4.4. | 3    | Spectral Response Measurements            | 70 |

|------|------|-------------------------------------------|----|

| 4.5  | Elec | trical Measurements for Individual Layers | 71 |

| 4.5. | 1    | Carrier Type Determination                | 71 |

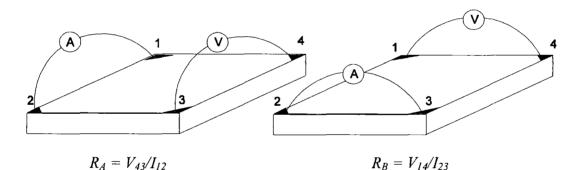

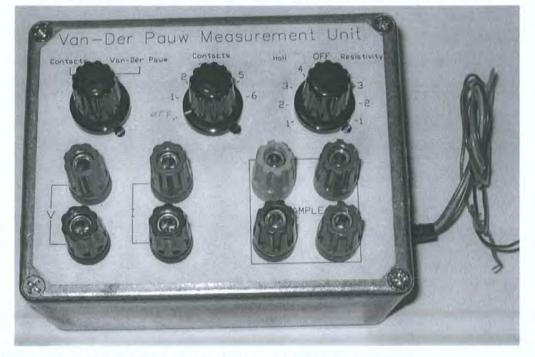

| 4.5. | 2    | Resistivity and Sheet Resistance          | 73 |

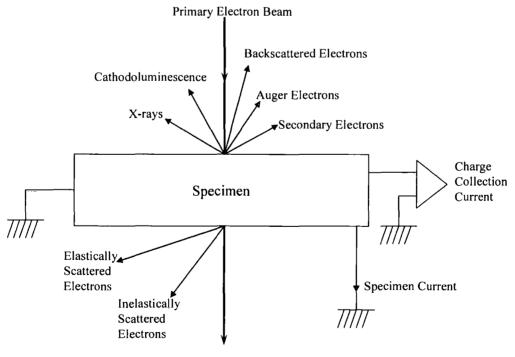

| 4.6  | Scar | nning Electron Microscopy                 | 75 |

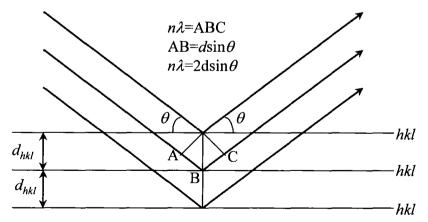

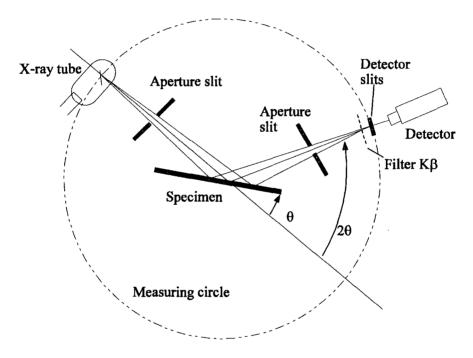

| 4.7  | X-Ra | ay Diffraction                            | 77 |

| 4.7. | 1    | Determination of the Lattice Parameter    | 79 |

| 4.7. | 2    | Grain Size and Deformation Strain         | 79 |

| 4.7. | 3    | Crystallographic Orientation              | 80 |

| 4.8  | Thic | kness Measurements                        | 81 |

| 4.9  | Seco | ondary Ion Mass Spectroscopy              | 81 |

| 4.10 | Refe | erences for Chapter 4                     | 83 |

| 5   | Doping Studies of CdTe:As on Sapphire Substrate                     | es 85 |  |

|-----|---------------------------------------------------------------------|-------|--|

| 5.1 | Introduction                                                        | 85    |  |

| 5.2 | Description of the Samples Used in this Study                       | 86    |  |

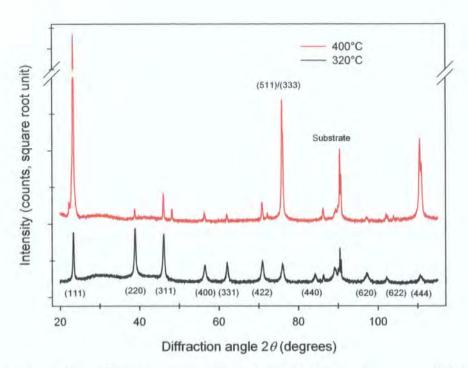

| 5.3 | General Effects of Growth Temperature                               | 89    |  |

| 5.  | 3.1 On Electrical Properties                                        | 89    |  |

| 5.  | 3.2 On Crystal Structure                                            | 90    |  |

| 5.4 | Effect of VI/II Ratio and Dopant Incorporation on the Properties of |       |  |

|     | Layers Grown at 400°C                                               | 91    |  |

| 5.5 | Structural Analysis                                                 | 96    |  |

| 5.6 | Discussion                                                          | 99    |  |

| 5.7 | Conclusion                                                          | 102   |  |

| 5.8 | References for Chapter 5                                            | 104   |  |

| 6 Influence of the Post-Growth Treatment on the Abso |                                               | Absorber |

|------------------------------------------------------|-----------------------------------------------|----------|

|                                                      | Layer Microstructure                          | 107      |

| 6.1                                                  | Introduction                                  | 107      |

| 6.2                                                  | Description of the Samples Used in this Study | 108      |

| 6.3                                              | Results for As-Grown Material   |                      |

|--------------------------------------------------|---------------------------------|----------------------|

| 6.4 Heat Treated Samples (No CdCl <sub>2</sub> ) |                                 | l <sub>2</sub> ) 114 |

| 6.5                                              | 119                             |                      |

| 6.5                                              | 5.1 Effect on Crystal Structure | 119                  |

| 6.5                                              | 5.2 Effect on Crystallite Size  | 123                  |

| 6.6                                              | Discussion                      | 125                  |

| 6.7                                              | Conclusion                      | 129                  |

| 6.8                                              | References for Chapter 6        | 131                  |

| 7   | Chara   | acterisation of CdCl <sub>2</sub> -Treated Solar Cell Devices | 134 |

|-----|---------|---------------------------------------------------------------|-----|

| 7.1 | Intr    | oduction                                                      | 134 |

| 7.2 | Des     | cription of the Samples Used in this Study                    | 135 |

| 7.  | 2.1     | The Samples                                                   | 135 |

| 7.  | 2.2     | Post-Growth Treatment and Parameters                          | 137 |

| 7.3 | Per     | formance of Cells with ~2 and ~8 $\mu m$ Thick CdTe Absorber  | 137 |

| 7.4 | Res     | ults for Cells with ~4 $\mu$ m Thick CdTe Absorber            | 142 |

| 7.  | 4.1     | Influence of CdCl <sub>2</sub> Thickness                      | 142 |

| 7.  | 4.2     | Influence of Annealing Temperature                            | 143 |

| 7.  | 4.3     | Influence of Annealing Time                                   | 145 |

| 7.  | 4.4     | Limiting Factors for Higher Efficiencies                      | 146 |

| 7.5 | EBI     | C Measurements (Cells with ~4 $\mu m$ CdTe)                   | 156 |

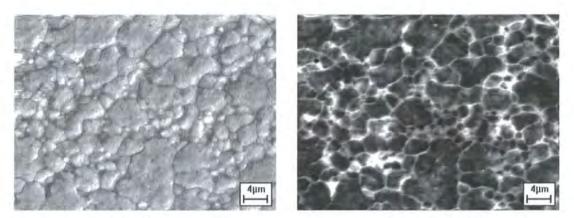

| 7.  | 5.1     | Front-Wall EBIC                                               | 156 |

| 7.  | 5.2     | Variation of Back-Wall EBIC Signal with Beam Voltage          | 157 |

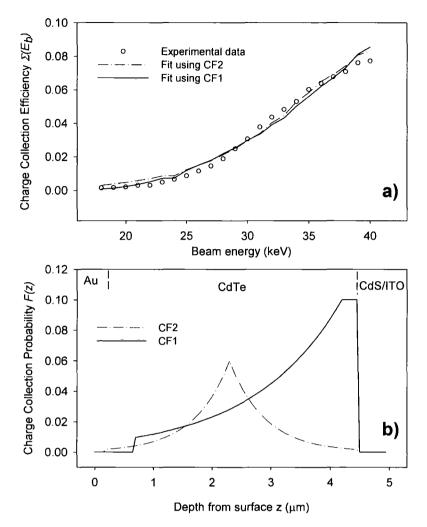

|     | 7.5.2.1 | Theory and Experimental Procedure                             | 158 |

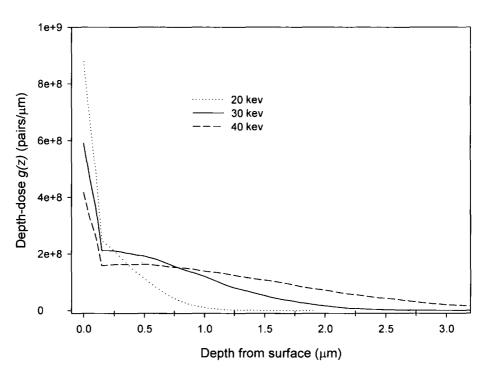

|     | 7.5.2.2 | Monte Carlo Simulation of Carrier Generation                  | 158 |

|     | 7.5.2.3 | Experimental Results                                          | 160 |

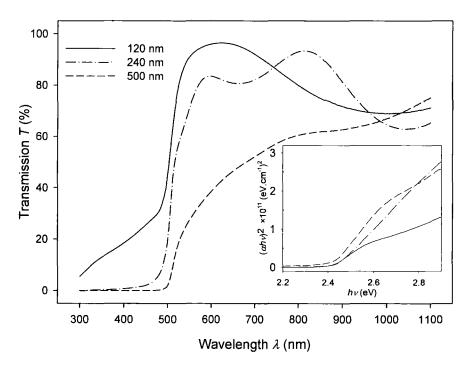

| 7.6 | Infl    | uence of CdS Thickness and the ITO Substrate Type             | 164 |

| 7.7 | Disc    | cussion                                                       | 166 |

| 7.8 | Con     | clusion                                                       | 169 |

| 7.9 | Ref     | erences for Chapter 7                                         | 171 |

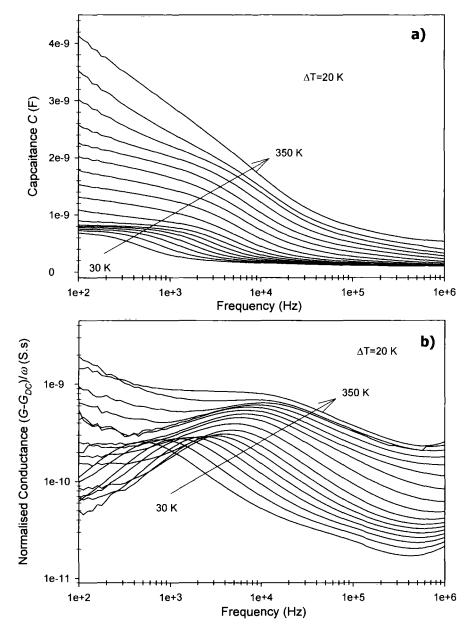

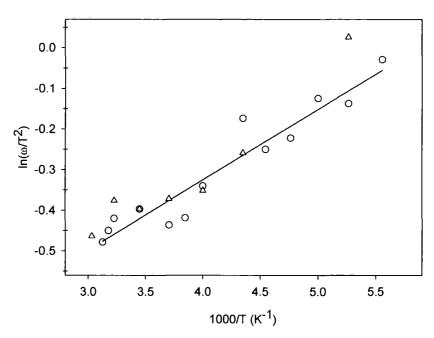

| AC Impedance Measurements  | 174                                                                                                      |

|----------------------------|----------------------------------------------------------------------------------------------------------|

| Introduction               | 174                                                                                                      |

| Theoretical Approach       | 175                                                                                                      |

| Experimental Details       | 178                                                                                                      |

| Thermal Admittance Results | 179                                                                                                      |

| Conclusion                 | 185                                                                                                      |

| References for Chapter 8   | 186                                                                                                      |

|                            | Introduction<br>Theoretical Approach<br>Experimental Details<br>Thermal Admittance Results<br>Conclusion |

| 9   | Conclusions                 | 188 |

|-----|-----------------------------|-----|

| 9.1 | Summary of Conclusions      | 188 |

| 9.2 | Suggestions for Future Work | 192 |

## LIST OF SYMBOLS

| а                | Lattice parameter                        | Å                               |

|------------------|------------------------------------------|---------------------------------|

| A                | Diode quality factor                     | -                               |

| α                | Absorption coefficient                   | cm <sup>-1</sup>                |

| С                | Capacitance                              | F                               |

| $C_{hkl}$        | Texture coefficient                      | -                               |

| d <sub>hkl</sub> | Interatomic distance                     | Å                               |

| d                | Thickness                                | m                               |

| $E_b$            | Electron beam energy                     | keV                             |

| $E_C$            | Energy of bottom of conduction band      | eV                              |

| $E_F$            | Fermi level energy                       | eV                              |

| $E_g$            | Energy bandgap                           | eV                              |

| $E_i$            | Ionisation energy                        | eV                              |

| $E_t$            | Defect characteristic energy             | eV                              |

| $E_V$            | Energy of top of valence band            | eV                              |

| $D_n, D_p$       | Electron and hole diffusion coefficients | $\mathrm{cm}^2.\mathrm{s}^{-1}$ |

| F(z)             | Collection probability                   | -                               |

| FF               | Fill Factor                              | %                               |

| G                | Conductance                              | S                               |

| $g(E_b,z)$       | Generation function for minority carrier | m <sup>-1</sup>                 |

| h                | Planck's constant                        | J.s                             |

| h, k, l          | Miller's indices                         | -                               |

| $I_c$            | Electron beam current                    | А                               |

| J                | Current density                          | mA.cm <sup>-2</sup>             |

| $J_0$            | Saturation current density               | mA.cm <sup>-2</sup>             |

| $J_L$            | Light generated current density          | mA.cm <sup>-2</sup>             |

| $J_{mp}$         | Maximum power current density            | mA.cm <sup>-2</sup>             |

| $J_{sc}$         | Short circuit current density            | mA.cm <sup>-2</sup>             |

| k                | Boltzmann's constant                     | J.K <sup>-1</sup>               |

|                  |                                          |                                 |

| $L_n, L_p$         | Electron and hole diffusion lengths     | cm                   |

|--------------------|-----------------------------------------|----------------------|

| n                  | Refractive index                        | -                    |

| n                  | Number of reflection                    | -                    |

| n                  | Grain growth exponent                   | -                    |

| n, p               | Electron and hole densities             | cm <sup>-3</sup>     |

| $n_p, p_n$         | Minority carrier densities              | cm <sup>-3</sup>     |

| $n_{p_0}, p_{n_0}$ | Equilibrium carrier densities           | cm <sup>-3</sup>     |

| $N_V$              | Valence band density of states          | cm <sup>-3</sup>     |

| $N_t$              | Defect density of states                | cm <sup>-3</sup>     |

| P <sub>in</sub>    | Incident illumination intensity         | W.m <sup>-2</sup>    |

| q                  | Electronic charge                       | С                    |

| r                  | Grain radius                            | μm                   |

| $R_A, R_B$         | Van der Pauw characteristic resistances | Ω                    |

| $R_s$              | Series resistance                       | $\Omega.cm^{-2}$     |

| $R_s$              | Sheet resistance                        | Ω.□                  |

| R <sub>sh</sub>    | Shunt resistance                        | $\Omega.cm^{-2}$     |

| $S_{xy}$           | Component of compliance                 | dyn.cm <sup>-2</sup> |

| t                  | Time                                    | S                    |

| Т                  | Temperature                             | Κ                    |

| V                  | Voltage                                 | V                    |

| $V_{oc}$           | Open circuit voltage                    | V                    |

| V <sub>bi</sub>    | Built-in voltage                        | V                    |

| $V_{mp}$           | Maximum power voltage                   | V                    |

| Ζ                  | Depth                                   | μm                   |

| x <sub>d</sub>     | Depletion width                         | cm                   |

| $eta_p$            | Hole capture coefficient                | $cm^3.s^{-1}$        |

| ε                  | Strain                                  | -                    |

| η                  | Efficiency                              | %                    |

| λ                  | Wavelength                              | nm                   |

| $\mu_n, \mu_p$     | Electron and hole motilities            | $cm^2.V^{-1}.s^{-1}$ |

| ν                  | Frequency                               | Hz                   |

|                    |                                         |                      |

| ρ                 | Resistivity                           | $\Omega.cm$          |

|-------------------|---------------------------------------|----------------------|

| $\sigma$          | Degree of preferred orientation       | -                    |

| $\sigma_i$        | Conductivity                          | S.cm <sup>-1</sup>   |

| $\sigma_{p}$      | Hole capture cross section            | cm <sup>2</sup>      |

| $\sigma_{s}$      | In-plane stress                       | dyn.cm <sup>-2</sup> |

| $\mathcal{U}_{0}$ | Attempt-to-escape frequency           | s <sup>-1</sup>      |

| Uth               | Thermal velocity                      | cm.s <sup>-1</sup>   |

| ω                 | Angular frequency                     | s <sup>-1</sup>      |

| $\omega_t$        | Defect characteristic frequency       | s <sup>-1</sup>      |

| $\Sigma(E_b)$     | Charge collection efficiency          | -                    |

| $\phi_B$          | Barrier height                        | eV                   |

| $\phi_m, \phi_s$  | Work function of metal, semiconductor | eV                   |

| Xs                | Electron affinity                     | eV                   |

# Chapter

# Introduction

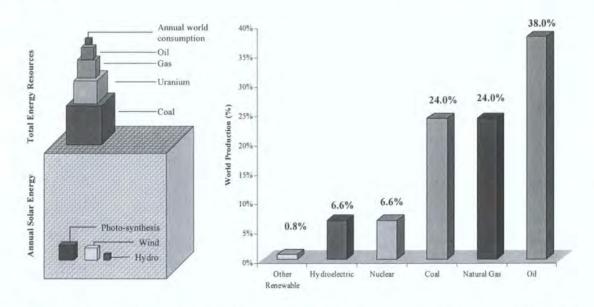

Global energy consumption has increased at a rate of around 2% each year, doubling, on average, every 30 to 40 years [1]. Today world energy consumption is highly dependent on fossil fuel-based sources, i.e. oil, natural gas and coal, these sources accounting for over 80% of the global market [2]. The remainder is provided predominantly from nuclear resources but also from renewable energy, such as hydro-power (Figure 1-1). However, this ever-growing global demand for energy cannot be sustained indefinitely as primary resources are rapidly running out. Projections based on known reserves and predicted consumption extrapolations have been made regarding the different time scales over which, through depletion, each fuel source will become increasingly scarce and therefore their expense will increase considerably. It is estimated that coal production can continue for the next 200 years while resources of natural gas and oil will extinguish in 40 and 60 years, respectively [3].

The environmental impact of the burning of fossil fuels for energy production is also of high considerations and concerns. Green house gases and ozone depleting gases are among the product of such combustion. Long term effects of this include smog build up in urban areas, acid rain deforestation and global climate changes. The latter being considered as a high priority matter for many governmental institutions. Regarding nuclear power, safety, disposal, storage, material handling and reactor

decommissioning are some of the questions that make the future of nuclear energy uncertain.

Figure 1-1 Order of magnitude of primary energy resources (left) [3] and world production of primary energy (right) [2].

Since the 1970's a diverse range of technologies have emerged as potential alternatives for renewable energies from natural resources. These include wind, geothermal, tidal wave, hydroelectric and biomass, solar thermal and solar photovoltaic energies. As seen in Figure 1-1, the sun is responsible for most of the earth's exploitable energy, producing the exploitable resources of wind, wave, photosynthesis and hydroelectric power. It is also solar radiation in its immediate form that can be exploited through solar thermal heating and photovoltaic conversion. The latter is the subject of this work.

Photovoltaic (PV) conversion is the direct conversion of the solar energy into electrical power, providing a promising renewable, almost unlimited, affordable and environmentally friendly energy source as well as being economically viable. Among the different photovoltaic materials available, the cadmium telluride – cadmium sulphide solar cell has attracted considerable attention. The use of cadmium telluride (CdTe) as a light absorbing material in solar cells is attractive, because it possesses a nearly optimal bandgap of 1.5 eV for conversion efficiency [4]. The direct band gap of this semiconductor allows considerable light absorption for film thicknesses of

only 2  $\mu$ m, resulting in low material usage. Moreover, CdTe is a robust material open to a wide variety of deposition techniques.

One of these techniques is metal-organic chemical vapour deposition (MOCVD) and has been used throughout the course of this work to produce the different layers and structures studied. MOCVD is a well established technique for producing optoelectronic devices based on III-V materials [5]. The use of MOCVD for solar cell applications has mainly been limited to the development of GaAs-based devices for space applications. In the case of II-VI materials such as CdTe and CdS, progress on controlling point defects, doping and alloy composition have been slower compared to III-V technology. At a research level, MOCVD is utilised for the growth of CdTe/CdS solar cells in an attempt to improve the quality of the CdTe layer compared to other deposition techniques and hence improving the collecting power of the film. Although the growth conditions can be optimised to produced *p*-type CdTe films with micron sized grains [6], the resulting polycrystalline films are, however, often too resistive for photovoltaic applications arising from the high density of grain boundaries.

The opportunities offered by the MOCVD technique for reproducible high efficiency photovoltaic devices are (i) control in the growth of the CdTe/CdS structures, (ii) doping consistently in all areas of the device and (iii) annealing in a controlled atmosphere during and after growth cycles. Improvement in heterojunction and metal-semiconductor junction formation, maximisation of grain size and controlled passivation of grain boundary provide the major challenges for MOCVD if it is to become a reliable and cost-effective technique for the production of thin film solar cells.

Initially this thesis discusses the principles and fundamentals of solar cell devices and also the diverse structures and materials used (Chapter 2). Following this, Chapter 3 will focus on the CdTe/CdS polycrystalline thin film solar cell by reviewing the technologies and properties of the materials and also the effects of processing. Then the range of experimental techniques used through the course of this work is described in details in Chapter 4. The experimental results are then described and analysed in the following chapters:

3

- In Chapter 5, the structural and electrical properties of arsenic doped thin film CdTe are investigated in order to assess the influence of the dopant incorporation.

- (ii) In Chapter 6, the microstructure of the absorber layer of CdTe/CdS bi-layers is studied with regards to the post-deposition treatment of the structures.

- (iii) The processing and characterisation of solar cell structures are then detailed in Chapter 7 by means of current-voltage characteristics and microscopy techniques.

- (iv) Finally, the junction properties of two devices with thin and thick CdTe are analysed by means of impedance spectroscopy in order to assess the particular differences between the two junctions (Chapter 8).

#### 1.1 References for Chapter 1

- International Institute for Applied Systems Analysis, Environmentally Compatible Energy Strategies (1998) http://www.iiasa.ac.at/Admin/OSR/RP95/ECS.html

- 2. M. Combarnous and A. Prieur, Les consommations d'énergie dans le monde : une méthode robuste de prévision de leur évolution à moyen terme ; premières conséquences - World energy consumption: a robust method for the prevision of their medium term evolution; first consequences, Comptes Rendus Geosciences 335 (2003) 943-950

- 3. World Energy Council, Survey of Energy Resources (2004) http://www.worldenergy.org/wec-geis/

- 4. J. J. Loferski, Theoretical considerations governing the choice of the optimum semiconductor for photovoltaic solar energy conversion, Journal of Applied Physics 27 (1956) 777-784

- 5. R. L. Moon, *MOVPE: is there any other technology for optoelectronics?*, Journal of Crystal Growth **170** (1997) 1-10

- T. L. Chu, S. S. Chu, C. Ferekides, J. Britt, and C. Q. Wu, *Cadmium telluride films by metalorganic chemical vapor deposition*, Journal of Applied Physics 69 (1991) 7651-7655

# Fundamentals of Solar Cell Devices

#### 2.1 Introduction

Solar cells are semiconductor devices that convert sunlight directly into electrical energy using the photovoltaic process. Not only is the efficiency of the cell important, but also its ability to perform well over a long period of time under real atmospheric conditions. This chapter presents a review of the features of solar cells, their band structures, their working parameters and the main materials.

#### 2.1.1 Historical Development

Solar cells depend upon the photovoltaic effect for their operation. Becquerel, who observed a light-dependent voltage between electrodes immersed in an electrolyte, reported this effect initially in 1839 [1]. It was also observed in an all-solid-state system in 1876 for the case of selenium [2]. This was followed by the development of photocells based on both this material and cuprous oxide. Although a silicon cell was reported in 1941, it was not until 1954 [3] that the forerunner of present silicon cells was announced. This device represented a major development because it was the first photovoltaic structure that converted light to electricity with reasonable efficiency. These cells found application as power sources in spacecrafts

as early as 1958. By the early 1960's, the design of cells for space use had stabilized and over the next decade this was their major application.

The early 1970's saw an innovative period in silicon cell development with marked increases in realisable energy conversion efficiencies. At about the same time, there was a reawakening of interest in terrestrial use of these devices. By the end of the 1970's, the volume of cells produced for terrestrial use had completely outstripped that for space use. This increase in production volume was accompanied by a significant reduction in solar cell costs. The early 1980's saw newer device technologies being evaluated at the pilot production stage, poised to enable further reduction in costs over the coming decade such as copper indium diselenide and cadmium telluride based devices. Today, attention is concentrated on implementing new devices such as organic solar cells or multijunction cells and also on improving performances of current devices.

#### 2.1.2 The Photovoltaic Effect

The photovoltaic (PV) effect in a semiconductor is the combined result of two processes. The first one is the generation of carriers by interaction of incident photons with the semiconductor. The second process consists of the collection of those generated carriers in order to create an electrical current. Those two stages are now explained.

Carrier generation depends upon the photon energy hv and the energy bandgap  $E_g$  of the semiconductor. If  $hv < E_g$  then nothing will happen as the energy provided by the photon is too small to excite an electron from the valence band to the conduction band of the semiconductor. If  $E_g \le hv < 2E_g$  an electron-hole pair is created by the promotion of an electron across the bandgap of the semiconductor. In a third case, if  $hv \ge 2E_g$  the electron promoted across the bandgap gain enough energy so that it can excite electron-holes pairs by the process known as impact ionisation.

Carrier collection is achieved by separating an electron and hole pair through the creation of a built-in electric field. In a solar cell, such a field arises when a semiconductor is put in contact with a metal, i.e. Schottky barrier, or to another semiconductor. In the latter case, the two semiconductors can be of different compounds (heterojunction) or from the same material but differently doped (homojunction).

In this chapter, the three different solar cell configurations mentioned above are described followed by the derivation of the diode equation for an ideal p-njunction and the description of solar cell parameters from the current-voltage J-Vcurve. Finally, losses and limitations affecting cell parameters are introduced followed by a review of the different types of photovoltaic devices and the materials used for them.

#### 2.2 Solar Cell Configurations

#### 2.2.1 Schottky Junction

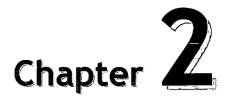

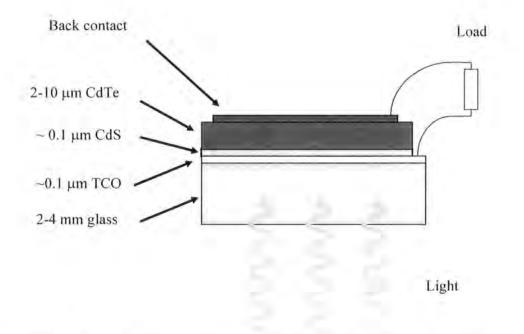

The potential barrier, which forms when a metal is in contact with a semiconductor, arises from the separation of charges at the metal-semiconductor interface. The energy band diagrams in Figure 2-1 illustrate the process of barrier formation. Figure 2-1 a) shows the electron energy band diagram of a metal having a work function  $\phi_m$  and an *n*-type semiconductor of work function  $\phi_s$  and electron affinity  $\chi_s$ .

**Figure 2-1** Electron energy band diagrams of a metal contact to an *n*-type semiconductor with  $\phi_m > \phi_s$ . a) Neutral materials separated from each other and b) thermal equilibrium situation after the contact has been made.

Figure 2-1 b) shows the energy band diagram after the contact is made and equilibrium has been reached. When the two materials are brought into intimate contact, electrons from the conduction band of the semiconductor, which have higher energy than the metal electrons, flow into the metal until the Fermi level on the two sides is brought into coincidence. As the electrons move out of the semiconductor into the metal, the free electron concentration in the semiconductor region near the boundary decreases. Since the separation between the conduction band edge  $E_C$  and the Fermi level  $E_F$  of the semiconductor increases with decreasing electron concentration, the conduction band edge bends up as shown in Figure 2-1 b).

The conduction band electrons which cross over into the metal leave a positive charge of ionised donors behind, so the semiconductor region near the metal gets depleted of mobile electrons. Thus a positive charge is established on the semiconductor side of the interface and the electrons which cross over into the metal form a thin sheet of negative charges. Consequently an electric field is established from the semiconductor to the metal.

The amount of band bending is equal to the difference between the two vacuum levels and is  $qV_{bi} = \phi_m - \phi_s$  where  $V_{bi}$  is the built-in potential of the junction.  $qV_{bi}$  is the potential barrier which an electron, moving from the semiconductor into the metal, has to surmount. However, the barrier looking from the metal towards the semiconductor is different and is given by  $\phi_B = \phi_m - \chi_s = qV_{bi} + \phi_n$  where  $\phi_n = E_C - E_F$  represents the penetration of the Fermi level in the bandgap of the semiconductor.

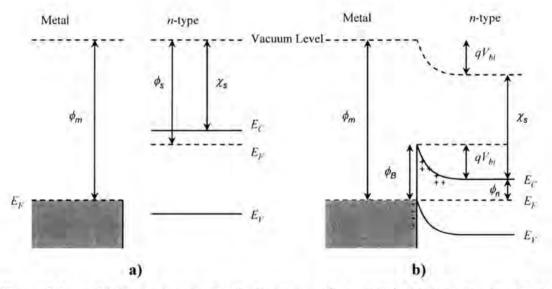

#### 2.2.2 Homojunction

We now consider the case of a formation of a barrier between two semiconductors of the same material, doped differently to ensure they have opposite conductivity. The energy band diagram of the isolated pieces of semiconductor is shown in Figure 2-2 a). When contacted together, the Fermi level of the two semiconductors are brought into coincidence at the equilibrium condition so some electrons have migrated from the *n*-type into the *p*-type and a dipole layer of charge exists near the contact surface creating a barrier. This is shown in Figure 2-2 b). Again the amount of band bending is equal to the difference between the two vacuum levels,  $qV_{bi} = \phi_p - \phi_n$ .

**Figure 2-2** Electron energy band diagram of a homojunction: a) Neutral materials separated from each other and b) thermal equilibrium situation after the contact has been made.

#### 2.2.3 Heterojunction

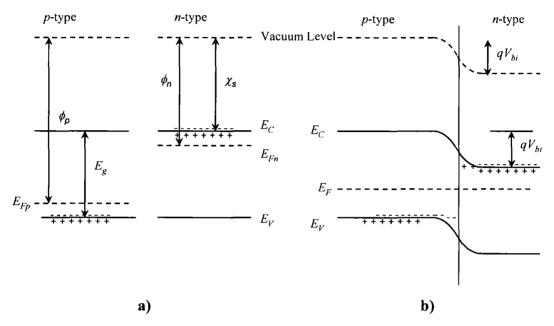

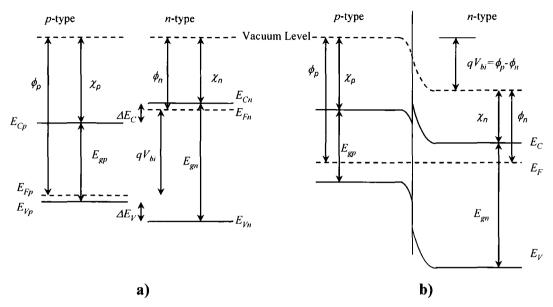

A heterojunction is a junction formed between semiconductors having different energy bandgaps. The energy band model of the two isolated semiconductors is shown in Figure 2-3 a). When the junction is formed between these semiconductors, the energy band profile at equilibrium is shown in Figure 2-3 b) and based upon the Anderson model [4].

The differences in energy bandgap and electron affinity require discontinuities in the conduction band and valence band,  $\Delta E_C$  and  $\Delta E_V$  that can be seen on the diagram. These discontinuities act as barriers to the flow of electrons and limit the performance of the solar cell.

**Figure 2-3** Electron energy band diagram of a heterojunction. a) Neutral materials separated from each other and b) thermal equilibrium situation after the contact has been made.

The heterojunction structure is the configuration that concerns the CdTe/CdS structures used in this work. The wide bandgap CdS material is referred to as the window layer and the narrow bandgap CdTe semiconductor as the absorber or active layer. Although the homojunction offers no possibility of discontinuities in the band diagram at the interface, a working constraint of homojunction is that the active junction must be located near the surface in order to avoid strong absorption loss in the layer which receives the light. This can significantly reduce the generated current due to surface recombination in absorbers with high absorption coefficients. However, some of the most efficient cells to date use this type of junction. Indeed, silicon homojunction are eminently practical in contrast to those made from compound semiconductors for which the absorption coefficients are higher. The Schottky junction is also of concern in this work: one of the inherent difficulties in device processing is the inability, due to the high work function of CdTe (5.8 eV), to prepare ohmic contacts to *p*-CdTe. If the metallization layer has a smaller work function, a Schottky barrier will form when the two materials are contacted.

#### 2.3 Diode Physics and Cell Parameters

#### 2.3.1 The Diode Equation

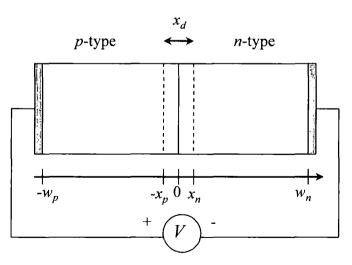

The current voltage characteristic for an ideal p-n junction was first derived by Shockley in 1949 [5]. The derivation assumed that the doped regions are uniformly doped and that the transition between the two regions is abrupt. It also assumed low level injection, i.e. the injected minority carrier densities are small compared to the majority carrier densities. A diagram of the junction is presented in Figure 2-4.

The minority carrier densities at the edges of the depletion width  $x_d$  are defined for the holes as:

$$p_n(x = x_n) = p_{n_0} \exp\left(\frac{qV}{kT}\right)$$

(2-1)

and for the electrons

$$n_p(x = -x_p) = n_{p_0} \exp\left(\frac{qV}{kT}\right)$$

(2-2)

where V is the applied voltage, T the temperature, k the Boltzman constant, q the electronic charge,  $p_{n_0}$  and  $n_{p_0}$  are the equilibrium hole and electron density respectively on the *n*-side and *p*-side.

**Figure 2-4** Diagram of a *p*-*n* junction cross section.

The carrier density at the metal contacts is assumed to be equal to the thermal equilibrium carrier density. This assumption implies that excess carriers immediately recombine when reaching either of the two metal-semiconductor contacts. This results in the following set of boundary conditions:

$$p_n(x = w_n) = p_{n_0} \tag{2-3}$$

and

$$n_p(x = -w_p) = n_{p_0} \tag{2-4}$$

The general expression for the ideal diode current is obtained by applying the boundary conditions to the general solution of the diffusion equation for each of the quasi neutral regions:

$$p_n(x \ge x_n) = p_{n_0} + A \exp\left(-\frac{x - x_n}{L_p}\right) + B \exp\left(\frac{x - x_n}{L_p}\right)$$

(2-5)

$$n_{p}\left(x \leq -x_{p}\right) = n_{p_{0}} + C \exp\left(-\frac{x + x_{p}}{L_{n}}\right) + D \exp\left(\frac{x + x_{n}}{L_{n}}\right)$$

(2-6)

where  $L_n$  and  $L_p$  are the diffusion lengths of electrons and holes, respectively and A, B, C and D are constants.

Applying the boundary conditions after rearranging equations 2-5 and 2-6 into hyperbolic terms and assuming  $\frac{1}{\tanh x} \cong \frac{1}{x}$  for  $x \ll 1$  yields:

$$p_n(x \ge x_n) = p_{n_0} + p_{n_0} \left( \exp\left(\frac{qV}{kT}\right) - 1 \right) \exp\left(\frac{-(x - x_n)}{L_p}\right)$$

(2-7)

$$n_p(x \le -x_p) = n_{p_0} + n_{p_0} \left( \exp\left(\frac{qV}{kT}\right) - 1 \right) \exp\left(\frac{x + x_p}{L_n}\right)$$

(2-8)

The current density in each region is obtained by calculating the diffusion current density [6]:

$$J_{p}(x \ge x_{n}) = qD_{p} \frac{\delta p_{n}}{\delta x}$$

$$= \frac{qD_{p}p_{n_{0}}}{L_{p}} \left( \exp\left(\frac{qV}{kT}\right) - 1 \right) \exp\left(\frac{-(x - x_{n})}{L_{p}}\right)$$

(2-9)

and

$$J_{n}(x \leq -x_{p}) = qD_{n} \frac{\delta n_{p}}{\delta x}$$

$$= \frac{qD_{n}n_{p_{0}}}{L_{n}} \left( \exp\left(\frac{qV}{kT}\right) - 1 \right) \exp\left(\frac{x + x_{p}}{L_{n}}\right)$$

(2-10)

where  $D_n$  and  $D_p$  are the diffusion coefficients for electrons and holes, respectively.

The total current must be constant throughout the structure since a steady state case is assumed. No charge can accumulate or disappear somewhere in the structure so that the charge flow must be constant throughout the diode. The total current then equals the sum of the maximum electron current in the *p*-type region and the maximum hole current in the *n*-type region. The maximum currents in the quasi-neutral regions occur at either side of the depletion region and can therefore be calculated from equations 2-9 and 2-10. The total current is then given by:

$$J = J_n + J_p = J_0 \left( \exp\left(\frac{qV}{kT}\right) - 1 \right)$$

(2-11)

where  $J_0 = \frac{qD_n n_{p_0}}{L_n} + \frac{qD_p p_{n_0}}{L_p}$

Equation 2-11 is the diode equation for an ideal p-n junction with  $J_0$  the saturation current density.

#### 2.3.2 Current-Voltage Characteristic and Cell Parameters

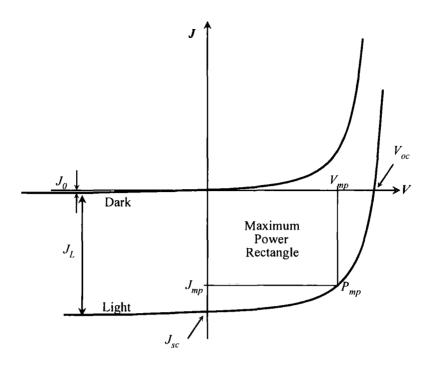

The diode equation for an ideal homojunction was previously derived in the dark (equation 2-11). Under illumination the dark current-voltage (*J-V*) characteristic is translated downward by the magnitude of the light generated current density  $J_L$  without change in shape (equation 2-13). These ideal characteristics for a solar cell operating in the dark and under illumination are shown in Figure 2-5.

$$J = J_0 \left( \exp\left(\frac{qV}{AkT}\right) - 1 \right) - J_L$$

(2-13)

where  $J_0$  is the reverse saturation current density,  $J_L$  the light generated current density and A the diode quality factor. For an ideal junction, the diode factor is equal to 1 and in real devices it is almost always between one and two.

(2-12)

**Figure 2-5** Typical current-voltage (J-V) curves for a solar cell operating in the dark and under illumination. The important points are marked on the plot and are explained in the text.

From the light J-V characteristic, the primary parameters of the solar cell under investigation may be extracted. These are open circuit voltage  $V_{oc}$ , short circuit current density  $J_{sc}$ , efficiency  $\eta$  and fill factor FF, and are defined as:

**Open circuit voltage** The open circuit voltage  $V_{oc}$  is defined as the applied voltage at which no current is flowing through the junction. For an ideal cell the open circuit voltage value is obtained by setting the total current to zero and has a value of:

$$V_{oc} = \frac{AkT}{q} \ln \left( \frac{J_L}{J_0} + 1 \right)$$

(2-14)

**Short circuit current** The short circuit current density  $J_{sc}$  is the current density measured when no bias is applied to the device and in an ideal case it is equal to the light generated current density  $J_L$ .

**Fill Factor** The fill factor is given by:

$$FF = \frac{J_{mp} \times V_{mp}}{J_{sc} \times V_{oc}}$$

(2-15)

where  $J_{mp}$  and  $V_{mp}$  are the current density and voltage describing the maximum output power  $P_{mp}$  of the cell and is computed from the area of the rectangle indicated in the fourth quadrant of the *J-V* curve. The fill factor is a measure of the "squareness" of the *J-V* curve in forward bias.

**Efficiency** The efficiency gives the power conversion of the device and is defined as the ratio of the maximum power over the incident illumination intensity  $P_{in}$ :

$$\eta = \frac{J_{mp} \times V_{mp}}{P_{in}} \tag{2-16}$$

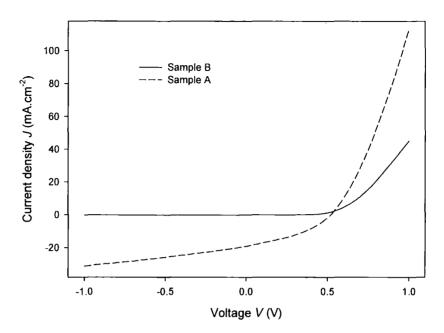

Typical values for a 16.5% efficient CdTe/CdS cell are:  $V_{oc} = 850$  mV,  $J_{sc} = 25$  mA/cm<sup>2</sup> and FF = 75% [7].

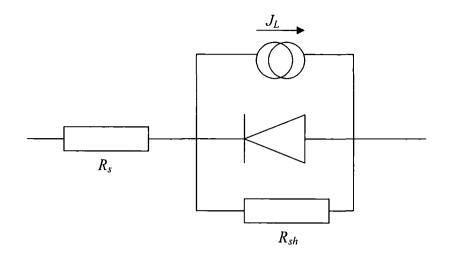

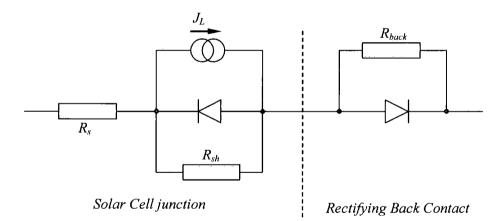

Although these four parameters have been used throughout this work, in the case of real devices, the diode equation must be modified to take into account the resistance losses due to the different layers. Two resistances are introduced, the series resistance  $R_s$  and the shunt resistance  $R_{sh}$ . The series resistance arises from the resistance of the different layers of the device, and hence limits the total output current available. The shunt or parallel resistance is attributed to short circuit paths through the device. The ideal single diode equation can be modified to describe real devices:

$$J = J_0 \left[ \exp\left(\frac{q(V - JR_s)}{AkT}\right) - 1 \right] + \frac{V - JR_s}{R_{sh}} - J_L$$

(2-17)

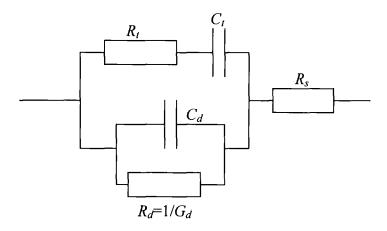

The equivalent circuit is shown in Figure 2-6. It consists of a current source in parallel with a non-ideal diode, i.e. with a diode quality factor  $\neq 1$ . In addition are included a shunt resistor to model the current flowing through pin-holes in the window layer and a resistor in series to take into account the resistance of the films.

Figure 2-6 Equivalent single diode circuit for a real solar cell.

#### 2.3.3 Efficiency Limits and Losses

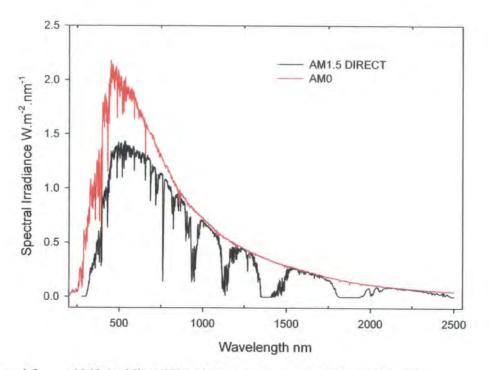

The major constraints on photovoltaic efficiency come from the poor match between the broad spectral distribution of the sunlight and the single bandgap  $E_g$  of a given semiconductor. The bandgap of a photoactive semiconductor determines the upper bound of both the open circuit voltage  $V_{oc}$  and short circuit current density  $J_{sc}$ . A narrow bandgap cell such as a silicon based device has a larger  $V_{oc}$  than a wider bandgap cell, e.g. CdTe device, but it absorbs fewer photons so it has a smaller  $J_{sc}$ . The theoretical limit for a single junction cell is a power conversion efficiency of ~30% for a bandgap of ~1.4 eV [8].

As mentioned earlier for the case of real devices, power losses are also due to the presence of series and shunt resistances. Series resistance arises both from the resistance of the semiconductor bulk and from the contact resistance to the semiconductor to complete the circuit. Shunt resistance arises from imperfections on the devices surface or in the bulk as well as leakage currents across the edge of the cell. The experimental determination of series and shunt resistance from the *J-V* curve is explained in Chapter 7. In this section, origins of losses are considered with regard to the main parameters of the cells,  $J_{sc}$ ,  $V_{oc}$  and *FF*.

#### 2.3.3.1 Short Circuit Current

Under ideal conditions, each incident photon of greater energy than the bandgap gives rise to one electron flowing in the external circuit. Hence, to calculate the maximum short circuit current, the photon flux of the sunlight must be known. This can be calculated from the energy distribution of the sunlight by dividing the energy content at a given wavelength by the energy of an individual photon. The maximum  $J_{sc}$  is then found by integrating these distributions from low wavelengths up to the maximum wavelength for which electron hole pairs can be generated for a given semiconductor. Types of optical losses can be described as follows:

- (i) Reflection losses at the front surface of the glass substrate in superstrate configuration cell. Reflection losses also occur at the interfaces between the different layers constituting the cell [9]. To reduce this, an anti-reflective coating such as  $MgF_2$  is used in some applications [10-12].

- (ii) Absorption losses occur in the glass substrate, front contact and window layer. The substrate and the front contact can account for a loss of 5-10% of the incoming sunlight [13].

- (iii) If the cell is not thick enough, some of the light will pass right through before being absorbed. This problem is not significant for direct bandgap materials like CdTe as it has a large absorption coefficient,  $\sim 10^5$  cm<sup>-1</sup> [14, 15].

- (iv) In the case of large area modules, a conductive grid is used to retrieve the current at the front contact, grid that can cover 5 to 15% [13] of the structure area generating considerable optical losses.

Because of the wavelength dependence of the absorption coefficient, it is expected that the shorter wavelength photons will be absorbed close to the surface, while those with longer wavelengths are absorbed deeper in the bulk. Surface recombination will therefore be more important for short wavelengths while recombination in the quasi-neutral region is more important for long wavelengths. Short circuit current losses can also occur due to the recombination at the surfaces and/or in the bulk of semiconductor materials. Only electron-hole pairs generated in the depletion region of the *p-n* junction contribute towards  $J_{sc}$ .

#### 2.3.3.2 Open Circuit Voltage

The ideal open circuit voltage value (equation 2-14) can be simplified for  $J_L/J_0 >> 1$  as:

$$V_{oc} = \frac{AkT}{q} \ln\left(\frac{J_L}{J_0} + 1\right) \approx \frac{AkT}{q} \ln\left(\frac{J_L}{J_0}\right)$$

(2-18)

For a good cell performance,  $V_{oc}$  and hence  $J_L$  must be as large as possible. The maximum value of  $J_L$  would be obtained if all photo-generated electron hole pairs are collected as photocurrent.  $J_L$  can achieve 80-90% of this limit if light absorption and minority carrier collection are both highly efficient [16]. The limiting value of  $V_{oc}$  is the built-in voltage barrier  $qV_{bi}$  and usually  $V_{oc}$  is no more than  $0.7 \times qV_{bi}$ . Inspection of equation 2-18 shows that  $V_{oc}$  increases as the saturation current  $J_0$  decreases. Interestingly,  $J_0$  has no absolute minimum value. In thin film solar cells with well passivated surfaces,  $J_0$  can be reduced to zero and  $V_{oc}$  increased to its upper limit of  $qV_{bi}$ . In thicker cells where volume recombination occurs, the lower limit on  $J_0$  is determined by the rate of radiative recombination of minority carriers. Usually non-radiative recombination also occurs and this raises  $J_0$  by some orders of magnitude and lowers  $V_{oc}$  accordingly.

#### 2.3.3.3 Fill Factor

The fill factor is strongly affected by series and shunt resistances due to their influence on  $J_{sc}$  and  $V_{oc}$ . Series resistance in high efficiency polycrystalline cells is usually small ( $R_s < 1 \ \Omega$ .cm) and probably dominated by the TCO layer [4].

The fill factor is also influenced by the voltage dependence of the light generated current. This can be easily observed on the J-V curve, by the fact that the dark and light curves cannot be superimposed. At reverse and small forward bias the light generated current decreases with increasing voltage hence reducing the fill factor value.

#### 2.4 Types of Solar Cells

The first solar cell was developed at Bell laboratories in 1954 [3]. At that time, solar cells were made from semiconductor grade single crystalline silicon and were used as power source for space applications such like on satellites. The systems were very reliable, and the cost was of little concern with regard to huge space program budgets. At present, solar cells can be single junction devices or multijunction structures and new technologies are employed for making solar cells. Nanotechnology have helped producing a 8.2% efficient nanocrystalline dyesensitized solar cell [17] while organic cells with 3-4% efficiencies have been reported [18]. However, most efficient devices have been produced using inorganic materials and the technology of these solar cells is outlined next.

#### 2.4.1 Single Crystal and Polycrystalline Silicon

Silicon is still the most popular solar cell material for commercial application because it is so readily abundant (it is actually the second most abundant element in the earth's crust second only to oxygen [19]). Another reason why silicon is a popular choice for photovoltaic energy generation is the large technology base that has built up over the past 50 years for silicon used in the semiconductor industry [19]. The source material for extraction of silicon is silicon dioxide, the major constituent of sand. Single crystalline and polycrystalline silicon have an indirect bandgap of 1.1 eV and low absorption coefficient  $(1.1 \times 10^3 \text{ cm}^{-1} \text{ at } 1.63 \text{ eV} [4])$ . This means that over a large range of the visible spectrum, light absorption occurs only with the assistance of phonons. Phonons provide the additional wave vector needed for momentum conservation in any energy transition in an indirect bandgap semiconductor.

Single crystal silicon devices have attained an efficiency of 24.4% [20] on the laboratory scale. Commercial crystalline silicon solar cell modules are available with conversion efficiencies as high as 22.7% [21]. The major disadvantages of single crystal silicon solar cells are the requirements of high grade material and the problems associated with producing single crystals over large areas. Recently, there have been some imaginative attempts to make single crystal ribbon silicon, which is

lower in cost than high quality single crystals and today, accounts for 10% of the world PV total [22, 23].

The production of polycrystalline silicon cells is more cost effective than single crystal silicon. Silicon is poured into blocks that are subsequently sawn into plates. During solidification of the material, crystal structures of varying sizes are formed. Polycrystalline silicon has the disadvantage that large grain sizes are required to reduce the negative influence caused by grain boundaries. In polycrystalline silicon the smaller crystals or "grains" introduce boundaries that impede the flow of electrons and encourage them to recombine with holes, thereby reducing the output power of the cell. However, polycrystalline silicon is much cheaper to produce than single crystal silicon, hence researchers are working on new innovative ways of minimizing the effects of grain boundaries.

#### 2.4.2 Group III-V Technologies

Photovoltaic technologies based on group III and V elements in the periodic table show very high efficiencies under either normal or concentrated sunlight. Although expensive, their cost can be compensated for by using concentrators, which increase the energy conversion efficiency under higher illumination [24, 25]. Concentrators focus light from a large area to a small area, thereby increasing illumination to many times the terrestrial sunlight. The most important solar cells in this category are gallium arsenide (GaAs) and indium phosphide (InP).

#### 2.4.2.1 Gallium Arsenide

Gallium arsenide is a compound semiconductor for which the use in solar cells has been developing synergistically with its use in light emitting diodes, lasers, and other optical devices. It has a direct bandgap of 1.43 eV, nearly ideal for single junction solar cells [8]. The absorption coefficient of GaAs is relatively high (>  $10^4$  cm<sup>-1</sup> for  $h\nu$  > 1.45 eV [26]) and causes sufficient absorption of photons in only a few microns of material. It is also very resistant to radiation damage. This, along with its high efficiency, makes GaAs very desirable for space applications. The most efficient solar cell to date has been based on this material and cells of 25.1% efficiency have already been confirmed [21]. When used in concentrator application,

the efficiency increases to 27.6% [27]. The greatest barrier to the success of GaAs cells has been the high cost of single crystalline GaAs substrates. For this reason, GaAs cells are used primarily in concentrator system. For mass production of GaAs solar cells, gallium element availability and the toxic nature of the arsenic are considered as major limitations of this technology.

#### 2.4.2.2 Indium Phosphide

Indium phosphide (InP) has a direct bandgap of 1.34 eV, close to the optimum for solar energy conversion [8]. Research on InP heterojunctions did not start until about 1974, probably because of the unavailability of high quality single crystals of *p*-type InP. InP crystals are grown by the Czochraski method at high pressures using the liquid encapsulation technique to preserve the stoichiometry [28]. A 21.9% efficient InP crystalline solar cell was reported 15 years ago [29]. When a 99-sun concentrator is used, the efficiency increases to 24.3% [30]. A 31.8% multijunction InP/GaInAs cell, operating at 50 suns concentration has been achieved [31]. The major limitation of this technology is the high cost due to limited resources for indium and purification of phosphorous.

#### 2.4.3 Thin Film Solar Cell

In an effort to reduce the fabrication costs of the present technology based on silicon, and to increase material utilisation, thin film materials have been the subject of intensive research. Three main types of materials have emerged as the most promising candidates for the next generation of solar cells. These are hydrogenated amorphous silicon (a-Si:H), cadmium telluride (CdTe) and copper indium diselenide (CuInSe<sub>2</sub>) and its related alloys.

#### 2.4.3.1 Hydrogenated Amorphous Silicon a-Si:H

Amorphous silicon films exhibit very different characteristics than crystalline silicon. The main difference between the two materials is that there is no long-range order in the amorphous film. There is also a large number of dangling bonds in amorphous films that create trap states throughout the bandgap region. In order to remove the dangling bonds, amorphous silicon films are hydrogenated during deposition. This results in the occupation of dangling bonds by hydrogen atoms. Hydrogenated amorphous silicon (a-Si:H) exhibits a bandgap that is not well defined. Its value may vary from approximately 1.6 to 1.8 eV depending on deposition conditions. For plasma chemical vapour deposited a-Si:H, the variation depends on the deposition conditions including substrate temperature, RF power and gas pressure [32]. This material can be doped either p- or n-type by introduction, during deposition, of boron or phosphorous, respectively.

Solar cells fabricated from a-Si:H are based on a p-*i*-n structure rather than a p-n junction. This is because the doping necessary to generate the field across the junction results in a very high defect density, greatly reducing carrier lifetime. The deposition of an insulating intrinsic layer between thin p-type and n-type layers circumvents this problem. A nominally 100 nm thick p-type layer and a 20-30 nm thick n-type layer generate a field across the 100-400 nm intrinsic layer. The intrinsic layer becomes the absorber in this configuration, with the collection of the generated carriers enabled by the externally generated field. Textured surfaces are typically used in this type of device to induce light trapping, thereby effectively increasing the optical path length within the device. This results in an increased probability of collecting each photon and generating an electron-hole pair. A primary problem associated with these devices is a photo-induced increase in defect density resulting in degraded device performance [33]. The effect can be reversed by annealing the device after degradation, but the process repeats when the device is again illuminated. Elimination of this effect is a topic of current research.

#### 2.4.3.2 Copper Indium Diselenide (CuInSe<sub>2</sub>)

One of the most promising thin film solar cell devices is based on CuInSe<sub>2</sub> (CIS) absorber films. Conversion efficiencies of between 12 and 15% have already been achieved for devices based on a CuInSe<sub>2</sub>/CdS/ZnO heterojunction [34-36]. The bandgap of CIS can be modified continuously over a wide range (i.e. 1.0-1.65 eV) by substituting Ga for In. Similarly, one can also increase the bandgap by the substitution of Se for S.

Recent trends in  $CuInSe_2$  research and development focus on these high bandgap chalcopyrite alloys, and preliminary results indicated that conversion efficiencies above 18% can be achieved when using these specific absorber films [37]. Gallium incorporation is also believed to improve adhesion between the CIS and the molybdenum electrical back contact [38] and also increases the open circuit voltage of the cell. Record efficiency of 19.2% has been demonstrated using this type of devices [39]. Beside basic investigations at various university laboratories, commercialisation of CIS based solar cell technology has already been realised. To compete with silicon solar cells, conversion efficiency above 10% is required on large areas and currently, the best modules can achieve 13.4% efficiency for an active area of 3460 cm<sup>2</sup> [40].

#### 2.4.3.3 Cadmium Telluride (CdTe)

Cadmium telluride was very early seen as one of the best materials for solar cell applications with a theoretical efficiency limit of ~27% [8], CdTe is the nearly ideal material for absorbing the maximum amount of the solar spectrum with minimal losses. CdTe is typically used in conjunction with cadmium sulphide (CdS) for the formation of heterojunctions. The first CdTe/CdS solar cell device was developed by Bonnet and Rabenhorst in the early 1970's and achieved a power conversion of ~5% [41]. Today the best cell reaches an efficiency of 16.5% in laboratories [7] whilst large area modules perform at ~11% [42].

The development of CdTe/CdS cells has been dominated by empirical methodology. For example, the 99.999% purity standard used in industry has not been defined by systematic investigations. Hence doping by residual impurities and the CdCl<sub>2</sub> post-growth heat treatment is an optimised if not fully understood process. One feature of the present work is to investigate the feasibility of intentional arsenic doping of CdTe as a new route to controllable CdTe/CdS solar cells.

In order to perform well CdTe solar cells require a post-deposition heat treatment in a CdCl<sub>2</sub> environment (see for example [43]). One of the critical issues for CdTe-based devices is the formation of an ohmic back contact, which requires in most case a chemical treatment of the surface [44]. This CdCl<sub>2</sub> treatment and back contact formation as well as the CdTe/CdS solar cell as a whole are studied in more depth in the next chapter as it is the type of solar cell concerned in this work.

# 2.5 References for Chapter 2

- 1. E. Becquerel, On electric effects under the influence of solar radiation, Comptes Rendus Hebdomadaires des Séances de l'Académie des Sciences 9 (1839) 561

- 2. W. G. Adams and R. E. Day, *The action of light on selenium*, Proceedings of the Royal Society of London A25 (1877) 113

- 3. D. M. Chapin, C. S. Fuller, and G. L. Pearson, A new silicon p-n junction photocell for converting solar radiation into electrical power, Journal of Applied Physics **25** (1954) 676-677

- 4. A. L. Fahrenbruch and R. H. Bube, *Fundamentals of Solar Cells: Photovoltaic Solar Energy Conversion.* (1983) Academic Press

- 5. W. Shockley, *The theory of p-n junctions in semiconductors and p-n junction transistors*, Bell Syst. Tech. J. **28** (1949) 435

- 6. S. M. Sze, *Physics of Semiconductor Devices*. 2<sup>nd</sup> Edition (1981) Wiley

- 7. X. Wu, J. C. Keane, R. Dhere, C. DeHart, D. S. Albin, A. Duda, T. A. Gessert, S. Asher, D. H. Levi, and P. Sheldon, *16.5%-efficient CdS/CdTe polycrystalline thin-film solar cell*, Proceedings of the 17<sup>th</sup> European Photovoltaic Solar Energy Conference, Munich, Germany (2001)

- 8. J. J. Loferski, Theoretical considerations governing the choice of the optimum semiconductor for photovoltaic solar energy conversion, Journal of Applied Physics 27 (1956) 777-784

- 9. J. R. Sites, *Quantification of losses in thin-film polycrystalline solar cells*, Solar Energy Materials and Solar Cells **75** (2003) 243-251

- D. H. Rose, D. H. Levi, R. J. Matson, D. S. Albin, R. G. Dhere, and P. Sheldon, *The role of oxygen in CdS/CdTe solar cells deposited by close-spaced sublimation*, Proceedings of the 25<sup>th</sup> IEEE Photovoltaic Specialists Conference, Washingtion, D. C. (1996) 777-780

- 11. M. A. Green, *Limiting efficiency of bulk and thin-film silicon solar cells in the presence of surface recombination*, Progress in Photovoltaics: Research and Applications 7 (1999) 327

- M. A. Contreras, T. Nakada, M. Hongo, A. O. Pudov, and J. R. Sites, ZnO/ZnS(O,OH)/Cu(In,Ga)Se<sub>2</sub>/Mo solar cell with 18.6% efficiency, Proceedings of the 3<sup>rd</sup> World Conference on Photovoltaic Energy Conversion, Osaka, Japan (2003) 2LN-C08

- 13. M. A. Green, Solar cells: operating principles, technology and system applications. (1992) Prentice-Hall

- K. Mitchell, A. L. Fahrenbruch, and R. H. Bube, *Photovoltaic determination* of optical-absorption coefficient in CdTe, Journal of Applied Physics 48 (1977) 829-830

- 15. X. Mathew and P. J. Sebastian, *Optical properties of electrodeposited CdTe thin films*, Solar Energy Materials and Solar Cells **59** (1999) 85-98

- 16. J. R. Sites, J. E. Granata, and J. F. Hiltner, *Losses due to polycrystallinity in thin-film solar cells*, Solar Energy Materials and Solar Cells **55** (1998) 43-50

- A. Hinsch, J. Kroon, R. Kern, R. Sastrawan, A. Meyer, and I. Uhlendorf, Long-term stability and efficiency of dye-sensitized solar cells, Proceedings of the 17<sup>th</sup> European Photovoltaic Solar Energy Conference, Munich, Germany (2001) 51-54

- 18. C. Waldauf, P. Schilinsky, J. Hauch, and C. J. Brabec, *Material and device concepts for organic photovoltaics: towards competitive efficiencies*, Thin Solid Films **451-452** (2004) 503-507

- 19. R. H. Bube, *Photovoltaic materials*. (1998) Imperial College Press

- 20. J. Zhao, A. Wang, M. A. Green, and F. Ferrazza, 19.8% efficient "honeycomb" textured multicrystalline and 24.4% monocrystalline silicon solar cells, Applied Physics Letters 73 (1998) 1991-1993

- 21. M. A. Green, K. Emery, D. L. King, S. Igari, and W. Warta, *Solar cell efficiency tables (version 23)*, Progress in Photovoltaics: Research and Applications **12** (2004) 55-62

- 22. J. Falejs, B. Bathey, J. Cao, J. Doedderlein, R. Gonsiorawski, B. Heath, B. Mackintosh, M. Ouellette, M. Rosenblum, B. Southimath, and G. Xavier, *EFG ribbon technology R&D for large scale photovoltaic manufacturing*, NCPV and Solar Program Review Meeting, (2003) 600-604

- 23. W. Schmidt, B. Woesten, and J. P. Kalejs, *Manufacturing technology for* ribbon silicon (EFG) wafers and solar cells, Progress in Photovoltaics: Research and Applications 10 (2002) 129-140

- 24. R. M. Swanson, *The promise of concentrators*, Progress in Photovoltaics: Research and Applications 8 (2000) 93-111

- 25. V. M. Andreev, V. P. Khvostikov, V. R. Larionov, V. D. Rumyantsev, E. V. Paleeva, and M. Z. Shvarts, *High-efficiency AlGaAs/GaAs concentrator* (2500 suns) solar cells, Semiconductors **33** (1999) 976-977

. . . . . . . .

- 26. H. C. Casey, Jr., D. D. Sell, and K. W. Wecht, *Concentration dependence of* the absorption coefficient for n- and p type GaAs between 1.3 and 1.6 eV, Journal of Applied Physics **46** (1975) 250-257

- S. M. Vernon, S. P. Tobin, V. E. Haven, L. M. Geaffroy, and M. M. Sanfacon, *High-efficiency concentrator cells from GaAs on Si*, Proceedings of the 22<sup>nd</sup> IEEE Photovoltaic Specialists Conference, Las Vegas, Nevada (1991) 353-357

- 28. J. B. Mullin, *Progress in the melt growth of III-V compounds*, Journal of Crystal Growth **264** (2004) 578-592

- 29. C. J. Keavney, V. E. Haven, and S. M. Vernon, *Emitter structures in MOCVD InP solar cells*, Proceedings of the 21<sup>st</sup> IEEE Photovoltaic Specialists Conference, Kissimmee, Florida (1990) 31-36

- 30. J. S. Ward, M. W. Wanlass, T. J. Coutts, K. Emery, and C. R. Osterwald, *InP* concentrator solar cells, Proceedings of the 22<sup>nd</sup> IEEE Photovoltaic Specialists Conference, Las Vegas, Nevada (1991) 365-370

- M. W. Wanlass, T. J. Coutts, J. S. Ward, K. Emery, T. A. Gessert, and C. R. Osterwald, Advanced high-efficiency concentrator tandem solar cells, Proceedings of the 21<sup>st</sup> IEEE Photovoltaic Specialists Conference, Kissimmee, Florida (1990) 38-45

- 32. Y. Hishikawa, S. Tsuda, K. Wakisaka, and Y. Kuwano, Principles for controlling the optical and electrical properties of hydrogenated amorphous silicon deposited from a silane plasma, Journal of Applied Physics 73 (1993) 4227-4231

- 33. D. L. Staebler and C. R. Wronski, *Optically induced conductivity changes in discharge-produced hydrogenated amorphous silicon*, Journal of Applied Physics **51** (1980) 3262-3268

- 34. S. Verma, N. Orbey, R. W. Birkmire, and T. W. Russel, *Chemical reaction* analysis of copper indium selenization, Progress in Photovoltaics: Research and Applications 4 (1996) 341-353

- 35. H. Sato, T. Hama, C. Niemi, Y. Ichikawa, and H. Sakai, Fabrication oh high efficiency CuIn(Ga)Se<sub>2</sub> thin film solar cell by selenization with H<sub>2</sub>Se, Proceedings of the 23<sup>rd</sup> IEEE Photovoltaic Specialists Conference, Louisville, Kentucky (1993) 521-526

- 36. J. Hedstrom, H. Ohlsen, M. Bodegard, A. Kyler, L. Stolt, D. Hariskos, M. Ruuch, and H. W. Schock, ZnO/CdS/Cu(In,Ga)Se<sub>2</sub> thin film solar cells with improved performance, Proceedings of the 23<sup>rd</sup> IEEE Photovoltaic Specialists Conference, Louisville, Kentucky (1993) 364-371

- 37. M. A. Contreras, B. Egaas, K. Ramanathan, J. F. Hiltner, A. Swartzlander, F. Hasoon, and R. Noufi, *Progress Towards 20% efficiency in Cu(In,Ga)Se*

polycrystalline thin-film solar cell, Progress in Photovoltaics: Research and Applications 7 (1999) 311-316

- 38. C. L. Jensen, D. E. Tarrant, J. H. Ermer, and G. A. Pollock, *The role of gallium in CuInSe<sub>2</sub> solar cells fabricated by a two-stage method*, Proceedings of the 23<sup>rd</sup> IEEE Photovoltaic Specialists Conference, Louisville, Kentucky (1993) 577-580

- K. Ramanathan, M. A. Contreras, C. L. Perkins, S. Asher, F. S. Hasoon, J. Keane, D. Young, M. J. Romero, W. Metzger, R. Noufi, J. Ward, and A. Duda, *Properties of 19.2% efficiency ZnO/CdS/CuInGaSe<sub>2</sub> thin-film solar cells*, Progress in Photovoltaics: Research and Applications 11 (2003) 225-230

- 40. Y. Tanaka, N. Akema, T. Morishita, D. Okumura, and K. Kushiya, Improvment of V<sub>oc</sub> upward of 600mV/cell with CIGS-based absorber prepared by selenization/sulfurization, Proceedings of the 17<sup>th</sup> European Photovoltaic Solar Energy Conference, Munich, Germany (2001) 989-994

- D. Bonnet and H. Rabenhorst, New results on the development of a thin-film p-CdTe n-CdS heterojunction solar cell, Proceedings of the 9<sup>th</sup> IEEE Photovoltaic Specialists Conference, Silver Springs, Maryland (1972) 129-132

- 42. D. Cunningham, K. Davies, L. Grammond, E. Mopas, N. O'Connor, M. Rubcich, M. Sadeghi, D. Skinner, and T. Trumbly, *Large area Apollo<sup>TM</sup> module performance and reliability*, Proceedings of the 28<sup>th</sup> IEEE Photovoltaic Specialists Conference, Anchorage, Alaska (2000) 13-18

- 43. S. A. Ringel, A. W. Smith, M. H. MacDougal, and A. Rohatgi, *The effects of* CdCl<sub>2</sub> on the electronic properties of molecular-beam epitaxially grown CdTe/CdS heterojunction solar cells, Journal of Applied Physics **70** (1991) 881-889

- 44. B. E. McCandless and K. D. Dobson, *Processing options for CdTe thin film* solar cells, Solar Energy 77 (2004) 839-856

# Thin Film CdTe/CdS Solar Cells

# 3.1 Introduction

The potential of cadmium telluride (CdTe) for use as absorber in a solar cell has long been recognised, as with a bandgap of 1.45 eV it is close to the theoretical ideal that could produce devices up to 27% efficient [1]. Homojunction cells were first investigated to make use of the ability to produce both p and n-type CdTe, but efficiencies were limited to 6% [2] due to surface recombination arising from the strong absorption coefficient of the CdTe and the collecting junction being located near the surface. The first efficient polycrystalline thin film CdTe-based solar cells was p-Cu<sub>2</sub>Te/n-CdTe heterojunction and demonstrated a conversion efficiency of 6% [3]. However, due to instabilities associated with the Cu<sub>2</sub>Te layer, alternative p-type window layers were sought. Ultimately, this proved unsuccessful and consequently attention turned to device structures employing p-CdTe.

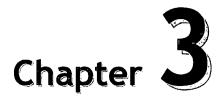

As a result, a *p*-CdTe/*n*-CdS heterojunction solar cell with 1% efficiency was fabricated in 1969 by evaporating CdS then CdTe films on a glass substrate coated with a transparent conductive oxide (TCO) [4]. This type of configuration is referred to as "superstrate" configuration and is shown in Figure 3-1. In 1972 an all thin film CdTe/CdS solar cell was reported by Bonnet and Rabenhorst [5] by evaporation of a

CdS layer over a CdTe absorber film, in "substrate" configuration. This device demonstrated an efficiency of 5% under 50 mW.cm<sup>-2</sup> illumination. In both "substrate" and "superstrate" configurations, light enters through the TCO and CdS films. In a superstrate cell, the TCO, CdS and CdTe layers are sequentially deposited onto a glass substrate. However, in a substrate configuration the CdTe film is typically deposited first onto a suitable metal substrate followed by the deposition of CdS and TCO.

In this chapter the functions and properties of each layer that constitutes the CdTe/CdS thin film solar cell are reviewed. In section 3.3, some of the growth techniques are described with particular emphasis on chemical vapour deposition, the deposition method used for the fabrication of the layers and devices investigated in this work. Then, the effects of the CdCl<sub>2</sub> post-growth treatment are detailed (section 3.4), followed by a review of defect chemistry in CdTe.

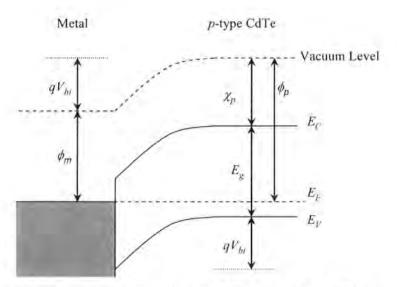

# 3.2 Solar Cell Structure

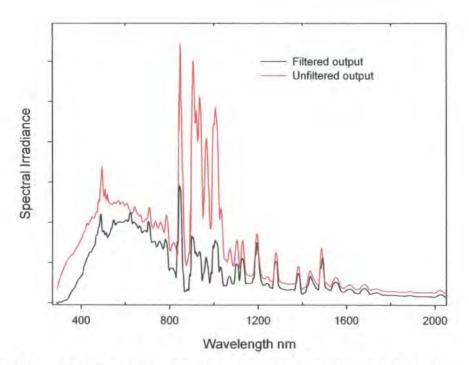

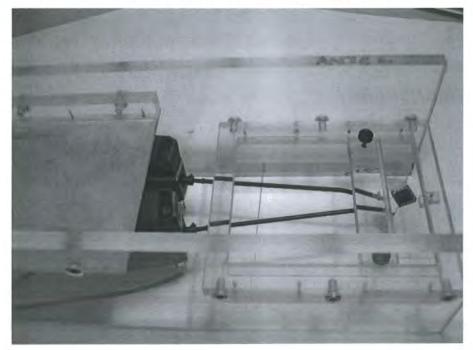

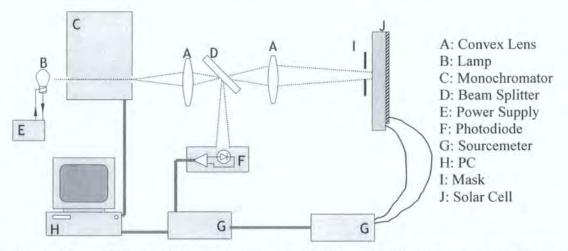

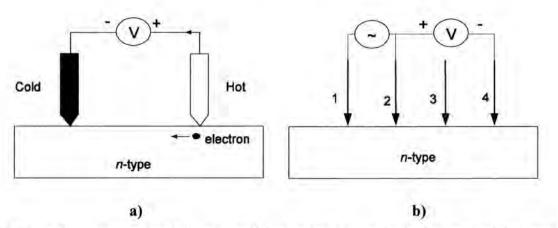

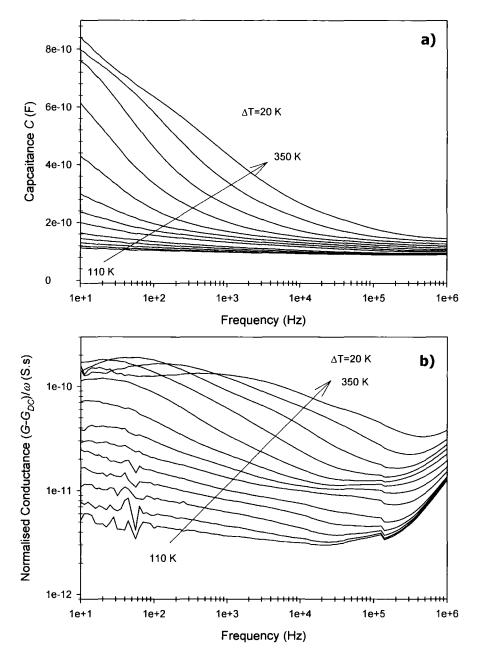

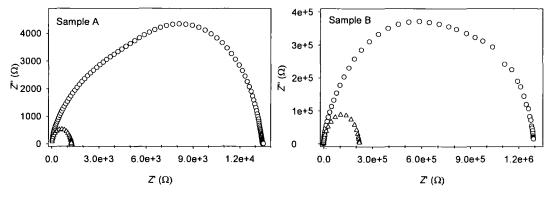

### 3.2.1 The substrate