#### **Durham E-Theses**

Development and modelling of a versatile active micro-electrode array for high density in-vivo and in-vitro neural signal investigation

CURRY, RICHARD, IAN

#### How to cite:

CURRY, RICHARD,IAN (2010) Development and modelling of a versatile active micro-electrode array for high density in-vivo and in-vitro neural signal investigation, Durham theses, Durham University. Available at Durham E-Theses Online: <a href="http://etheses.dur.ac.uk/232/">http://etheses.dur.ac.uk/232/</a>

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- ullet a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

# Development and modelling of a versatile active micro-electrode array for high density *in-vivo* and *in-vitro* neural signal investigation

Richard Ian Curry, M.Eng.

School of Engineering University of Durham

A Thesis presented for the degree of Doctor of Philosophy

April 2010

#### **Abstract**

The electrophysiological observation of neurological cells has allowed much knowledge to be gathered regarding how living organisms are believed to acquire and process sensation. Although much has been learned about neurons in isolation, there is much more to be discovered in how these neurons communicate within large networks. The challenges of measuring neurological networks at the scale, density and chronic level of non invasiveness required to observe neurological processing and decision making are manifold, however methods have been suggested that have allowed small scale networks to be observed using arrays of micro-fabricated electrodes. These arrays transduce ionic perturbations local to the cell membrane in the extracellular fluid into small electrical signals within the metal that may be measured.

A device was designed for optimal electrical matching to the electrode interface and maximal signal preservation of the received extracellular neural signals. Design parameters were developed from electrophysiological computer simulations and experimentally obtained empirical models of the electrode-electrolyte interface. From this information, a novel interface based signal filtering method was developed that enabled high density amplifier interface circuitry to be realised.

A novel prototype monolithic active electrode was developed using CMOS microfabrication technology. The device uses the top metallization of a selected process to form the electrode substrate and compact amplification circuitry fabricated directly beneath the electrode to amplify and separate the neural signal from the baseline offsets and noise of the electrode interface. The signal is then buffered for high speed sampling and switched signal routing. Prototype 16 and 256 active electrode array with custom support circuitry is presented at the layout stage for a 20  $\mu$ m diameter 100  $\mu$ m pitch electrode array. Each device consumes 26.4  $\mu$ W of power and contributes 4.509  $\mu$ V (rms) of noise to the received signal over a controlled bandwidth of 10 Hz - 5 kHz.

The research has provided a fundamental insight into the challenges of high density neural network observation, both in the passive and the active manner. The thesis concludes that power consumption is the fundamental limiting factor of high density integrated MEA circuitry; low power dissipation being crucial for the existence of the surface adhered cells under measurement. With transistor sizing, noise and signal slewing each being inversely proportional to the dc supply current and the large power requirements of desirable ancillary circuitry such as analogue-to-digital converters, a situation of compromise is approached that must be carefully considered for specific application design.

This thesis is dedicated to my father Roland Frederick Curry

The copyright of this thesis rests with the author.

No quotation from it should be published without their prior written consent and information derived from it should be acknowledged.

## Acknowledgements

I would like to thank Dr. Sherri Johnstone for stepping in as my supervisor towards the final stages of this project. It is unlikely that I would have succeeded without her invaluable help.

I would also like to express my thanks to Mark Rosamond and Dr. Andrew Gallant for helping me to perfect the microelectrode fabrication process for the experiments in chapters 6 & 7. Their assistance produced some fantastically reproducible 'merchandise' that gave me the means to identify the different capacitance mechanisms given by gold and platinum electrodes in saline.

I express my gratitude to Ian Hutchinson, Colin Wintrip, Neil Clarey and John Gibson of the school's technical staff for their assistance and advice during thesis work and the many other side projects during my time at Durham. I also wish to thank everyone in room E208 (the CES office) for their help and company during the PhD.

I would like to thank my parents, Roland and Margaret Curry for their endless support

This research was funded by a studentship from the Engineering and Physical Sciences Research Council (EPSRC) and a Cooperative Awards in Science and Engineering (CASE) award from the Centre of Excellence for Life Sciences (CELS) Newcastle-Upon-Tyne.

## Declaration

The work presented in this thesis is based on research carried out in the School of Engineering, University of Durham, UK. No part of this thesis has been submitted elsewhere for any other degree or qualification. The work is my own unless referenced to the contrary in the text.

## **Contents**

| Abstra  | act      |         |                                     | ii   |

|---------|----------|---------|-------------------------------------|------|

| Dedica  | ation    |         |                                     | iii  |

| Copyr   | right    |         |                                     | iv   |

| Ackno   | owledge  | ements  |                                     | v    |

| Declar  | ration   |         |                                     | vi   |

| List of | f Figure | es      |                                     | xvi  |

| List of | f Tables | S       |                                     | xxiv |

| 1       | Introd   | luction |                                     | 1    |

|         | 1.1      | Thesis  | Structure                           | 4    |

|         | 1.2      | Introdu | action to Neurophysiology           | 6    |

|         |          | 1.2.1   | Classification of Cells             | 7    |

|         |          | 1.2.2   | The Molecular Structure of the Cell | 9    |

|         |          | 1.2.3   | Cell Locomotion and Adhesion        | 11   |

|         |          | 1.2.4   | The Layout of the Cell              | 13   |

|   |       | 1.2.5 Other Important Cells                                  | 16 |

|---|-------|--------------------------------------------------------------|----|

|   |       | 1.2.6 Charge Manipulation for Communication                  | 17 |

|   |       | 1.2.6.1 Resting Potential of Cell Membrane                   | 18 |

|   |       | 1.2.6.2 Depolarisation as a Signalling Mechanism:            |    |

|   |       | The Action Potential                                         | 23 |

|   |       | 1.2.6.3 Propagation of the Action Potential                  | 25 |

|   |       | 1.2.6.4 The Influence of the Soma                            | 26 |

|   |       | 1.2.6.5 Myelinated Non Myelinated Axons                      | 26 |

|   |       | 1.2.6.6 Dendrites                                            | 29 |

|   |       | 1.2.7 Electrical Connections and Couples between Cells       | 29 |

|   | 1.3   | References                                                   | 30 |

| 2 | The l | Development of Neural Signal Recording Technology            | 32 |

|   | 2.1   | In Vitro and In Vivo Methods                                 | 33 |

|   | 2.2   | Recording Electrodes                                         | 34 |

|   |       | 2.2.1 Planar Electrodes and MEAs                             | 37 |

|   |       | 2.2.2 Non Planar Electrode Arrays                            | 41 |

|   | 2.3   | The Patch Clamp                                              | 43 |

|   |       | 2.3.1 The Micro-Array Patch Clamp                            | 46 |

|   | 2.4   | Active MEA Technologies                                      | 47 |

|   |       | 2.4.1 Neuron-Transistor Array                                | 53 |

|   | 2.5   | Optical Recording Methods                                    | 55 |

|   | 2.6   | Remarks                                                      | 56 |

|   | 2.7   | References                                                   | 58 |

| 3 | Anal  | ysis of the Passive and Active Micro Electrode Array Systems | 68 |

|   | 3.1   | Analysis of the MEA System                                   | 59 |

|   |       | 3.1.1 The MEA Measurement Circuit                            | 59 |

|   |       | 3.1.2 Front End Signal Conditioning                          | 72 |

|   |       | 3.1.3 Further Conditioning: The Back End                     | 73 |

|   | 3.2   | The MEA Interconnection Problem                              | 74 |

|   |      | 3.2.1  | Electrica   | al Limitations of the MEA                | /5  |

|---|------|--------|-------------|------------------------------------------|-----|

|   |      |        | 3.2.1.1     | The Source Impedance                     | 76  |

|   |      |        | 3.2.1.2 7   | The Track Resistance and Parasitic Shunt |     |

|   |      |        | I           | mpedance                                 | 81  |

|   |      |        |             |                                          |     |

|   |      | 3.2.2  | Track ar    | nd Cabling Noise                         | 85  |

|   |      |        | 3.2.2.1     | Thermal Noise                            | 86  |

|   |      |        | 3.2.2.2     | Shot and Flicker Noise                   | 88  |

|   |      |        | 3.2.2.3     | Electromagnetic Noise Sources            | 89  |

|   |      |        | 3.2.2.4     | Power Supply Noise                       | 91  |

|   |      |        | 3.2.2.5     | Noise Summary                            | 92  |

|   | 3.3  | Analy  | sis of the  | Interconnection Bottleneck               | 93  |

|   | 3.4  | Impro  | vement by   | y Integration                            | 96  |

|   |      | 3.4.1  | Integrati   | on Area Issues                           | 97  |

|   | 3.5  | Propo  | sed Active  | e MEA Design                             | 104 |

|   |      | 3.5.1  | Front En    | nd Design                                | 105 |

|   | 3.6  | Summ   | nary        |                                          | 109 |

|   | 3.7  | Refere | ences       |                                          | 109 |

| 4 | Deve | lopmen | t of an Eld | ectrical Neuron Model for Computer       |     |

|   | Simu | lation |             | •                                        | 112 |

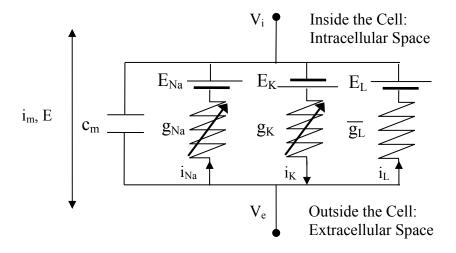

|   | 4.1  | The A  | ctive Mer   | mbrane                                   | 114 |

|   |      | 4.1.1  | The Hoc     | lgkin and Huxley Model                   | 115 |

|   |      | 4.1.2  | Characte    | erising the Ionic Conductance            | 118 |

|   |      | 4.1.3  | Summar      | у                                        |     |

|   | 4.2  | Electr | ical Mode   | el of the Neuron                         |     |

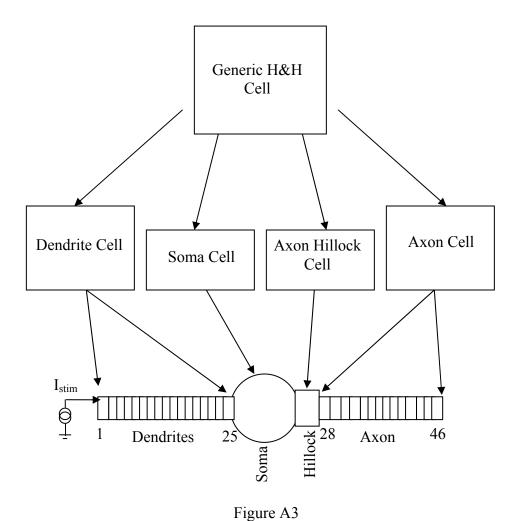

|   |      | 4.2.1  | The Con     | npartment Structure                      | 122 |

|   |      | 4.2.2  | Electrica   | al Connection to the Extracellular Bulk. | 126 |

|   |      | 4.2.3  | Extracel    | lular Nodal Conductivity                 | 128 |

|   |      | 4.2.4  |             | upling to the Recording Electrode        |     |

|   |      |        |             |                                          |     |

|   |       | 4.2.4.1   | Neural Signal Measurements in the Absence of $R_{\text{seal}}\dots$              | 133   |

|---|-------|-----------|----------------------------------------------------------------------------------|-------|

|   | 4.3   | The El    | ectrode Model                                                                    | 137   |

|   | 4.4   | The In    | put Front End                                                                    | 138   |

|   |       | 4.4.1 E   | Electrode Interconnection Parasitics                                             | 139   |

|   | 4.5   | Develo    | oping the Model for SPICE                                                        | 141   |

|   |       | 4.5.1     | Modelling the Ionic Conductance in SPICE                                         | 142   |

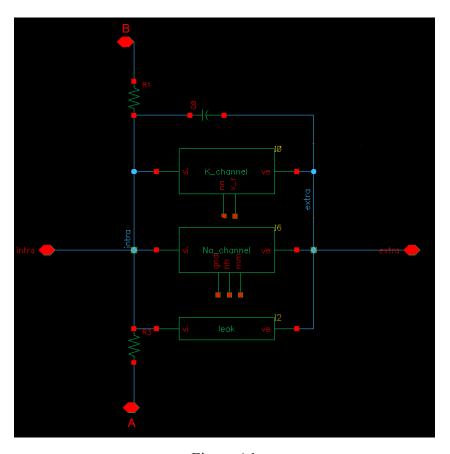

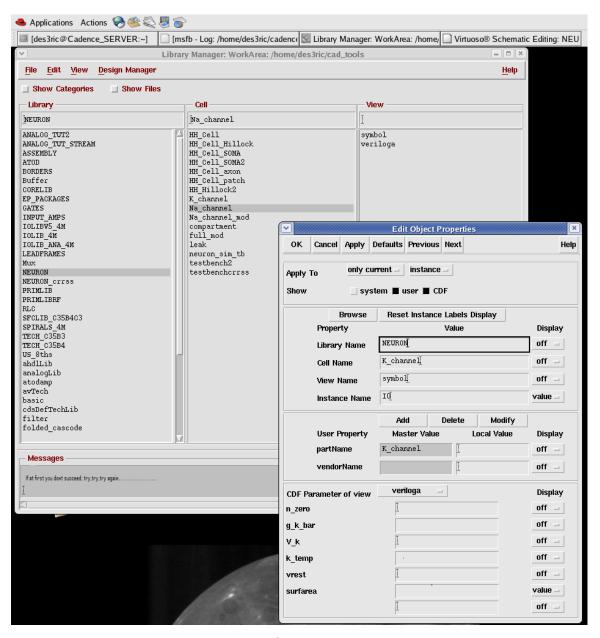

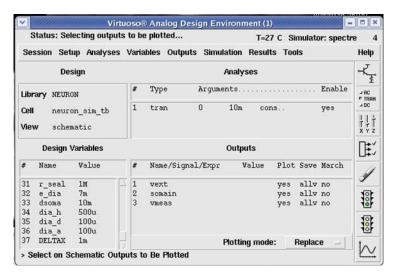

|   |       | 4.5.2     | The SPICE Circuit Layout                                                         | 142   |

|   | 4.6   | Conclu    | asion                                                                            | 146   |

|   | 4.7   | Refere    | nces                                                                             | 146   |

| 5 | Analy | sis of th | ne Model Neuron                                                                  | 150   |

|   | 5.1   | Valida    | tion of the Model                                                                | 151   |

|   |       | 5.1.1     | Comparison to the Hodgkin Huxley Signal Shape                                    | 151   |

|   |       | 5.1.2     | Verification of TMAP Propagation through the Model                               | 152   |

|   |       | 5.1.3     | Relationship between CAP and TMAP                                                | 154   |

|   |       |           | 5.1.3.1 The Critical Point for NLS CAP Signals                                   | 154   |

|   |       |           | 5.1.3.2 The Critical Point for PLS CAP Signals                                   | 159   |

|   | 5.2   | Calibra   | ation of the Model                                                               | 162   |

|   |       | 5.2.1     | Selection of Published Extracellular Signals for                                 |       |

|   |       |           | Comparison                                                                       | . 165 |

|   |       | 5.2.2     | Comparison with Extracellular Soma Recordings from                               |       |

|   |       |           | Helisoma B19, Hirudo Retzius and Aplysia MCC                                     |       |

|   |       |           | Neurons                                                                          | 166   |

|   |       | 5.2.3     | Analysis of Simulated Extracellular Signals                                      | 170   |

|   | 5.3   | Investi   | gation of Simulated Action Potentials                                            | . 171 |

|   |       | 5.3.1     | Effect of Soma Diameter and $R_{\text{seal}}\ \text{upon CAP}\ \text{Amplitude}$ | . 172 |

|   |       | 5.3.2     | Effect of Soma Diameter and $R_{\text{seal}}$ upon the Spectral                  |       |

|   |       |           | Frequencies of the CAP.                                                          | 173   |

|   |       | 5.3.3     | Thermal Noise within the Cleft                                                   | 175   |

|   | 5 4   | Offset    | s and Loading Errors from the Measurement Circuit                                | 181   |

|   |       | 5.4.1     | The Electrode                                                  |

|---|-------|-----------|----------------------------------------------------------------|

|   |       |           | 5.4.1.1 Electrode Impedance                                    |

|   |       |           | 5.4.1.2 Electrode-Electrolyte Interface Potential 183          |

|   |       | 5.4.2     | Parasitic Losses                                               |

|   |       |           | 5.4.2.1 Lumped Shunt Resistance                                |

|   |       |           | 5.4.2.2 Lumped Shunt Capacitance                               |

|   |       |           | 5.4.2.3 Amplifier Input Bias Current and Input                 |

|   |       |           | Load Impedance                                                 |

|   |       | 5.4.3     | Input Filter Circuitry                                         |

|   | 5.5   | Applic    | eation of Simulated data to the Design of an                   |

|   |       | Optim     | ised ASIC190                                                   |

|   |       | 5.5.1     | Input Impedance                                                |

|   |       | 5.5.2     | Amplifier Bandwidth and Signal Sampling Frequency 192          |

|   |       | 5.3.3     | Amplifier Gain                                                 |

|   | 5.6   | Summ      | ary                                                            |

|   | 5.7   | Refere    | ences                                                          |

|   |       |           |                                                                |

| 6 | Prop  | erties of | the Electrode Interface for Pt and Au in Physiological         |

|   | Salin | e         | 197                                                            |

|   | 6.1   | Charac    | cterising the DC Electrical Properties of Au and Pt            |

|   |       | Electro   | odes in Physiological Saline                                   |

|   |       | 6.1.1     | Electrode – Electrolyte Interface Potential 199                |

|   |       | 6.1.2     | Charge Transfer Reactions                                      |

|   |       | 6.1.3     | Identification of Reactions and Sorptions at Pt and            |

|   |       |           | Au Electrodes in Physiological Saline within the               |

|   |       |           | Water Window                                                   |

|   |       |           | 6.1.3.1 Charge Transfer Regions for Pt                         |

|   |       |           | 6.1.3.2 Charge Transfer Reactions for Au 206                   |

|   |       | 6.1.4     | DC Charge Transfer Resistance at Equilibrium 209               |

|   | 6.2   | Charac    | cterising the AC Electrical Properties of Au and Pt Electrodes |

|   |       | in Phy    | ysiological Saline                                             |

|   |      | 6.2.1   | The Double Layer                                          |   |

|---|------|---------|-----------------------------------------------------------|---|

|   |      | 6.2.2   | The Helmholtz Double Layer                                |   |

|   |      | 6.2.3   | The Gouy-Chapman Model                                    |   |

|   |      | 6.2.4   | The Stern Model                                           |   |

|   |      | 6.2.5   | Frequency Dependence of the Interfacial Impedance 214     |   |

|   |      | 6.2.6   | Comparison of Published Data for AC Electrical Properties |   |

|   |      |         | of Au and Pt in Physiological Saline Solutions            |   |

|   |      |         | 6.2.6.1 Collected Published Data                          |   |

|   |      |         | 6.2.6.2 Discussion                                        |   |

|   | 6.3  | Noise   | at the Interface                                          |   |

|   | 6.4  | Discus  | ssion: A Proposed Method to Remove the DC Half Cell       |   |

|   |      | Potent  | tial and Low Frequency Drift                              |   |

|   |      | 6.4.1   | Proposed Electrode Model                                  |   |

|   |      | 6.4.2   | Removal of the DC Half Cell Potential                     |   |

|   |      | 6.4.3   | Exploiting the Interface Capacitance for Removal of Low   |   |

|   |      |         | Frequency Interference                                    |   |

|   | 6.5  | Refere  | ences                                                     |   |

| 7 | Exne | riments | l Investigation into Thin Film Pt and Au Electrodes for a |   |

| , | -    |         | oducible CAP Signal Amplifier Area Reduction Method 23    | 4 |

|   | 7.1  |         | Film Electrodes                                           |   |

|   | 7.1  |         | Surface Roughness of Thin Film Electrodes                 |   |

|   | 7.2  |         | ical Properties of Pt and Au Thin Film Electrodes         |   |

|   | 1.2  | 7.2.1   | The DC Mode                                               |   |

|   |      | 7.2.1   | 7.2.1.1 Measured Values of E <sup>0</sup>                 |   |

|   |      |         | 7.2.1.2 The DC interface Resistance $R_{ct}$ near $E^0$   |   |

|   |      | 7.2.2   | The AC Mode                                               |   |

|   |      | 1.2.2   | 7.2.2.1 Method                                            |   |

|   |      |         | 7.2.2.1 Method                                            |   |

|   |      |         | 7.2.2.2 Results                                           |   |

|   |      | 722     |                                                           |   |

|   |      | 7.2.3   | Processing Issues with Pt                                 |   |

|   |      | 7.2.4    | Modelling                                                 | 249 |

|---|------|----------|-----------------------------------------------------------|-----|

|   |      | 7.2.5    | Conclusion                                                | 252 |

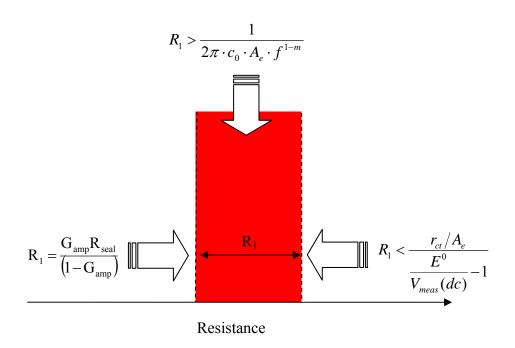

|   | 7.3  | Interfa  | ce Circuit Design using Au Thin Film Electrodes           | 254 |

|   |      | 2.3.1 C  | Circuit Design Procedure                                  | 255 |

|   | 7.4  | Verifyi  | ing the Electrical Properties of the Interface as Part of | an  |

|   |      | Input F  | Filter Circuit                                            | 256 |

|   |      | 7.4.1    | Electrode Scaling                                         | 257 |

|   |      | 7.4.2    | Verifying the Removal of the Half Cell Potential          | 261 |

|   |      |          | 7.4.2.1 Results                                           | 263 |

|   |      |          | 7.4.2.2 Discussion                                        | 264 |

|   |      | 7.4.3    | The Filter Response                                       | 265 |

|   |      | 7.4.4    | Experimental Filter Response                              | 267 |

|   |      | 7.4.5    | Discussion                                                | 270 |

|   | 7.5  | Discus   | sion                                                      | 271 |

|   | 7.6  | Summa    | ary                                                       | 273 |

|   | 7.7  | Refere   | nces                                                      | 274 |

|   |      |          |                                                           |     |

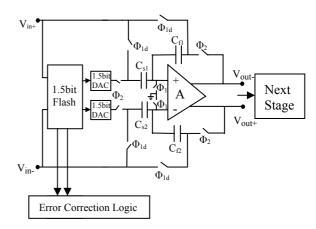

| 8 | Fron | t End AS | SIC Design                                                | 276 |

|   | 8.1  | Propos   | ed Structure                                              | 277 |

|   |      | 8.1.1    | Input Device Structure                                    | 277 |

|   |      | 8.1.2    | General IC Floor Plan                                     | 280 |

|   | 8.2  | Design   | Constraints and Topology Selection                        | 281 |

|   |      | 8.2.1    | Summary of Amplifier Design Requirements                  | 281 |

|   |      | 8.2.2    | Design Parameters                                         | 282 |

|   |      | 8.2.3    | Amplifier Architecture Selection                          | 285 |

|   | 8.3  | Circuit  | Design                                                    | 285 |

|   |      | 8.3.1    | Noise                                                     | 287 |

|   |      | 8.3.2    | Closed Loop Stability and Input Node Biasing              | 292 |

|   |      |          | 8.3.2.1 Upper Bandwidth Limiting                          | 293 |

|   |      | 8.3.3    | Output Current Slewing                                    | 295 |

|   |      | 8.3.4    | Resolving the Input Coupling Resistor                     | 296 |

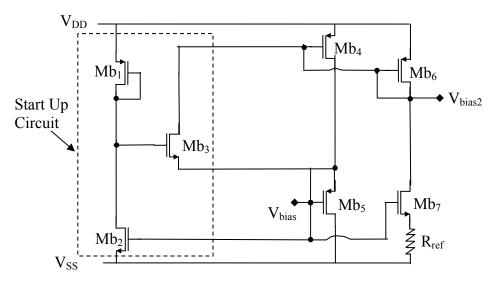

|    |       | 8.3.5 Biasing                                | 7 |

|----|-------|----------------------------------------------|---|

|    | 8.4   | Simulation Based Design                      | ) |

|    | 8.5   | In-Situ Circuit Simulation                   | 3 |

|    | 8.6   | Circuit Layout                               | 1 |

|    | 8.7   | Discussion                                   | 7 |

|    | 8.8   | Summary                                      | 2 |

|    | 8.9   | References                                   | 2 |

| 9  | Fron  | End Development for System on Chip (SoC) 314 | 4 |

|    | 9.1   | Amplifier Channel Handling                   | 5 |

|    |       | 9.1.1 Verifying Track Parasitic Capacitance  | 5 |

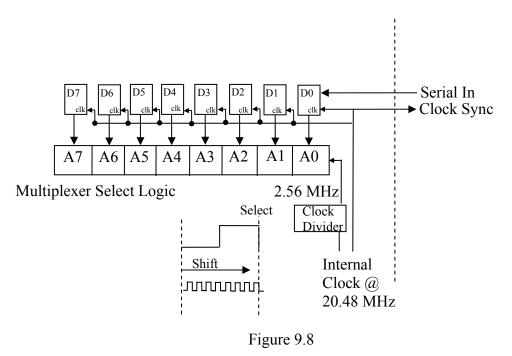

|    |       | 9.1.2 The Multiplexer Circuit                | 7 |

|    |       | 9.1.3 Pre-Multiplexer Buffer                 | ) |

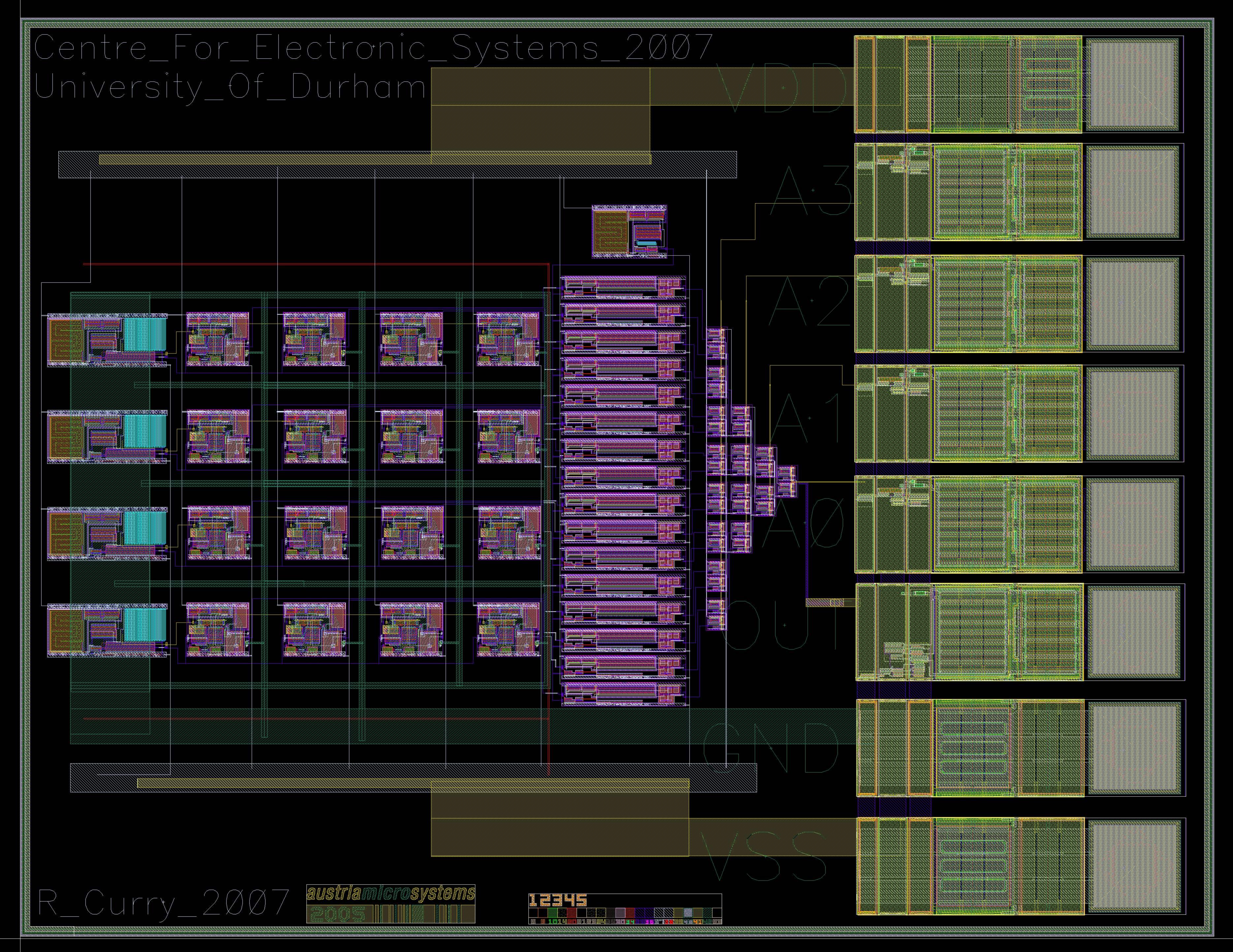

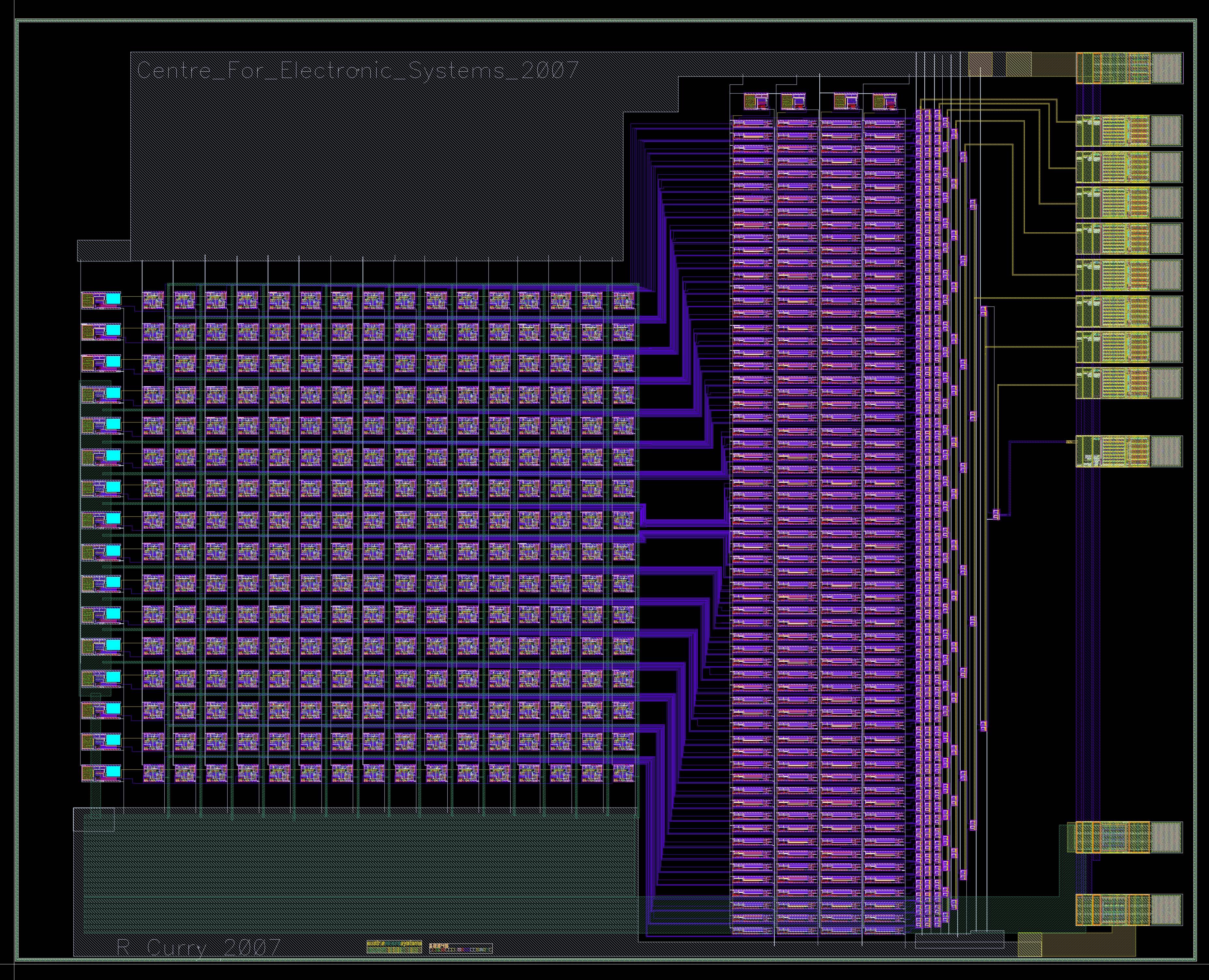

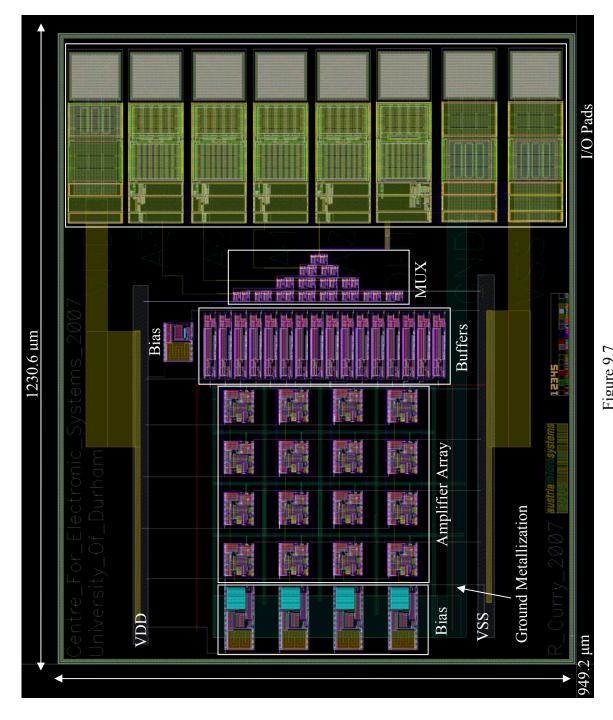

|    | 9.2   | Front End Layout Assembly                    | 2 |

|    | 9.3   | Forming the Ground Electrode Network         | 5 |

|    | 9.4   | A 256 Electrode Test Structure               | 5 |

|    | 9.5   | Further Work                                 | 5 |

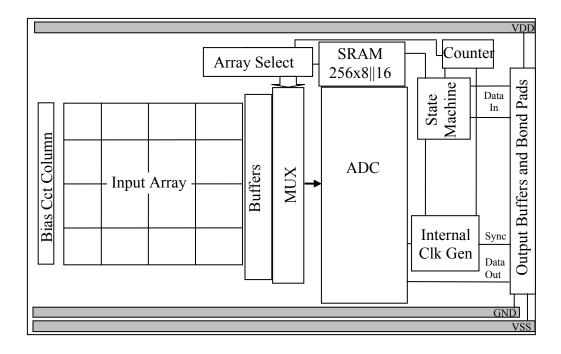

|    |       | 9.5.1 Analogue-to-Digital Conversion         | 5 |

|    |       | 9.5.2 Programmable Array Access Scheme       | ) |

|    |       | 9.5.3 Chip Floorplan                         | 1 |

|    |       | 9.5.4 Packaging                              | 3 |

|    |       | 9.5.5 The Effects of Power Dissipation       | 7 |

|    | 9.6   | Conclusion                                   | ) |

|    | 9.7   | References                                   | ) |

| 10 | Thesi | s Overview and Conclusion 341                | 1 |

| Appendix    | A                                        |     |

|-------------|------------------------------------------|-----|

| VerilogA N  | Model and Structure for Cadence Virtuoso | 351 |

| 1           | Hodgkin and Huxley Model                 | 351 |

| 2           | Model Cell Structure in SPICE            | 355 |

| Appendix    | В                                        |     |

| Electrode . | Array Fabrication Materials              | 360 |

| Appendix    | $\mathbf{c}$                             |     |

| Electrode . | Array Fabrication Recipes                | 361 |

| Appendix    | D                                        |     |

| IEEE Prin   | ne Publication                           | 363 |

| Appendix    | E                                        |     |

| ASIC Prot   | otype Arrays for Test                    | 368 |

## **List of Figures**

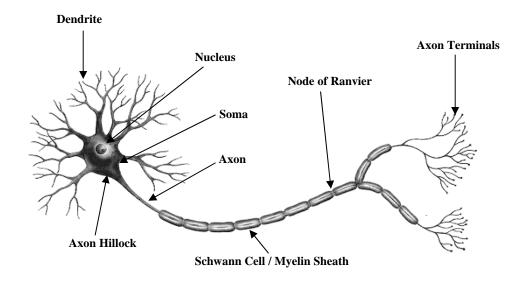

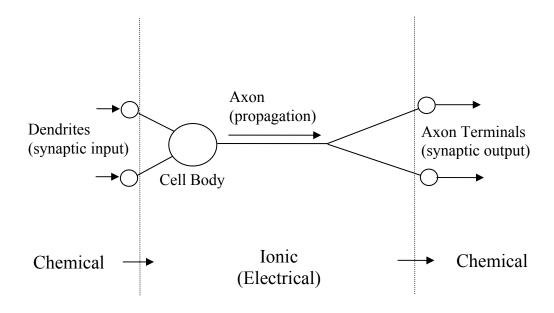

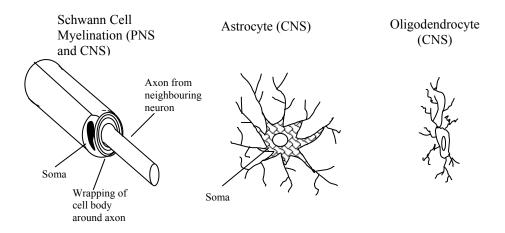

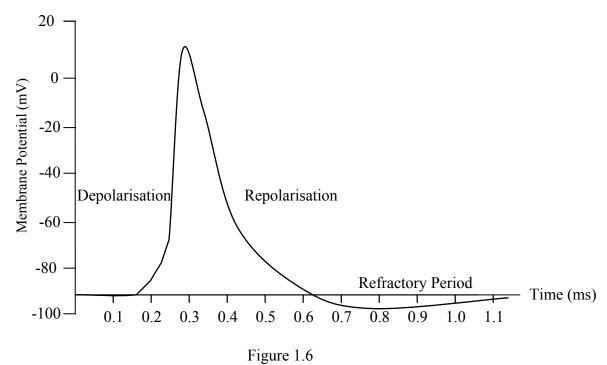

| 1.1 | Illustration of generic cell dimensions and a selection of CNS neuron   |    |

|-----|-------------------------------------------------------------------------|----|

|     | cell types                                                              | 9  |

| 1.2 | Arrangement of the lipid bi-layer                                       | 11 |

| 1.3 | A typical neuron                                                        | 14 |

| 1.4 | The basic mechanism of cellular communication                           | 15 |

| 1.5 | Illustrating the form of schwann cells and neuroglia                    | 17 |

| 1.6 | Typical Shape of an Action Potential                                    | 24 |

| 1.7 | The sodium cycle theory of membrane depolarisation and the potassium    |    |

|     | cycle theory of aided repolarisation                                    | 25 |

| 1.8 | Diagram of action potential propagation mechanism in (a) non-myelinated |    |

|     | and (b) myelinated fibres                                               | 28 |

| Cha | apter 2                                                                 |    |

| 2.1 | The four main branches of electrophysiological research                 | 33 |

| 2.2 | The use of a glass micropipette for intracellular potential measurement | 35 |

| 2.3 | Illustration of the voltage clamp measurement configuration             | 36 |

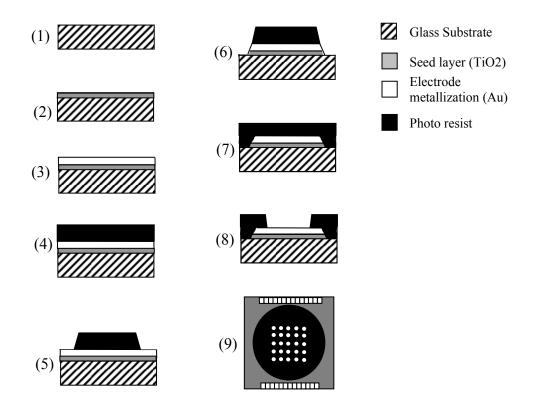

| 2.4 | Cross sectional illustration of basic photolithographic process         | 39 |

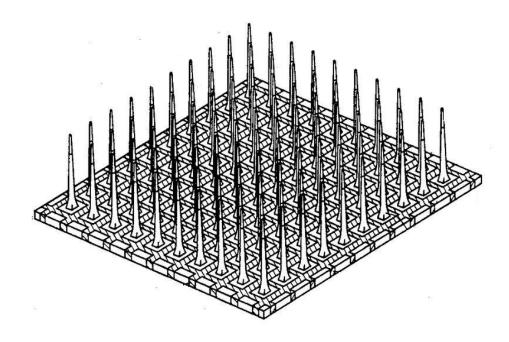

| 2.5 | The Utah Array: Diagram taken from Richard A. Normann's                 |    |

|     | patent application                                                      | 43 |

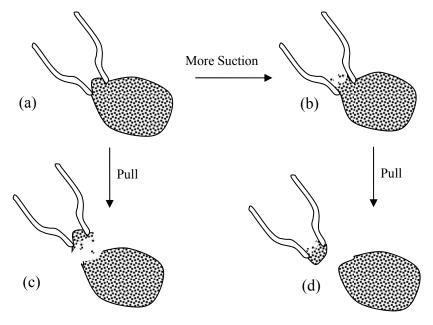

| 2.6  | The attachment of the tip of a micropipette to a cell in the four patch       |    |

|------|-------------------------------------------------------------------------------|----|

|      | clamp arrangements; forming the Giga Ohm seal                                 | 44 |

| 2.7  | Illustrations of two current topologies for on chip patch clamp techniques    | 46 |

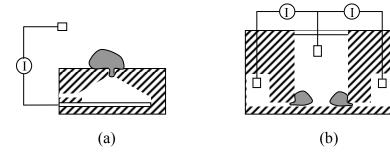

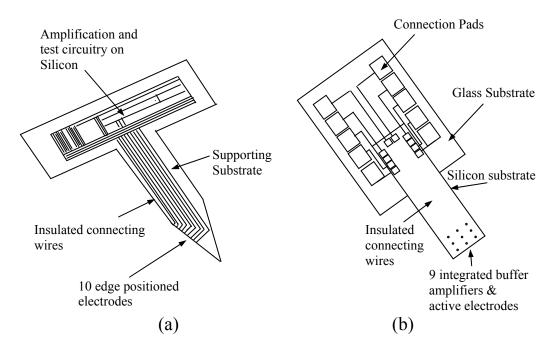

| 2.8  | Illustrations of the early active MEA Architectures offered by                |    |

|      | (a) Wise and Najafi and (b) Jobling et al                                     | 48 |

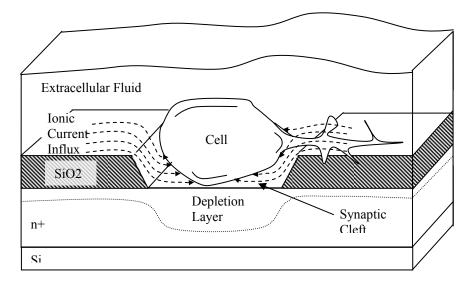

| 2.9  | Fromherz' neuron-silicon junction                                             | 53 |

| Cha  | apter 3                                                                       |    |

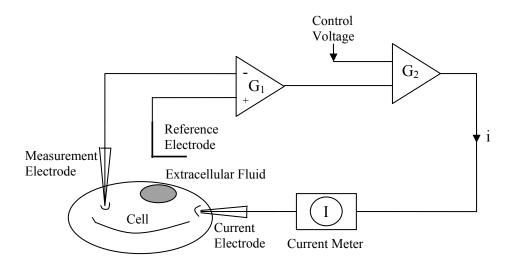

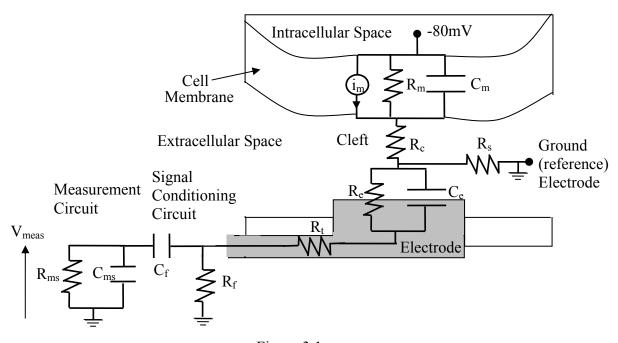

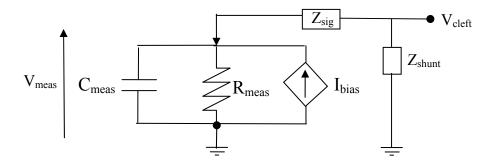

| 3.1  | Typical circuit diagram for the extracellular recording of neural signals     | 69 |

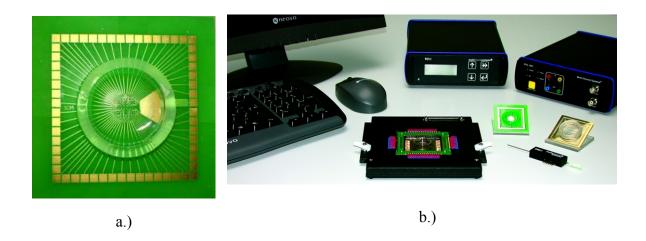

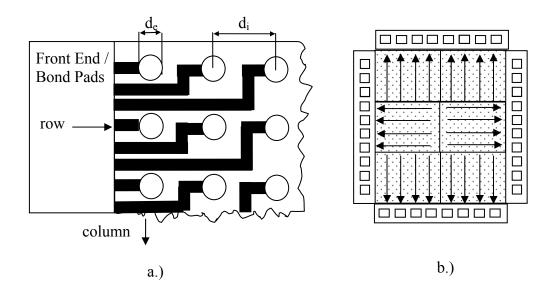

| 3.2  | a.) A commercial passive MEA with 60 gold electrodes wired to bond            |    |

|      | pads outside of the extracellular chamber. b.) photograph of a                |    |

|      | commercial MEA system                                                         | 71 |

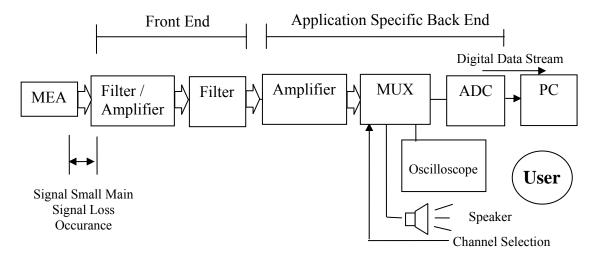

| 3.3  | Overall MEA recording system from the microelectrode to the end user,         |    |

|      | showing the classification of front end and back end                          | 72 |

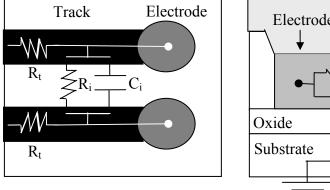

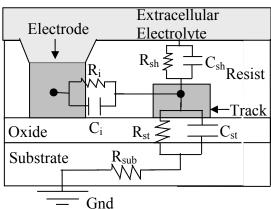

| 3.4  | Track parasitics of the MEA                                                   | 75 |

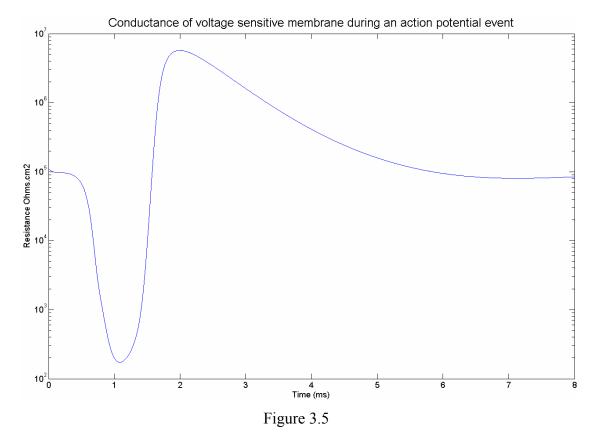

| 3.5  | Membrane resistance during an action potential calculated using               |    |

|      | computer simulation of Hodgkin and Huxley model                               | 77 |

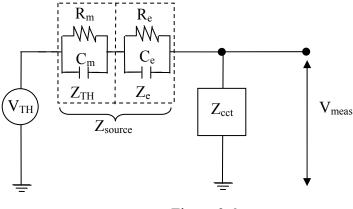

| 3.6  | Reduced component equivalent circuit of the neuron-measurement                |    |

|      | circuit interface                                                             | 79 |

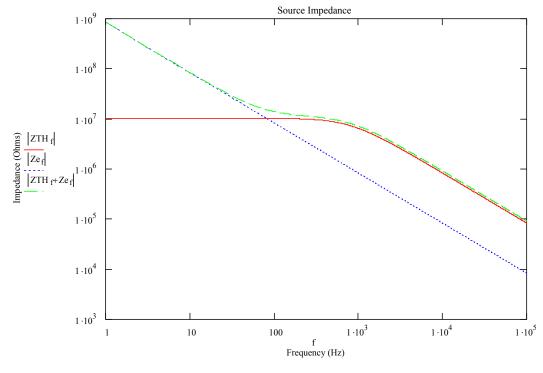

| 3.7  | Component parts of frequency dependent source impedance Z <sub>TH</sub> (red) |    |

|      | and ZE (blue) and their combined value (green) for a 50 µm diameter cell-     |    |

|      | electrode interface                                                           | 80 |

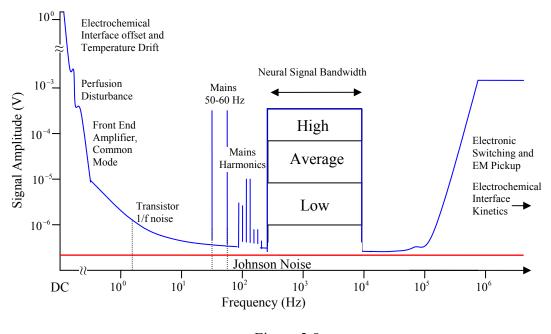

| 3.8  | Illustrative summary of the many noise sources that may affect the MEA        |    |

|      | and AMEA devices                                                              | 92 |

| 3.9  | MEA interconnection diagram                                                   | 94 |

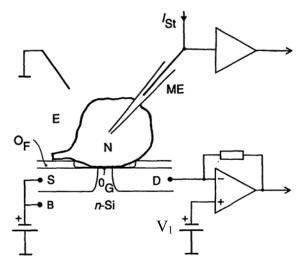

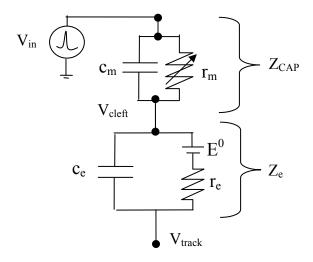

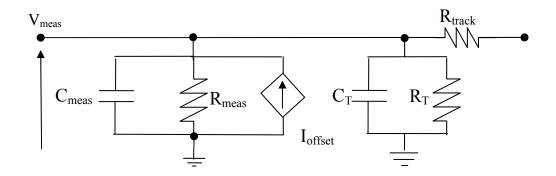

| 3 10 | The Measurement circuit for the Fromherz method                               | 10 |

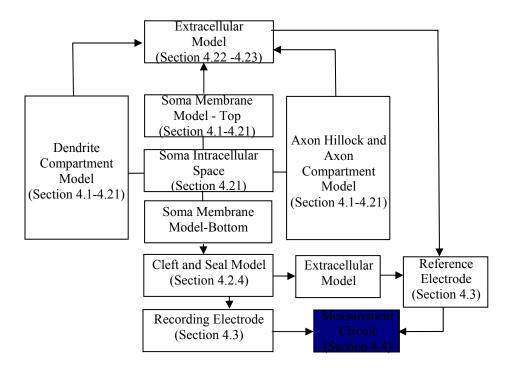

| 4.1   | Overview of the <i>in vitro</i> planar microelectrode model including                                                      |         |

|-------|----------------------------------------------------------------------------------------------------------------------------|---------|

|       | corresponding chapter sections for each modelled component                                                                 | 113     |

| 4.2   | Electrical equivalent circuit of the cell membrane                                                                         | 116     |

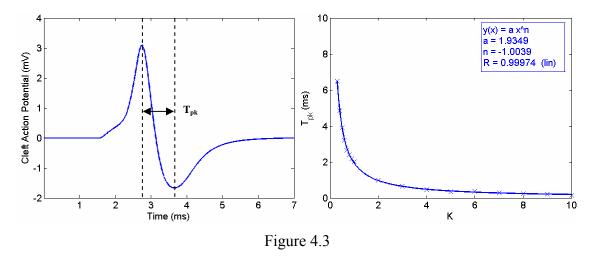

| 4.3   | Relationship between K and peak to peak time $T_{pk} \dots \dots$                                                          | 120     |

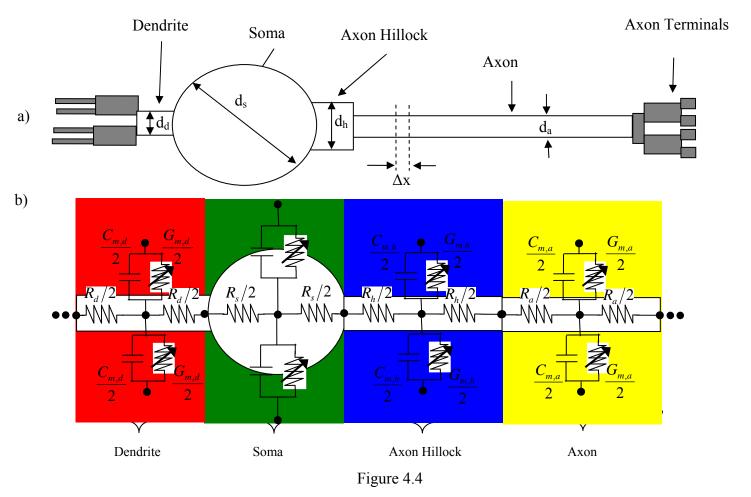

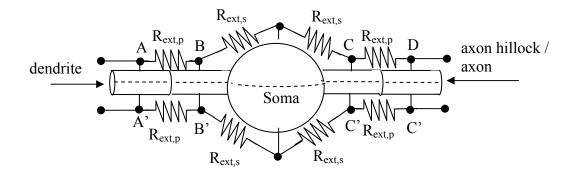

| 4.4   | Diagram of the neuron model                                                                                                | 124     |

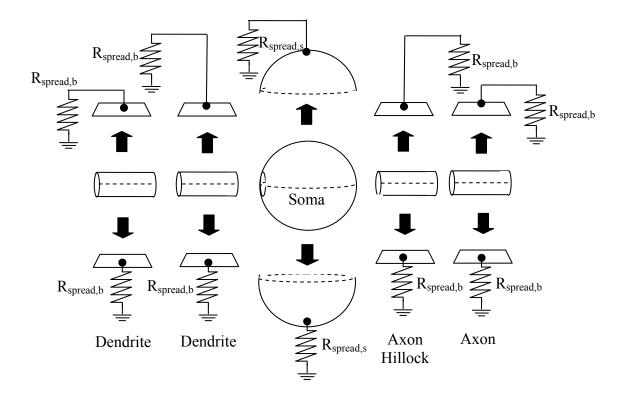

| 4.5   | Expanded view of the neuron model showing the use of the hemispherical                                                     |         |

|       | and rectangular spreading resistances to represent the electrical connection                                               |         |

|       | between the neuron compartment nodes to the bulk solution                                                                  | 127     |

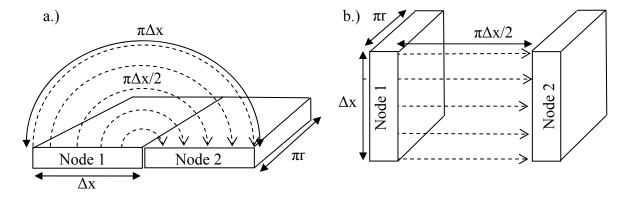

| 4.6   | Approximation of extracellular nodal current path between two adjacent                                                     |         |

|       | nodes                                                                                                                      | 129     |

| 4.7   | The extracellular connectivity between the compartmental nodes                                                             | 130     |

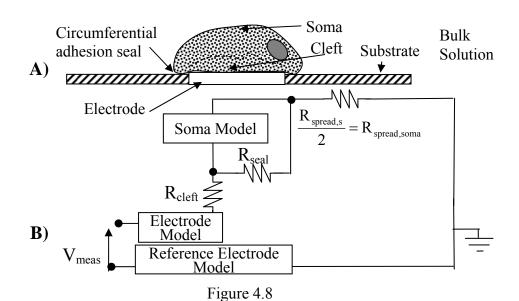

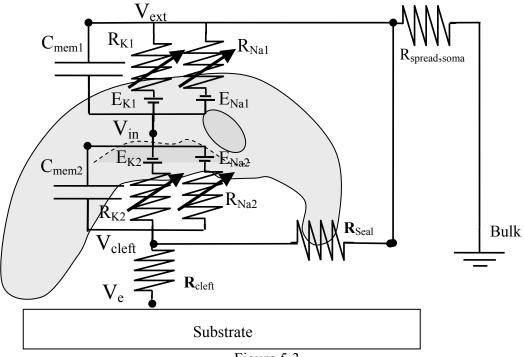

| 4.8   | A) Schematic of soma - electrode interface. B) Lumped electrical model                                                     |         |

|       | of extracellular microelectrode recording                                                                                  | 131     |

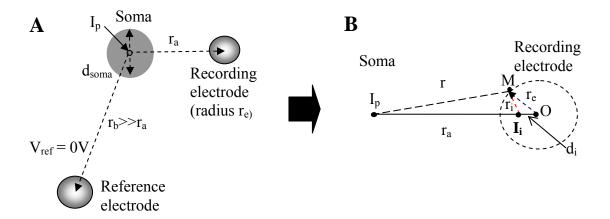

| 4.9 . | Illustration of A. The physical model of the soma and the electrodes                                                       |         |

|       | with the soma membrane current modelled as a point source, and B. the me                                                   | thod of |

|       | images model showing $\boldsymbol{I}_{\boldsymbol{p}}$ with its image source $\boldsymbol{I}_{i}$ placed within the volume | of the  |

|       | spherical recording electrode                                                                                              | 134     |

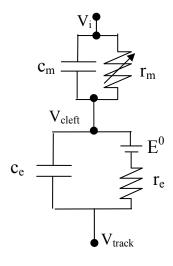

| 4.8   | Circuit implementation of the non-contact model                                                                            | 138     |

| 4.9   | The electrode model showing the unit area capacitances                                                                     | 135     |

| 4.10  | Input load model for measurement circuit                                                                                   | 139     |

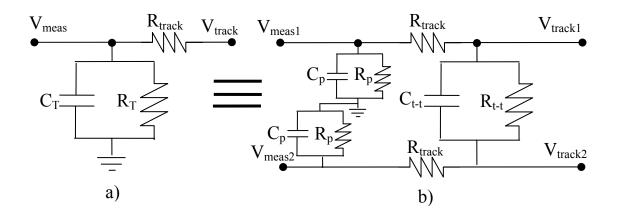

| 4.11  | Track Parasitics: a) lumped model for single track, b) breakdown                                                           |         |

|       | of contributing paths                                                                                                      | 140     |

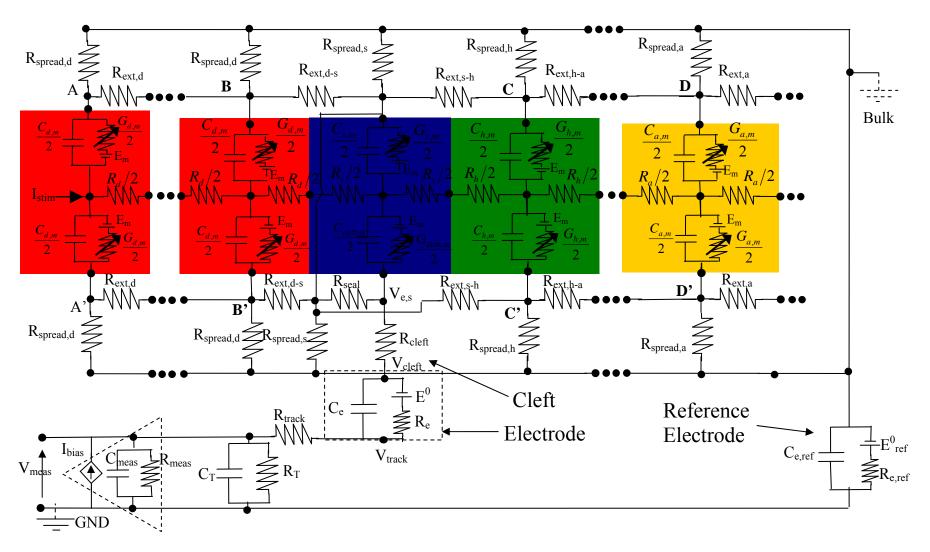

| 4.12  | The complete circuit model used in SPICE simulation                                                                        | 145     |

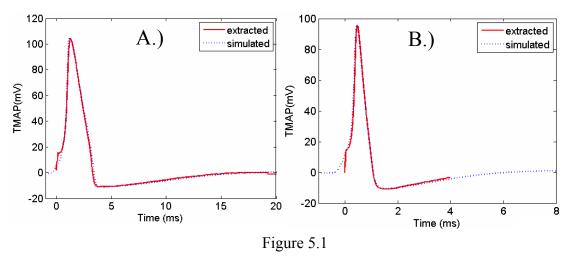

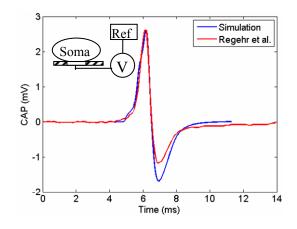

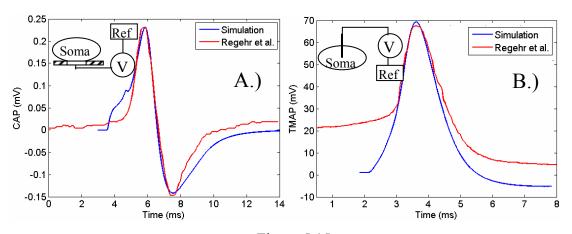

| 5.1  | Comparison of SPICE Membrane simulation with original numerical                            |     |

|------|--------------------------------------------------------------------------------------------|-----|

|      | simulation of Hodgkin and Huxley for: A.) 6.3°C and B.) 18.5 °C                            | 152 |

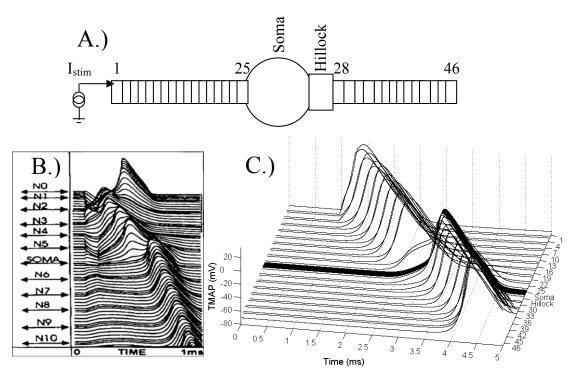

| 5.2  | Comparison of TMAP propagation through the neuron model                                    | 153 |

| 5.3  | The neuron-cleft circuit                                                                   | 155 |

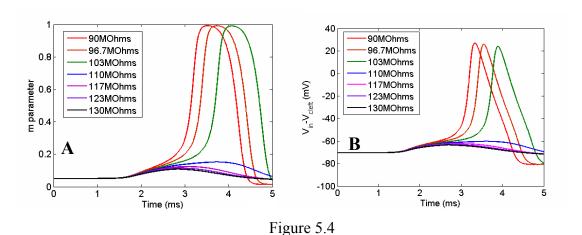

| 5.4  | A.) Activation of the m parameter and . B.) the TMAP produced for a                        |     |

|      | range of R <sub>seal</sub> values around the critical point for the Hodgkin Huxley         |     |

|      | model at 6.3 °C                                                                            | 156 |

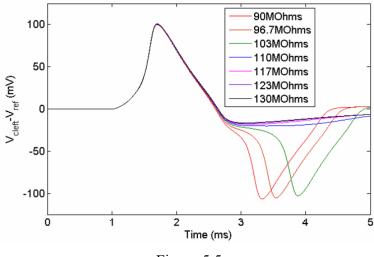

| 5.5  | Anomalous CAP signal due to the value of R <sub>seal</sub> being close to the critical     |     |

|      | point                                                                                      | 157 |

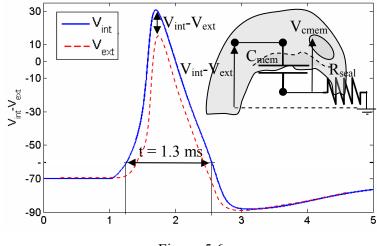

| 5.6  | Simulated intracellular potential $V_{\text{int}}\text{at}$ soma due to propagating TMAP   | 157 |

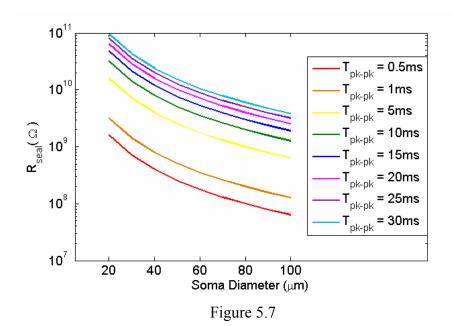

| 5.7  | Critical values of $R_{\text{seal}}$ for soma diameters between 20 $\mu m$ and 100 $\mu m$ |     |

|      | and action potential durations of 0.5 ms to 30 ms                                          | 159 |

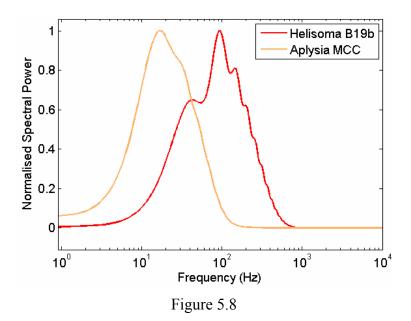

| 5.8  | Normalised TMAP spectral power from the Helisoma B19 neuron                                |     |

|      | and Aplysia MCC neuron                                                                     | 161 |

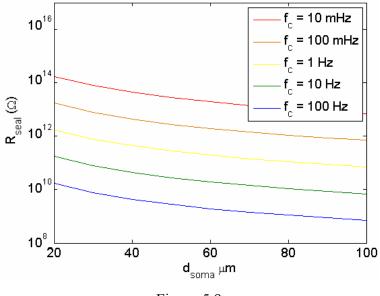

| 5.9  | Critical values of $R_{\text{seal}}$ for PLS CAP for soma diameters between 20 $\mu m$     |     |

|      | and 100 μm                                                                                 | 161 |

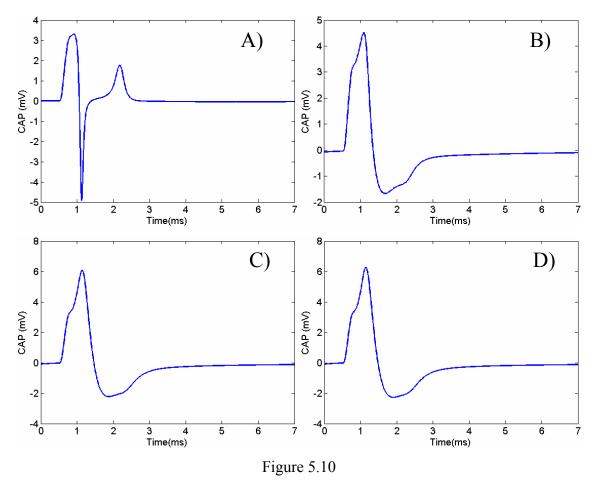

| 5.10 | CAP signals from the Hodgkin and Huxley model with varying values                          |     |

|      | of $g_{Na}$ and $g_{K}$                                                                    | 163 |

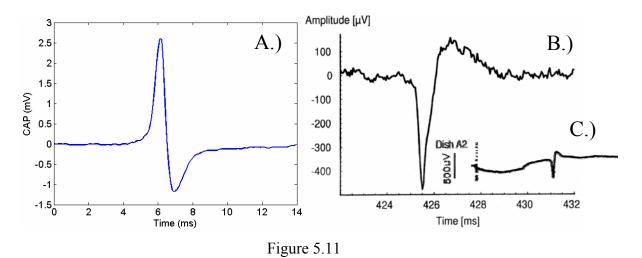

| 5.11 | A.) The positive first spike CAP. B.) and C.) the negative first spike                     |     |

|      | CAP. Data taken from Regehr et al and Heer et al                                           | 164 |

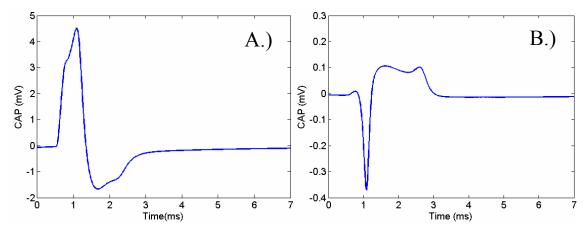

| 5.12 | Simulated PLS and NLS signals                                                              | 16: |

| 5.13 | Real signals from Helisoma B19 neuron compared with simulated                              |     |

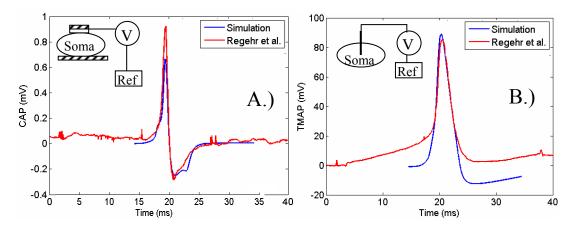

|      | signals from model: A.) CAP and B.) TMAP                                                   | 167 |

| 5.14 | Real CAP signal for Helisoma B19 neuron compared with simulated                            |     |

|      | signals from model                                                                         | 168 |

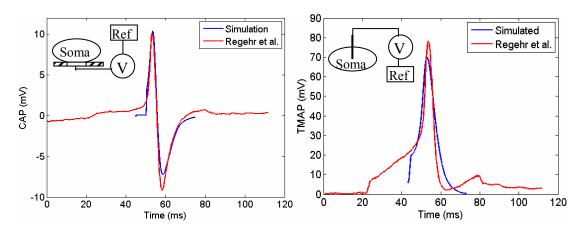

| 5.15 | Real signals for Hirudo Retzius neuron compared with simulated signals                     |     |

|      | from model                                                                                 | 168 |

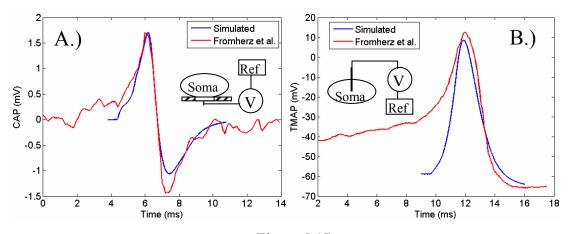

| 5.16 | Real signals for Aplysia MCC neuron compared with simulated signals               |

|------|-----------------------------------------------------------------------------------|

|      | from model: A.) CAP and B.) TMAP                                                  |

| 5.17 | Real signals for Hirudo Retzius neuron compared with simulated                    |

|      | signals from model: A.) CAP and B.) TMAP                                          |

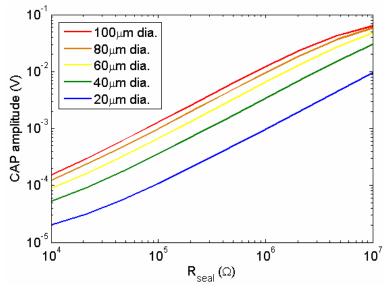

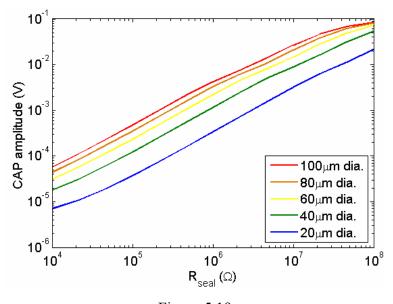

| 5.18 | Effect of $R_{seal}$ upon CAP amplitude for Helisoma B19 type model               |

| 5.19 | Effect of $R_{seal}$ upon CAP amplitude for Aplysia MCC type model                |

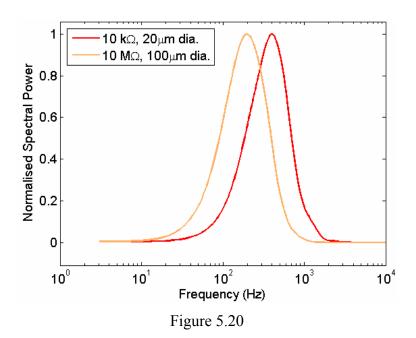

| 5.20 | Normalised Spectral Power for Helisoma B19 type model showing                     |

|      | maximum and minimum curves                                                        |

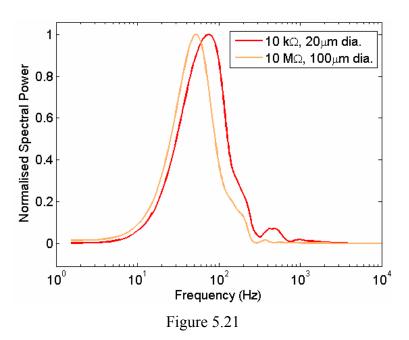

| 5.21 | Normalised Spectral Power for Aplysia type model showing maximum                  |

|      | and minimum curves                                                                |

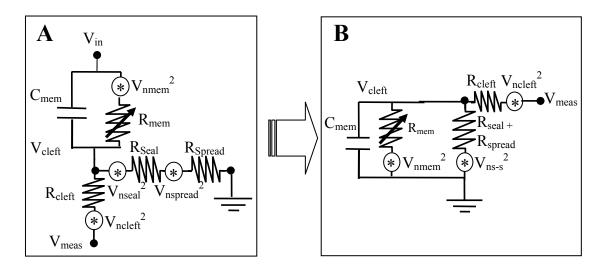

| 5.22 | Thermal noise sources in the CAP signal path: A. the cleft model,                 |

|      | B the noise analysis model                                                        |

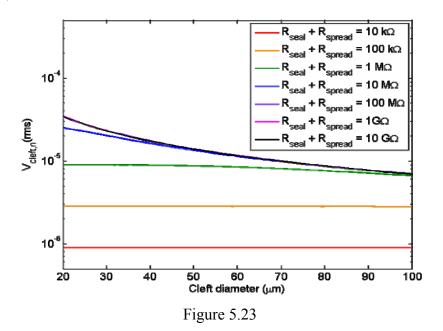

| 5.23 | SPICE (Cadence Virtuoso) simulation of rms noise voltage within the               |

|      | cleft during membrane resting state                                               |

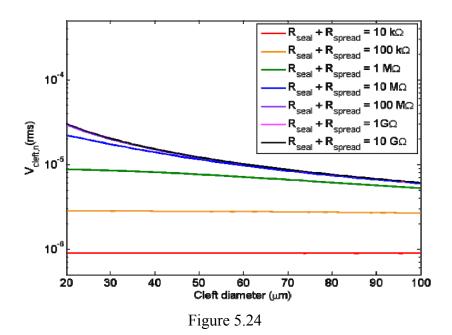

| 5.24 | SPICE (Cadence Virtuoso) simulation of rms noise voltage within                   |

|      | the cleft during action potential peak                                            |

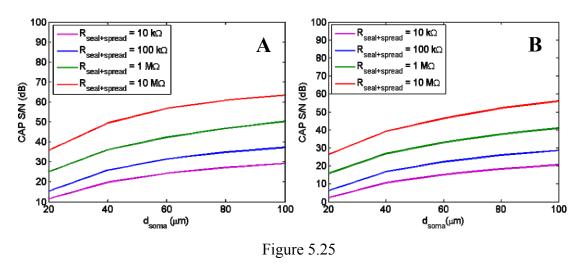

| 5.25 | Signal to noise ratio range for A, Helisoma B19 neuron model                      |

|      | and B, Aplysia MCC neuron model over the range of $d_{\text{soma}}$ and           |

|      | R <sub>seal+spread</sub> values given in table 5.3 and 5.4.                       |

| 5.26 | Electrical circuit between the TMAP and the recording electrode                   |

| 5.27 | Lumped circuit model for input circuit parasitic resistances and                  |

|      | capacitances                                                                      |

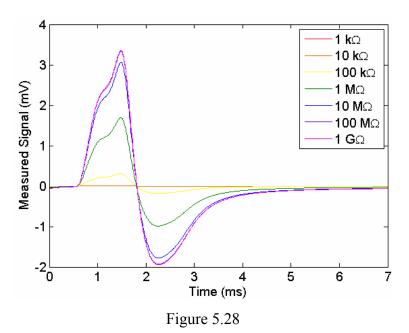

| 5.28 | Effect of $R_L$ upon signal amplitude                                             |

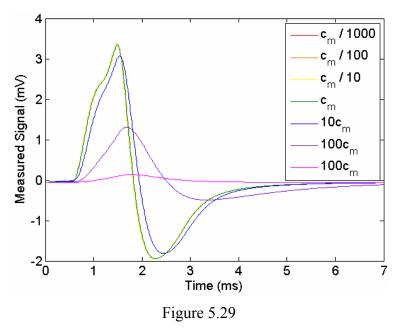

| 5.29 | Relationship between the amplitude of the measured signal and                     |

|      | the total shunt capacitance $C_T$ . $C_T$ is chosen relative to the capacitance   |

|      | per unit area of the membrane to illustrate the dependence upon the               |

|      | membrane area within the cleft                                                    |

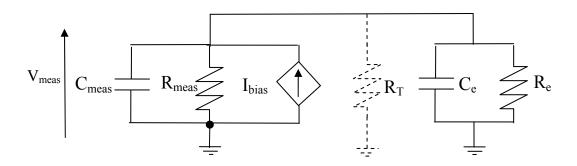

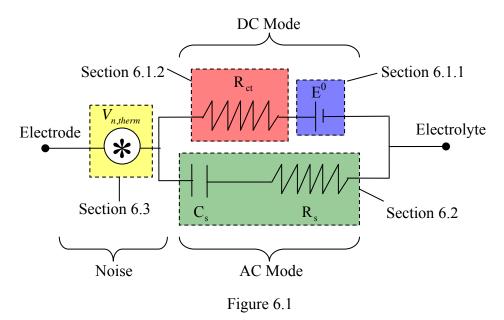

| 5.30 | The amplifier input circuit together with the electrode circuit and               |

|      | parasitic shunt resistance R <sub>T</sub>                                         |

| 5.31 | Effect of high pass input filter circuit with varying $f_{\text{c}}$ on simulated |

|      | Helisoma B19 and Aplysia MCC neurons                                              |

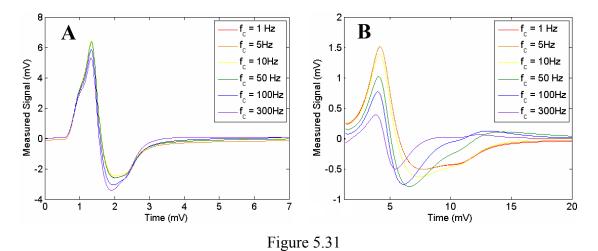

| 5.32 | Frequency range of spectral power of neural signals from SPICE model             |     |  |  |

|------|----------------------------------------------------------------------------------|-----|--|--|

|      | incorporating fitted values from figure 5.2                                      | 192 |  |  |

| Cha  | apter 6                                                                          |     |  |  |

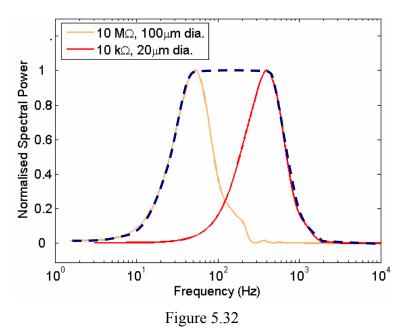

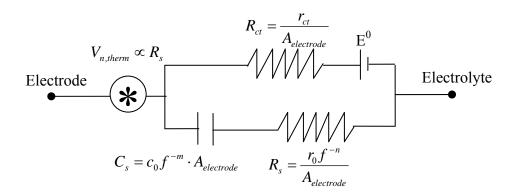

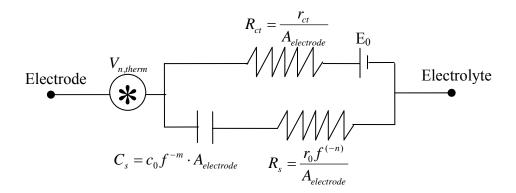

| 6.1  | Electrical properties of the electrode electrolyte interface                     | 198 |  |  |

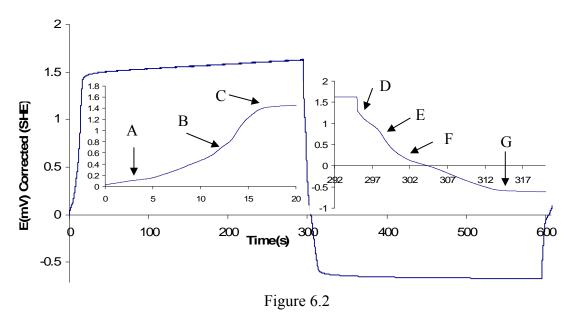

| 6.2  | Chronopotentiometric response of Pt electrode at +/- $100 \mu A/cm^2 \dots$      | 203 |  |  |

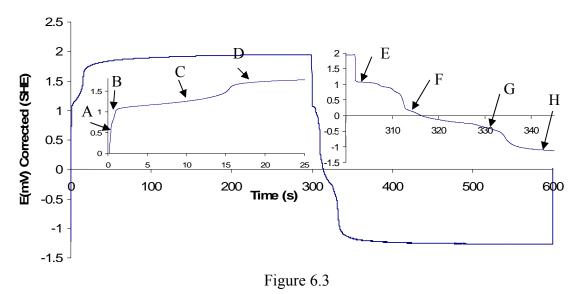

| 6.3  | Chronopotentiometric response of Au electrode at +/- $100 \mu A/cm^2 \dots$      | 204 |  |  |

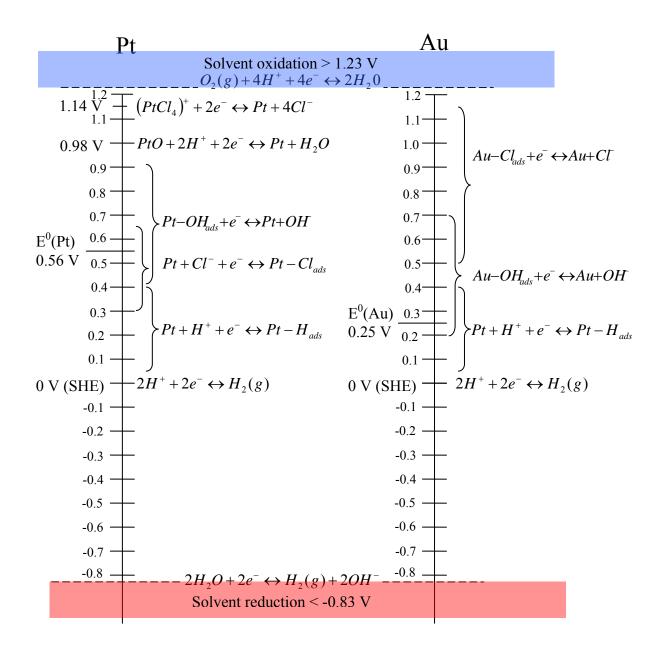

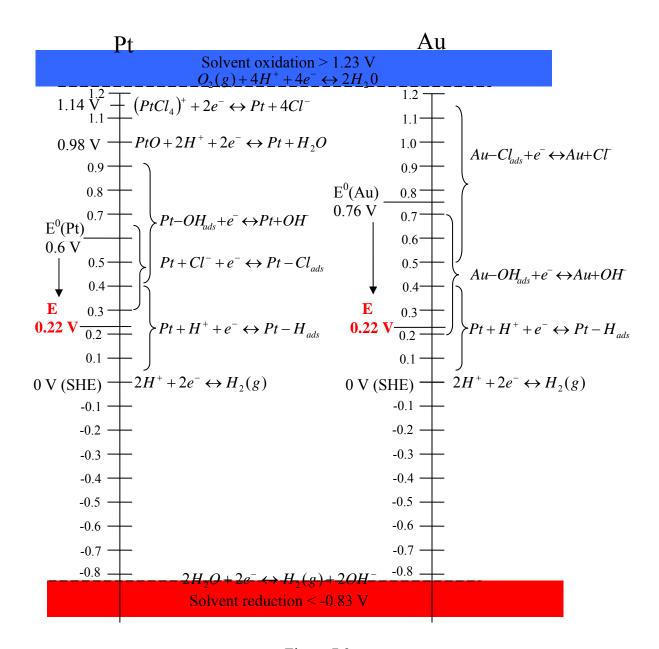

| 6.4  | Table of electrochemical reactions and sorptions in physiological saline         | 209 |  |  |

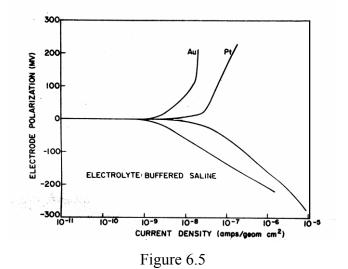

| 6.5  | V-I plot for Pt and Au electrodes in phosphate buffered physiological            |     |  |  |

|      | saline; adapted from Wise et al                                                  | 210 |  |  |

| 6.6  | Electrical model of the electrode-electrolyte interface                          | 224 |  |  |

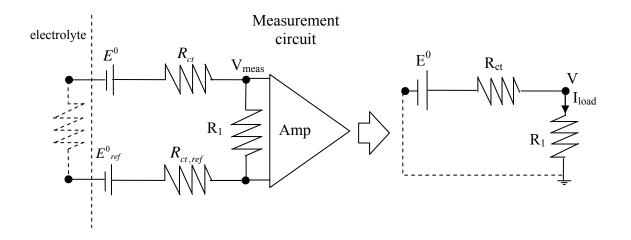

| 6.7  | Electrode interface potential electrical equivalent circuit                      | 225 |  |  |

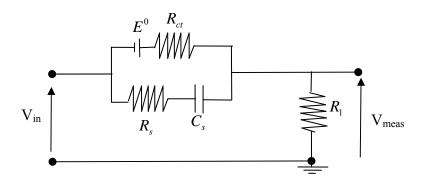

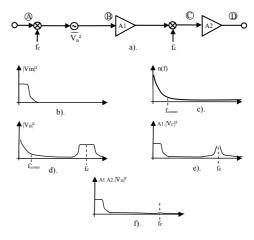

| 6.8  | The modelled interface high-pass filter circuit                                  | 226 |  |  |

| Cha  | apter 7                                                                          |     |  |  |

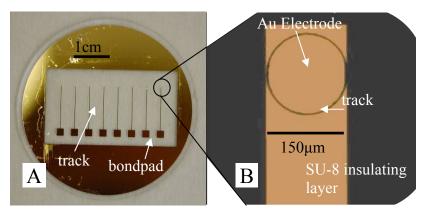

| 7.1  | Photograph of A, an Au on quartz electrode array, B, a magnified                 |     |  |  |

|      | single electrode                                                                 | 235 |  |  |

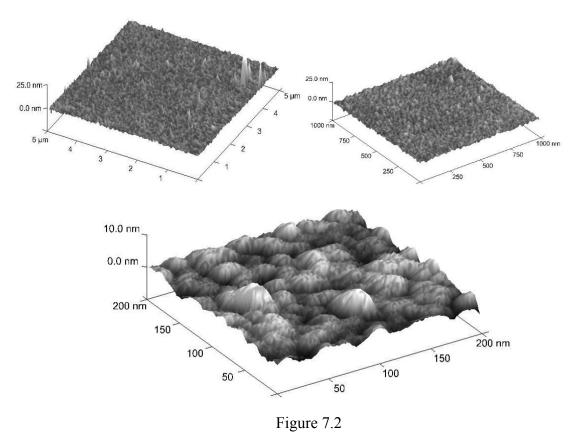

| 7.2  | AFM 3D surface profile of thin film platinum electrode at 5 $\mu$ m x 5 $\mu$ m, |     |  |  |

|      | 1 μm x 1 μm and 200 nm x 200 nm area                                             | 236 |  |  |

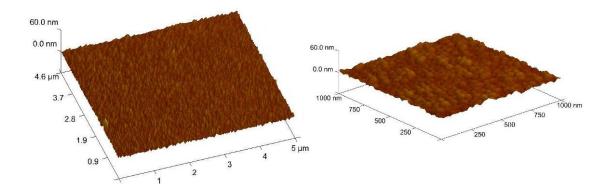

| 7.3  | AFM 3D surface profile of thin film gold electrode at 5 $\mu$ m x 5 $\mu$ m and  |     |  |  |

|      | 1 μm x 1 μm area                                                                 | 237 |  |  |

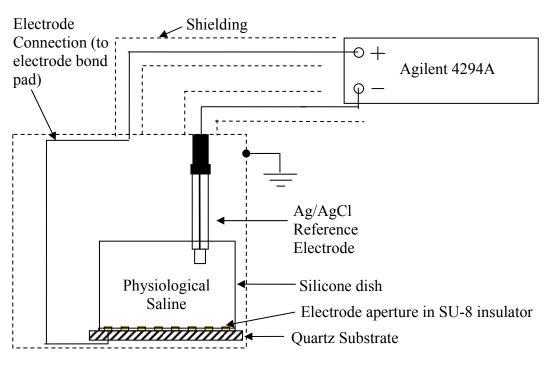

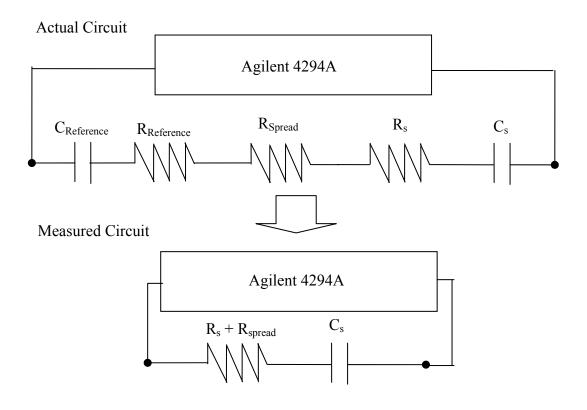

| 7.4  | Connection of array to impedance analyser                                        | 239 |  |  |

| 7.5  | Comparison of the actual series circuit with the measured series circuit         | 240 |  |  |

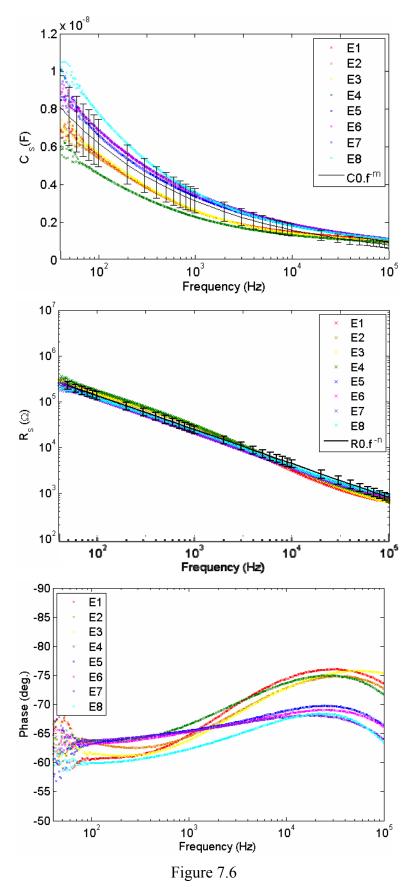

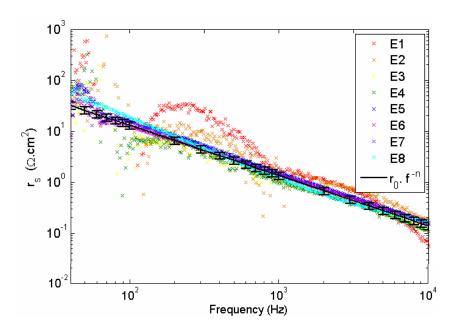

| 7.6  | Series capacitance, resistance and phase of thin film Pt electrode               |     |  |  |

|      | interface with physiological saline                                              | 242 |  |  |

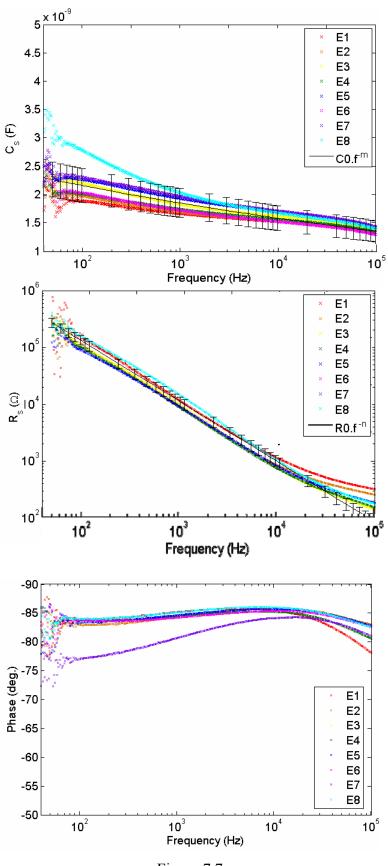

| 7.7  | Series capacitance, resistance and phase of thin film Au electrode               |     |  |  |

|      | interface with physiological saline                                              | 243 |  |  |

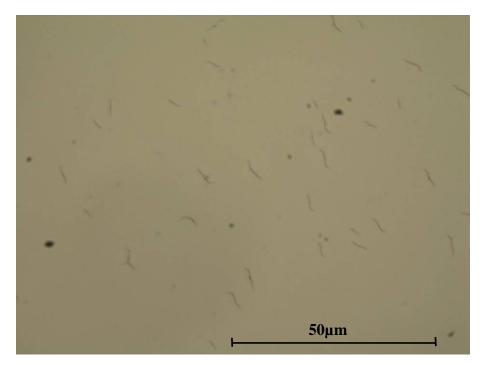

| 7.8  | Microscope images of typical density of surface cracks in thin film                   |     |

|------|---------------------------------------------------------------------------------------|-----|

|      | Pt electrodes                                                                         | 248 |

| 7.9  | Table of electrochemical reactions and sorptions in physiological                     |     |

|      | saline noting the experimentally measured value of E <sup>0</sup> for thin film       |     |

|      | Pt and Au electrodes                                                                  | 250 |

| 7.10 | Electrode model for Pt and Au electrodes                                              | 251 |

| 7.11 | Summary of the relationship between pertinent design variables                        | 256 |

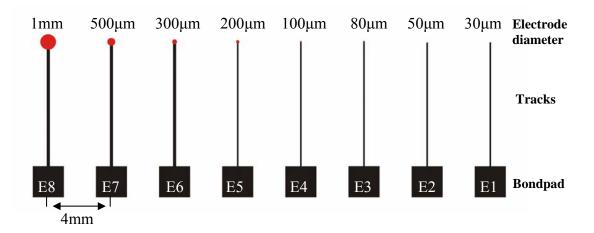

| 7.12 | Layout of the scaled thin film Au array                                               | 257 |

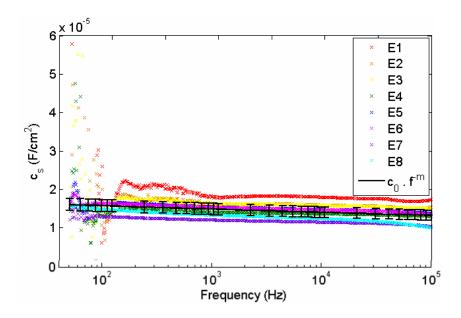

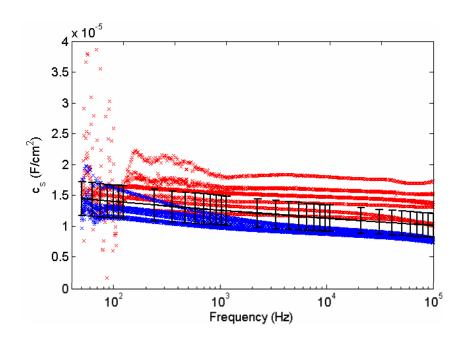

| 7.13 | Comparison of capacitance per unit area for scaled Au thin film array                 | 258 |

| 7.14 | Comparison of capacitance per unit area for scaled Au thin film array                 | 258 |

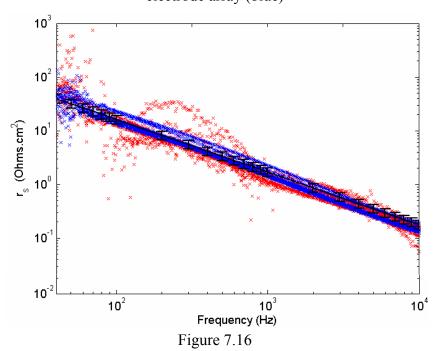

| 7.15 | Comparison between $c_{\rm s}$ for the scaled electro array (red) and the 150 $\mu m$ |     |

|      | electrode array (blue)                                                                | 260 |

| 7.16 | Comparison between $r_{s}$ for the scaled electro array (red) and the 150 $\mu m$     |     |

|      | electrode array (blue)                                                                | 260 |

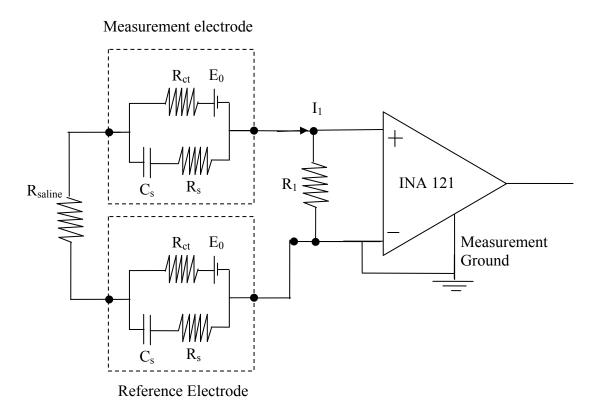

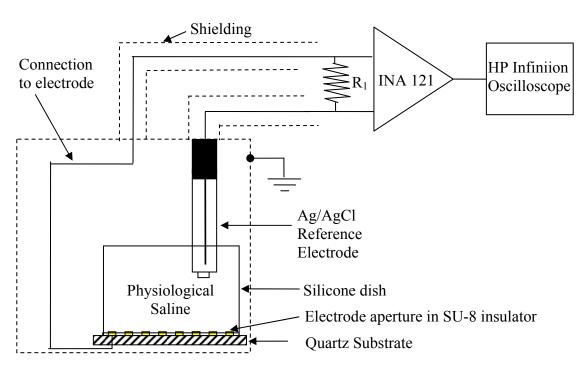

| 7.17 | The configuration of the circuit                                                      | 262 |

| 7.18 | Amplifier circuit to measure the half cell offset potential                           | 262 |

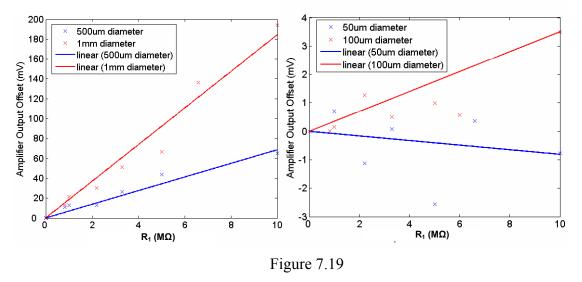

| 7.19 | Measured amplifier offset potentials for resistances ranging from                     |     |

|      | $0~\Omega$ to $10~\text{M}\Omega$                                                     | 263 |

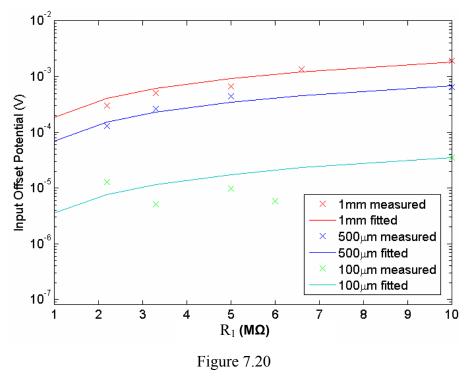

| 7.20 | Calculated and measured values of input offset vs. R <sub>1</sub>                     | 264 |

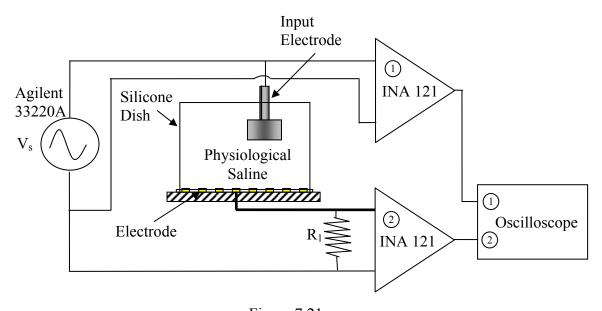

| 7.21 | Illustration of measurement circuit                                                   | 266 |

| 7.22 | Electrical circuit of the experiment arrangement                                      | 260 |

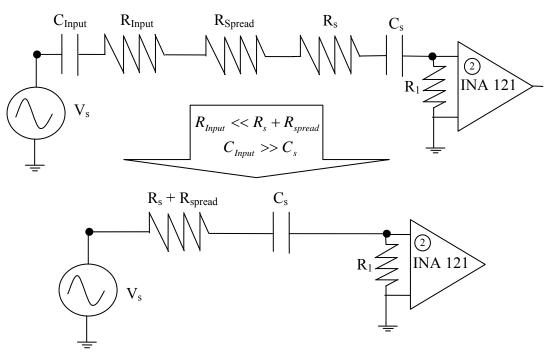

| 7.23 | A.) Measured gain and B.) phase of current through $R_1$ for 50 $\mu m$               |     |

|      | diameter thin film Au electrode                                                       | 267 |

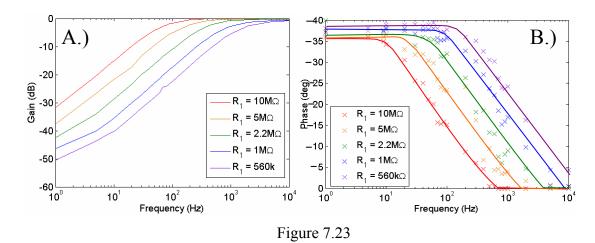

| 7.24 | A.) Measured gain and B.) phase of current through $R_1$ for 30 $\mu m$ diameter      |     |

|      | thin film Au electrode                                                                | 268 |

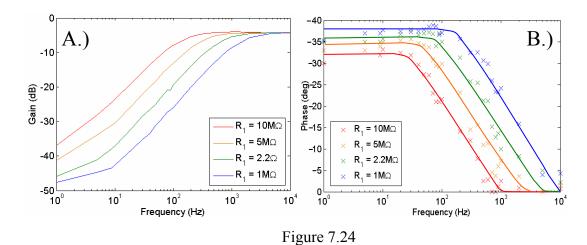

| 7.25 | Comparison of recorded waveforms                                                      | 269 |

| 7.25 | Comparison of experimental and predicted gain response for 50 $\mu m$                 |     |

|      | diameter electrode                                                                    | 270 |

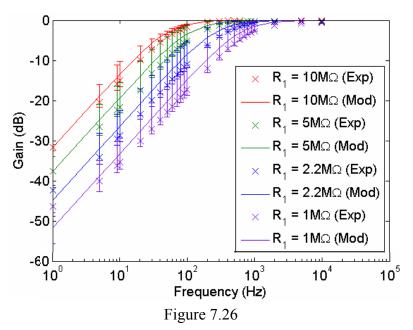

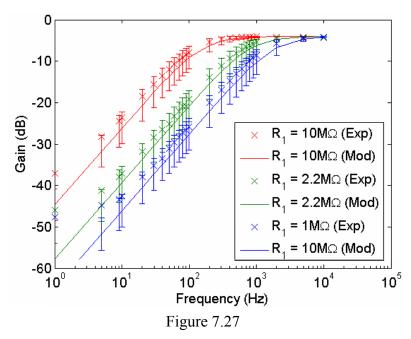

| 7.26 | Comparison of experimental and predicted gain response for 30 $\mu m$                 |     |

|      | diameter electrode                                                                    | 270 |

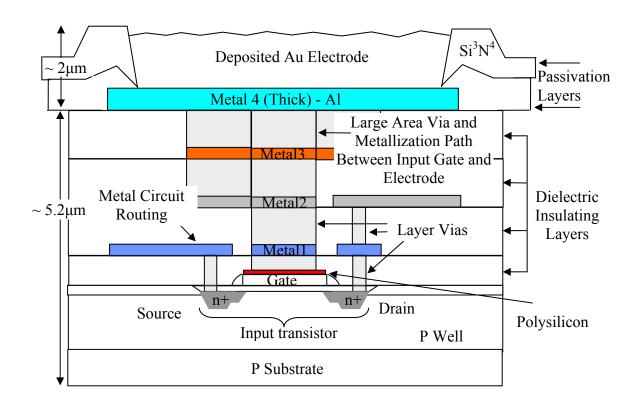

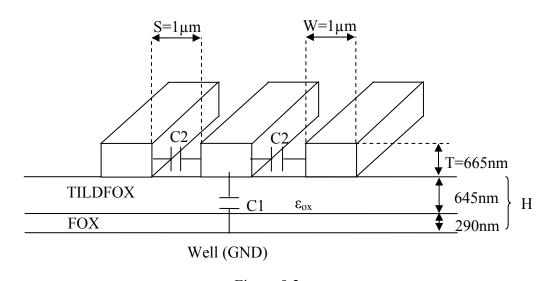

| 8.1  | Water cross section illustrating direct placement of amplifier beneath elect | rode  |

|------|------------------------------------------------------------------------------|-------|

|      | forming active electrode 'pixel'                                             | 278   |

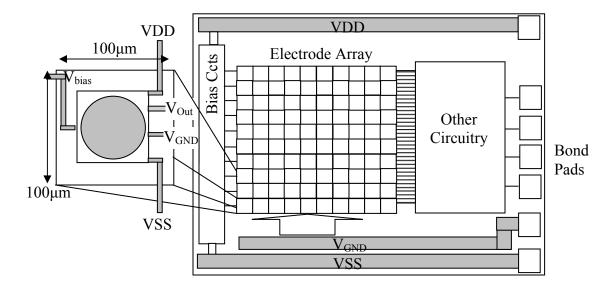

| 8.2  | First stage conceptual floorplan                                             | 280   |

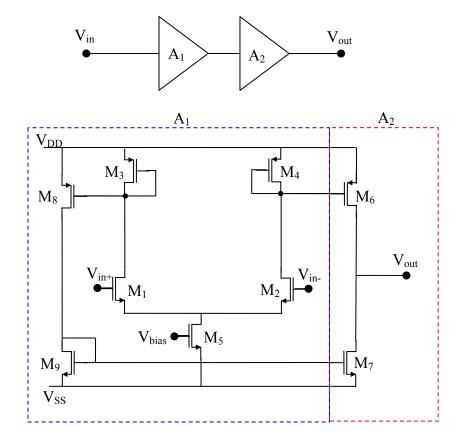

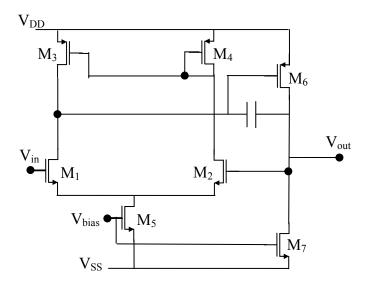

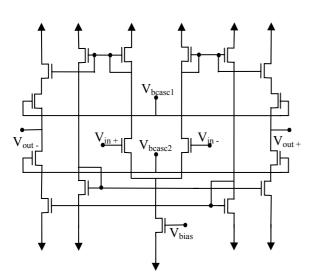

| 8.3  | Schematic of push-pull current mirror operational amplifier                  | 286   |

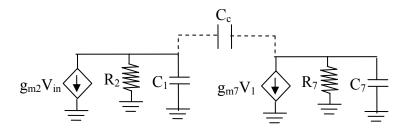

| 8.4  | Small signal circuit for compensation capacitor                              | 294   |

| 8.5  | Amplifier bias circuit                                                       | 299   |

| 8.6  | Final amplifier circuit schematic                                            | 300   |

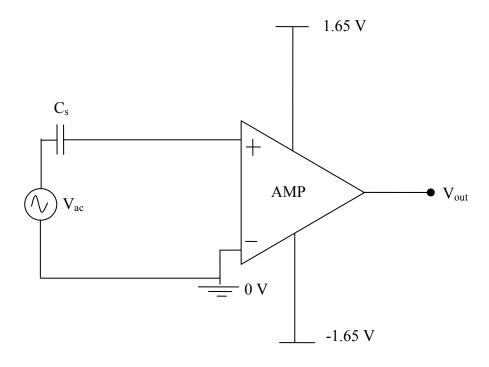

| 8.7  | Amplifier testbench circuit configuration as simulated in Virtuoso           | 302   |

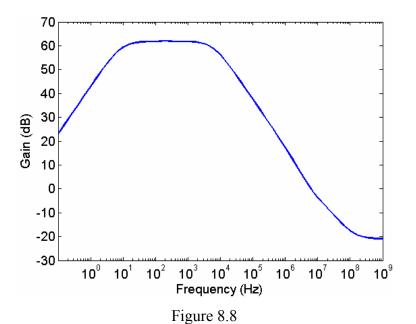

| 8.8  | Gain performance of amplifier between 0.1 Hz and 1 GHz                       | 302   |

| 8.9  | Testbench schematic for connection between the amplifier and                 |       |

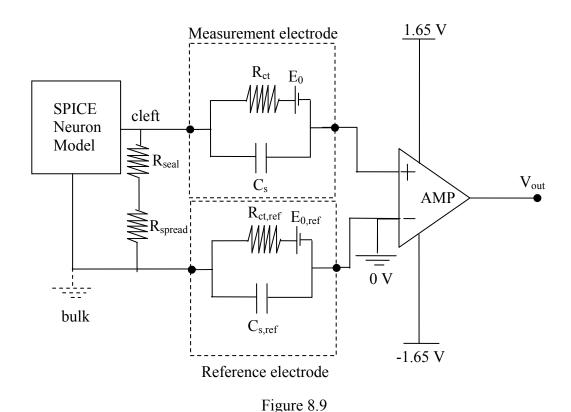

|      | SPICE model                                                                  | 303   |

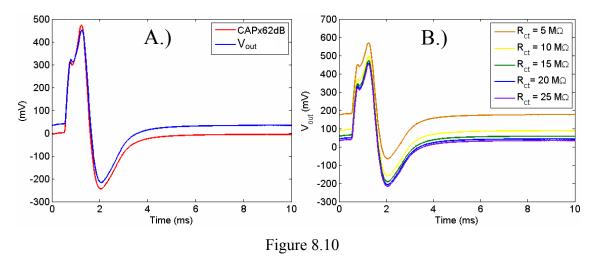

| 8.10 | Simulated response for Helisoma B19 neuron model                             | 304   |

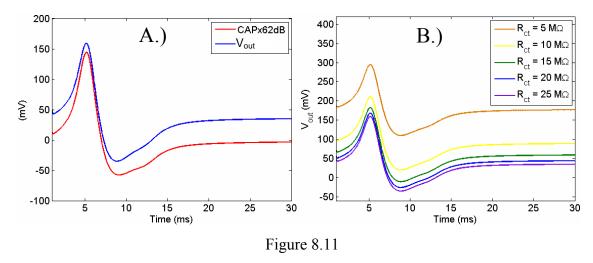

| 8.11 | Simulated response for Aplysia MCC neuron model                              | 304   |

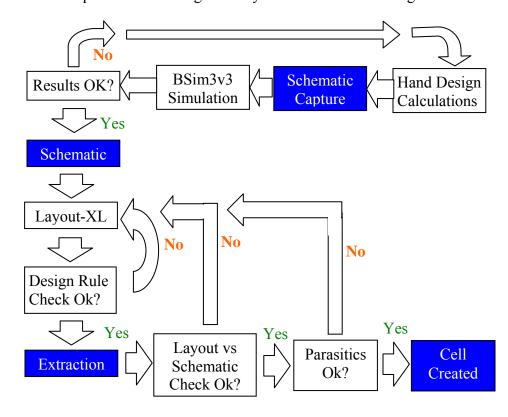

| 8.12 | Analogue circuit design and layout flow                                      | 305   |

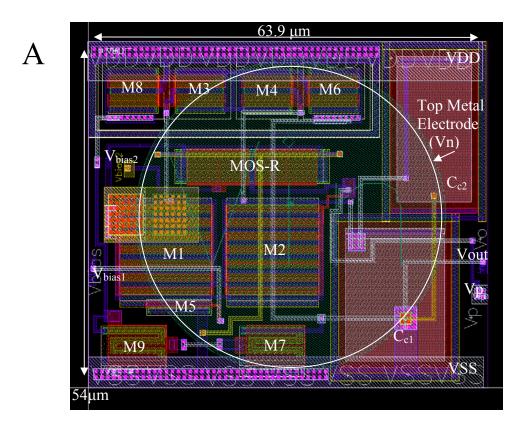

| 8.13 | Front end device layout: A.) Input amplifier, B.) Bias circuit               | 306   |

| Cha  | apter 9                                                                      |       |

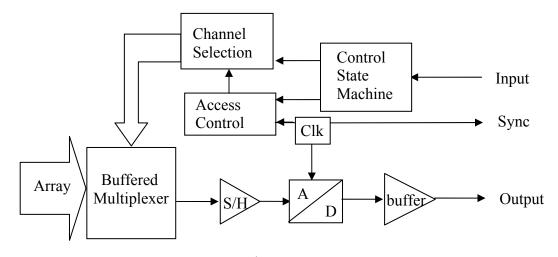

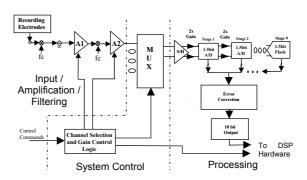

| 9.1  | Chip functional structure                                                    | . 314 |

| 9.2  | VLSI signal routing capacitance parameters for AMS 0.35 µm process           | 316   |

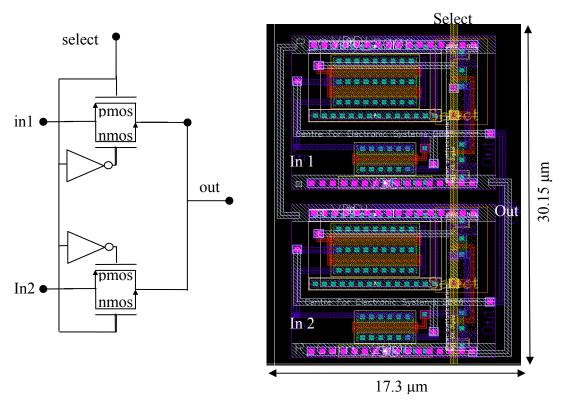

| 9.3  | Schematic and layout of multiplexer circuit                                  | 318   |

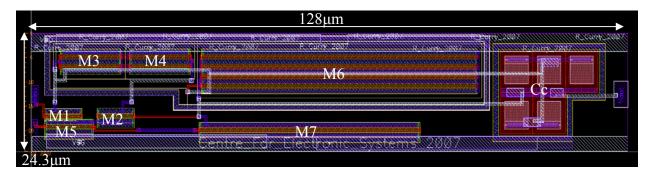

| 9.4  | Buffer amplifier schematic                                                   | 320   |

| 9.5  | Layout of buffer circuit                                                     | 322   |

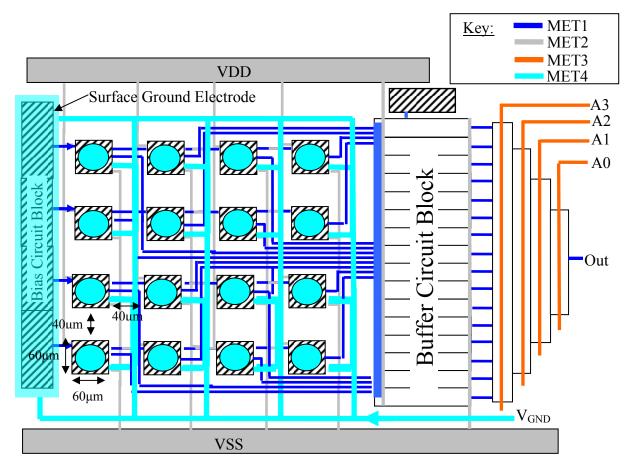

| 9.6  | Diagram of active electrode connectivity                                     | 323   |

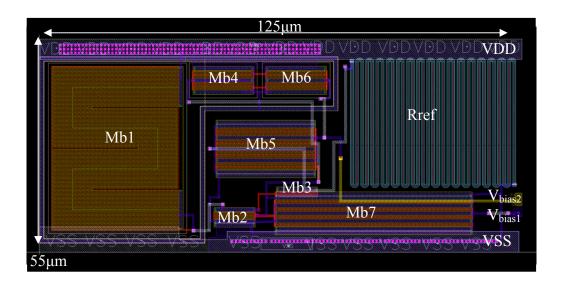

| 9.7  | An example layout for a 16 active electrode array                            | 324   |

| 9.8  | Simple schematic and timing diagram for externally controlled array          |       |

|      | access                                                                       | 330   |

| 9.9  | Envisioned floorplan of fully integrated active MEA soc with  |     |

|------|---------------------------------------------------------------|-----|

|      | minimal input / output connections                            | 333 |

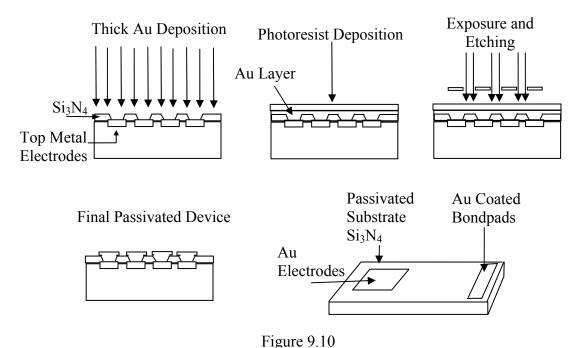

| 9.10 | Illustration of final Au deposition process for passivation   | 335 |

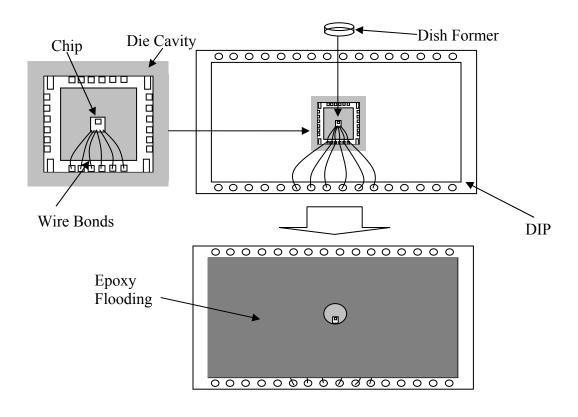

| 9.11 | Prospective MEA style DIP packaging scheme                    | 336 |

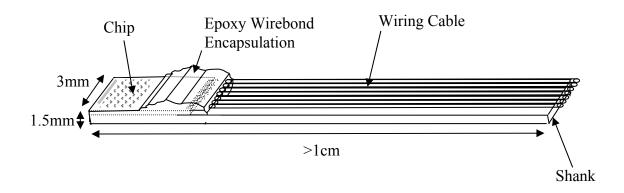

| 9.12 | Use of the device as a hypothetical shank header              | 337 |

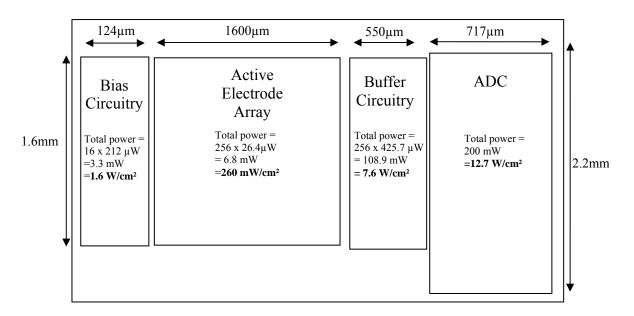

| 9.13 | Power consumption of the composite functional analogue blocks | 338 |

## **List of Tables**

| Cha | pter 1                                                                                    |     |

|-----|-------------------------------------------------------------------------------------------|-----|

| 1.1 | Concentration of ionic species for squid axon                                             | 19  |

| Cha | pter 4                                                                                    |     |

| 4.1 | Significant design parameters in SPICE model                                              | 144 |

| Cha | pter 5                                                                                    |     |

| 5.1 | Pertinent model variables modified form generic values to reproduce extracted signal form | 167 |

| 5.2 | Mean squared error for the simulated neural signals                                       | 170 |

| 5.3 | Summary of intrinsic values of components forming the cleft circuit                       | 171 |

| 5.4 | Equations and range of values for cleft circuit components                                | 172 |

| 5.5 | Summary table of rms noise within the cleft for varying resistances                       |     |

|     | of $R_s$ and $R_{mem}$                                                                    | 177 |

| 5.6 | Summary of design parameters                                                              | 194 |

| 6.1 | Published $c_s$ and $r_s$ data for Pt electrodes             | 218 |

|-----|--------------------------------------------------------------|-----|

| 6.2 | Published $c_s$ and $r_s$ data for Au electrodes             | 219 |

|     |                                                              |     |

| Ch  | apter 7                                                      |     |

| 7.1 | Statistical information for the Pt array                     | 244 |

| 7.2 | Statistical information for the Au array                     | 244 |

| 7.3 | Statistical values of Pt per unit area of electrode surface  | 245 |

| 7.4 | Statistical values of Au per unit area of electrode surface  | 245 |

| 7.5 | Mean parameter summary for thin film electrode Model         |     |

|     | (40 Hz – 100 kHz)                                            | 252 |

| 7.6 | Statistical information for the scaled Au array              | 261 |

| 7.7 | Updated mean parameter summary for thin film electrode Model |     |

|     | (40 Hz – 100 kHz)                                            | 251 |

|     |                                                              |     |

| Ch  | apter 8                                                      |     |

| 8.1 | Bias Circuit Design Variables                                | 299 |

| 8.2 | Table of Device Sizes                                        | 301 |

| 8.3 | Simulated Device Performance Results                         | 301 |

| 9.1 | Buffer Amplifier Transistor Sizes     | 321 |

|-----|---------------------------------------|-----|

| 9.2 | Summary of Buffer Circuit Performance | 321 |

#### Introduction

The work presented in this thesis develops the theoretical investigation and design of an active (transistor integrated circuit) bioelectric sensor device, capable of measuring and extracting the neural network activity of living neurons on a high spatiotemporal basis. The device is geared towards the electrophysiological study of cultured or dissected tissue (*in vitro*) and possible applications with tissue remaining intact inside the body (*in vivo*) of the studied organism.

Living neural networks are the basis for all biological sensation and processing. From the recognition of shapes to the enjoyment of music, the evidence strongly suggests that every isolated feeling and reaction is facilitated by relative neural positioning, interconnection and coordinated electrochemical activity formed by the vast parallel connection morphologies between billions of cells.

To understand the cumulative functionality of neurons, one must ideally be able to observe many such connected cells over a suitably long period of time. Considering that these cells are often much smaller than  $100 \mu m$  and that complex functional networks may require the cooperation of many thousands of such cells, the task of observing each and every cell in the network during its operation becomes very difficult. Furthermore,

these cells are very fragile in nature and will only survive in environments closely resembling the in vivo state of their host species.

Fortunately for the curious researcher, neurons communicate using electrical signals that we may measure passively using many different electrical measurement approaches. However, many of these methods are harmful to the cell and do not allow the cell to function naturally over long periods of time. This may not be a problem in primary physiological research but for the study of network formation and operation it obviously reduces the link between *in vivo* (within the organism) and *in vitro* (outside of the organism) study and may terminate the operation of the cultured cells prematurely.

Further difficulties manifest themselves with the micron scale of discrete cells and the large numbers of such cells required to deliver mental functionality. There are for example thousands of billions of cells that constitute our own human thought processes and tens of thousands that constitute the simple nervous system of large pond snails, with each cell measuring many times less than  $100~\mu m$ . It would be very difficult, if not impossible at this stage in neural signal interfacing to study every neuron in such a large network as presented by the snail.

We can however study smaller network connections that contribute to these larger systems to determine certain behavioural mechanisms of the neuron networks. Just as *in vitro* cultures were developed to isolate and simplify the dependencies of organ cells and neurons we may dissect and study small network groups with the final aim of understanding the larger system.

Solutions have been presented that utilise the measurable electrical activity of single and multiple communicating cells to observe network activity using penetrating and non-penetrating metallic electrode elements. However the only method capable of measuring large spatial signal distributions is the planar Micro Electrode Array (MEA). The cost for this flexibility is that only the local extracellular electrical activity of the neuron may be measured. This signal is very small in magnitude and may be in many situations very

close to the fundamental electrical noise floor of the measurement equipment. For high density recording MEAs it may be shown that the available number of electrodes is primarily limited by the connectivity of each electrode to external signal conditioning and monitoring equipment. For this reason electrode arrays rarely exceed 60-100 recording sites and do not come close to providing a one-to-one recording density with the studied neurons for large functional cultures. Because of these topological and electrical bottlenecks, integrated circuitry has been piggybacked with customised passive arrays to extend their versatility. Such circuitry, often termed 'neurochips' require large arrays of connective wiring and consume much larger physical areas than the neurons they are measuring. Due to the small magnitude of the extracellular signal that is measured there must be a low resistance path between the cell and the amplification circuitry to maintain the quality of the measured signal.

#### Objectives of this Work

This work represents an electronic engineer's attempt to investigate the interface between the biological and electronic domains for the purpose of neural signal measurement. By understanding the principles and mechanisms of this interface it is believed that a novel high density active transduction method may be developed to advance the measurement of high density neuron network communication.

The design of the device is developed using information gained from a generic physical model and computer simulation of the neural interface and the experimental characterisation of a suitable transducer microelectrode. By integrating the recording electrode with a dedicated amplification and conditioning circuitry, it is believed that many of the limitations of passive devices may be overcome, thus allowing a higher recording site density for larger numbers of channels. Electrode connectivity and access may also be improved by using digital channel selection and multiplexing schemes to reduce the number of device connections making the device more versatile and easy to use.

The ultimate goal of this work is to provide an active signal amplifying front end that approaches or is reduced below the size of a typical cultured neuron, such that a 1:1 ratio between neuron and active electrode may be reached. By providing immediate amplification to the neural signal at the source of transduction, many of the topological and operational constraints of passive MEAs may be reduced to a manageable level for large arrays, thus allowing the study of larger networks to further develop the current knowledge of neurological processing.

In addition, the advent of a cellular size active transducer may have relevance in other neighbouring biological fields such as cellular drug screening and smart biological sensors whereby the reaction of the cell to chemical or other stimuli may be detected by the electrical response patterns of the exposed culture.

This project was funded by the EPSRC (Engineering and Physical Sciences Research Council) under the EPPIC (Electronic and Photonics Packaging and Inter-Connection) Faraday partnership with additional funding from CELS (Centre of Excellence for Life Sciences) in the form of a CASE (Cooperative Awards in Science and Engineering).

Despite the interdisciplinary theme of the research it remains strongly placed in the field of electronic engineering. It may therefore be necessary to familiarise the reader with aspects of the neurological system under consideration before describing the development within the main body of work. It is hoped that this will provide an interesting and informative introduction to neurophysiology and this thesis.

#### 1.1 Thesis Structure

This thesis is split into three main parts. The first discusses the relevant background and theoretical framework from which the work is built and considers the variety of methods that are used to observe neural signals. This begins in section 1.2 with an introduction to neurophysiology that establishes key concepts and physiological descriptions of neural

physiology. Chapter 2 gives a comprehensive comparison of various methods that are used to measure the electrophysiological signals of neurons and assesses their suitability for use in a high density recording site integrated device. Chapter 3 analyses and discusses the general problems that are associated with the passive and the active MEA systems as they approach higher densities.

Chapters 4 to 7 cover the second part of this thesis and address the modelling, simulation and experimental characterisation of the system around which the design and design methodology are centred. Chapter 4 develops an electrical model of a neuron based upon the empirical work of Hodgkin and Huxley and the theory of extracellular signal recording. A novel SPICE model is developed that is a 2D nodal representation of a neuron. The model is scalable for different neuron geometries and action potential signal durations. In chapter 5, the model is fitted to real extracellular microelectrode recordings. The simulation is then used to determine the electrical characteristics of the extracellular source signal for a range of neuron sizes and neuron-electrode coupling configurations to determine the electrical requirements fro an optimised measurement circuit.

Chapter 6 develops the electrochemical theory of the electrode-electrolyte interface for biological systems and a model is formed to describe the ac and dc electrical properties based upon the literature. Chapter 7 investigates the ac and dc properties of thin film platinum and gold electrodes presents a set of experimental results and an empirical model that characterises this interface. It is then demonstrated that the most challenging aspect of the interface, the interface offset potential, may be removed by careful selection of the input characteristics of the measurement circuit. This method exploits the large capacitance of the electrode to remove the need for dc blocking capacitance at the input. A design method is developed to ensure that the low level neural signal is preserved as the offset is removed.

The third part of this thesis, consisting of chapters 8 and 9, proposes an area efficient design for an active MEA front end. The design utilizes the capacitive properties of the electrode interface developed in chapter 7 to reduce the area of the circuit on silicon. The

resulting amplifier front end may be fabricated for neural measurement at much higher spatial densities. The device bridges the spatial recording gap between single transistor input devices and full amplifier devices while retaining the low power and high signal recording quality of full amplifier devices.

Chapter 8 develops the front end into a compact CMOS transistor based circuit. The process of schematic design and simulation for the selected CMOS process is discussed along with layout implementation. Chapter 10 considers the overall layout of the device and the additional circuits required to give functionality as a stand alone neural monitoring device. A 16 and 256 element array layout is presented for test and packaging. Issues are considered for biocompatibility and application. Chapter 9 considers the device floorplan and packaging development to allow for versatility within *in vivo* and *in vitro* use. The issues of high thermal power dissipation are discussed as device compactness and on board sampling and digitization functionality is added.

The thesis is concluded in chapter 10. An overview of the thesis is given and the achievements of the work are highlighted. The features and benefits of the design are discussed and possible future challenges to such devices are highlighted.

## 1.2 Introduction to Neurophysiology

To the engineer, close inspection of the living cell shows an amazing system of complex mechanical and chemical processing that is based upon the efficient manipulation of environmental charge carriers. At the fundamental cellular level, it may be shown that nature harnesses the charges of different chemical and ionic particles to perform absolute functionality; from replication to locomotion and inter-cellular communication.

Although we are composed of billions of these composite cells, we are oblivious to their operation and properties in our natural state. Their existence and functionality has only become apparent to our consciousness due to the explorative observation of physiological

researchers who have endeavoured to understand the fundamentals of our physical operation.

This section outlines some of the basic concepts of neural physiology that creates this functionality and develops the basic theory of the electrophysiological phenomenon whereby we may study their behaviour.

#### 1.2.1 Classification of Cells

There are many different cells within nature, each identified by their morphological and behavioural traits. Some exist in isolation and others exist collectively. This thesis is concerned with the classification of cells known as neurons. Neuron is the descriptive name for electrically excitable cells that form the nervous systems and process and transmit information. Due to the electrical excitability of these cells the researcher may monitor and stimulate them by electrical means. This allows a method of direct study that is not present with other cell types.

Neurons may be sub-categorised into the sub-group of the central nervous system (CNS) or the peripheral nervous system (PNS) depending upon its position in the nervous system hierarchy of the host organism.

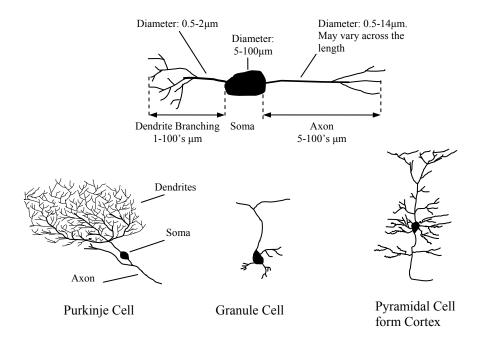

Neurons are differentiated into different sub-groups, depending on their placement in the body and the cells that surround them. The morphology of each can be very different given the task it is required to perform, this includes size, number of connections and dendrite and terminal configurations. Some have few dendritic branches; others are highly branched and receive large amounts of signal data. Typical neuron sizes are illustrated in figure 1.1.

The afferent PNS can be loosely split into the sensation gathering receptor cells and projection neurons, with their distinct elongated axons that carry the signals to the CNS.

Receptor cells, such as the auditory hair cell, olfactory granule cell and the retinal bipolar cell are generally termed intrinsic neurons and have very little or no axon protrusions but many terminal branches. As a general rule, afferent cells do not require dendritic inputs due to their depolarisation on physical stimuli such as light, pressure, temperature, etc.

Efferent neurons that provide motor function are generally much larger than their afferent counterparts. These cells typically have axon protrusions many tens to thousands of times longer than the diameter of the constituent soma. The purpose of these cells is the stimulation of end effectors throughout the body's extremities providing the recruitment of muscle fibre. In humans single axons can be up to a metre in length, as found in the sciatic nerve trunk, for the routing of axons beyond the spinal cord to the extremities. Large axons of this kind are typically wrapped in myelin sheaths.

Neurons within the CNS typically follow the general neuron structure given in figure 1.3. They are densely packed and necessitate many connections, resulting in many dendrite outgrowths and connective axon terminals. Purkinje cells in the cerebellum, for example, can have over one thousand dendritic branches.

Fig 1.1 Illustration of generic cell dimensions and a selection of CNS neuron cell types.

The cells are structured within a matrix of glial cells that shape their growth and provide myelination. The axons of CNS neurons vary in length depending on function and the connections required, but are typically no longer than a few tens of microns.

## 1.2.2 The Molecular Structure of the Cell

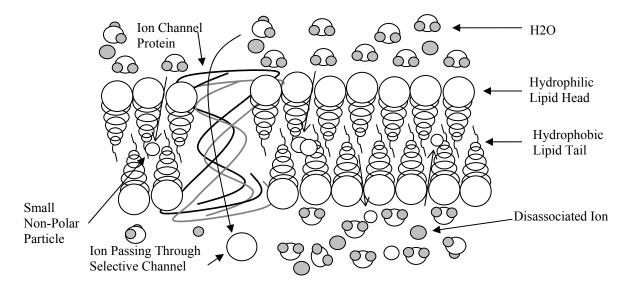

Biological cells are complex systems of molecular building blocks that provide protection and functionality within the natural environment. It is believed that life developed amongst the planet's abundant surface waters and as a result it is geared to operation within such conditions. In essence the cell is an enforced compartment with an aqueous interior that is physically separated from its surrounding electrolyte. The barrier presents a control over the flux of solute particles and is termed the cell membrane. The interior electrolyte is termed the intracellular fluid and the exterior is termed the extracellular fluid.

The barrier is formed by two layers of phospholipid molecules. Phospholipids present asymmetrical properties over their length; they have an electrically charged 'head' and an uncharged 'tail' that influences the behaviour of the surrounding water molecules. The structure is commonly referred to as the 'hydrophilic head' and 'hydrophobic tail' of the molecule. As water molecules are dipolar (they possess a net positive charge on their H<sub>2</sub> and net negative charge on the O) physical forces will present themselves when the two molecules are brought in contact. Due to these forces, the lipid molecules spontaneously orient themselves, forming a bi-layer with a depth of approximately 10nm. The lipid bilayer is structured with the hydrophilic heads presented to the water molecules and the hydrophobic tails facing inwards, ensuring an impenetrable barrier between the intracellular and extracellular fluid. The structure is illustrated in figure 1.2. The tails of the lipids form an oily core which is also impermeable to polar, non-organic molecules or ions. Small non-polar molecules such as O<sub>2</sub> may pass through this layer due to their partial solubility within lipids.

Smaller quantities of other various lipids and proteins are moved into the phospholipid tail structure that structurally stabilise the membrane and allow the cell to distort in a fluid like manner while maintaining integrity, or promote rigidity as and when required. Such proteins are what form the basis of cell morphology, cell division and movement and are discussed further in section 1.2.3. Other proteins form carriers that shuttle nutrients and ions across the membrane or provide a selective ionic pathways that operate under mechanical, electrical or chemical stimulus. It is these protein types that enable the electrogenic properties of the neuron.

Figure 1.2

Arrangement of the lipid bi-layer that is the basis for the plasma membrane, separating the intracellular fluid from the extracellular plasma. the diagram also shows the peripheral arrangement of selected ions.

The intracellular fluid within the lipid membrane contains the cells functional parts. These are termed organelles and consist of the nucleus, endoplasmic reticulum, mitochondria, lysosomes, etc. In eukaryotic cells (animal cells) these components may be compartmentalised within the cell by further membrane structures.

As the work presented in the thesis is more concerned with the direct properties of the membrane the organelles will not be described further. For more information on these cellular components the reader is referred to the texts [1, 2, 3].

#### 1.2.3 Cell Locomotion and Adhesion

It is commonly noted that mature neurons and developing neuroblast precursors do not remain at their point of genesis and migrate to their functional position. This fact is important in the consideration of developmental cellular study *in vivo* and especially in cultured *in vitro* preparations. This phenomenon is caused by proteins within the cell such

as tubulin and actin whose branching filaments form its structural skeleton. In neurons, locomotion is directly controlled by the constriction of structural actin bundles and polymeric extension of the tubulin proteins by the interaction of enzymes such as myosin and the hydrolysis of ATP. In the basic cell locomotion process the extension of the tubulin microtubes from their anchor point in the nucleus locally stretches and extends the lipid cell membrane to form a small outgrowth known as Lamellipodia. These structures have been observed to bond to other cells *in vivo* and substrates *in vitro*. The cell moves to this new anchorage point by actin constriction and de-polymerisation of the microtubulin. It is by similar processes that functional cell structures such as axons and dendrites are formed.

The bonding of the cell to the substrate occurs as a result of the properties of the extracellular matrix that is composed of lipids and collagen proteins. Certain protein types within the matrix such as fibronectin are believed to form strong bonds with the cells surrounding environment. As portions of the extracellular matrix come into contact with the substrate, oval foot like structures emerge of approximately  $1\mu m$  known as focal adhesion points. These adhesion points are generally extended from the cell by several nm and are structurally connected to actin bundles within the cell via transmembrane proteins. These adhesion points are believed collectively to form the ohmic seal observed between electrogenic cells and measurement electrodes. This seal has been determined experimentally within the range of  $100 \text{ k}\Omega$  to  $5 \text{ M}\Omega$  [4, 5].

Neurons tend to migrate in accordance to the surfaces and structures of their immediate surroundings. In the *in vivo* environment neural growth is directed by the glial cells which also serve to hold the cells in a fixed orientation to one another and relative to their functionality within the organism.

The study of dissected excitable cells is generally more predictable for this reason; mature hippocampal slices retain their glial enforced cellular structuring as do retinal dissections, allowing fixed positioning of the neurons over their experimental lifetime.

Cultures of isolated neurons have been grown specifically for in vitro study since the late 1960's. Typically such cultures, being absent of glial guidance, tend to grow randomly and with sub optimal connection rates between the synapses of neighbouring cells. When fully grown the cells may also continue their migration to a limited extent across the containing substrate.

## 1.2.4 The Layout of the Cell

A generic neural cell is shown in figure 1.3. The neuron is formed by the lipid by-layer and structural proteins that give it a shape that may be identified by several distinct compartments. The largest of these is the cell body or Soma. This is the main functional compartment of the cell and presents a spherical shape with a physical diameter of approximately  $10~\mu m$  to  $150~\mu m$ . The Soma contains the nucleus and the bulk of the functional proteins and organelles required for operation. Developing cells originate from spherical neuroblast precursors of the simple Soma shape and grow thin tubular extensions known as Axons and Dendrites as they form for functionality in their environment.

Dendrites are branching 'tree-like' processes and form the 'input' of the cell. The Dendrite branches form the input to the cell and contain chemical sensitive proteins at their tips that register neurotransmitter that is released locally by the axon terminals of other neurons. The signals activate a regenerative electrical response signal, known as the action potential that passes through the branches and the Soma into the axon. Neurons typically display many long complex Dendrite branches that form neurotransmitter sensitive connections with neighbouring neurons.

Figure 1.3

A typical neuron

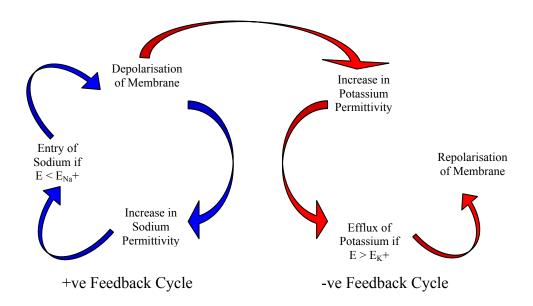

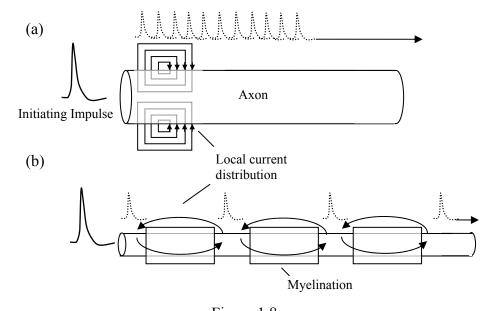

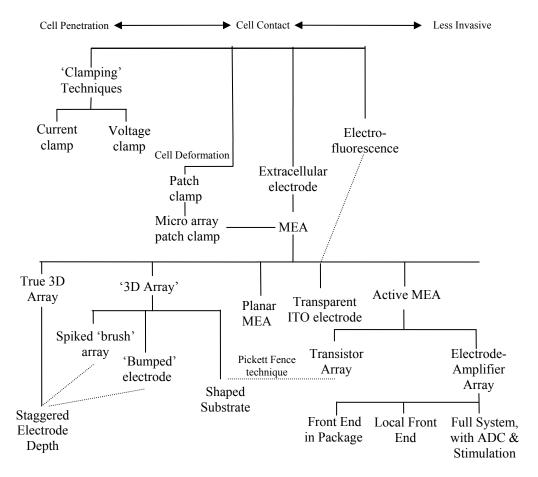

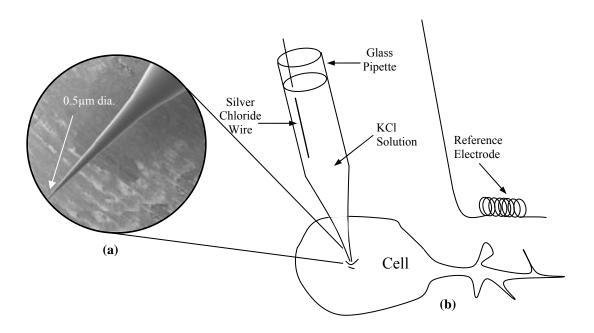

The axon is physically cylindrical in shape with diameters ranging from 1-20  $\mu$ m [6] in vertebrate neurons, depending on its connection or function, to 20  $\mu$ m - 1 mm in invertebrate cells. Axons can be found in lengths of several micrometres up to tens of centimetres. Axons are generally found grouped together in protective bundles or cords commonly described as 'nerves' e.g. the ulna and radial nerves in the human forearm. In these cords, protective tissue known as Myelin that is formed by Schwann cells, are wrapped around the constituent axons forming an insulating barrier to ionic flux across the cell membrane (see section 1.2.3). At frequent intervals of up to a few millimetres, gaps known as nodes of Ranvier between the neighbouring myelinated cells are present, and are important in the conduction process along the length of the axon for certain neurons.