# **Durham E-Theses**

#

BLACKHORSE-HULL, DAX,KYE

#### How to cite:

BLACKHORSE-HULL, DAX,KYE (2025) A Non-Isolated DC-DC Converter With An Ultra-High Voltage Ratio for Offshore Power Applications, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/16381/

#### Use policy

This work is licensed under a Creative Commons Public Domain Dedication 1.0 (CC0)

# A Non-Isolated DC-DC Converter With An Ultra-High Voltage Ratio for Offshore Power Applications

## Dax Blackhorse-Hull

A Thesis presented for the degree of Doctor of Philosophy

Department of Engineering

Durham University

United Kingdom

September 2025

#### **Abstract**

To maximise renewable energy generation, different forms of renewable power systems will need to be utilised. With this comes the opportunity to minimise capital expenditure and spatial usage via co-location. A promising co-location opportunity comes from the integration of the offshore wind farms with wave energy converters. Where floating or submerged wave energy converters are placed within the space between offshore wind turbines, to optimise marine spatial usage and utilise the same electrical infrastructure. To achieve this integration, the low output voltage of the wave energy converters would need to be stepped up to a medium voltage compatible with the inter-array voltage of an offshore wind farm. Conventionally, power converters which utilise step-up transformers have been adopted to produce similar forms of voltage conversion. While effective for offshore wind applications, complications arise from the mechanical constraints and environmental hazards associated with the use of a transformer on a floating or submerged platform. To study this issue, the work presented explored a strategy to achieve low to medium voltage conversion without the need for a step-up transformer. This strategy involved the exploration and development of transformerless DC-DC converters capable of high and ultra-high voltage conversion ratios, which produced an output voltage multiple times greater than the given input voltage.

Convertionally, to achieve a high voltage conversion ratio (> 10) in generic DC-DC converters, designs either require the use of excessive duty ratios (> 0.75) or the integration of voltage multiplying sub-circuits. Excessive duty ratios are often associated with reduced operational power efficiency, which limits the maximum amount of energy that may be extracted from a power system. Conversely, voltage multiplying sub-circuits increase circuit complexity while maintaining high operational efficiency. Therefore, voltage multiplication sub-circuits are often the chosen strategy to achieve high voltage conversion ratios when the maximisation of energy extraction is of high priority. To electrically integrate low-voltage wave generation technologies into medium-voltage offshore wind farm infrastructure, ultra-high voltage conversions (> 40) would be required. To achieve this, combinations of voltage multiplication techniques demonstrated within the literature were explored and evaluated for suitability.

Three transformerless DC-DC converters were sequentially conceptualised and devel-

oped. The operational analysis of all designs was presented and then subsequently validated via simulated and experimental demonstration. The novel continuous operation of a 1 kW scalable bipolar switched capacitor-based boost converter capable of a high voltage conversion ratio at a 98.2 % power efficiency was initially proposed. The experimental converter demonstrated a gain of  $\pm 10$  via the step up of a 100 V input into a  $\pm 1$  kV output. Following this, a scalable unipolar switch capacitor boost submodule was combined with a new method of scaling the voltage lift switched inductor topology to achieve ultra-high voltage conversion. The device demonstrated a voltage conversion ratio of 41 with a 100 V input and 4.1 kV output, at 97.5 % efficiency when operating at 1 kW. Finally, the bipolarity was reintegrated into the design to demonstrate an innovative DC-DC converter capable of a greater voltage conversion ratio than the previously demonstrated converters and those reported in the literature for continuous, not isolated, operation. The peak operating efficiency was recorded during a 2 kW test with an input of 100 V and output of ±4 kV where the converter achieved an efficiency of 95.7 %. To demonstrate the ability of the converter to achieve a continuous medium voltage output from a range of low voltage inputs, two DC sweeps were conducted at 1 kW. During the unipolar DC sweep, the positive output of the converter was referenced to the negative output. From this operation, the converter produced a single 4.7 kV output for an input voltage range of 40 - 125 V. During the bipolar DC sweep, the two outputs of the converter were referenced to a common ground. From this operation, the converter produced a positive and negative output of  $\pm 4.7$  kV output for an input voltage range of 70 - 200 V. When considering both unipolar and bipolar operation, the converter demonstrated a voltage conversion ratio range of 24 - 118.

Opportunities for power efficiency optimisation were identified based on the simulated and experimental findings. A particular focus was on the reduction of power and voltage losses in switched capacitor voltage multipliers. From this, key trade-offs were identified between both types of losses and capacitor sizes. The greatest unrealised pathway for power loss reduction originated from the active switching devices. A focus on the reduction of conduction-based losses led to the selection of devices with low on-state resistances. Due to this, the greatest proportion of power dissipation originated from switching-based losses. From this, strategies for the reduction of switching losses were identified as a key area for future research. Further opportunities for development were identified based on the experimental findings, strategies for integration into a solid-state transformer, allowing for bidirectional power flow, upscaling operation power and potential alternative applications were outlined and discussed.

## Declaration

The work in this thesis is based on research carried out at the Department of Engineering, Durham University, United Kingdom. No part of this thesis has been submitted elsewhere for any other degree or qualification and it is all my own work unless referenced to the contrary in the text.

#### Copyright © 2025 by Dax Blackhorse-Hull.

"The copyright of this thesis rests with the author. No quotations from it should be published without the author's prior written consent and information derived from it should be acknowledged".

## Acknowledgements

Firstly, my thanks to Professor Alton Horsfall for his guidance and support throughout this process and for ensuring we did not 'kill each other in the 3 years of the project'; And to Dr Nur Sarma for her thorough feedback on the project, including when to utilise semi-colons appropriately.

Secondly, my deepest appreciation to Amy Roberts for her patience and support whenever I hyperfocused on a task and forgot the need for basic human necessities such as food and sleep.

Thirdly, thanks to my immediate colleagues through the years, including: Dr Abdulrahman Alsafrani for his supporting efforts at the beginning of the PhD. Dr Lydia Robinson for both showing what is required of a PhD student and creating many origami figures to decorate my desk with. Theo McCarthy for providing many interesting crossword puzzles when we were supposed to be teaching labs together. Jakob Kay for always finding the optimum opportunity to start a 'highly meaningful' conversation when working in the lab. Dr Parvathy Mohanan Leela, for ensuring some semblance of sanity in the research group. Tearlach Horn, for being an excellent project student, asking all the questions that I would rather have ignored. I would also like to appreciate my colleagues both within the Aura CDT and Durham University for never getting tired of my morning response to 'how are you' with 'living the PhDream'

I'd also like to thank the technical staff for their support in prototype manufacture and troubleshooting in addition to their uplifting daily comments such as 'What you broke now?' and 'Oh no'.

Finally, I would like to thank Dr Oliver Morgan Clague for playing a significant role in my decision to undertake this PhD... I will never forgive you.

# Contents

ii

| Declaration                          | iv                                                                                                                                                       |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Acknowledgements                     | $\mathbf{v}$                                                                                                                                             |

| List of Figures                      | xi                                                                                                                                                       |

| List of Tables                       | xx                                                                                                                                                       |

| Dedication                           | xiv                                                                                                                                                      |

| Introduction                         | 1                                                                                                                                                        |

| 1.1 Wave and Wind Energy Integration | 2                                                                                                                                                        |

| 1.2 Research Aim                     | 5                                                                                                                                                        |

| 1.3 Thesis Structure                 | 6                                                                                                                                                        |

| Literature Review                    | 8                                                                                                                                                        |

| 2.1 Introduction                     | 8                                                                                                                                                        |

|                                      | Acknowledgements  List of Figures  List of Tables  Dedication x  Introduction  1.1 Wave and Wind Energy Integration  1.2 Research Aim  Literature Review |

${\bf Abstract}$

|   | 2.2 | DC-D   | C Converter Theory                                         | Ĝ  |

|---|-----|--------|------------------------------------------------------------|----|

|   |     | 2.2.1  | Conventional Boost Converter                               | 9  |

|   | 2.3 | DC-D   | C Converter Characteristics                                | 11 |

|   |     | 2.3.1  | Isolation                                                  | 11 |

|   |     | 2.3.2  | Polarity                                                   | 12 |

|   |     | 2.3.3  | Directionality                                             | 14 |

|   |     | 2.3.4  | Scalability                                                | 15 |

|   | 2.4 | Analys | sis of Innovative High-Gain DC-DC Topologies               | 15 |

|   |     | 2.4.1  | Cascaded                                                   | 16 |

|   |     | 2.4.2  | Coupled Inductor                                           | 19 |

|   |     | 2.4.3  | Switched Inductor                                          | 21 |

|   |     | 2.4.4  | Switched Capacitor                                         | 24 |

|   |     | 2.4.5  | Comparison of Discussed Topologies                         | 25 |

|   | 2.5 | Consid | deration of High Gain Topologies for Wind Wave Integration | 30 |

|   | 2.6 | Chapt  | er Summary                                                 | 34 |

| 3 | Des | ign an | d Analysis of a High-Gain Bipolar DC-DC Converter          | 36 |

|   | 3.1 | Introd | uction                                                     | 36 |

|   | 3.2 | Conve  | rter Modes of Operation                                    | 37 |

|   | 3.3 | Propos | sed Converter Analysis                                     | 40 |

|   |     | 3.3.1  | Steady State Operation                                     | 40 |

|   | 3.4 | Design | n Considerations                                           | 45 |

|   |     | 3.4.1  | Switching Device                                           | 46 |

|   |     | 3.4.2  | Input Inductor                                             | 47 |

|   |     | 3.4.3  | Output Capacitor Ladder                                    | 48 |

|   |     | 3.4.4  | Practical Estimated Gain and Maximum Duty Ratio            | 49 |

|   | 3.5 | Simula  | ation and Experimental Validation                        | 50 |

|---|-----|---------|----------------------------------------------------------|----|

|   |     | 3.5.1   | Input Stage Operation                                    | 51 |

|   |     | 3.5.2   | Output Stage Operation                                   | 52 |

|   |     | 3.5.3   | Switching Operation                                      | 58 |

|   |     | 3.5.4   | Efficiency at Different Power Operating Points           | 59 |

|   | 3.6 | Power   | Efficiency Analysis                                      | 60 |

|   |     | 3.6.1   | Input Stage Power Losses                                 | 60 |

|   |     | 3.6.2   | Output Stage Power Losses                                | 61 |

|   |     | 3.6.3   | Switch Power Losses                                      | 62 |

|   |     | 3.6.4   | Converter Efficiency                                     | 63 |

|   | 3.7 | Comp    | arison to other converters                               | 64 |

|   | 3.8 | Chapt   | er Summary of High-Gain Bipolar DC-DC Converter          | 66 |

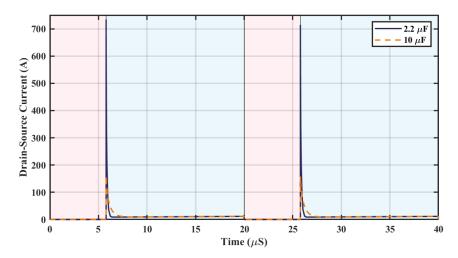

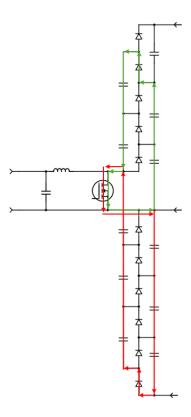

|   |     | 3.8.1   | Capacitor Size Converter Efficiency and Transient Spikes | 66 |

|   |     | 3.8.2   | Total Capacitive Voltage Against Output Voltage          | 68 |

|   |     | 3.8.3   | Conclusion                                               | 69 |

| 4 | Des | sign an | d Comparison of Ultra-High Gain DC-DC Boost Converter    | 70 |

|   | 4.1 | Introd  | uction                                                   | 70 |

|   | 4.2 | Propo   | sed Topology Specifications                              | 72 |

|   |     | 4.2.1   | Steady State Operation                                   | 75 |

|   | 4.3 | Design  | Considerations                                           | 82 |

|   |     | 4.3.1   | Input Inductor                                           | 83 |

|   |     | 4.3.2   | Output Capacitor Ladder                                  | 86 |

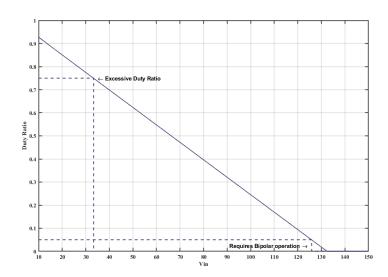

|   |     | 4.3.3   | Practical Estimated Gain and Maximum Duty Ratio          | 88 |

|   | 4.4 | Simula  | ated and Experimental Validation                         | 91 |

|   |     | 4.4.1   | Input Stage Operation                                    | 91 |

|   |     | 4.4.2  | Output Stage Operation                                       |

|---|-----|--------|--------------------------------------------------------------|

|   |     | 4.4.3  | Switching Operation                                          |

|   | 4.5 | Exper  | imental Designs Comparison                                   |

|   |     | 4.5.1  | Input Stage Operation                                        |

|   |     | 4.5.2  | Output Stage Operation                                       |

|   |     | 4.5.3  | Capacitor Operation                                          |

|   |     | 4.5.4  | Switching Operation                                          |

|   | 4.6 | Chapt  | er Summary of Ultra-High Gain DC-DC Boost Converter 108      |

|   |     | 4.6.1  | Power Supply Limitations and Input Current                   |

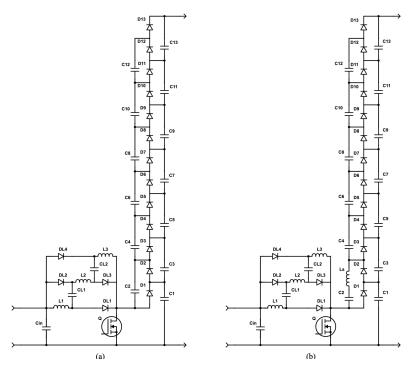

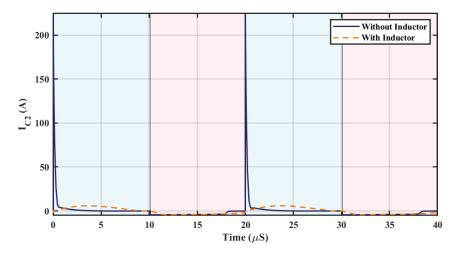

|   |     | 4.6.2  | Series Inductor Design Implementation                        |

|   |     | 4.6.3  | Conclusion                                                   |

| 5 | Des | ign an | d Analysis of an Ultra-High Gain Bipolar DC-DC Converter 112 |

|   | 5.1 | Introd | uction                                                       |

|   | 5.2 | Propo  | sed Topology                                                 |

|   |     | 5.2.1  | Modes of Operation                                           |

|   | 5.3 | Steady | y State Operation                                            |

|   | 5.4 | Design | Considerations                                               |

|   |     | 5.4.1  | Imbalanced Voltage Lift Switched Inductor                    |

|   |     | 5.4.2  | Capacitor Ladder                                             |

|   |     | 5.4.3  | Proposed Operation Range                                     |

|   |     | 5.4.4  | Practical Impact of Modes 3 and 4                            |

|   | 5.5 | Simula | ation and Experimental Validation                            |

|   |     | 5.5.1  | Single Duty Ratio, Single Input                              |

|   |     | 5.5.2  | Variable Duty Ratio, Variable Input                          |

|   | 5.6 | C1 +   | er Summary of Ultra-High Gain Bipolar DC-DC Converter 157    |

|              |              | 5.6.1   | Experimental Method to Achieve Anti-Phase Switching | . 157 |  |  |

|--------------|--------------|---------|-----------------------------------------------------|-------|--|--|

|              |              | 5.6.2   | Low to Medium Voltage Conversion Applications       | . 157 |  |  |

|              |              | 5.6.3   | Conclusion                                          | . 158 |  |  |

| 6            | Cor          | nclusio | ns and Further Research                             | 160   |  |  |

|              | 6.1          | Conclu  | usion                                               | . 160 |  |  |

|              | 6.2          | Future  | e Research                                          | . 161 |  |  |

|              |              | 6.2.1   | Implementation into Solid-State Transformer         | . 162 |  |  |

|              |              | 6.2.2   | Bidirectionality                                    | . 163 |  |  |

|              |              | 6.2.3   | Upscaling Power Output                              | . 164 |  |  |

|              |              | 6.2.4   | Alternative Applications                            | . 165 |  |  |

| Appendix 176 |              |         |                                                     |       |  |  |

|              | A            | Exper   | imental Setups                                      | . 176 |  |  |

|              | В            | Low C   | Capacitance Bipolar Experiment                      | . 181 |  |  |

|              | $\mathbf{C}$ | FWB     | VLSIMBC Unipolar DC Sweep Inputs                    | . 183 |  |  |

# List of Figures

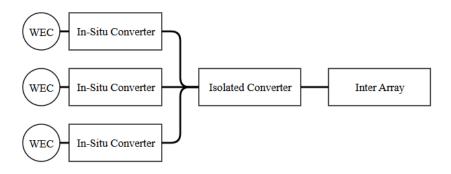

| 1.1 | wind-wave electrical integration outline                                     | 4  |

|-----|------------------------------------------------------------------------------|----|

| 1.2 | Block diagram of a proposed in situ converter where: (a) is a low voltage    |    |

|     | rectifier (b) a transformerless DC-DC converter, and (c) is a medium voltage |    |

|     | inverter                                                                     | 4  |

| 2.1 | Circuit diagram of a CBC                                                     | 9  |

| 2.2 | Block diagram of (a) Non-Isolated converter, (b) Isolated converter          | 12 |

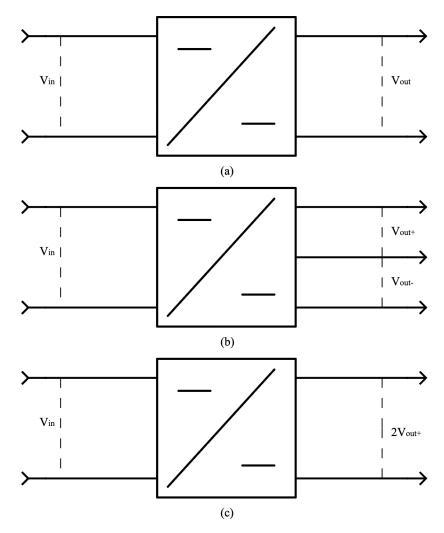

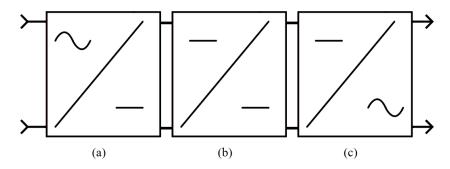

| 2.3 | Block diagram of (a) Unipolar converter, (b) Bipolar converter with 2 out-   |    |

|     | puts referenced to a common ground (c) Bipolar converter with positive       |    |

|     | output referenced to the negative output                                     | 13 |

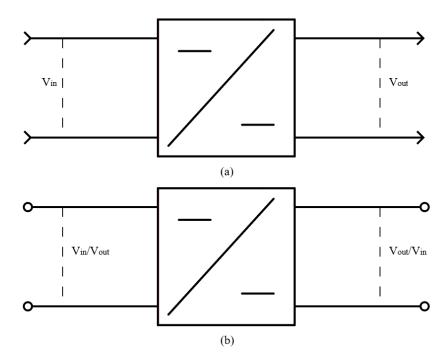

| 2.4 | Block diagram of (a) Unidirectional converter, (b) Bidirectional converter . | 14 |

| 2.5 | Block diagram of (a) Series scaled converter, (b) Parallel scaled converter  | 16 |

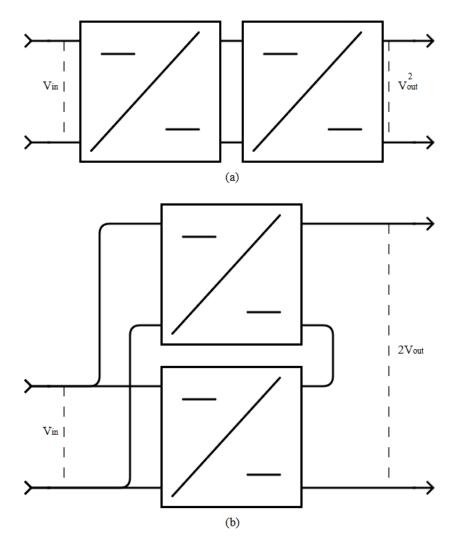

| 2.6 | Circuit diagram of a cascaded boost converter                                | 17 |

| 2.7 | Circuit diagram of quadratic boost converter                                 | 19 |

| 2.8 | Circuit diagram of a flyback converter                                       | 20 |

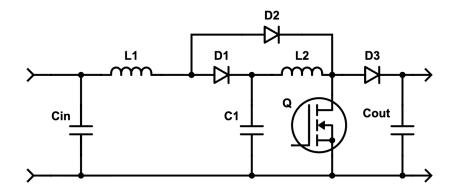

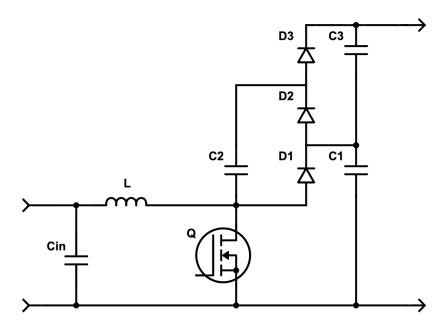

| 2.9  | Circuit diagram of a modified CBC with a 2-stage switched inductor            | 22 |

|------|-------------------------------------------------------------------------------|----|

| 2.10 | Circuit diagram of a modified CBC with a 2-stage voltage lift switched        |    |

|      | inductor                                                                      | 23 |

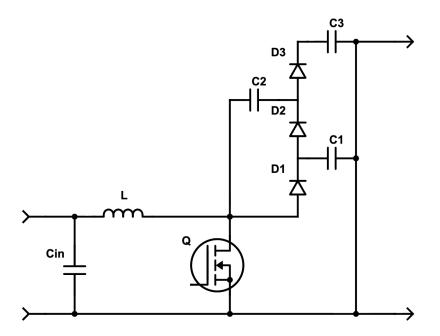

| 2.11 | Circuit diagram of a modified CBC with a 2-stage Cockcroft-Walton switched    |    |

|      | capacitor                                                                     | 25 |

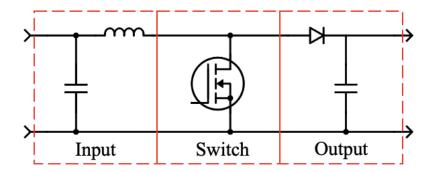

| 2.12 | Circuit diagram of a CBC separated into 3 operating stages                    | 31 |

| 2.13 | Circuit diagram of a 2-stage Dickinson switched capacitor                     | 33 |

| 2.14 | Circuit diagram of a 2-stage Hybrid Cockcroft-Walton Dickinson switched       |    |

|      | capacitor                                                                     | 33 |

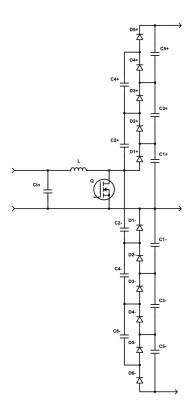

| 3.1  | Circuit diragram of a modified CBC with a combined $2N_C-1$ and inverting     |    |

|      | $2N_C$ topologies switched capacitor topology                                 | 38 |

| 3.2  | Equivalent non-inverting, $2N_C-1$ Cockcroft-Walton circuit for (a) Mode 1    |    |

|      | switch conduction, (b) Mode 2 switch blocking                                 | 39 |

| 3.3  | Equivalent inverting, $2N_C$ , Cockcroft-Walton circuit for (a) Mode 1 switch |    |

|      | conduction, (b) Mode 2 switch blocking                                        | 40 |

| 3.4  | Conduction modes of proposed converter with a 50 kHz switching frequency      |    |

|      | and output load of 2 k $\Omega$                                               | 48 |

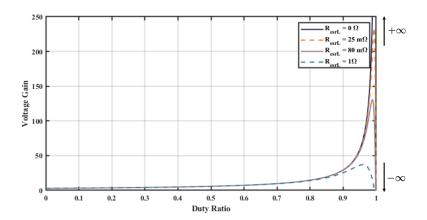

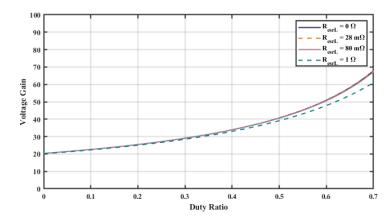

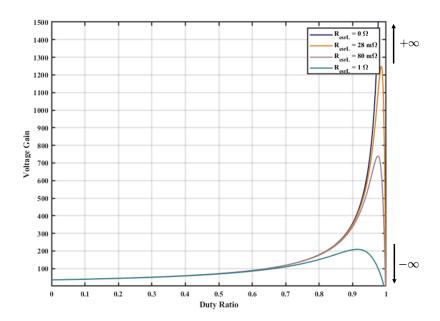

| 3.5  | Voltage gain against duty cycle for a 3-stage multilevel boost converter with |    |

|      | 10 $\mu F$ capacitors and 50 kHz switching frequency                          | 50 |

| 3.6  | Experimental Gate-Source voltage waveform of the proposed bipolar con-        |    |

|      | verter                                                                        | 51 |

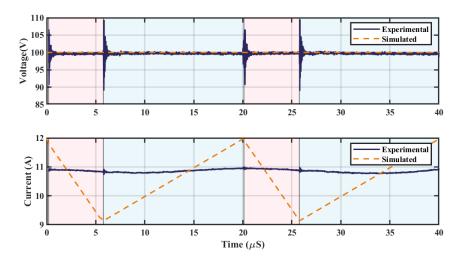

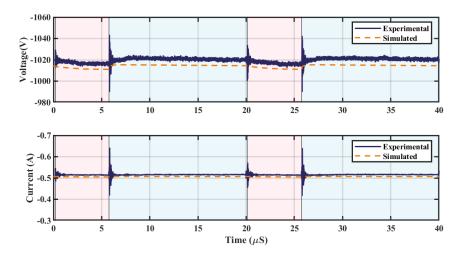

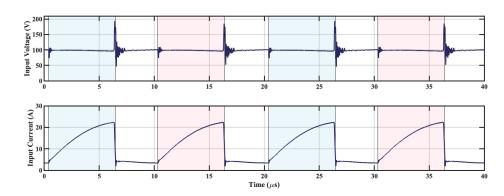

| 3.7  | Input voltage and current waveforms of the proposed bipolar converter. $$     | 52 |

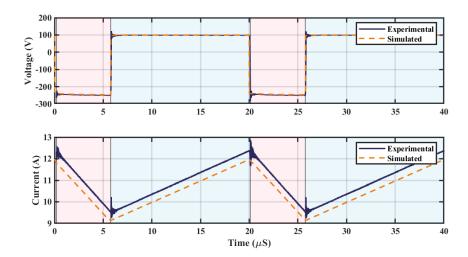

| 3.8  | Input inductor voltage and current waveforms of the proposed bipolar con-     |    |

|      | vonton                                                                        | 59 |

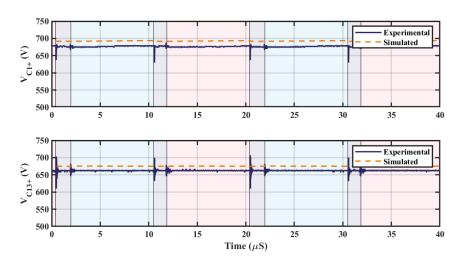

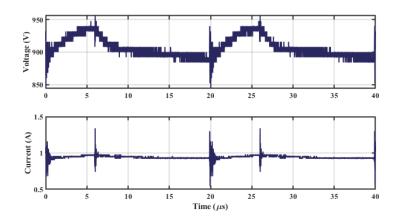

| 3.9  | Non-inverting output ladder voltage and current waveforms of the proposed        |    |

|------|----------------------------------------------------------------------------------|----|

|      | bipolar converter                                                                | 53 |

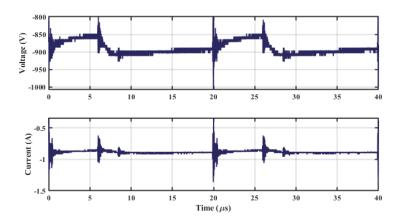

| 3.10 | Inverting output ladder voltage and current waveforms of the proposed            |    |

|      | bipolar converter                                                                | 54 |

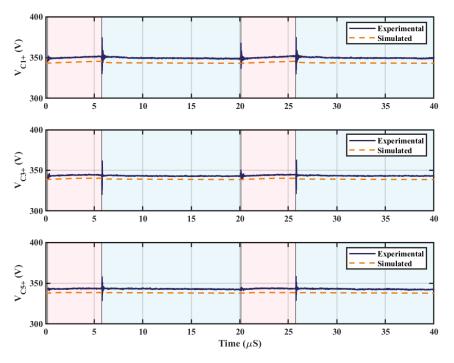

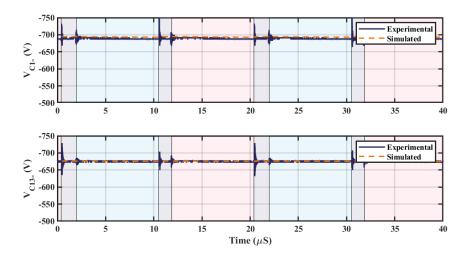

| 3.11 | Voltage waveforms across each non-inverting output capacitor of the pro-         |    |

|      | posed bipolar converter                                                          | 55 |

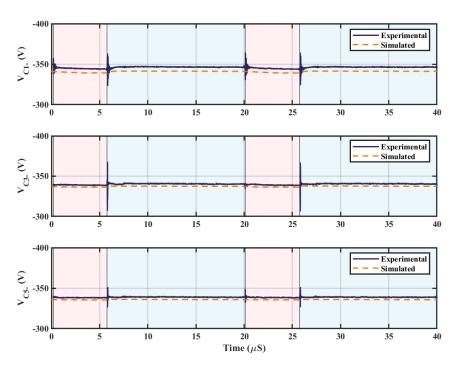

| 3.12 | Voltage waveforms across each inverting output capacitor of the proposed         |    |

|      | bipolar converter                                                                | 56 |

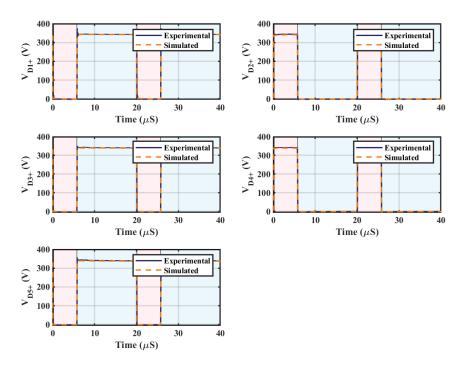

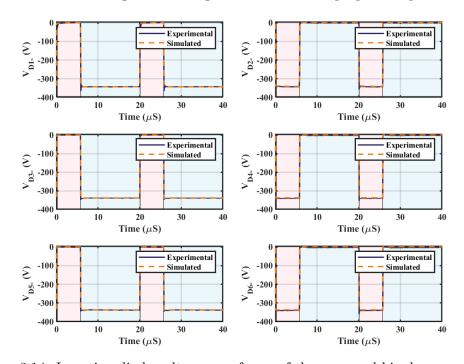

| 3.13 | Non-inverting diode voltage waveforms of the proposed bipolar converter          | 57 |

| 3.14 | Inverting diode voltage waveforms of the proposed bipolar converter              | 57 |

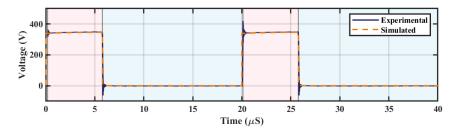

| 3.15 | Switch Drain-Source voltage waveform of the proposed bipolar converter           | 58 |

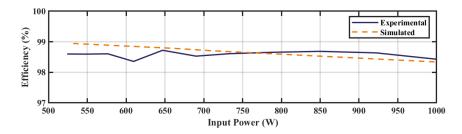

| 3.16 | Power efficiency of the proposed 3-stage bipolar multilevel boost converter      |    |

|      | from 520 W to 1 kW                                                               | 59 |

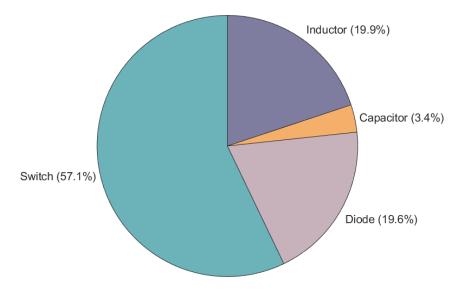

| 3.17 | Distribution of 20 W power dissipation within experimental 1 kW bipolar          |    |

|      | multi-level boost converter                                                      | 63 |

| 3.18 | Simulated switch current for proposed design with 2.2 $\mu F$ and 10 $\mu F$ ca- |    |

|      | pacitors                                                                         | 66 |

| 3.19 | Circuit diagram of the proposed bipolar converter with highlighted capaci-       |    |

|      | tor ladder current pathways during mode 1 operation                              | 67 |

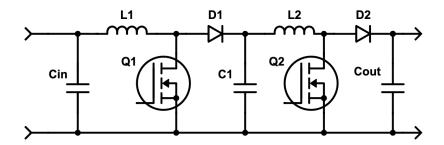

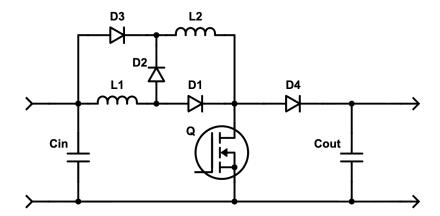

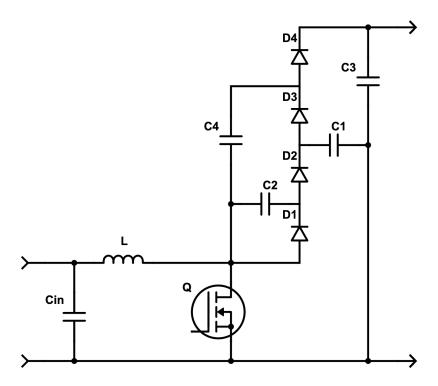

| 4.1  | Circuit diagram of VLSIMBC designs, (a) The capacitor ladder presented           |    |

|      | in Chapter 3 and (b) The capacitor ladder with a series inductor                 | 73 |

| 4.2  | Simulated current through the first stage smoothing capacitor, $C_2$ , for a     |    |

|      | VLSIMBC with and without a 5 $\mu F$ series inductor                             | 74 |

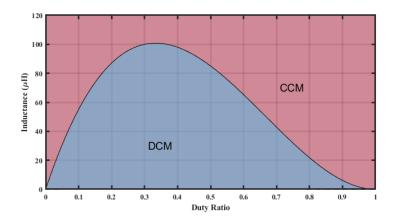

| 4 3  | Circuit diagram of the proposed VLSIMBC topology                                 | 75 |

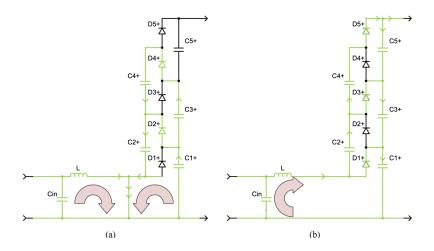

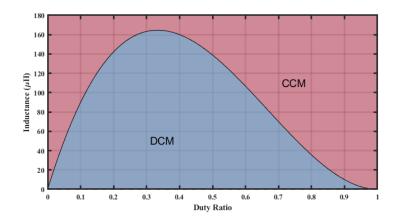

| 4.4  | Operating modes of the proposed VLSIMBC converter with a 50 kHz switch-                  |    |

|------|------------------------------------------------------------------------------------------|----|

|      | ing frequency and output load of 15 k $\Omega$                                           | 84 |

| 4.5  | Current and voltage waveforms of inductors with imbalance ratios of $N_{I2}=$            |    |

|      | 2 and $N_{I3}=3$                                                                         | 84 |

| 4.6  | Gain against high duty cycle for a 3 inductor stage, 7 capacitor stage,                  |    |

|      | voltage lift multilevel boost converter with 11 $\mu\mathrm{F}$ capacitors and 50 kHz    |    |

|      | switching frequency.                                                                     | 89 |

| 4.7  | Gain against duty cycle from 0 to $0.7$ for a 3 inductor stage, 7 capacitor              |    |

|      | stage, voltage lift multilevel boost converter with 11 $\mu\mathrm{F}$ capacitors and 50 |    |

|      | kHz switching frequency                                                                  | 89 |

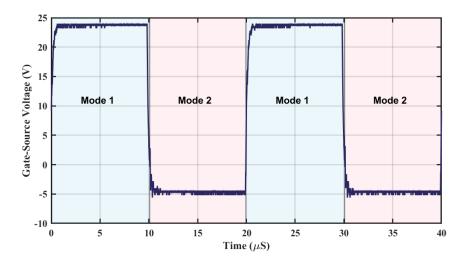

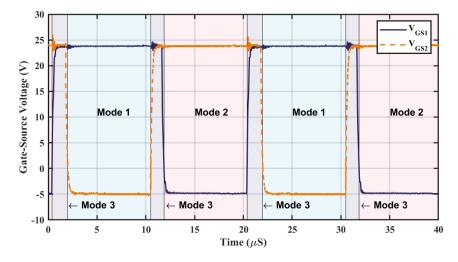

| 4.8  | Experimental Gate-Source voltage waveform of the proposed VLSIMBC                        | 92 |

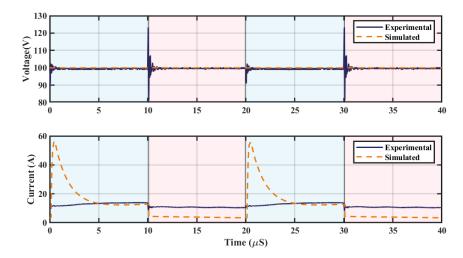

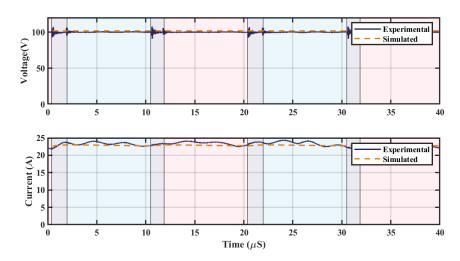

| 4.9  | Experimental and simulated input voltage and current waveforms of the                    |    |

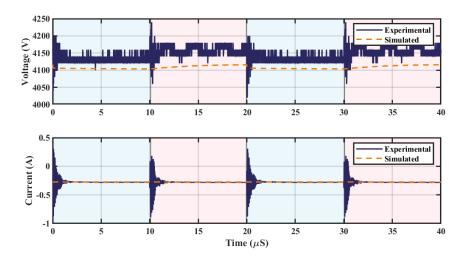

|      | VLSIMBC-HC design                                                                        | 93 |

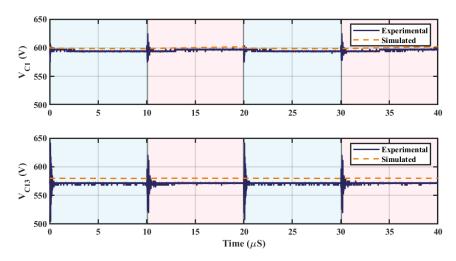

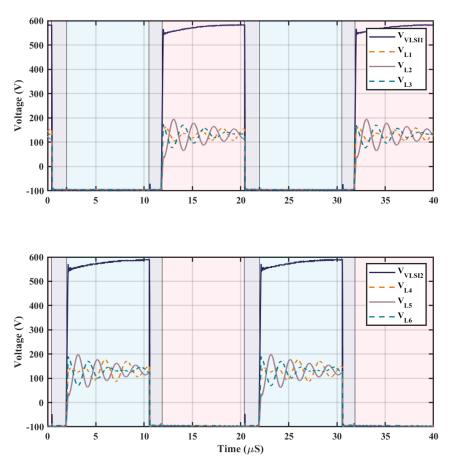

| 4.11 | Experimental and simulated voltage waveforms of voltage lift capacitors of               |    |

|      | the VLSIMBC-HC design                                                                    | 94 |

| 4.10 | Experimental voltage waveforms across input inductors and converter input                |    |

|      | stage for the VLSIMBC-HC design                                                          | 94 |

| 4.12 | Experimental and simulated voltage across the input stage of VLSIMBC-HL $$               |    |

|      | design                                                                                   | 95 |

| 4.13 | Input inductor voltage waveforms of the VLSIMBC-HC and VLSIMBC-                          |    |

|      | HCL designs                                                                              | 96 |

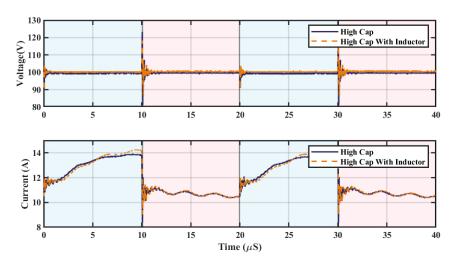

| 4.14 | Input inductor current waveforms of the VLSIMBC-HC and VLSIMBC-                          |    |

|      | HCL designs                                                                              | 97 |

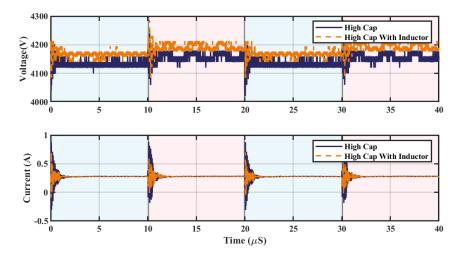

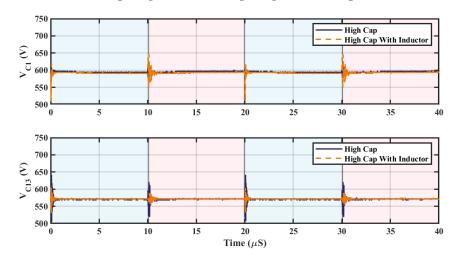

| 4.15 | Output voltage and current waveforms of the VLSIMBC-HC and VLSIMBC-                      |    |

|      | HCL designs                                                                              | 98 |

| 4.16 | Experimental and simulated voltage across the first and final stage output                                                                 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|

|      | capacitors of the VLSIMBC-HC design                                                                                                        |

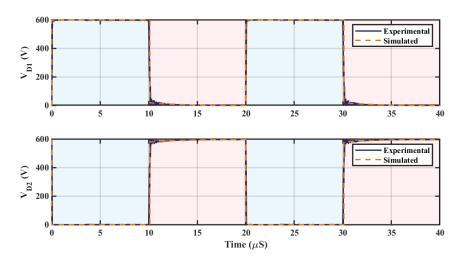

| 4.17 | Experimental and simulated voltage waveforms across $D_1$ and $D_2$ 99                                                                     |

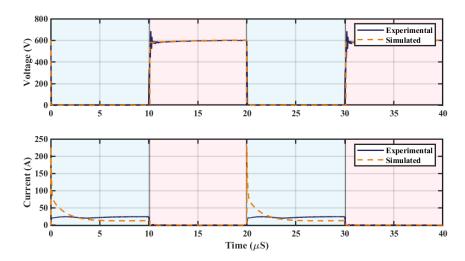

| 4.18 | Experimental and simulated drain-source voltage and current waveforms of                                                                   |

|      | the VLSIMBC-HC design                                                                                                                      |

| 4.19 | Input voltage and current waveforms of the VLSIMBC-HC and VLSIMBC-                                                                         |

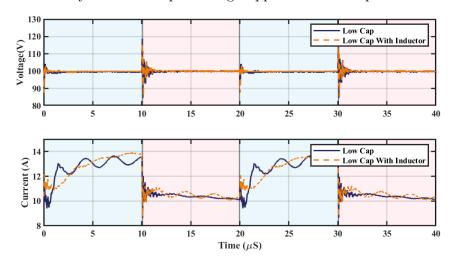

|      | HCL designs                                                                                                                                |

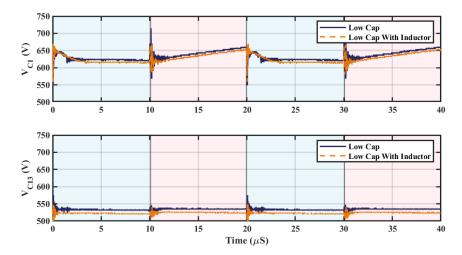

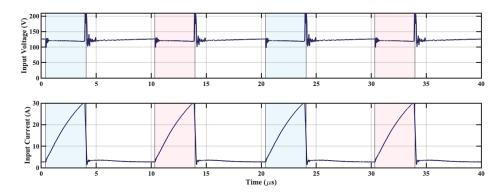

| 4.20 | Input voltage and current waveforms of the VLSIMBC-LC and VLSIMBC-                                                                         |

|      | LCL designs                                                                                                                                |

| 4.21 | Output voltage and current waveforms of the VLSIMBC-HC and VLSIMBC- $$                                                                     |

|      | HCL designs                                                                                                                                |

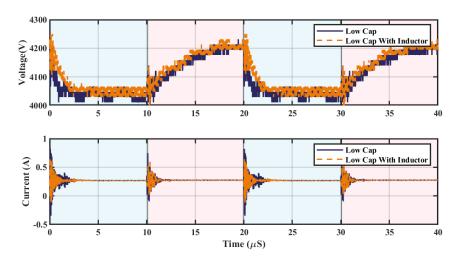

| 4.22 | Output voltage and current waveforms of the VLSIMBC-LC and VLSIMBC- $$                                                                     |

|      | LCL designs                                                                                                                                |

| 4.23 | Output voltage waveforms from the first and last stage output capacitors                                                                   |

|      | of the VLSIMBC-HC and VLSIMBC-HCL designs                                                                                                  |

| 4.24 | Output voltage waveforms from the first and last stage output capacitors                                                                   |

|      | of the VLSIMBC-LC and VLSIMBC-LCL designs                                                                                                  |

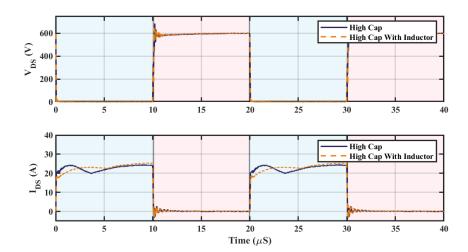

| 4.25 | Drain-Source voltage and current waveforms of the VLSIMBC-HC and                                                                           |

|      | VLSIMBC-HCL designs                                                                                                                        |

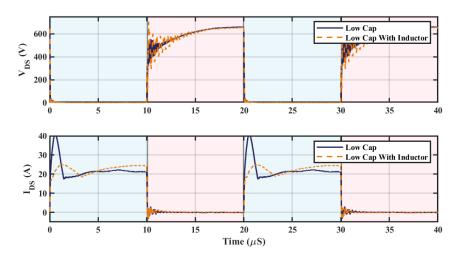

| 4.26 | $\label{eq:control_problem} \label{eq:control_problem} \mbox{Drain-Source voltage and current waveforms of the VLSIMBC-LC and VLSIMBC-LC}$ |

|      | LCL designs                                                                                                                                |

| 4.27 | Input voltage waveform of the proposed VLSIMBC converter without de-                                                                       |

|      | coupling capacitors                                                                                                                        |

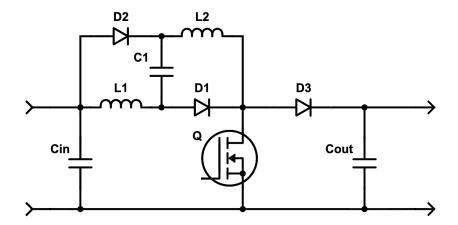

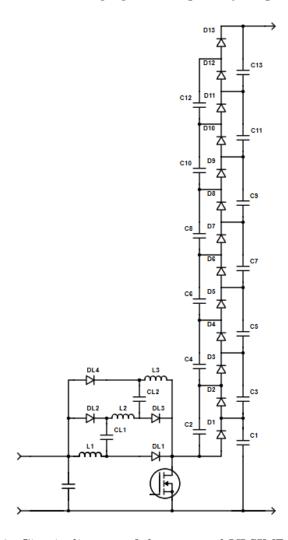

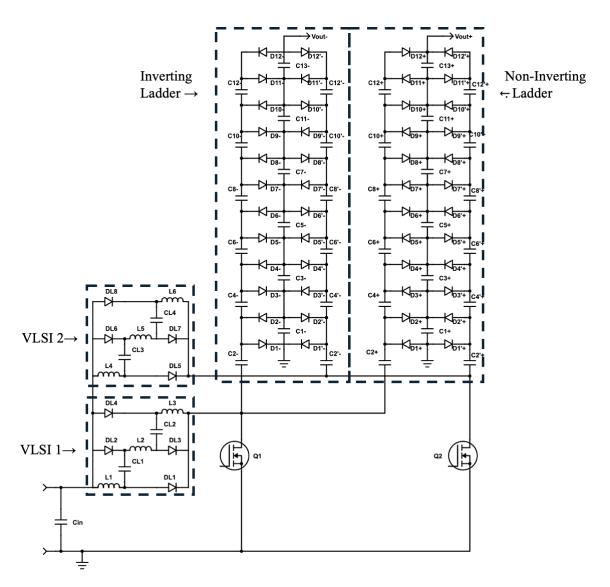

| 5.1  | Circuit diagram of proposed topologies full wave bipolar voltage lift switched                                                             |

|      | inductor multi-level boost converter (FWBVLSIMBC)                                                                                          |

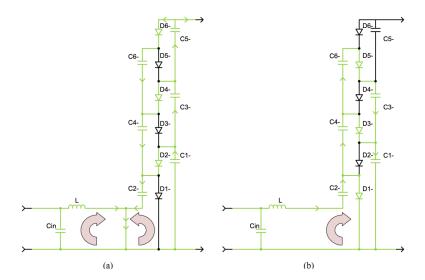

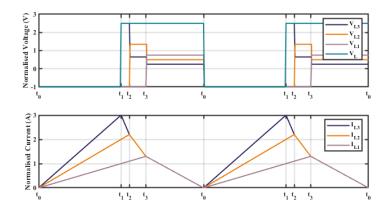

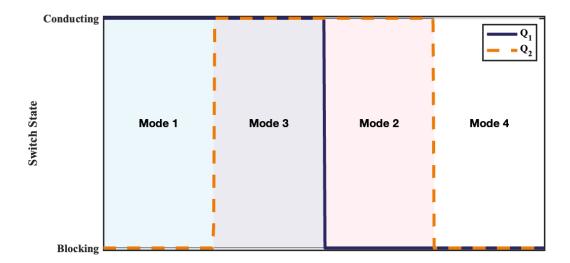

| 5.2  | FWBVLSIMBC switch modes of operation                                                 |

|------|--------------------------------------------------------------------------------------|

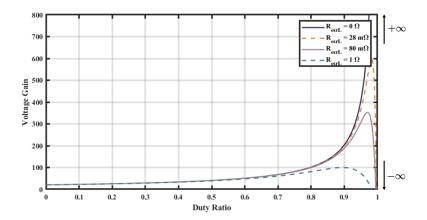

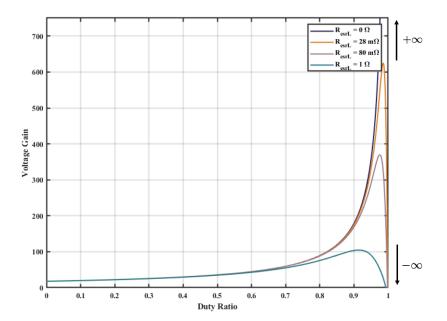

| 5.3  | Voltage gain of a single output capacitor ladder against duty ratio for a $3$        |

|      | inductor stage, 6 capacitor stage, FWBVLSIMBC with 2.2 $\mu\mathrm{F}$ capacitors    |

|      | and 50 kHz switching frequency                                                       |

| 5.4  | Voltage gain against duty ratio for a 3 inductor stage, 6 capacitor stage,           |

|      | FWBVLSIMBC with 2.2 $\mu\mathrm{F}$ capacitors and 50 kHz switching frequency $$ 127 |

| 5.5  | Experimental Gate-Source voltage waveforms of the proposed FWBVL-                    |

|      | SIMBC topology                                                                       |

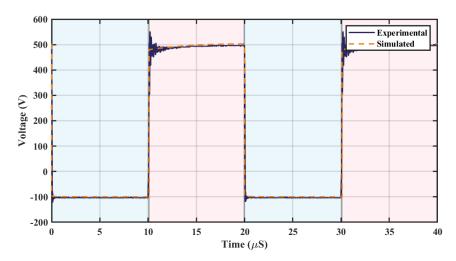

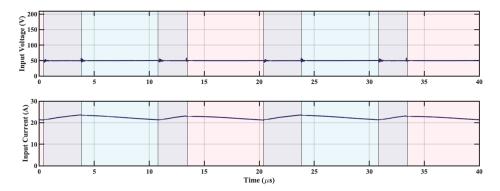

| 5.6  | Experimental and simulated input voltage and current waveforms of the                |

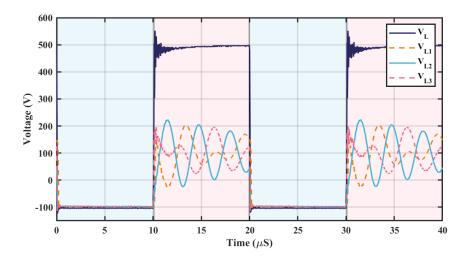

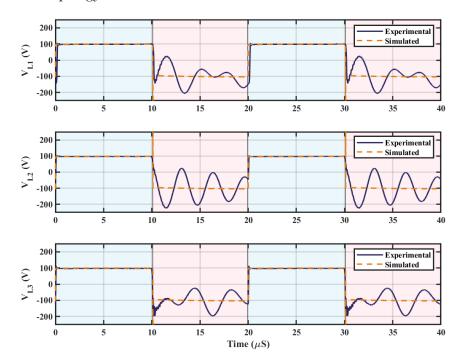

|      | proposed FWBVLSIMBC topology                                                         |

| 5.7  | Experimental inductor voltage waveforms of the proposed FWBVLSIMBC                   |

|      | topology                                                                             |

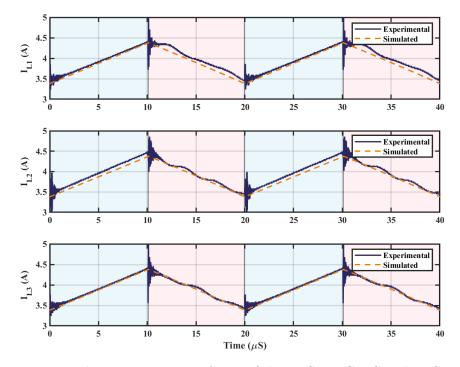

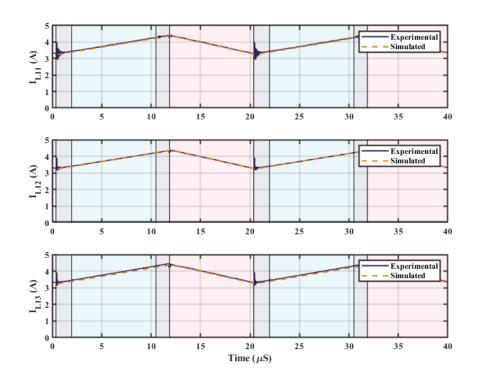

| 5.8  | Experimental inductor current waveforms of the proposed FWBVLSIMBC                   |

|      | topology                                                                             |

| 5.9  | Experimental inductor current waveforms of the L2 VLSI stage within the              |

|      | proposed FWBVLSIMBC topology                                                         |

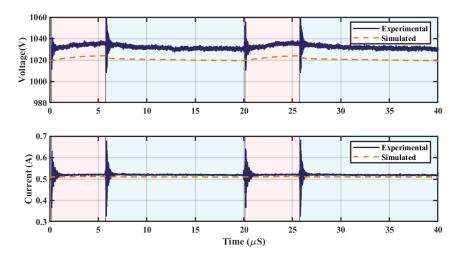

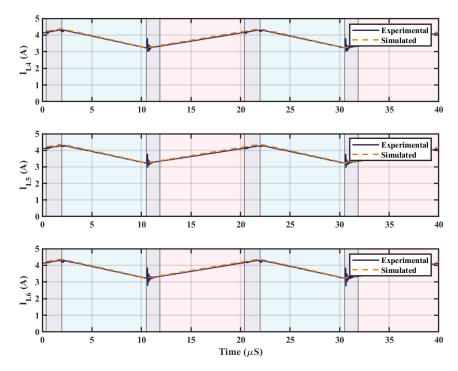

| 5.10 | Experimental and simulated positive output voltage and current waveforms             |

|      | of the proposed FWBVLSIMBC topology                                                  |

| 5.11 | Experimental and simulated negative output voltage and current waveforms             |

|      | of the proposed FWBVLSIMBC topology                                                  |

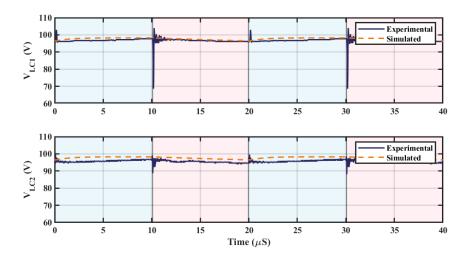

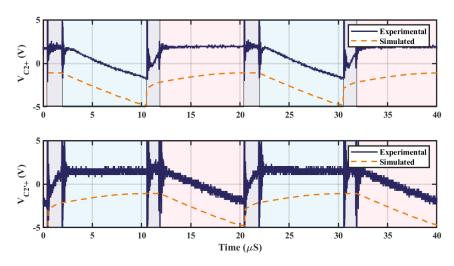

| 5.12 | Experimental and simulated first and last stage non-inverting ladder capac-          |

|      | itor voltage waveforms of the proposed FWBVLSIMBC topology 137                       |

| 5.13 | Experimental and simulated first and last stage inverting ladder capacitor           |

|      | voltage waveforms of the proposed FWBVLSIMBC topology                                |

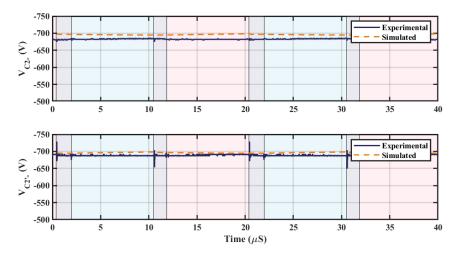

| 5.14 | Experimental and simulated voltage across the first stage diodes of the            |     |

|------|------------------------------------------------------------------------------------|-----|

|      | proposed FWBVLSIMBC non-inverting output capacitor ladder                          | 140 |

| 5.15 | Experimental and simulated voltage across the first stage diodes of the            |     |

|      | proposed FWBVLSIMBC inverting output capacitor ladder                              | 141 |

| 5.16 | Experimental and simulated left and right non-inverting first stage capacitor      |     |

|      | voltage waveforms of the proposed FWBVLSIMBC topology                              | 142 |

| 5.17 | Experimental and simulated left and right inverting first stage capacitor          |     |

|      | voltage waveforms of the proposed FWBVLSIMBC topology                              | 143 |

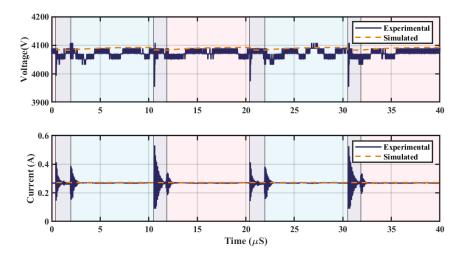

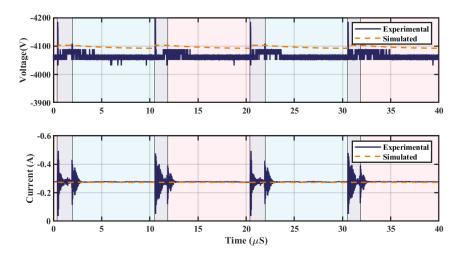

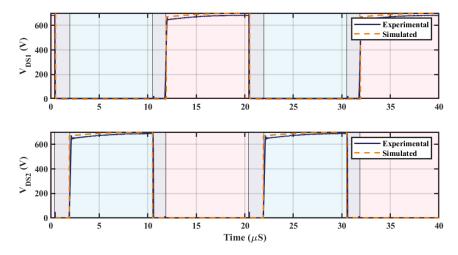

| 5.18 | Experimental and simulated Drain-Source voltage waveforms of the pro-              |     |

|      | posed FWBVLSIMBC topology.                                                         | 144 |

| 5.19 | Simulated Drain-Source current waveforms of the proposed FWBVLSIMBC                |     |

|      | topology                                                                           | 145 |

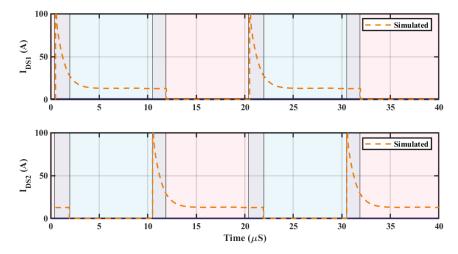

| 5.20 | Calculated distribution of the 103 W power dissipation within Experimental         |     |

|      | 2 kW FWBVLSIMBC                                                                    | 149 |

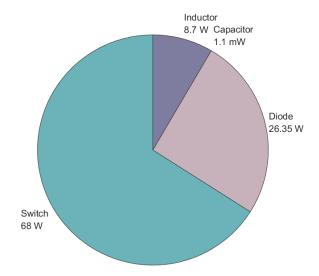

| 5.21 | Analytical parameters of the proposed topology to achieve 4.7 kV $_{DC}$ during    |     |

|      | unipolar operation at 1 kW                                                         | 151 |

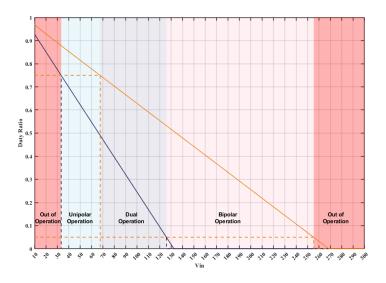

| 5.22 | Operational range of the proposed FWBVLSIMBC topology with target                  |     |

|      | output voltage of 4.7 kV $_{DC}$                                                   | 152 |

| 5.23 | Duty ratio required to achieve an output of 4.7 $\mathrm{kV}_{DC}$ in the proposed |     |

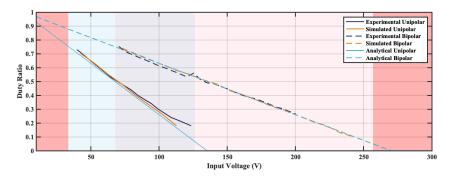

|      | FWBVLSIMBC topology operating at 1 kW                                              | 154 |

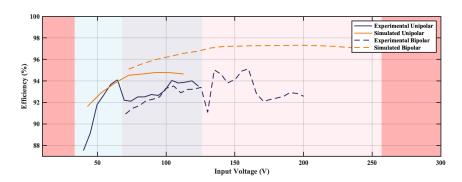

| 5.24 | Efficiency for a given input voltage with an output of 4.7 ${\rm kV}_{DC}$ in the  |     |

|      | proposed FWBVLSIMBC topology operating at 1 kW                                     | 155 |

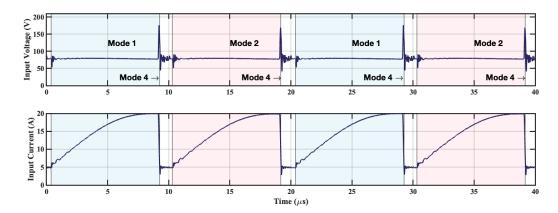

| 5.25 | Input Current ripple the proposed FWBVLSIMBC topology, with an input               |     |

|      | of 80 V and Output of 4.7 kVpc                                                     | 156 |

| 6.1 | Block diagram of a potential use of proposed DC-DC in a SST where: (a)                 |

|-----|----------------------------------------------------------------------------------------|

|     | Is a low voltage rectifier (b) Is the proposed DC-DC converter, and (c) Is a           |

|     | medium voltage inverter                                                                |

| 6.2 | Circuit diagram of a bidirectional switched inductor boost converter $\dots 164$       |

| 6.3 | Circuit diagram of a 3-stage Cockcroft-Walton boost converter with parallel            |

|     | output stages                                                                          |

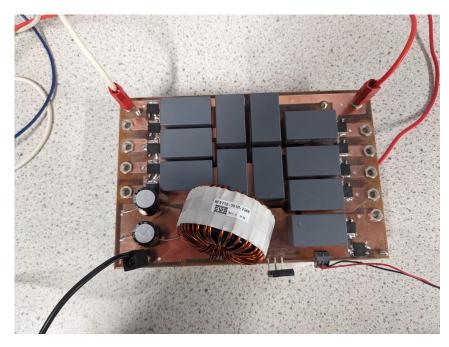

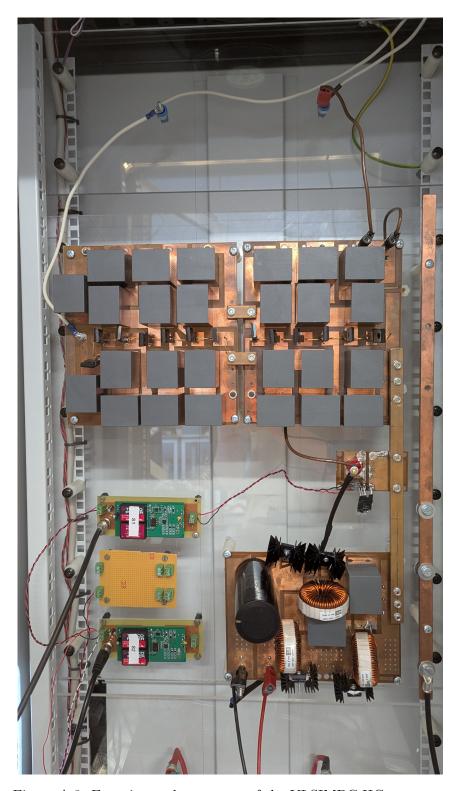

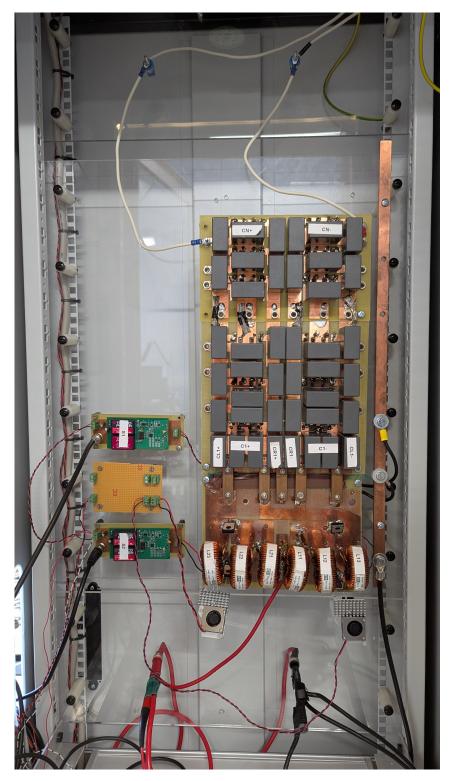

| A.1 | Experimental set-up utilised for converter characterisations 177                       |

| A.2 | Experimental prototype of the bipolar multi-level boost converter 177                  |

| A.3 | Experimental prototype of the VLSIMBC-HC converter                                     |

| A.4 | Experimental prototype of the VLSIMBC-LC converter                                     |

| A.5 | Experimental prototype of the FWBVLSIMBC converter                                     |

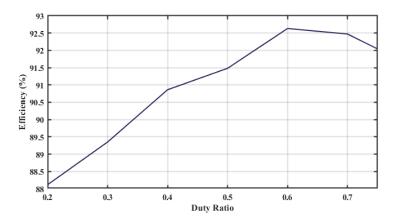

| B.1 | Experimental efficiency against duty ratio for a 2.2 $\mu F$ bipolar multilevel        |

|     | boost converter operating at 50 kHz                                                    |

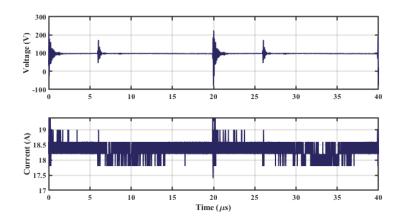

| B.2 | Experimental input voltage and current waveforms for a $2.2\mu$ F bipolar              |

|     | multilevel boost converter operating at 50 kHz                                         |

| В.3 | Experimental non-inverting output voltage and current waveforms for a                  |

|     | 2.2 $\mu F$ bipolar multilevel boost converter operating at 50 kHz $\dots 182$         |

| B.4 | Experimental inverting output voltage and current waveforms for a 2.2 $\mu \mathrm{F}$ |

|     | bipolar multilevel boost converter operating at 50 kHz                                 |

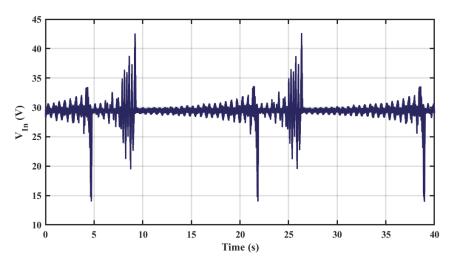

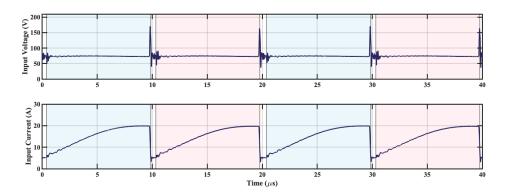

| C.1 | Experimental input voltage and current waveform of FWBVLSIMBC vari-                    |

|     | able duty ratio, variable input test where $V_{in} = 50 \text{ V} \dots 183$           |

| C.2 | Experimental input voltage and current waveform of FWBVLSIMBC vari-                    |

|     | able duty ratio, variable input test where $V_{in} = 75 \text{ V} \dots 183$           |

| C.3 | Experimental input voltage and current waveform of FWBVLSIMBC vari-                    |

|     | able duty ratio, variable input test where $V_{in} = 100 \text{ V} \dots \dots 184$    |

| C.4 | Experimental input voltage and current waveform of FWBVLSIMBC vari-                   |     |

|-----|---------------------------------------------------------------------------------------|-----|

|     | able duty ratio, variable input test where $V_{in} = 125 \text{ V} \dots \dots \dots$ | 184 |

# List of Tables

| 2.1 | Comparison of discussed voltage multiplication techniques based on identi-      |

|-----|---------------------------------------------------------------------------------|

|     | fied key characteristics                                                        |

| 2.2 | Voltage conversion ratio, point of interaction, maximum switch voltage and      |

|     | component complexity of the discussed relevant topologies                       |

| 3.1 | Experimental parameters of the proposed multi level boost converter 51          |

| 3.2 | Comparison of the proposed multi level boost converter with other topologies 65 |

| 4.1 | Experimental parameters of the proposed VLSIMBC high capacitance de-            |

|     | signs                                                                           |

| 4.2 | Experimental parameters of the proposed VLSIMBC low capacitance de-             |

|     | signs                                                                           |

| 5.1 | Non-inverting capacitor ladder output diode bias under different modes of       |

|     | operation in the FWBVLSIMBC                                                     |

| 5.2 | Inverting capacitor ladder output diode bias under different modes of oper-     |

|     | ation in the FWBVLSIMBC                                                         |

|     |                                                                                 |

| 5.3 | Experimental component parameters of the FWBVLSIMBC 129                     |

|-----|-----------------------------------------------------------------------------|

| 5.4 | Experimental parameters for the single duty ratio single input study of the |

|     | FWBVLSIMBC                                                                  |

| 5.5 | Comparison of the proposed FWBVLSIMBC converter with other topolo-          |

|     | gies reported in the literature                                             |

| 5.6 | Experimental parameters for the variable duty ratio, variable input study   |

|     | of the FWBVLSIMBC                                                           |

| A.1 | Experimental Measurement Equipment List                                     |

#### Nomenclature

#### Symbols

- $\eta$  Efficiency

- C Capacitance

- D Duty Ratio

- f Switching Frequency

- I Current

- L Inductance

- N Number of

- P Power

- R Resistance

- V Voltage

#### List of Acronyms

- AC Alternating Current

- ADC Analogue to Digital Converter

- BCM Boundary Conduction Mode

- CBC Conventional Boost Converter

- CCM Continuous Conduction Mode

- DCM Discontinuous Conduction Mode

- DC Direct Current

- ${\bf FWBVLSIMBC\ \ Full-Wave\ Bipolar\ Voltage\ Lift\ Switched\ Inductor\ Multi-level\ Boost\ Converter}$

- FWCW Full-Wave Cockcroft-Walton

- IEC International Electrotechnical Commission

- IGBT Insulated Gate Bipolar Transistor

- LVAC Low Voltage Alternating Current

- LVDC Low Voltage Direct Current

- MBC Multi-level Boost Converter

- MOSFET Metal Oxide Semiconductor Field-Effect Transistor

MVAC Medium Voltage Alternating Current

MVDC Medium Voltage Direct Current

PV Photovoltaic

PWM Pulse Width Modulation

SiC Silicon Carbide

SI Switched Inductor

SST Solid-State Transformer

VLSIMBC-HCL Voltage Lift Switched Inductor Multi-level Boost Converter High Capacitance Series Inductor

VLSIMBC-HC Voltage Lift Switched Inductor Multi-level Boost Converter High Capacitance

VLSIMBC-LCL Voltage Lift Switched Inductor Multi-level Boost Converter Low Capacitance Series Inductor

VLSIMBC-LC Voltage Lift Switched Inductor Multi-level Boost Converter Low Capacitance

VLSIMBC Voltage Lift Switched Inductor Multi-level Boost Converter

VLSI Voltage Lift Switched Inductor

WEC Wave Energy Converter

|                                                              | Dedication |

|--------------------------------------------------------------|------------|

|                                                              |            |

| Dedicated to my wonderful partner Amy and living the PhDream |            |

|                                                              |            |

# CHAPTER 1

#### Introduction

Innovations in the renewable energy sectors have led to a surge in the development of DC-DC converter topologies to accommodate new generator designs with the aim to maximise power extraction [1]. To minimise transmission-based power losses, high-gain, high-efficiency power converters have been a key component for the integration of renewable energy systems into distribution networks [2–4].

With the expansion of the offshore wind sector has led to larger capacity wind farms. With this comes the opportunity to exploit the existing electrical infrastructure for use in alternative renewable generation [5]. Wave energy converters (WEC) transform the kinetic energy of waves into electrical energy [6, 7]. The technology has yet to reach maturity due to a diverse set of challenges, including: development of power-efficient designs, optimising power extraction from high peak, low average power of waves and large initial costs [6–8]. While many WEC projects focus on efficient and scalable designs [9–12], work to explore generalised integration solutions of WECs into the distribution grid has

been limited. One potential solution is to integrate WECs with offshore wind farms, utilising the space between wind turbines for placement and electrically connecting to established infrastructure [5]. This approach would optimise marine spatial use and reduce capital expenditure in comparison to the development of 2 separate renewable energy installations.

## 1.1 Wave and Wind Energy Integration

As the offshore wind sector is reaching maturity and the wave energy sector is still emerging, any integration between the technologies would require wave technology to adapt to the established requirements of wind technology. Therefore, to integrate WEC platforms into offshore wind farms, the WEC power take-off system must be compatible with the current and ideally future infrastructure of offshore wind farms.

Within the UK offshore wind farm arrays primarily operate at 33 kV $_{\rm AC}$ , with discussion of future wind farms operating at 66 kV $_{\rm AC}$  [13]. Additionally, due to their increased efficiency and safety, DC collection networks are becoming an appealing future alternative for offshore wind farm infrastructure [14]. Due to the relative immaturity of the sector, there has been no convergence on operating voltages for WEC platforms. Current discussion within the literature outlines a range of low voltage operating points ranging from 40 V $_{\rm AC}$  to 1 kV $_{\rm AC}$  [15–17]. Of these, the WEC platforms may be divided into medium voltage platforms, which operate around 1 kV $_{\rm AC}$  [17] and low voltage platforms, which operate in the range of 40 V $_{\rm AC}$  - 240 V $_{\rm AC}$  [15,16]. To achieve effective wind-wave integration, the WEC output must be stepped up into a voltage comparable to a given offshore wind farm array voltage.

For high voltage step-up applications, including both AC & DC networks, designs commonly rely on transformers with large voltage step-up ratios. While demonstrably

effective in offshore wind applications, and useful for both galvanic isolation, offering circuit protection; and simple voltage conversion method, only requiring an AC or pseudo-AC input. Transformer-based designs are often subject to leakage inductance, which generates overvoltage spikes that reduce component reliability and lifespan [18]. The mechanical stress of the transformer, related to the size and mass of the component, can introduce further design constraints [19]. For WECs, mechanical stress may impede technological development as designs would be required to ensure both enough buoyancy in floating platforms and adequate shielding in the event of device failure to prevent transformer oil leakage. A simple solution would be to utilise a separate platform for power conversion, relieving the WEC of the constraints of the transformer, while also allowing the use of pre-existing, transformer-based technology. However, such a design would be subject to transmission based power losses from the low-voltage, high-current output of WECs, leading to conduction losses through connecting cables, reducing the power extracted and overall system efficiency. Therefore, to aid in the maximisation of power extraction, some form of voltage conversion is required within the WEC platform. With this, transformerless high-gain DC-DC converters offer a potential, physically small, lightweight solution.

While transformers within a WEC platform are not ideal, the galvanic isolation and associated circuit protections are paramount in offshore wind farms. This issue may partially be solved with the use of currently utilised transformer based power converters. Galvanically isolated designs, capable of stepping up the MVAC output of wind turbines, may be used as an integration point for multiple WEC platforms into the electrical network of offshore wind farms. This strategy would be effective for a medium voltage WEC platform, because the output voltage is similar to an offshore wind turbine. Low voltage WEC platforms would require an additional voltage conversion stage to achieve an inte-

grable voltage. Figure 1.1 outlines a block diagram of how low voltage WEC platforms may be integrated into offshore wind farm infrastructure, utilising an in situ converter to achieve a medium voltage, and an isolated converter to step up into a compatible interarray voltage.

Figure 1.1: Wind-wave electrical integration outline

In this paradigm, the power converter within the WEC would only be required to step up the WEC output voltage to the output voltage of an offshore wind turbine rather than the inter-array voltage. Additionally, the transformer based power converter would not physically impede the connected WEC platforms, mitigating design constraints.

To realise the highlighted in-situ LVAC-MVAC converter, power electronic circuits may be utilised as shown in Figure 1.2

Figure 1.2: Block diagram of a proposed in situ converter where: (a) is a low voltage rectifier (b) a transformerless DC-DC converter, and (c) is a medium voltage inverter.

Of the 3 stages low voltage rectification and medium voltage inversion are relatively well understood [20–22], whereas transformerless LVDC-MVDC are less well researched.

With this comes the opportunity to explore the potential of ultra-high-gain DC-DC to achieve low to medium voltage conversion.

### 1.2 Research Aim

This project sought to explore the potential of transformerless DC-DC converters for LVDC to MVDC conversion as an alternative to conventional step-up transformers. The project objective was the development of a DC-DC converter that could step-up a range of low voltage inputs similar to reported WEC outputs, into an output voltage that could be inverted into an MVAC comparable to that generated in offshore wind turbines. With this, a specific target output of  $4.7 \text{ kV}_{DC}$  was identified, as this is the required voltage to achieve 3.3 kV<sub>AC</sub> inversion, assuming the utilisation of a standard 3-phase inverter circuit. This voltage would be compatible with the power converters proposed as a WEC integration point. As identified, different low-voltage WEC platforms have reported operation in the range of 40 V to 240 V. After rectification, this voltage range would be approximately 38 V to 230 V, when assuming a full wave 3-phase rectifier. This translates to a voltage conversion ratio range of 20 - 124 to achieve an output of 4.7 kV<sub>DC</sub>. When discussing high-gain transformerless DC-DC converters, a voltage conversion ratio of 10 [23–26] is considered high, with little research present exploring voltage conversion ratios above 20, which has been termed ultra-high [12]. Therefore, this project aimed to demonstrate a proof of concept device, with a voltage conversion ratio range equal to the ratios required for low voltage WEC platforms to achieve 4.7 kV $_{DC}$ .

#### 1.3 Thesis Structure

The thesis is organised into the following:

Chapter 2 explores innovative DC-DC converter voltage multiplication techniques capable of high step-up voltage conversion described in the literature. These techniques are discussed based on key characteristics, including isolation, output polarity, directionality of power flow and scalability. The techniques are evaluated to determine suitable designs to achieve the project objective.

Chapter 3 explores the potential of a high-gain single switch, bipolar converter operating with a continuous output. The design and analysis of a scalable, non-isolated, bipolar, switched capacitor-based topology, capable of producing a voltage conversion ratio of  $\pm$  10 with inherent voltage balancing within both the positive and negative output, are presented. The experimental characterisation of a 1 kW laboratory demonstrator is presented to experimentally validate simulated results and theoretical analysis.

Chapter 4 primarily explores the scalability of a unipolar variant of the switched capacitor design presented in Chapter 3. Additionally, a voltage lift switched inductor-based topology is identified and examined based on scalability and ability to achieve high voltage conversion ratios. A 4 kV voltage lift switched inductor multi-level boost converter capable of a voltage conversion greater than 40 is presented and analysed with a particular focus on non-idealities, including inductor imbalances, scalable voltage losses from the switched inductor topology and the trade-off between increased capacitance and voltage spikes. A secondary set of tests, which explores transient mitigation through variations of the capacitance within the switched capacitor network and the introduction of a small series inductor within the first stage of the network, is also presented. Findings from the secondary test demonstrate a trade-off between transient mitigation and operating efficiency.

Chapter 5 combines the bipolar design of Chapter 3 and the scalable topologies of Chapter 4 to realise an ultra high-gain bipolar DC-DC converter. With this, a  $\pm 4.7 \text{ kV}_{DC}$  laboratory demonstrator was developed and presented. Experimental results from the demonstrator are utilised alongside simulated findings to validate theoretical analysis. Results from additional tests, which demonstrate the ability of the proposed converter to maintain a stable output voltage of 4.7 kV $_{DC}$  across an input voltage range of 48-200 V $_{DC}$  are also shown. Factors that limited the voltage conversion range are identified, and solutions to achieve the voltage conversion ratio range specified in Section 1.2 are discussed.

Chapter 6 offers a summary of the findings of this thesis and identifies areas for future research, including strategies for upscaling operating power, without sacrificing voltage conversion; achieving bidirectional power flow, to allow for energy storage applications; and strategies of how the proposed converter, demonstrated in Chapter 5, may be integrated into a solid state transformer to achieve LVAC to MVAC conversion to facilitate wind-wave integration.

#### Literature Review

## 2.1 Introduction

This chapter explores DC-DC converter designs, which may be used to achieve high voltage conversion ratios. The second section of this chapter describes the fundamental boost converter design and how it achieves voltage conversion. The third section considers key characteristics of DC-DC converters, which define their functionality as well as how these characteristics may contribute to the design specifications. This includes aspects related to galvanic isolation, unipolar and bipolar outputs, direction of power flow and the ability to scale up designs to achieve greater voltage conversion ratios. The fourth section in this chapter explores high-gain voltage multiplication techniques reported within the literature and compares them to these key characteristics. Finally, a comparison between these techniques is presented and evaluated to identify suitable designs to achieve the project objective.

## 2.2 DC-DC Converter Theory

DC-DC converters are utilised to change a given input voltage into a specified output voltage. Converters which produce a lower output voltage than the input are designated as buck converters, whereas designs which produce a higher output voltage in comparison to the input are boost converters [20]. As the aim of this project is to produce high output voltages with low voltage inputs, only boost converters were considered.

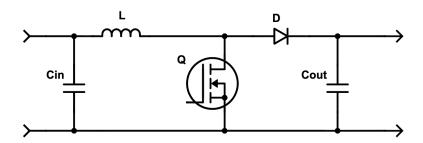

#### 2.2.1 Conventional Boost Converter

The most understood and arguably simplest type of boost converter is the conventional boost converter (CBC) [20] shown in Figure 2.1.

Figure 2.1: Circuit diagram of a CBC

The operation of the CBC may be observed by considering two working states, or modes of operation. In the first state, or Mode 1, the switching device conducts which creates a short pathway to ground. This pathway leads to the parallelisation of the input supply and inductor, allowing a relatively large amount of current to flow in the inductor, which in turn generates a magnetic field. In the second state, or Mode 2, the switching device blocks, removing the short pathway. In this configuration, the input supply and inductor are in series with the output capacitor; the magnetic field generated by the inductor collapses, generating a voltage spike. This inductive voltage spike combines with the input supply voltage, resulting in a higher voltage across the output capacitor. After

the next transition to Mode 1, while the magnetic field in the inductor regenerates, the output capacitor discharges into the output, allowing for a constant output voltage and current between switching modes.

This operation may be quantitatively described with relatively simple equations. During Mode 1, the voltage across the inductor and input stage are equal, giving:

$$V_{Lm1} = V_{in}D (2.1)$$

where  $V_{Lm1}$  is the voltage across the inductor during Mode 1,  $V_{in}$  the input voltage, and D the duty ratio used to describe the ratio of Mode 1 operation over a complete switching period. The voltage across the inductor during Mode 2 may be described using Kirchhoff's second law:

$$V_{Lm2} = (V_{in} - V_C)(1 - D) (2.2)$$

where  $V_{Lm2}$  is the voltage across the inductor during Mode 2 and  $V_C$  the voltage across the output capacitor. During steady state operation, when the charge of the inductor during Mode 1 is equal to the discharge of the inductor during Mode 2,  $V_{Lm1} + V_{Lm2} = 0$ . This allows the voltage conversion ratio, or gain of the CBC to be calculated with

$$\frac{V_C}{V_{in}} = \frac{1}{(1-D)} \tag{2.3}$$

as the capacitor and output are in parallel, this equation may be expressed with

$$\frac{V_{out}}{V_{in}} = \frac{1}{(1-D)} \tag{2.4}$$

where  $V_{out}$  is the output voltage. Therefore, by varying the duty ratio, the magnitude of the output voltage compared to the input voltage may be controlled. Theoretically, as

D approaches 1, the voltage gain of a boost converter will tend towards infinity, offering infinite voltage gain. Practically, when the duty ratio surpasses 0.8, losses within the CBC reduce the output voltage substantially. This limits the practical voltage gain of a CBC to a maximum of 5 times the input value. To overcome this limitation, research has explored alternative designs to the CBC to achieve greater voltage conversion ratios in addition to offering additional capabilities to improve the functionality of a given DC-DC converter.

#### 2.3 DC-DC Converter Characteristics

When discussing alternate DC-DC converters designs, key distinctions are required to accurately describe operation and capability.

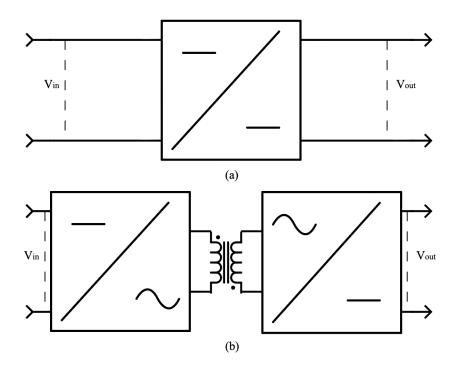

#### 2.3.1 Isolation

Isolation is a characteristic primarily associated with circuit protection. Isolated devices utilise magnetic coupling, often a transformer, to physically separate 2 sections of a circuit while maintaining an electrical connection. This is often used to reduce electrical noise between sections of a circuit and protect low voltage connections from high voltage operating points. [27].

A by-product of isolated topologies is the ability to achieve high voltage conversion ratios by configuring the turns ratio of the magnetic coupling. However, this comes at the expense of the previously identified transformer shortcomings. To outline the characteristic, Figure 2.2 provides a diagram demonstrating the difference between Isolated and non-isolated designs

Due to the separation, if a large voltage increase were to instantaneously occur in Figure 2.2(b), the coupling would limit the potential damage to the devices connected to the output. Conversely if the same increase were to occur in Figure 2.2(a), the increase

Figure 2.2: Block diagram of (a) Non-Isolated converter, (b) Isolated converter would propagate through the converter, potentially damaging connected devices.

The implications of isolated technologies, which include increased instillation costs and mechanical fatigue associated with transformers, commonly utilised in isolated converters, have already been identified for wind energy applications [28]. These concerns are compounded for wave energy applications when considering many designs are more sensitive to mechanical and environmental constraints due to this, non-isolated topologies were identified as preferable for DC-DC converter designs in WEC platforms.

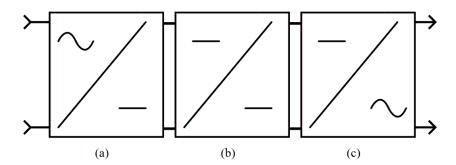

## 2.3.2 Polarity

Polarity outlines whether a given converter is capable of producing a single, unipolar, output or two, bipolar, outputs of equal and opposite magnitude. Bipolarity offers both the potential of integration into bipolar collection networks and devices as well as the ability to double a converters voltage conversion ratio by referencing the outputs to each

other rather than a common ground.

Figure 2.3: Block diagram of (a) Unipolar converter, (b) Bipolar converter with 2 outputs referenced to a common ground (c) Bipolar converter with positive output referenced to the negative output.

Unipolar converters, shown in Figure 2.3(a), utilise a single referenced output offering reduced circuit complexity compared to bipolar designs. Bipolar converters with 2 equal and opposite outputs, shown in Figure 2.3(b), have been discussed in the literature as part of a potential solution to cable failure in offshore wind farms. Such designs allow for continued power extraction in the event of a single cable failure, reducing unexpected costs at the expense of increased capital investment. However, the operating voltages of such designs are at least an order of magnitude greater than the project objective

[29, 30]. Bipolar converters operating with a single, combined voltage output, shown in Figure 2.3(c), increase the voltage conversion ratio given converter by a factor of 2, while offering the same integration potential as unipolar converters. This method of voltage multiplication may be compounded with other voltage multiplication techniques to achieve large voltage conversion ratios.

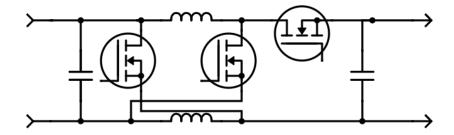

## 2.3.3 Directionality

The directionality of a DC-DC converter outlines how power may potentially flow through a given converter. Unidirectional converters, shown in Figure 2.4(a), allow power to flow in a single direction, extracting energy from a source and delivering energy into a single load. Bidirectional converters, shown in Figure 2.4(b), are capable of power flow in both directions. This allows devices connected to be treated as either a source or a load.

Figure 2.4: Block diagram of (a) Unidirectional converter, (b) Bidirectional converter

Bidirectional converters are capable of power extraction and injection, and as such have been identified for their ability to integrate energy storage systems in generator networks [31–35]. Such designs may smooth out the large variation in power in renewable systems and as such may be highly benficial in providing a consistent power output for high peak, low average wave generation. Transformerless, high-gain bidirectional converters often require comparatively more switching devices than unidirectional devices, which often rely on diodes to limit power flow within the device [36, 37]. This requires bidirectional converters to utilise more complex control schemes during operation, as well as develop strategies to mitigate switching losses from the additional devices. Therefore, while a desirable trait, the use of bidirectionality must be considered based on its impact on operational complexity and efficiency.

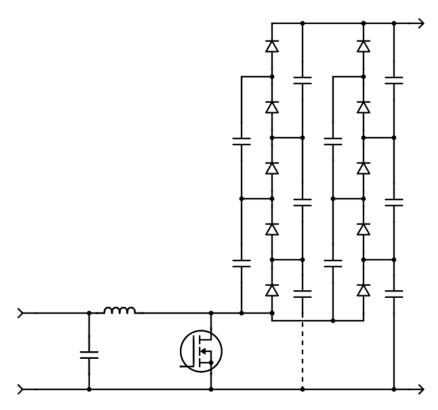

## 2.3.4 Scalability

An intuitive method of achieving a high voltage conversion ratio is to use topologies that both produce a voltage gain and may stack upon themselves. Such designs may scale in series with another to achieve a cascading effect as shown in Figure 2.5(a) [32,33,38,39]. Alternative designs may scale in parallel as shown in Figure 2.5(b) [37,40–46]. These approaches may also be combined to achieve a form of cascaded parallelisation.

Series scaled designs are capable of quadratic voltage conversion ratios; however, this often comes at a trade off resulting from the increased voltages across individual components. which leads to increased power losses. Conversely, parallel scaled designs produce linear increases in voltage conversion ratio; however, the increased voltage may be shared across the parallel states to limit the voltage across of any singular device.

# 2.4 Analysis of Innovative High-Gain DC-DC Topologies

A range of voltage multiplication techniques presented in the literature were identified and compared, based on the outlined characteristics, to determine potential designs compatible

Figure 2.5: Block diagram of (a) Series scaled converter, (b) Parallel scaled converter. with DC-DC boost converters.

## 2.4.1 Cascaded

Cascaded topologies may overcome the voltage gain limitation of a single CBC, by scaling multiple in series, combining the output of one CBC to the input of another [39]. These boost converters may be stacked to achieve a quadratic voltage conversion ratio, based on the number of CBCs utilised. The fundamental cascaded boost converter schematic is outlined in Figure 2.6.

For a 2 stage cascaded boost converter the voltage gain of the individual converters

Figure 2.6: Circuit diagram of a cascaded boost converter

are multiplied to create a voltage conversion ratio of

$$\frac{V_{out}}{V_{in}} = \frac{1}{(1 - D_1)(1 - D_2)} \tag{2.5}$$

where  $D_1$  and  $D_2$  are the duty ratios of the first (left) and second (right) switching devices with respect to Figure 2.6. When considering the scalable nature of the cascaded boost converter, this equation may be generalised, assuming all duty cycles are equal, to:

$$\frac{V_{out}}{V_{in}} = \frac{1}{(1-D)^{N_{Cas}}} \tag{2.6}$$

where  $N_{Cas}$  is the number of converters cascaded. With the concept of cascaded boost converters, which involves connecting the output of one boost converter to the input of another, a range of cascaded boost converters, exploring different functionalities, have also been demonstrated. While non-isolated cascaded designs are more prevalent within the literature [32,33,38] isolated designs have also been reported [47]. With the use of a step up transformer, isolated designs can easily achieve high voltage conversion ratios at the isolation stage in addition to the cascaded boost stages [47].

The cascaded design is inherently scalable, as theoretically any number of boost converters may be cascaded together to achieve any target voltage converion ratio. However, as more stages are implemented, greater voltage stresses are observed by the subsequent

converters, leading to large power losses and reductions in power efficiency, mitigating the effective scalability of such topologies. Bidirectional cascaded designs utilise topologies capable of energy extraction and delivery have been demonstrated [32, 33, 48]. Due to the low component usage and relative simplicity, some bidirectional designs have reported power efficiencies in excess of 98 % [32,48]. However, [32] achieved bidirectionally via the use of a buck and boost element, such designs have demonstrated voltage gains comparable to the practical limit of the CBC and [48] was only able to achieve greater than 98 % operation efficiency, with a high voltage gain when operating below 40 W. Boost based bipolar cascaded designs have been reported in low power applications (<5 W) where they demonstrate comparitively low power efficiencies and low voltage conversion ratios [49,50]. This is likely due to the reported application of audio amplifiers. Further research would be required to determine the performance of bipolar cascaded designs at higher operating powers.

Due to the general definition of a cascaded design, a design capable of any of the key characteristics outlined is possible; the limiting factor originates from high voltage stress in addition to limited reported applicability at operating powers above 1 kW.

#### Quadratic Designs

To overcome the high voltage observed across the later stage switches in cascaded topologies, Quadratic converters exchange a switching device for a capacitor [24]. By definition, the quadratic boost converter is a design such that the duty cycle of a single switch has a quadratic relationship to the voltage gain, which may include a 2 stage cascaded design; however the commonly accepted fundamental quadratic topology is outlined in Figure 2.7. Such a design sacrifices the scalability of the cascaded boost topology to achieve lower voltage stress across switching components, reduce operation complexity and increase device

efficiency.

Figure 2.7: Circuit diagram of quadratic boost converter

The voltage conversion ratio of a basic quadratic boost converter is

$$\frac{V_{out}}{V_{in}} = \frac{1}{(1-D)^2} \tag{2.7}$$

which offers a quadratic voltage conversion ratio when utilising large duty ratios. Similar to the cascaded boost designs, quadratic boost converters have been demonstrated to be capable of unipolar [51–53] or bipolar [54] operation as well as bidirectional power flow [55]. Quadratic topologies have also been demonstrated to achieve comparable operating efficiencies to cascaded designs; however, efficient operation has also only been demonstrated at operating powers below 1 kW [52,53]

## 2.4.2 Coupled Inductor

Conceptually coupled inductors operate in the same manner as transformers, where 2 or more inductor windings are wound around the same magnetic core. With this, coupled inductor are subject to the same benefits and drawbacks as transformers. Including high efficiency, scalable voltage conversion, undesirable leakage inductances and comparatively greater weight to other components from the magnetic core [19].

The most well know example of a coupled inductor based boost converter is the flyback

Figure 2.8: Circuit diagram of a flyback converter

converter [19]. Shown in Figure 2.8 flyback converters couple the primary inductor used in a CBC with a secondary inductor placed in parallel of the output capacitor. This design offers inherent isolation between the input and output, with a voltage conversion ratio of:

$$\frac{V_{out}}{V_{in}} = N_T \frac{1}{(1-D)} \tag{2.8}$$

where  $N_T$  is the turns ratio between the primary and secondary inductors.

As coupled inductor designs are based on a device with galvanic isolation, many isolated coupled inductor based topologies have been reported in the literature [23,25,34,56]. When isolation is not required, coupled inductor topologies may be reconfigured to allow a direct connection to the input and output [26,57–60]. Bipolarity has also been achieved with coupled inductor designs, [26] reported a design capable of a balanced bipolar output with an operating efficiency of 93.3 % at 210 W, but demonstrated a voltage conversion ratio of  $\pm 4.4$ , which is comparable in magnitude to the CBC. [59] utilised a triple coupled inductor in a similar configuration to achieve bipolar outputs with a reported greater efficiency of 96.27 % at 200 W and a slightly increased voltage gain of  $\pm 5.9$ . As the voltage gain of these converters is proportional to the turns ratio of the coupled inductors, the gain is inherently scalable, without the need for additional circuitry. When considering

bidirectionality, coupled inductor designs possess an inherent advantage, as the direction of power flow dictates whether a coupled inductor with a given turns ratio will boost or buck [34]. However, as with other bidirectional designs, the ability to allow power to flow bidirectionally in a circuit required the use of comparably more active switching components than unidirectional designs. For example, the design proposed in [26] required 2 MOSFETs where as the bidirectional design outlined in [34] required 4.

When holistically considering coupled inductor topologies, designs capable of meeting all the ideal characteristics have been demonstrated within the literature. The voltage gain of coupled inductor topologies can be scaled relatively simply by adjusting the turns ratio. Furthermore, they may also be designed to limit the voltage stresses observed by active switching devices, offering an inherent advantage over cascaded and quadratic topologies. However, coupled inductor designs are subject to the same limitations of transformers, such as leakage inductance, which needs additional circuitry to mitigate [58]. Furthermore, as the aim of this project was to explore transformerless alternatives for high gain converters, the use of coupled inductors would undermine the initial goal of the project. Therefore, coupled inductor techniques were identified as unsuitable for the project design.

#### 2.4.3 Switched Inductor

Switched inductor topologies offer an alternative use case for inductors in high gain applications [11,61–63]. By charging inductors in parallel and then discharging in series, switched inductors offer a scalable form of voltage multiplication. Outlined in Figure 2.9, switched inductor topologies may replace single inductor stages in boost converter designs with a stacking inductor diode network.

When implemented into a CBC, and assuming no losses from the diodes, the voltage across an inductor during Mode 1 remains unchanged. During Mode 2 the voltage across

Figure 2.9: Circuit diagram of a modified CBC with a 2-stage switched inductor

a single inductor becomes:

$$V_{Lm2} = \frac{(V_{in} - V_C)(1 - D)}{N_L} \tag{2.9}$$

where  $N_L$  is the number of switched inductor stages. This leads to a voltage gain equation of

$$\frac{V_{out}}{V_{in}} = \frac{1 + (N_L - 1)D}{1 - D} \tag{2.10}$$

Due to the ability of the topology to be implemented at any point where there is a switching inductor, switched inductor topologies have been deomstrated with non-isolated converters [11,61,62], unipolar [11,61,62] and bipolar [63] as well as unidirectional [11,61-63] and bidirectional [35,36,64] designs. No designs of isolated topologies utilising switched inductors were found within the literature. This was likely due to the lack of need for a scalable voltage multiplication switching network, when isolated topologies may simply change the winding ratios at the point of isolation to achieve the same effect.

#### Voltage Lift Switched Inductor

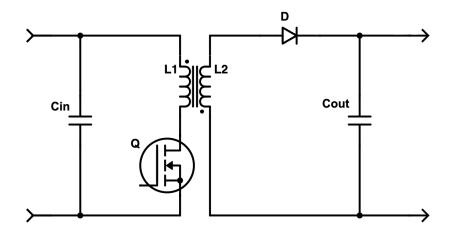

The voltage lift switched inductor (VLSI) topology is a variant of the switched inductor design, which exchanges the diodes forward biased during Mode 2 for a voltage lift

capacitor, illustrated in Figure 2.10 [12,65].

Figure 2.10: Circuit diagram of a modified CBC with a 2-stage voltage lift switched inductor

The voltage lift capacitor charges in Mode 1 and discharges in series with the switched inductors during Mode 2. Similar to the base switched inductor design, the voltage across an individual inductor remains unchanged during Mode 1. During Mode 2 the voltage across a single inductor becomes

$$V_{Lm2} = \frac{(V_{in} + (N_L - 1)V_{CVL} - V_C)(1 - D)}{N_L}$$

(2.11)

where  $V_{CVL}$  is the voltage across the voltage lift capacitor that, under ideal conditions, is assumed to equal  $V_{in}$ . This leads to a voltage gain equation of

$$\frac{V_{out}}{V_{in}} = \frac{N_L}{1 - D} \tag{2.12}$$

From this, it can be observed that a VLSI topology may achieve a greater voltage conversion ratio, for the same number of stages, compared to the switched inductor topology.

While from this analysis, voltage lift switched inductor designs are scalable [66], most literature which reported on the topology utilised a 2-stage design [12, 65]. Additionally, although voltage lift variants could be implemented into bipolar switched inductor

converters with relative simplicity, there has been limited demonstration of this.