### **Durham E-Theses**

### Optimisation of High Reliability Integrated Motor Drives

#### CALDER, HUGO

#### How to cite:

CALDER, HUGO (2023) Optimisation of High Reliability Integrated Motor Drives, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/15189/

#### Use policy

$The full-text\ may\ be\ used\ and/or\ reproduced,\ and\ given\ to\ third\ parties\ in\ any\ format\ or\ medium,\ without\ prior\ permission\ or\ charge,\ for\ personal\ research\ or\ study,\ educational,\ or\ not-for-profit\ purposes\ provided\ that:$

- $\bullet\,$  a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders. Please consult the full Durham E-Theses policy for further details.

> Academic Support Office, The Palatine Centre, Durham University, Stockton Road, Durham, DH1 3LE e-mail: e-theses.admin@durham.ac.uk Tel: +44 0191 334 6107 http://etheses.dur.ac.uk

# **Optimisation of High Reliability**

# **Integrated Motor Drives**

### **Hugo Calder**

Department of Engineering University of Durham

This dissertation is submitted for the degree of Doctor of Philosophy

October 2023

I would like to dedicate this thesis to my family, friends, my supervisors and everyone else who supported me along the way...

### **Publications**

- H. Calder, A. Horsfall, M. Shahbazi, "Optimal Device Selection Tool For Discrete SiC MOSFETs Considering Switching Loss Challenges Of Paralleled Devices", 2022 Power Electronics and Motor Drives (PEMD), Conference Paper

- L. Robinson, H. Calder, A. Gallant and A. Horsfall, "Short circuit ruggedness of SiC MOSFETs for high reliability applications", 2022 IEEE Energy Conversion Congress and Exposition (ECCE), Detroit, MI, USA, 2022, pp. 1-7, doi: 10.1109/ECCE50734.2022.9947766.

#### Abstract

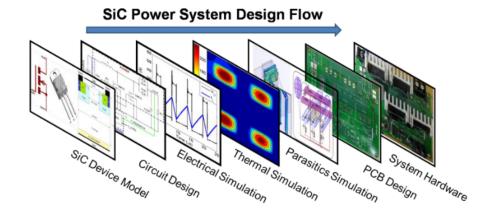

The development of integrated motor drives (IMDs) with high volumetric power density and reliability are crucial for the continued development and adoption of electric vehicles (EV). The development of the wide bandgap (WBG) devices, especially Silicon Carbide (SiC) MOSFETs, enables new possibilities for traction drive systems. However, to maximise the benefits of SiC, the IMD design process, including passive component selection, control and thermal management should be optimised. This thesis goes through the initial major design steps in SiC power system design, from SiC device analysis and modelling to circuit design and electrothermal simulation of an IMD system.

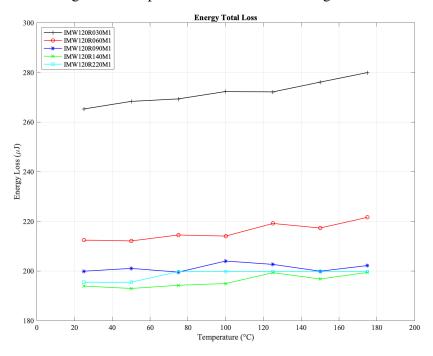

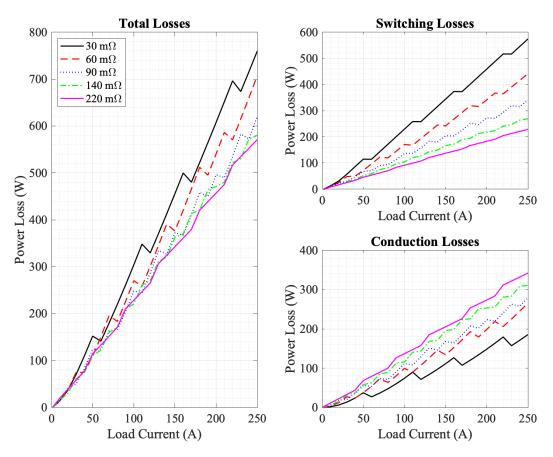

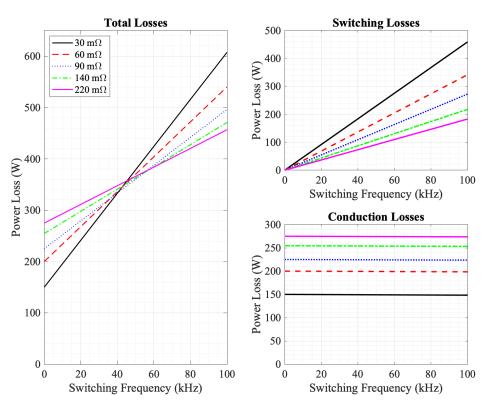

A novel approach to discrete SiC MOSFET selection, using a method of calculating performance based on experimental data, is described. Dynamic behaviour of a family of 1200 V MOSFETs is studied at temperatures up to 175 °C using a double pulse test to show the combined effect of the differences in internal design between MOSFETs with different current ratings. It is observed that the 30 m $\Omega$  MOSFET had a 24 % higher switching loss than a 140 m $\Omega$  at a 30 A load current. The study then goes on to compare the effect of switching frequency, paralleling of MOSFETs and the device type used to demonstrate the inverter design with the lowest power losses, which will equate to low temperatures and high lifetime.

The novel methodology can find the optimal choice of MOSFET from the family, and number required through paralleling, for a circuit when given the load current, temperature and switching. Understanding the device interdependencies in a single family is utilised to also predict the relative performance between SiC MOSFETs from different manufacturers. An axial-flux permanent magnet synchronous motor (PMSM) driven by a three-phase SiC inverter is simulated in PLECS using experimentally validated MOSFET models chosen by the device selection methodology. Electrothermal analysis shows the influence of switching frequency, temperature, MOSFETs paralleling and DC-link capacitance on voltage ripple, total harmonic distortion, efficiency and MOSFET loss and temperature profiles. With a 60 % decrease in THD and 50 % increase in maximum MOSFET junction temperature when switching frequency is increased from 10 to 100 kHz.

The high-temperature stress on the semiconductors due to close proximity with the machine stator means reliability is an important consideration that is yet to be fully investigated in IMD optimisations. This study uses a lifetime model specific to the transistor package TO-247 in reliability optimisation for IMD for the first time. It requires detailed MOSFET simulation outputs to provide a highly accurate lifetime for discrete SiC MOSFETs.

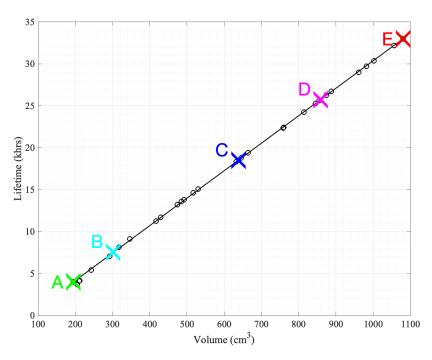

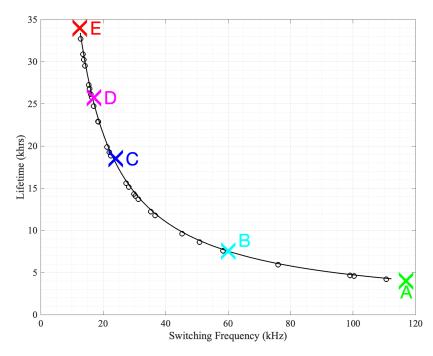

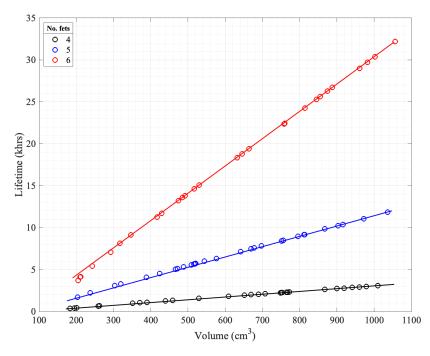

Both single and multi-objective optimisations of the volume and lifetime of the threephase inverter are presented. The single objective optimisation demonstrates the minimum volume and the corresponding switching frequency and lifetime when between three and six MOSFETs are paralleled at a temperature range between 50 and 150 °C. Design constraints were set limiting the feasible switching frequency range to between 13 kHz because of THD and 118 kHz because of efficiency limits, corresponding to required DC-link capacitors of 520 and 55  $\mu$ F respectively. Increases in temperature were found to further limit the maximum switching frequency and therefore increase the minimum volume of the inverter. A Pareto front identifies a range of possible solutions for the volume and lifetime of an inverter with six paralleled MOSFETs through the multi-objective objective procedure. Further analysis of these possible solutions identified a single optimal solution for the system, using a DC-link capacitance of 190  $\mu$ F at 45 kHz, giving a combined volume of the capacitor and MOSFETs of 440 cm<sup>3</sup> and a lifetime of 12,000 hours.

Finally, the electrothermal analysis of a dual inverter driving a symmetric six-phase PMSM is presented with the benefits of modular multi-phase systems in IMDs summarised. Effect on performance of lower per-phase current, interleaving strategies and fault tolerance are analysed and compared to equivalent three-phase systems, for 60 kW and 120 kW operation.

A novel method for lifetime prediction of systems with paralleled MOSFETs or fault tolerance capabilities considering incremental damage is developed based on TO-247 lifetime calculations from PLECS simulation, and component-level reliability profiles using Monte Carlo analysis. The dual inverter is used to model the system and implements control schemes for both single-phase and single inverter failure while maintaining the 4000 rpm and 140 Nm speed and torque requirements. A twofold increase in  $B_{10}$  lifetime of is observed when the effect of paralleled SiC MOSFETs prevents immediate system failure in a three-phase inverter.

A computational fluid dynamics (CFD) and 3D finite element thermal model are designed to study the inverter behaviour based on the thermal analysis of its shared cooling plate with a 300 mm diameter axial flux PMSM. Concentric layout designs minimise the variation of junction temperatures to 5 °C and the effect of the flow rate and temperature of the coolant in the PMSM cold plate is presented between 5 and 30 l/min.

The multi-objective optimisation procedure used to compare the dual inverter demonstrated it outperformed the three-phase inverter with 15 % smaller required DC-link capacitance, higher efficiency and increased lifetime in part due to its fault-tolerant nature. The optimal dual inverter considering the design constraints consists of four 40  $\mu F$  KEMET film capacitors operating with a switching frequency of 46 kHz giving an inverter volume of 300 cm<sup>3</sup> and a lifetime of 16.3 years, assuming 1000 hours of operation annually.

# **Table of contents**

| Li | List of figures  |            |                                      |  | xiii |     |      |

|----|------------------|------------|--------------------------------------|--|------|-----|------|

| Li | ist of tables xx |            |                                      |  |      | xxi |      |

| No | omenc            | ature      |                                      |  |      | Х   | xiii |

| 1  | Intro            | troduction |                                      |  |      |     | 1    |

|    | 1.1              | Integra    | ted Motor Drives                     |  |      |     | 2    |

|    | 1.2              | Applic     | ation of Wide bandgap Semiconductors |  |      |     | 3    |

|    | 1.3              | Import     | ance of Reliability                  |  |      |     | 4    |

|    | 1.4              | Resear     | ch question and contribution         |  |      |     | 5    |

|    | 1.5              | Thesis     | Structure                            |  | •    | •   | 6    |

| 2  | Lite             | rature I   | Review                               |  |      |     | 9    |

|    | 2.1              | Introdu    | uction                               |  | •    |     | 9    |

|    | 2.2              | Integra    | ted Motor Drives                     |  | •    |     | 10   |

|    |                  | 2.2.1      | IMD Topologies                       |  | •    |     | 11   |

|    |                  | 2.2.2      | Thermal Management                   |  |      |     | 15   |

|    | 2.3              | IMD C      | Converter Topologies                 |  |      |     | 16   |

|    | 2.4              | Semico     | onductor Power Devices               |  | •    |     | 18   |

|    |                  | 2.4.1      | Overview of WBG materials            |  | •    |     | 18   |

|    |                  | 2.4.2      | SiC Power MOSFETs                    |  | •    |     | 19   |

|    |                  | 2.4.3      | Power Electronic Packaging           |  |      |     | 28   |

|   |      | 2.4.4     | Modelling SiC Devices                                          | 29 |

|---|------|-----------|----------------------------------------------------------------|----|

|   | 2.5  | Passiv    | e Components                                                   | 30 |

|   | 2.6  | Reliab    | ility Analysis of Power Converters                             | 32 |

|   |      | 2.6.1     | Reliability Analysis                                           | 33 |

|   | 2.7  | Optim     | isation-based Design                                           | 37 |

|   | 2.8  | Summ      | ary                                                            | 39 |

| 3 | Opti | imised S  | Selection of Power Devices                                     | 41 |

|   | 3.1  | Introdu   | uction                                                         | 41 |

|   | 3.2  | Figure    | of Merit                                                       | 42 |

|   | 3.3  | Metho     | ds for Investigating SiC Device Performance                    | 45 |

|   |      | 3.3.1     | Double Pulse Testing                                           | 45 |

|   |      | 3.3.2     | Method Comparison and Validation                               | 48 |

|   | 3.4  | Switch    | ning Investigation for a Family of 1.2 kV SiC MOSFETs          | 52 |

|   |      | 3.4.1     | Switching Speed Characterisation                               | 55 |

|   |      | 3.4.2     | Switching Losses Characterisation                              | 61 |

|   |      | 3.4.3     | Gate Charge Analysis                                           | 67 |

|   |      | 3.4.4     | Voltage and Current Stresses                                   | 69 |

|   |      | 3.4.5     | Impact of Temperature                                          | 70 |

|   | 3.5  | Optim     | ised Device Selection                                          | 73 |

|   |      | 3.5.1     | MOSFET Analysis and Paralleling                                | 74 |

|   |      | 3.5.2     | Device Family Comparisons                                      | 78 |

|   | 3.6  | Summ      | ary                                                            | 80 |

| 4 | Reli | ability ( | Optimisation of Integrated Three-Phase Voltage Source Inverter | 83 |

|   | 4.1  | Introdu   | uction                                                         | 83 |

|   | 4.2  | Autom     | notive Power-train                                             | 84 |

|   |      | 4.2.1     | Electrical Simulation Software                                 | 85 |

|   |      | 4.2.2     | Permanent Magnet Synchronous Motor                             | 86 |

|   |      | 4.2.3     | Busbars                                                        | 87 |

|   |      | 4.2.4    | Control System                                      | 89  |

|---|------|----------|-----------------------------------------------------|-----|

|   | 4.3  | Inverte  | er Design                                           | 89  |

|   |      | 4.3.1    | Device Selection                                    | 90  |

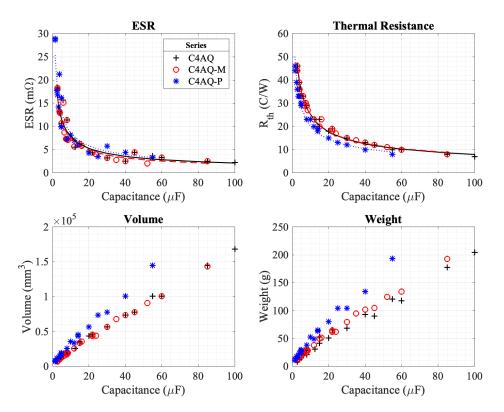

|   |      | 4.3.2    | DC-link Capacitor                                   | 91  |

|   |      | 4.3.3    | Inverter Volume                                     | 96  |

|   | 4.4  | IMD F    | Reliability Analysis                                | 96  |

|   |      | 4.4.1    | Semiconductor Device Lifetime Models                | 97  |

|   |      | 4.4.2    | DC-link Capacitor Reliability                       | 98  |

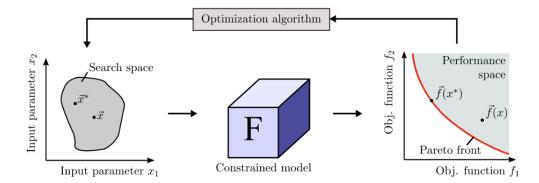

|   | 4.5  | Desigr   | Optimisation Procedure                              | 99  |

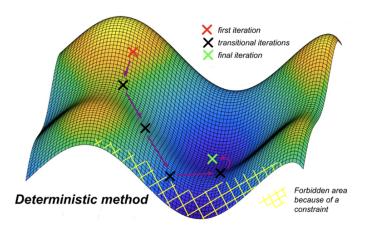

|   |      | 4.5.1    | Algorithm and Optimisation Tool                     | 100 |

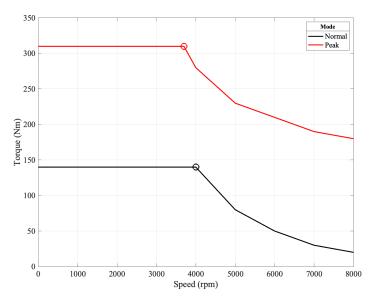

|   |      | 4.5.2    | Operating Conditions                                | 103 |

|   |      | 4.5.3    | Design Parameters and Constraints                   | 104 |

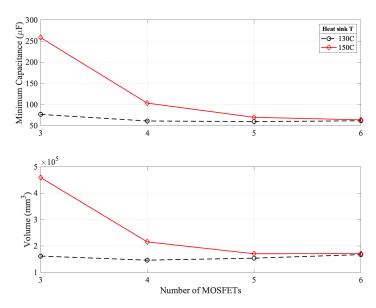

|   | 4.6  | Volum    | etric Power Density Optimisation                    | 106 |

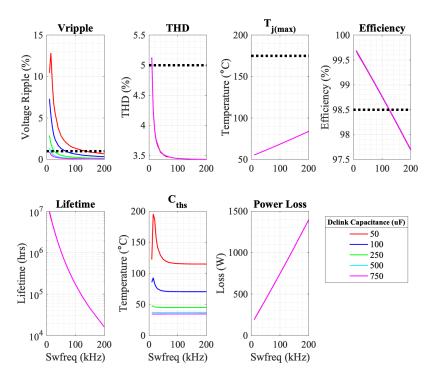

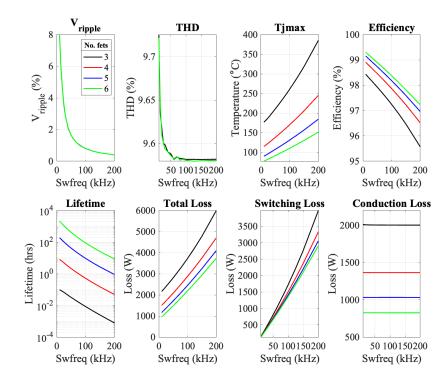

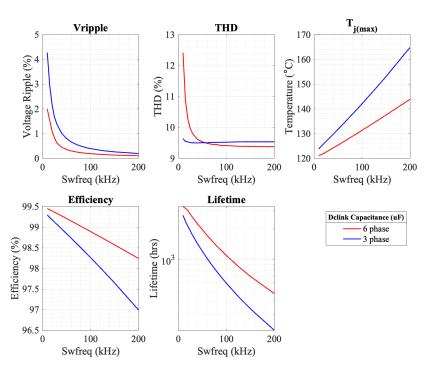

|   |      | 4.6.1    | Effect of Switching Frequency on Inverter Operation | 106 |

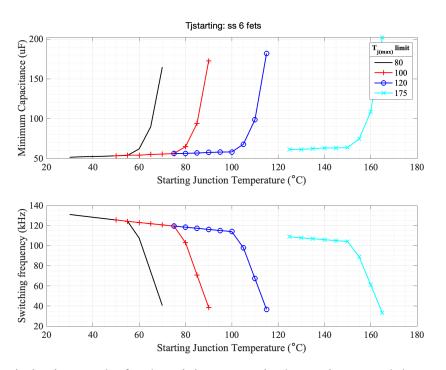

|   |      | 4.6.2    | Thermal Considerations                              | 113 |

|   |      | 4.6.3    | Reliability Optimisation                            | 117 |

|   |      | 4.6.4    | Design Summary                                      | 123 |

|   | 4.7  | Summ     | ary                                                 | 124 |

| 5 | Desi | gn of Fa | ault Tolerant Multi-phase IMD                       | 127 |

|   | 5.1  | Introdu  | uction                                              | 127 |

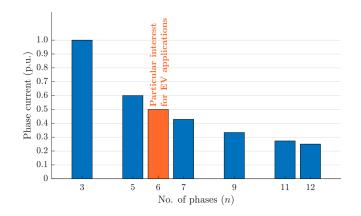

|   | 5.2  | Multi-   | phase Power Trains                                  | 128 |

|   |      | 5.2.1    | Per-phase Requirements                              | 130 |

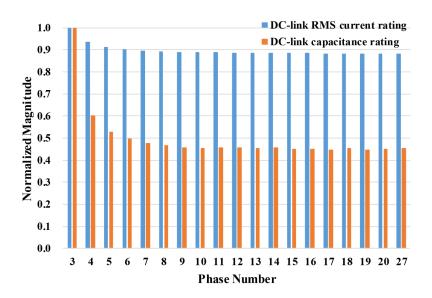

|   |      | 5.2.2    | DC Capacitor Requirement Reduction                  | 131 |

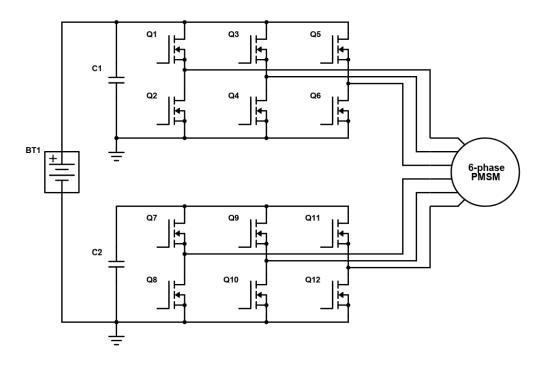

|   | 5.3  | Dual I   | nverter Motor Drive System                          | 132 |

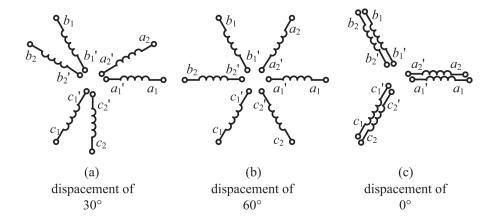

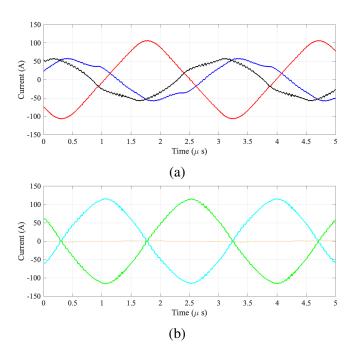

|   |      | 5.3.1    | Multi-phase PMSM Modelling                          | 132 |

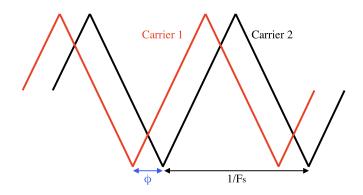

|   |      | 5.3.2    | Control                                             | 134 |

|   |      | 5.3.3    | Operating Conditions                                | 136 |

|   | 5.4  | Fault 7  | Folerant Operation                                  | 136 |

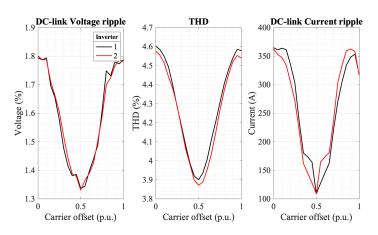

|   | 5.5  | Electro  | othermal Analysis and Design Improvement            | 141 |

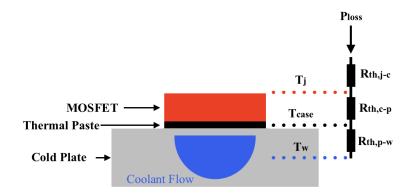

|    |        | 5.5.1   | Thermal Modelling                                          | 141 |

|----|--------|---------|------------------------------------------------------------|-----|

|    |        | 5.5.2   | Cooling System                                             | 144 |

|    |        | 5.5.3   | Physical Layout                                            | 144 |

|    |        | 5.5.4   | Method Comparison                                          | 146 |

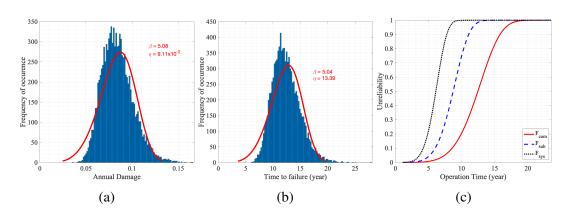

|    | 5.6    | New R   | Reliability Considerations                                 | 147 |

|    |        | 5.6.1   | Component Level Reliability Profiles                       | 148 |

|    |        | 5.6.2   | System Level Reliability Profiles                          | 151 |

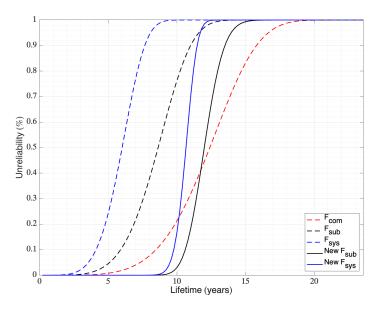

|    |        | 5.6.3   | Dual three-phase Case Study                                | 159 |

|    | 5.7    | Optim   | isation of Dual Inverter IMD                               | 161 |

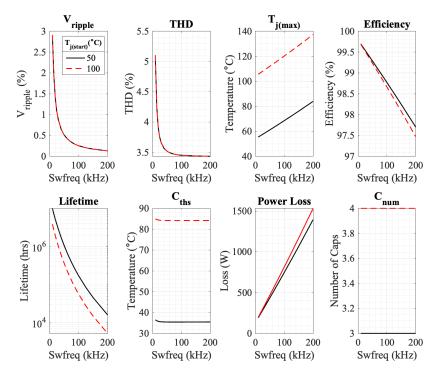

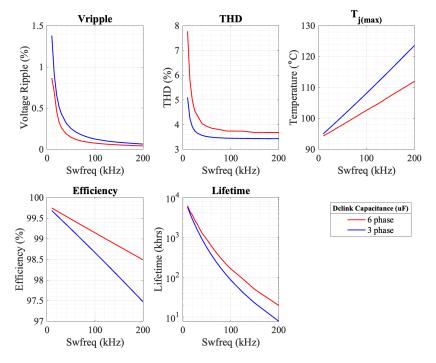

|    |        | 5.7.1   | Effect of Switching Frequency on Inverter Operation        | 161 |

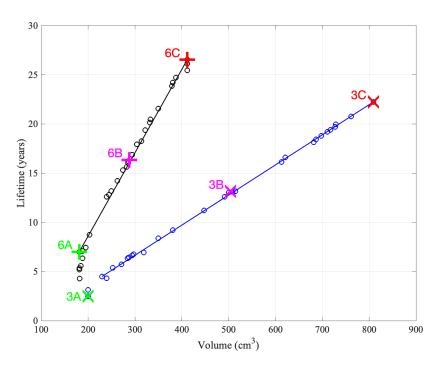

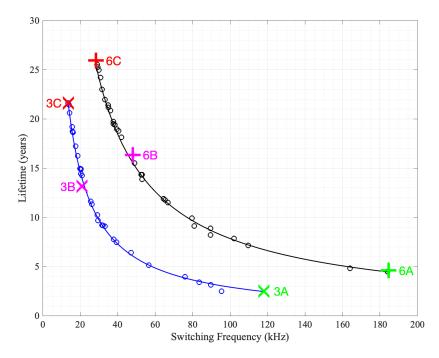

|    |        | 5.7.2   | Multi-objective Optimisation with System-level Reliability | 166 |

|    |        | 5.7.3   | Design Summary                                             | 169 |

|    | 5.8    | Summ    | ary                                                        | 170 |

| 6  | Con    | clusion | S                                                          | 173 |

|    | 6.1    | Future  | Work                                                       | 175 |

| Re | eferen | ces     |                                                            | 177 |

# List of figures

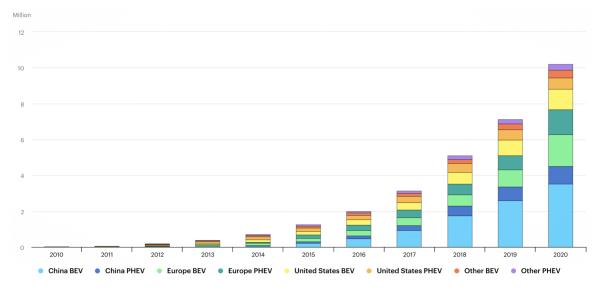

| 1.1  | Global electric passenger car stock, 2010-2020 [4]                              | 2  |

|------|---------------------------------------------------------------------------------|----|

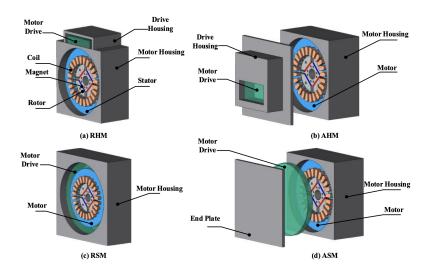

| 1.2  | Four categories of IMDs (a) Rotor Housing Mounted (RHM); (b) Axial              |    |

|      | Housing Mounted (AHM); (c) Radial Stator-iron Mounted (RSM); (d) Axial          |    |

|      | Stator-iron Mounted (ASM) [6]                                                   | 3  |

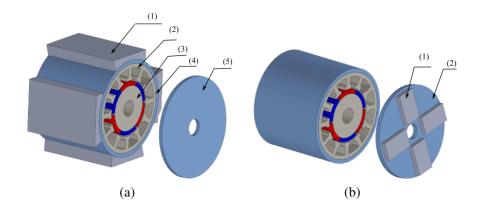

| 2.1  | Demonstration of housing mounted integration topologies (a) RHM: (1)            |    |

|      | power converter modules, (2) stator, (3) rotor, (4) housing, (5) end plate. (b) |    |

|      | AHM: (1) power converter modules, (2) end plate [27]                            | 11 |

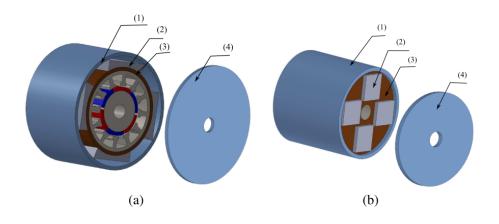

| 2.2  | Demonstration of stator mounted integration topologies (a) RSM: (1) housing,    |    |

|      | (2) power converter modules, (3) shared cooling structure, (4) end plate. (b)   |    |

|      | ASM: (1) housing, (2) power converter modules, (3) shared cooling structure,    |    |

|      | (4) end plate [27]                                                              | 13 |

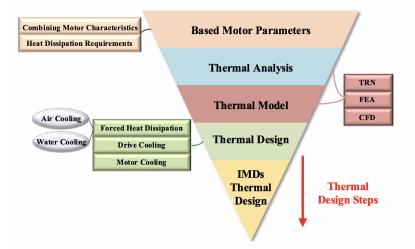

| 2.3  | IMDs integrated thermal design system [6]                                       | 15 |

| 2.4  | Cross section of simplified n-channel power MOSFETs (a) Planar (b) Trench       |    |

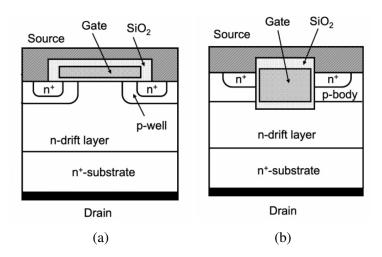

|      | [58]                                                                            | 20 |

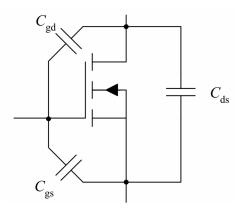

| 2.5  | Electrical equivalent circuit of MOSFET with parasitic capacitances [60]        | 20 |

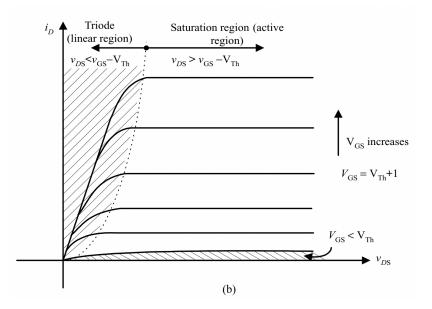

| 2.6  | Typical output characteristic of basic n-channel SiC MOSFET [60]                | 22 |

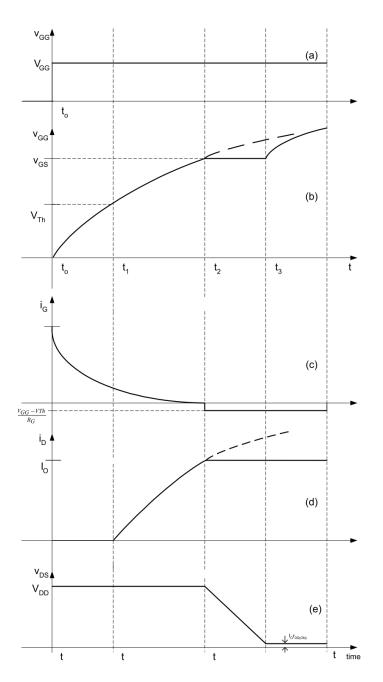

| 2.7  | Turn-on waveforms of a MOSFET with an inductive load [60]                       | 24 |

| 2.8  | Turn-off waveforms of a MOSFET with an inductive load [60]                      | 26 |

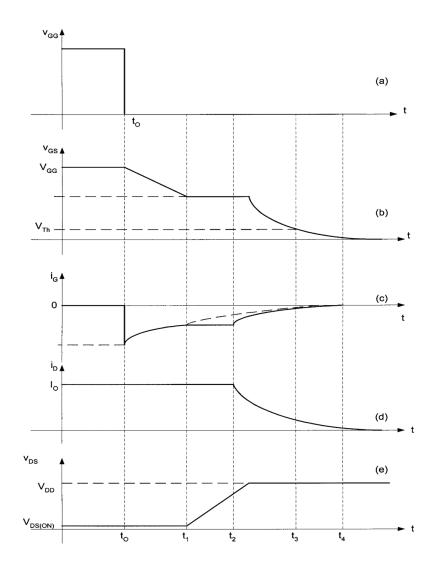

| 2.9  | Simple turn-on waveform of MOSFET with gate voltage curve and gate              |    |

|      | charge presented [12]                                                           | 27 |

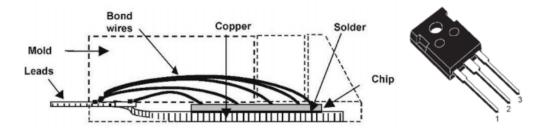

| 2.10 | Classic structure of TO-247 package [11]                                        | 29 |

|      |                                                                                 |    |

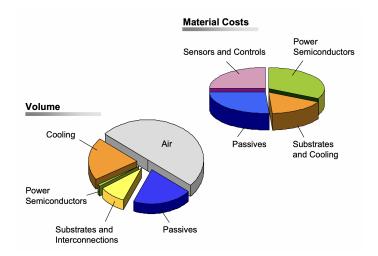

| 2.11 | Typical material cost and volume distribution in power electronics system [20]   | 31 |

|------|----------------------------------------------------------------------------------|----|

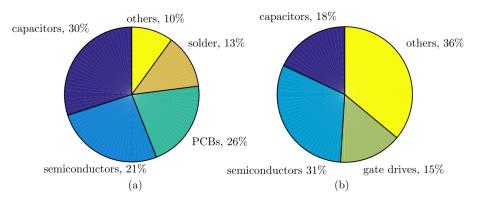

| 2.12 | Results of surveys on failures within power converter devices (a) [85], (b) [86] | 33 |

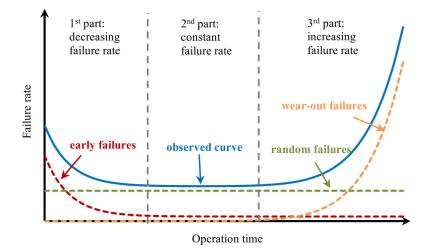

| 2.13 | Bathtub curve describing the failure rate during life cycle of a consumer        |    |

|      | product (not to scale) [89]                                                      | 34 |

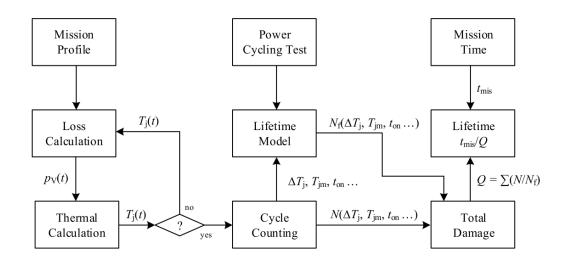

| 2.14 | Flow diagram for the lifetime estimation procedure [71]                          | 36 |

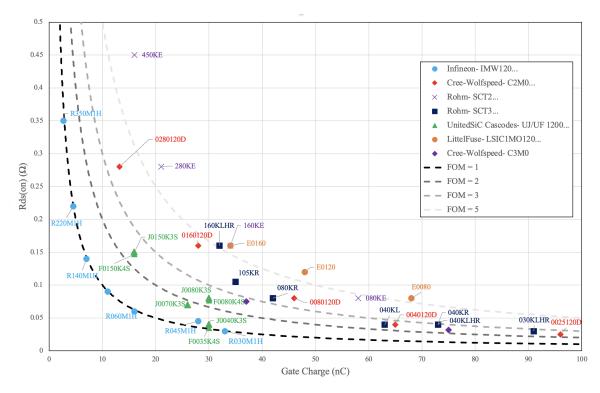

| 3.1  | On-state Resistance against Input Capacitance Charge for Range of 1.2 kV         |    |

|      | SiC MOSFETs Based on Datasheet Values                                            | 43 |

| 3.2  | On-state Resistance as a function of the reciprocal Input Capacitance Charge     |    |

|      | for Range of 1.2 kV SiC MOSFETs Based on Datasheet Values                        | 44 |

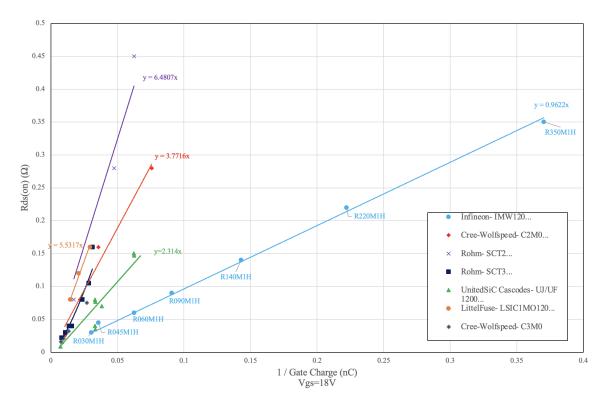

| 3.3  | Sample Waveforms for DPT                                                         | 46 |

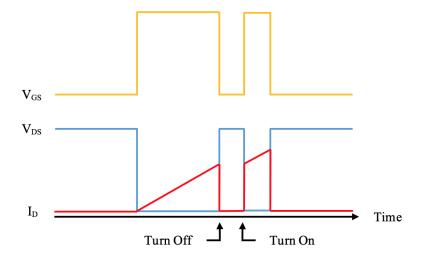

| 3.4  | DPT Fixture Schematic                                                            | 47 |

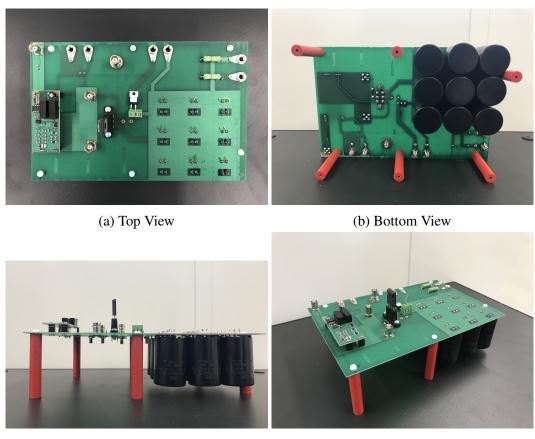

| 3.5  | DPT Fixture                                                                      | 48 |

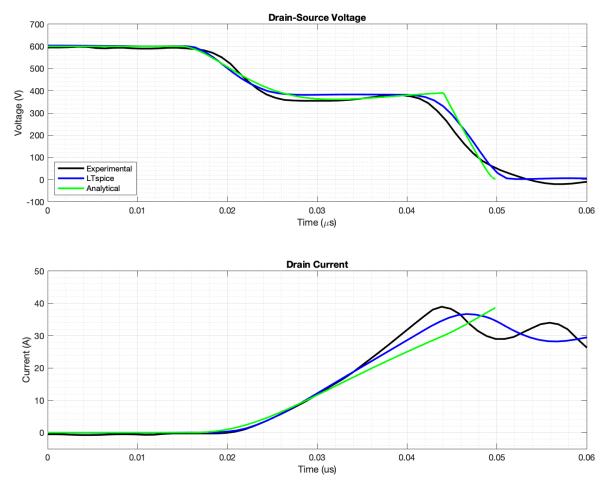

| 3.6  | Switching Waveform from Experimental Data, LTspice and Analytical Model          | 50 |

| 3.7  | Relationship between Infineon Series Datasheet Parameters showing linearity      |    |

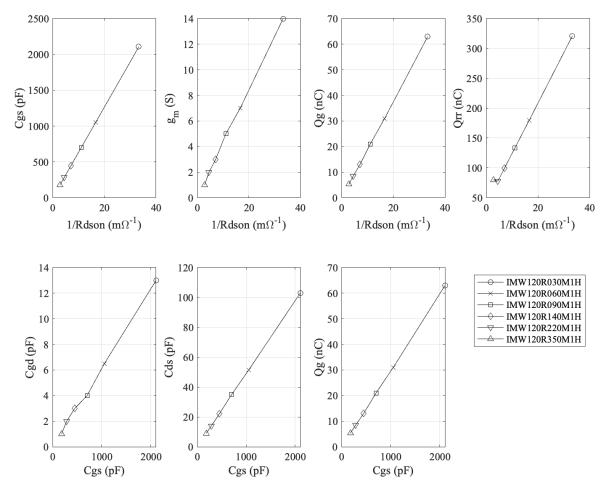

|      | of quoted device characteristics                                                 | 54 |

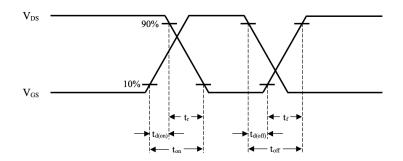

| 3.8  | Switching Times Definitions                                                      | 55 |

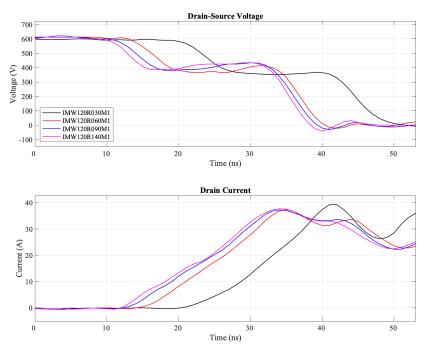

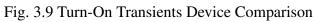

| 3.9  | Turn-On Transients Device Comparison                                             | 56 |

| 3.10 | Turn-Off Transients Device Comparison                                            | 56 |

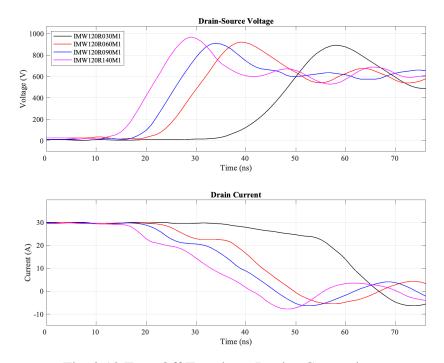

| 3.11 | Load Current Impact on Total Switching Time Device Comparison                    | 57 |

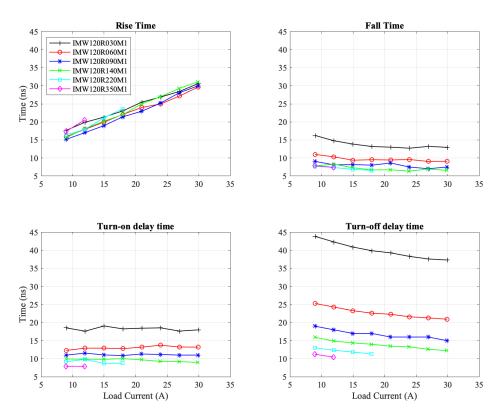

| 3.12 | Load Current Impact on Switching Time Components Device Comparison .             | 58 |

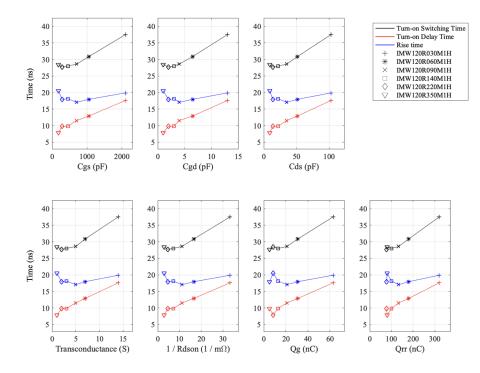

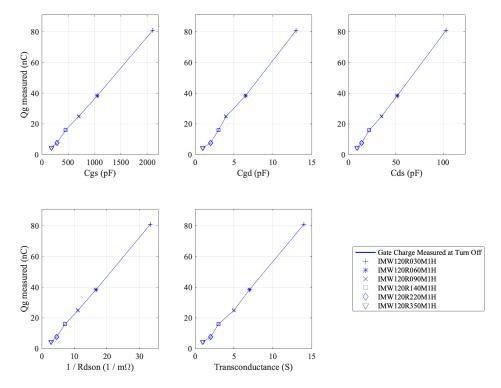

| 3.13 | Turn-On Switching Times Variation with Datasheet Parameters at 13 A              | 59 |

| 3.14 | Turn-Off Switching Times Variation with Datasheet Parameters at 13 A             | 59 |

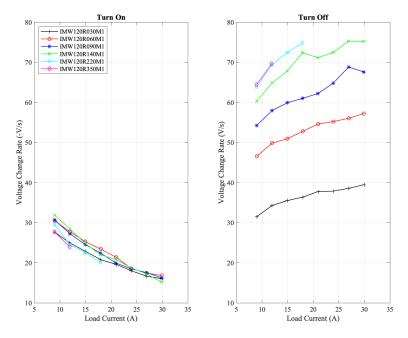

| 3.15 | Load Current Impact on Voltage Slew Rate Device Comparison                       | 60 |

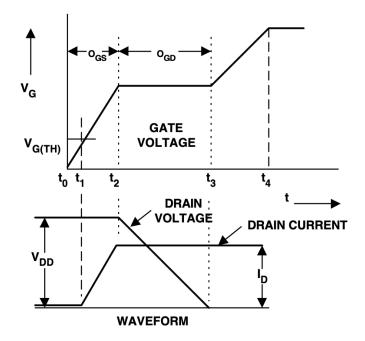

| 3.16 | Definitions for switching energy losses[12]                                      | 62 |

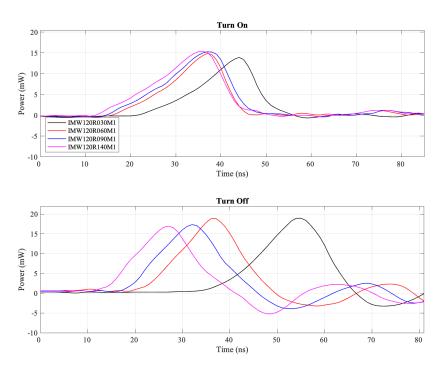

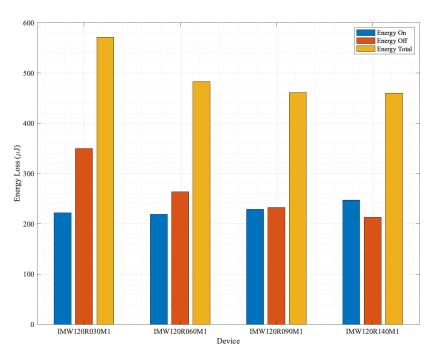

| 3.17 | Power Loss Transients Device Comparison                                          | 63 |

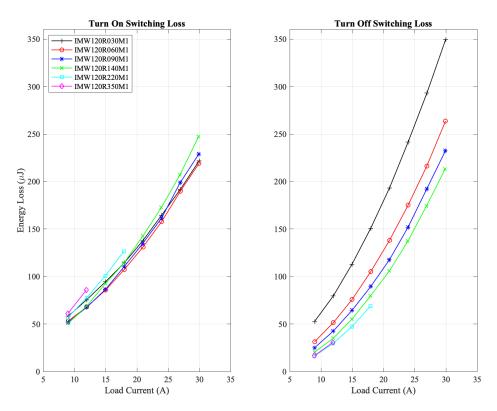

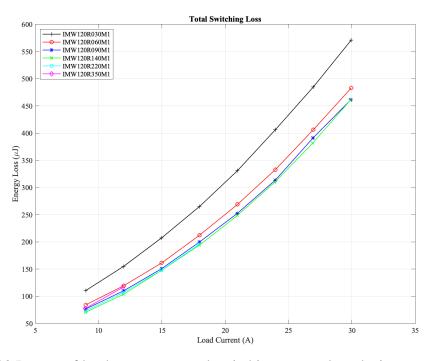

| 3.18 | Load Current Impact on Switching Energy Loss at Turn-On and Turn-Off             |    |

|      | Device Comparison                                                                | 64 |

| 3.19 | Impact of load current on total switching energy loss device comparison          | 65 |

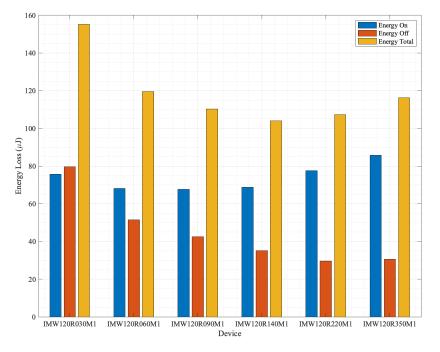

| 3.20 | Comparison of the Switching Energy Loss between Infineon Devices at 13 A         | 65 |

|      |                                                                                  |    |

| 3.21 | Comparison of Switching Energy Loss between Infineon Devices at 30 A $$ .              | 66  |

|------|----------------------------------------------------------------------------------------|-----|

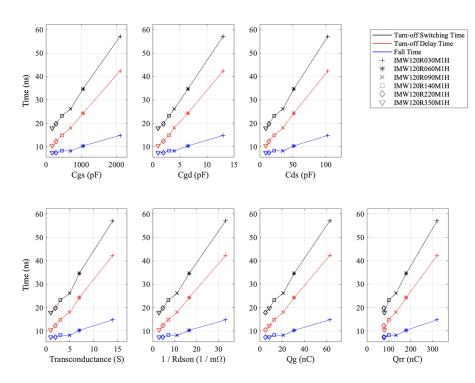

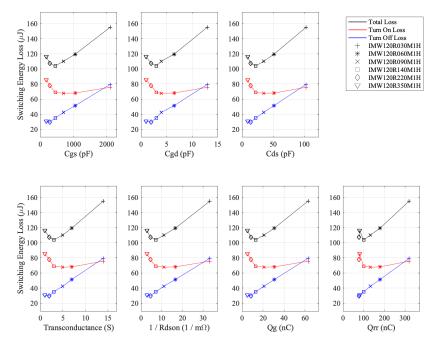

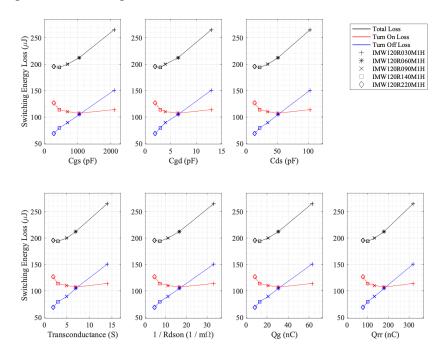

| 3.22 | Switching Loss Variation with Datasheet Parameters at 13 A                             | 67  |

| 3.23 | Switching Loss Variation with Datasheet Parameters at 18 A                             | 67  |

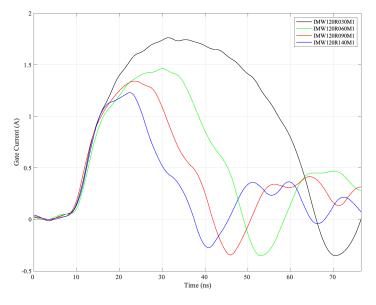

| 3.24 | Turn-Off Gate Current Transients Device Comparison                                     | 68  |

| 3.25 | Turn-Off Gate Charge Variation with Datasheet Parameters                               | 69  |

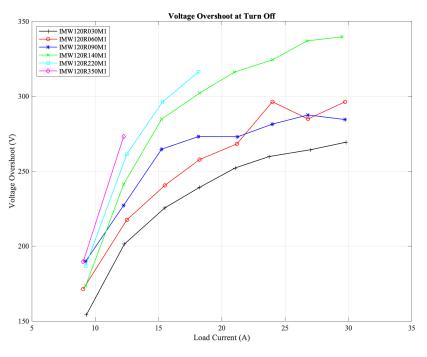

| 3.26 | Voltage Overshoot Device Comparison                                                    | 70  |

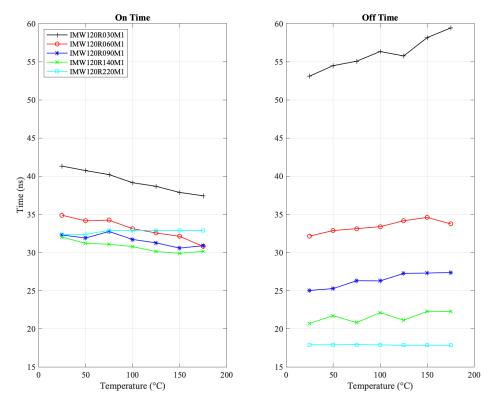

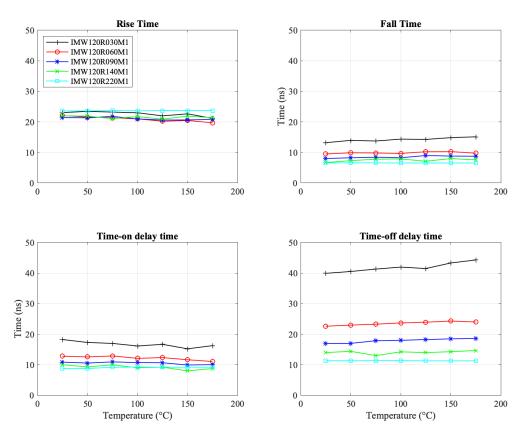

| 3.27 | Temperature Effect on Overall Switching Time                                           | 71  |

| 3.28 | Temperature Effect on Switching Times                                                  | 72  |

| 3.29 | Temperature Effect on Switching Losses                                                 | 72  |

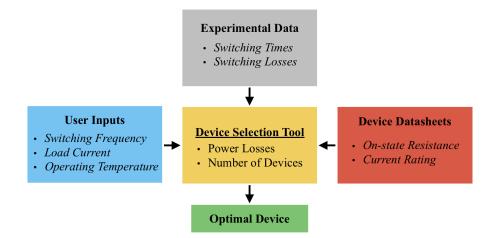

| 3.30 | Device Selection Tool Process                                                          | 73  |

| 3.31 | Load Current Impact on Power Losses Device Comparison                                  | 74  |

| 3.32 | Switching Frequency effect on Power Losses Device Comparison                           | 75  |

| 3.33 | Impact of load current on power losses in the switching frequency range for            |     |

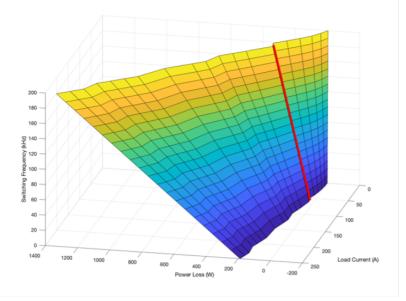

|      | IMW120R030M1H                                                                          | 77  |

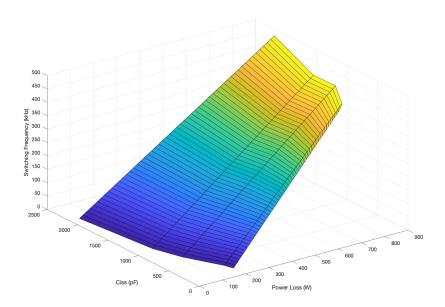

| 3.34 | Impact of Input Capacitance Rating on Power Losses at Range of Switching               |     |

|      | Frequency                                                                              | 77  |

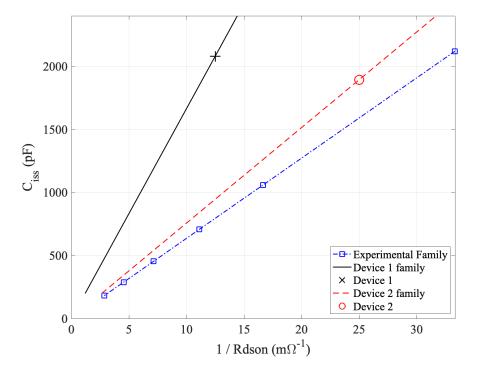

| 3.35 | Relationship between $C_{iss}$ and $R_{DS(on)}$ for the Infineon family, and predicted |     |

|      | relationships for test devices                                                         | 78  |

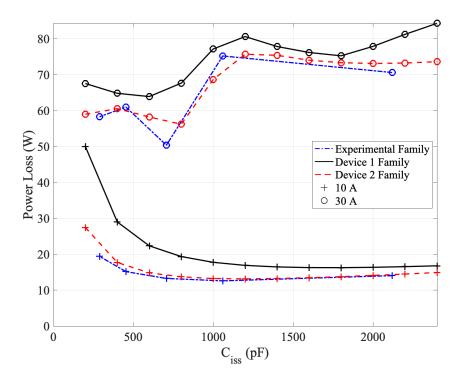

| 3.36 | Impact of Input Capacitance Rating on Power Losses for different manufac-              |     |

|      | turers at 10 A and 30 A                                                                | 79  |

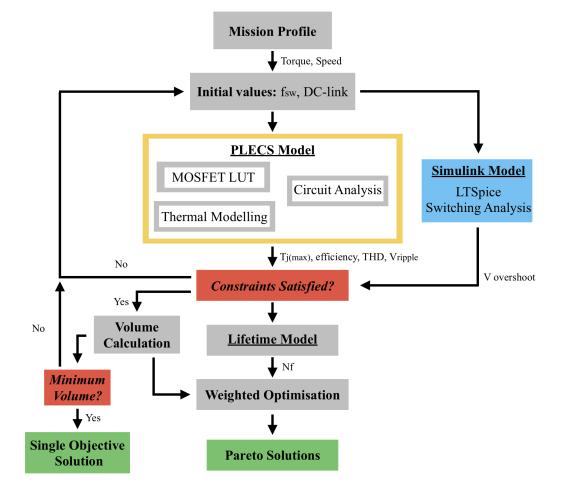

| 4.1  | SiC Power System Design Flow Chart [118]                                               | 85  |

| 4.2  | ESR, thermal resistance, volume and weight as a function of capacitance for            |     |

|      | three different KEMET capacitor series                                                 | 93  |

| 4.3  | Example capacitor lifetime expectancy data for KEMET C4AQ series [127]                 | 99  |

| 4.4  | Illustration of an optimisation-based design where complex models map a                |     |

|      | set of design variables from search space onto the design function space [133]         | 100 |

| 4.5  | Illustration of optimisation with a deterministic algorithm [116]                      | 101 |

| 4.6  | Flow chart of the optimisation algorithm                                               | 102 |

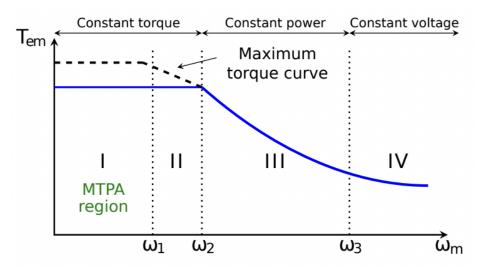

| 4.7  | Torque vs speed curve and operating regions of PMSMs [22]                              | 103 |

| 4.8  | PMSM Torque-Speed data for different Operating Modes                               | 104   |

|------|------------------------------------------------------------------------------------|-------|

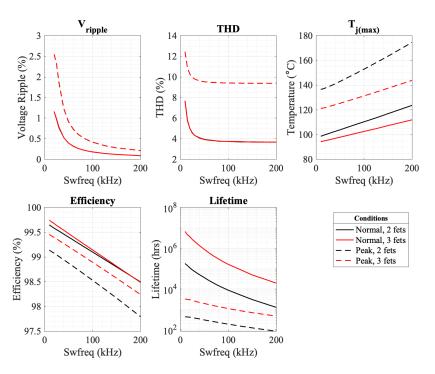

| 4.9  | Inverter parameters as functions of switching frequency with increasing            |       |

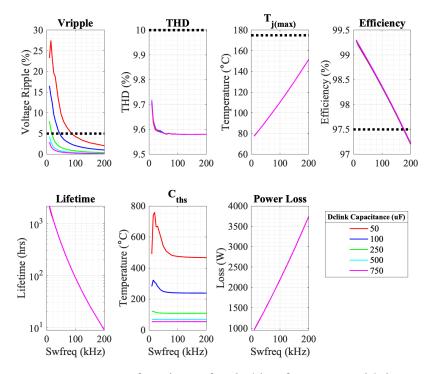

|      | DC-link capacitance under normal conditions                                        | 107   |

| 4.10 | Inverter parameters as functions of switching frequency with increasing            |       |

|      | DC-link capacitance under peak conditions                                          | 107   |

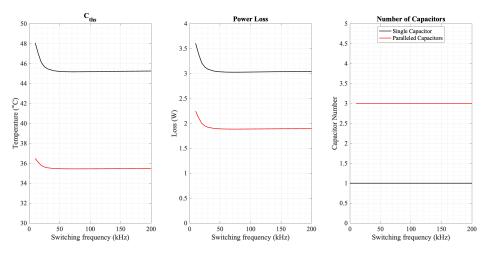

| 4.11 | Effect of paralleling capacitors on hot spot temperature and power loss as         |       |

|      | functions of switching frequency under normal operation                            | 109   |

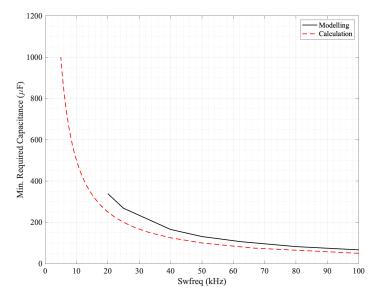

| 4.12 | Optimisation data for the minimum required capacitance as a function of            |       |

|      | switching frequency under normal operation, comparing calculated values            |       |

|      | with results from the optimisation using PLECS system model                        | 110   |

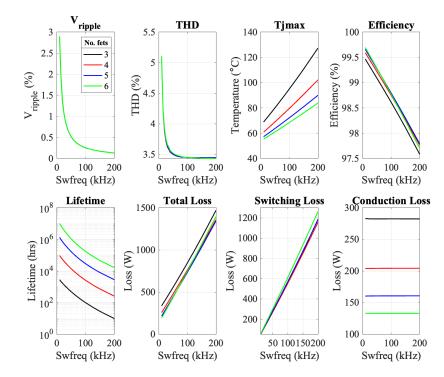

| 4.13 | Inverter parameters as functions of switching frequency under normal oper-         |       |

|      | ating conditions, a heat sink temperature of 50°C and a 250 $\mu$ F capacitor, for |       |

|      | different numbers of paralleled MOSFETs                                            | 111   |

| 4.14 | Inverter parameters as functions of switching frequency with decreasing the        |       |

|      | number of paralleled MOSFETs under peak operating conditions, 50°C for a           |       |

|      | 250 $\mu$ F capacitor                                                              | 112   |

| 4.15 | Optimisation results for the minimum required capacitance and inverter             |       |

|      | volume as a function of number of inverter MOSFETs, for normal operation           |       |

|      | at different heat sink temperatures                                                | 113   |

| 4.16 | Inverter parameters as functions of switching frequency with increasing heat       |       |

|      | sink temperature under normal operating conditions, DC-link capacitance of         |       |

|      | $250 \mu\text{F}$                                                                  | 114   |

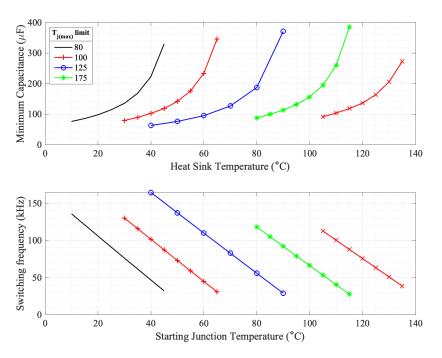

| 4.17 | Optimisation results for the minimum required capacitance and the corre-           |       |

|      | sponding switching frequency as a function of heat sink temperature for            |       |

|      | increasing MOSFET junction temperature limit for normal operating conditions       | \$116 |

| 4.18 | Optimisation results for the minimum required capacitance and the corre-           |       |

|      | sponding switching frequency as a function of heat sink temperature for            |       |

|      | increasing MOSFET junction temperature limit for peak operating conditions         | 5117  |

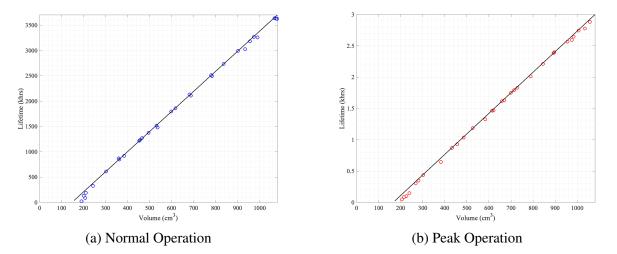

| 4.19 | Multi-objective optimisation results considering reliability and volume under            |   |

|------|------------------------------------------------------------------------------------------|---|

|      | normal and peak operation                                                                | 3 |

| 4.20 | Multi-objective optimisation results considering lifetime and volume for the             |   |

|      | combined operation of the system, with key points identified                             | ) |

| 4.21 | Multi-objective optimisation results considering lifetime and switching for              |   |

|      | the combined operation of the system, with key points identified 12                      | 1 |

| 4.22 | Comparison of Pareto front between volume and lifetime for 4, 5 and 6                    |   |

|      | paralleled MOSFETs                                                                       | 2 |

| 5.1  | Strengths, weaknesses, opportunities, and threats analysis of multi-phase                |   |

|      | inverters (MPIs) [53]                                                                    | ) |

| 5.2  | General phase distribution in n-phase inverters for different spatial displace-          |   |

|      | ment configurations. (a) Symmetric: $\delta = 2\pi/n$ (b) Asymmetric: $\delta = \pi/n$ , |   |

|      | k = (n-3)/3 for <i>n</i> multiples of 3 [53]                                             | ) |

| 5.3  | Reduced per-phase current requirements in MPIs [142]                                     | 1 |

| 5.4  | DC-link capacitor capacitance and RMS current ratings comparison among                   |   |

|      | different phase number VSIs [142]                                                        | 2 |

| 5.5  | Schematic of dual inverter traction drive system                                         | 3 |

| 5.6  | Stator winding arrangement for (a) asymmetrical six-phase, (b) symmetrical               |   |

|      | six-phase, and (c) dual three-phase machines [146]                                       | 3 |

| 5.7  | Interleaved carriers of dual inverter system                                             | 5 |

| 5.8  | Effect of interleaving on circuit parameters in the dual inverter system, at 40          |   |

|      | kHz switching frequency with 100 $\mu$ F DC-link capacitance                             | 5 |

| 5.9  | Six-phase to five-phase voltage conversion. (a) Original six-phase waveform              |   |

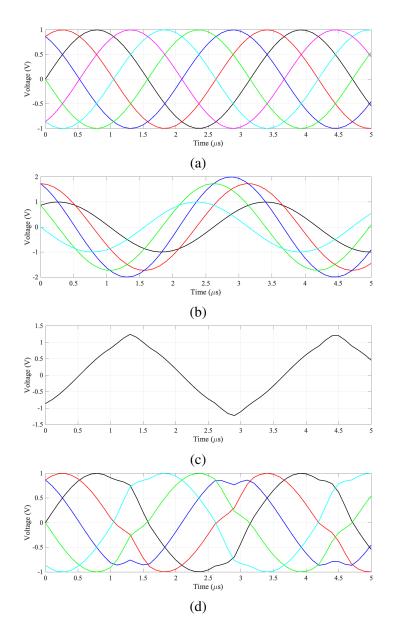

|      | (b) Voltage reference signals (c) Zero sequence signal (d) Five-phase waveform 139       | ) |

| 5.10 | Dual inverter current outputs after fault in phase 6 (a) Inverter 1 - phases 1 to        |   |

|      | 3 (b) Inverter 2 - phases 4 to 6                                                         | ) |

| 5.11 | Thermal resistance of the cold plate with different flow rate                            | 2 |

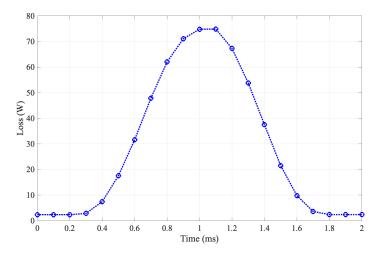

| 5.12 | MOSFET power Loss during one thermal cycle                                               | 3 |

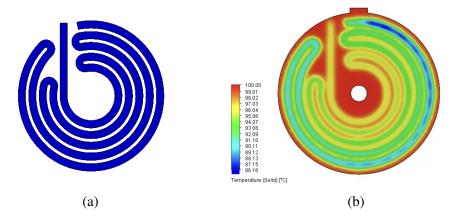

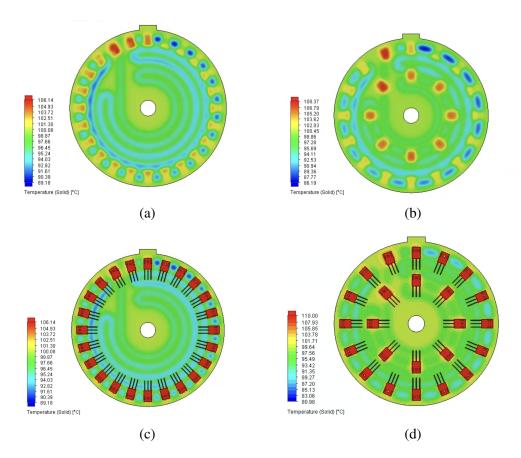

| 5.13 | PMSM cooling system (a) Shape (300mm diameter) (b) temperature profile                             |     |

|------|----------------------------------------------------------------------------------------------------|-----|

|      | with 100°C wall temperature and 70 °C coolant flowing at 15 L/min $\ldots$                         | 144 |

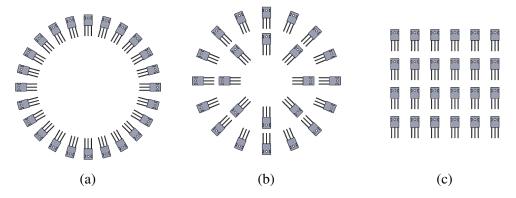

| 5.14 | MOSFET arrangements (a) Concentric (b) Concentric-2 (c) Square                                     | 145 |

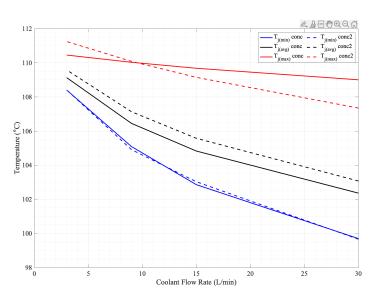

| 5.15 | Effect of coolant flow on MOSFET junction temperatures in the concentric                           |     |

|      | and concentric-2 arrangements, for 70 °C coolant temperature                                       | 146 |

| 5.16 | Thermal analysis of the concentric and concentric-2 arrangements for 24                            |     |

|      | MOSFETs showing board and MOSFET irregularity, at a flow rate of 15                                |     |

|      | L/min and flow temperature of 70 °C                                                                | 147 |

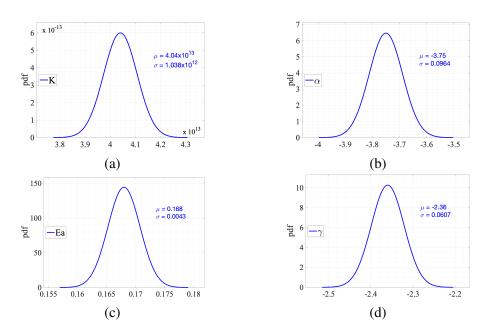

| 5.17 | Normal distribution of the factors from the strength model. (a) $K$ , basic                        |     |

|      | constant, (b) $\alpha$ , Coffin-Manson exponent (c) $E_a$ , activation energy (d) $\gamma$ ,       |     |

|      | exponent for the current per bond                                                                  | 149 |

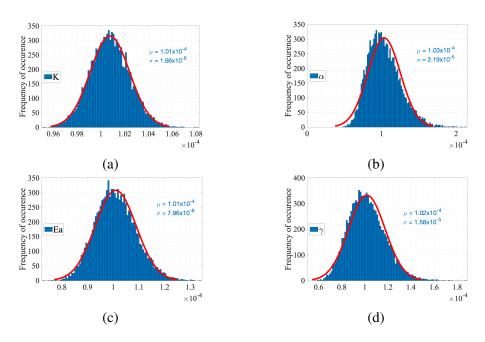

| 5.18 | Annual damage distribution considering the parameter variation in the life-                        |     |

|      | time model. (a) K, basic constant, (b) $\alpha$ , Coffin-Manson exponent (c) $E_a$ ,               |     |

|      | activation energy (d) $\gamma$ , exponent for the current per bond                                 | 150 |

| 5.19 | Monte Carlo analysis for lifetime calculation combining all parameter varia-                       |     |

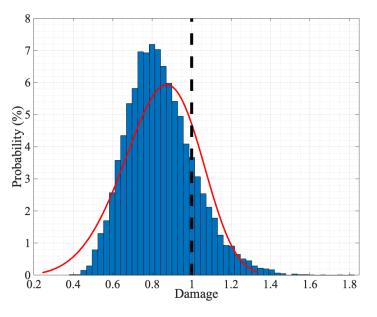

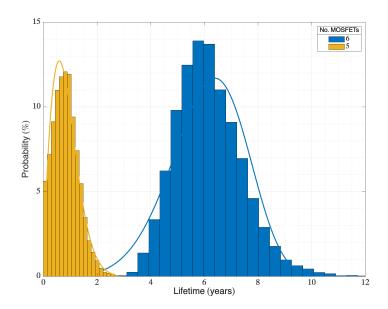

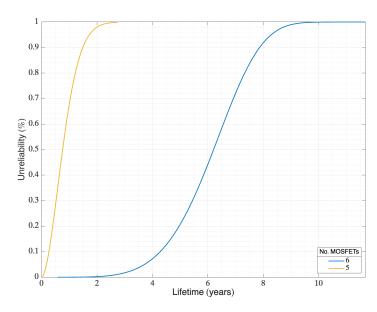

|      | tion (a) Annual damage; (b) Time-to-failure distribution; (c) Unreliability .                      | 151 |

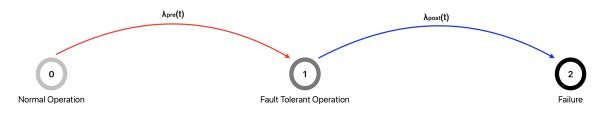

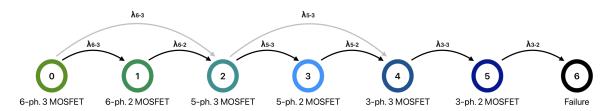

| 5.20 | Proposed reliability evaluation method based on Markov Chain model ap-                             |     |

|      | plied to fault-tolerant power converter with non-constant failure rates (i.e.,                     |     |

|      | $\lambda_{pre}(t)$ and $\lambda_{post}(t)$ )                                                       | 152 |

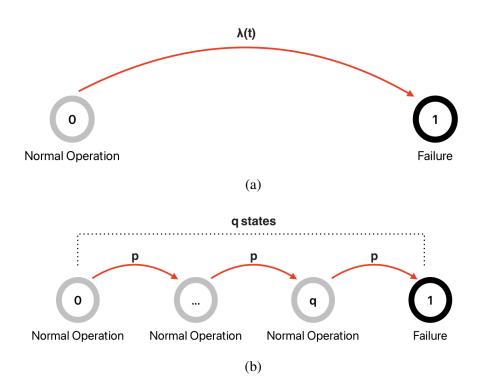

| 5.21 | Markov Chain model of non fault-tolerant power converter represented by:                           |     |

|      | a) Weibull distribution failure rate $\lambda_{wb}(t)$ and b) method of stages with $q$            |     |

|      | states with exponential distribution failure rate of $p$                                           | 154 |

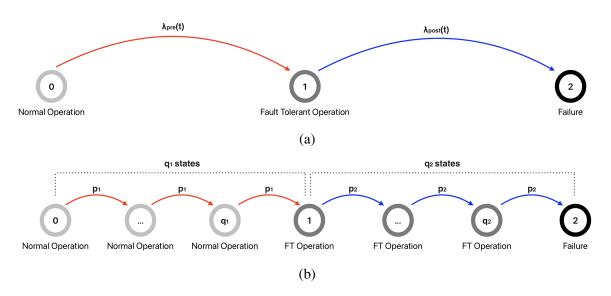

| 5.22 | Markov Chain model of fault-tolerant power converter represented by: a)                            |     |

|      | Weibull distribution where $\lambda_{pre}(t)$ and $\lambda_{post}(t)$ are the failure rates during |     |

|      | pre-fault and post-fault operation, respectively, and b) method of stages with                     |     |

|      | q1 states representing the pre-fault operation with exponential distribution                       |     |

|      | failure rate of $p1$ and $q2$ states representing the post-fault operation with an                 |     |

|      | exponential distribution failure rate of $p2$                                                      | 156 |

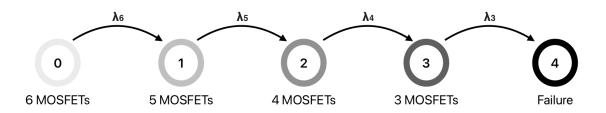

| 5.23 | Markov chain for three-phase inverter 'switch' with six paralleled MOSFETs                         | 157 |

| 5.24 | Reliability analysis of three-phase inverter with the proposed Monte Carlo        |     |

|------|-----------------------------------------------------------------------------------|-----|

|      | simulation method showing accumulated damage distribution after 10 years.         |     |

|      | Where the failed devices, those with damage over 1 are highlighted                | 158 |

| 5.25 | Reliability analysis of three-phase inverter with the proposed Monte Carlo        |     |

|      | simulation method showing accumulated damage distribution after 10 years          | 158 |

| 5.26 | Unreliability of pre-fault (6 MOSFETs functioning) and post fault (5 MOS-         |     |

|      | FETs functioning) operation                                                       | 159 |

| 5.27 | Reliability analysis of three-phase inverter with the proposed Monte Carlo        |     |

|      | simulation method showing accumulated damage distribution after 10 years          | 160 |

| 5.28 | Markov chain for dual three-phase inverter, with fault tolerant conditions        | 160 |

| 5.29 | Inverter parameters as functions of switching frequency for a 250 $\mu$ F ca-     |     |

|      | pacitor at each inverter, comparing number of paralleled MOSFETs and              |     |

|      | operating conditions                                                              | 162 |

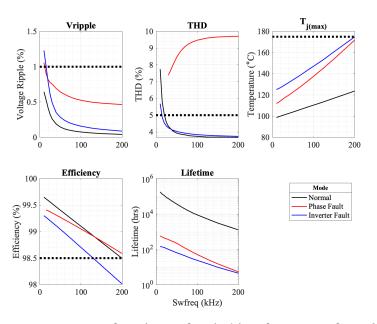

| 5.30 | Inverter parameters as functions of switching frequency for a 250 $\mu$ F DC-link |     |

|      | capacitance, comparing normal and fault tolerant modes                            | 164 |

| 5.31 | Inverter parameters as functions of switching frequency with decreasing the       |     |

|      | number of paralleled MOSFETs under normal operating conditions, 50°C              |     |

|      | for a 250 $\mu$ F capacitor                                                       | 165 |

| 5.32 | Inverter parameters as functions of switching frequency with decreasing the       |     |

|      | number of paralleled MOSFETs under normal operating conditions, 50°C              |     |

|      | for a 250 $\mu$ F capacitor                                                       | 166 |

| 5.33 | Multi-objective optimisation results considering lifetime and volume for the      |     |

|      | combined operation of the system, comparing three-phase and dual inverter,        |     |

|      | with key points identified                                                        | 168 |

| 5.34 | Multi-objective optimisation results considering lifetime and switching fre-      |     |

|      | quency for the combined operation of the system, comparing three-phase            |     |

|      | and dual inverter, with key points identified                                     | 169 |

# List of tables

| 2.1 | Properties and FOM for Si, SiC and GaN [39]                                   | 18  |

|-----|-------------------------------------------------------------------------------|-----|

| 3.1 | Manufactured 1.2 kV SiC Devices                                               | 43  |

| 3.2 | DPT Circuit Parasitic Values                                                  | 49  |

| 3.3 | Comparison of Turn-On Switching for Experimental and Analytical               | 51  |

| 3.4 | MOSFET Characteristics                                                        | 53  |

| 3.5 | Infineon Family of Devices                                                    | 53  |

| 3.6 | Devices Ordered by Power loss at 150 A and 40 kHz                             | 76  |

| 3.7 | Alternative Manufacturer Devices                                              | 79  |

| 4.1 | PMSM Parameters                                                               | 86  |

| 4.2 | Required paralleled device numbers and power losses using the DST at          |     |

|     | normal operation for min. and max. switching frequency                        | 91  |

| 4.3 | Required paralleled device numbers and power losses using the DST at peak     |     |

|     | operation for min. and max. switching frequency                               | 91  |

| 4.4 | Summary of parameters in proposed lifetime model for TO-247 package [71]      | 98  |

| 4.5 | PMSM Operating Conditions                                                     | 104 |

| 4.6 | Design Example Specification and Constraints                                  | 105 |

| 4.7 | Optimisation results for normal operation of six paralleled MOSFET inverter   |     |

|     | at a junction temperature limit of 100 °C at a range of heat sink temperature | 115 |

| 5.1 | PMSM Operating Conditions                                                     | 136 |

| 5.2 | Fault Conditions of the dual inverter system                                  | 141 |

| 5.3 | Thermal analysis method comparison           | 146 |

|-----|----------------------------------------------|-----|

| 5.4 | Design Example Specification and Constraints | 167 |

# Nomenclature

### Acronyms

| AHM               | Axially housing mounted                                                |

|-------------------|------------------------------------------------------------------------|

| ASC               | Active short circuit                                                   |

| ASM               | Axially stator mounted                                                 |

| BEV               | Battery electric vehicle                                               |

| CDF               | Cumulative distribution function                                       |

| CFD               | Computational fluid dynamics                                           |

| CTE               | Coefficient of thermal expansion                                       |

| DFVC              | Direct flux vector control                                             |

| DFVC              | Direct nux vector control                                              |

| DPVC              | Double-pulse test                                                      |

|                   |                                                                        |

| DPT               | Double-pulse test                                                      |

| DPT<br>DUT        | Double-pulse test<br>Device under test                                 |

| DPT<br>DUT<br>EMI | Double-pulse test<br>Device under test<br>Electromagnetic interference |

| FOM    | Figure of merit                                   |

|--------|---------------------------------------------------|

| GaN    | Gallium nitride                                   |

| IMD    | Integrated motor drive                            |

| IMMD   | Integrated modular motor drive                    |

| LUT    | Look-up table                                     |

| MLI    | Multi-level inverter                              |

| MOSFET | Metal-oxide-semiconductor field-effect transistor |

| MPI    | Multi-phase inverter                              |

| MPPF   | Metallised polypropylene film                     |

| NPC    | Neutral point converter                           |

| PDF    | Probability distribution function                 |

| PE     | Power electronics                                 |

| PMSM   | Permanent magnet synchronous motor                |

| PWM    | Pulse width modulation                            |

| RHM    | Radially housing mounted                          |

| RSM    | Radially stator mounted                           |

| SiC    | Silicon carbide                                   |

| SVPWM  | Space vector pulse width modulation               |

| THD    | Total harmonic distortion                         |

| TRN    | Thermal resistance network                        |

| VSI                     | Voltage source inverter                                     |

|-------------------------|-------------------------------------------------------------|

| WBG                     | Wide bandgap                                                |

| Variables               |                                                             |

| α                       | Coffin-Manson exponent                                      |

| $\Delta T$              | Temperature swing                                           |

| $\Delta V_{pp}$         | Voltage ripple                                              |

| η                       | Efficiency                                                  |

| λ                       | Thermal conductivity                                        |

| $\lambda_f$             | Failure rate                                                |

| $\mu_n$                 | Electron mobility                                           |

| <b>V</b> <sub>sat</sub> | Saturation electron drift velocity                          |

| $\omega_m$              | Mechanical speed                                            |

| $\phi_d$                | D axis flux                                                 |

| $\phi_m'$               | Flux induced by magnets                                     |

| $\phi_q$                | Q axis flux                                                 |

| $\mathcal{E}_r$         | Relative dielectric constant                                |

| $B_x$                   | Time when a group of samples has $x$ probability of failure |

| $C_{DS}$                | Drain-source capacitance                                    |

| $C_{GD}$                | Gate-drain capacitance                                      |

| $C_{GS}$                | Gate-source capacitance                                     |

| C <sub>iss</sub>        | Input capacitance              |

|-------------------------|--------------------------------|

| C <sub>min</sub>        | Minimum required capacitance   |

| Coss                    | Output capacitance             |

| $C_{ploss}$             | Power loss from capacitor      |

| C <sub>rss</sub>        | Reverse transfer capacitance   |

| $C_{ths}$               | Capacitor hot spot temperature |

| D                       | Damage                         |

| $E_A$                   | Activation energy              |

| $E_G$                   | Bandgap                        |

| F                       | Friction constant              |

| <i>F<sub>com</sub></i>  | Failure function of component  |

| F <sub>sub</sub>        | Failure function of sub-system |

| $f_{sw}$                | Switching frequency            |

| <i>F</i> <sub>sys</sub> | Failure function of system     |

| FOM <sub>iss</sub>      | Input figure of merit          |

| <i>g</i> <sub>m</sub>   | Transconductance               |

| $I_0$                   | Full load current              |

| I <sub>b</sub>          | Current per bond               |

| I <sub>D</sub>          | Drain current                  |

| i <sub>d</sub>          | D axis flux current            |

#### xxvi

| $I_g$               | Gate current                |

|---------------------|-----------------------------|

| $i_q$               | Q axis flux current         |

| $I_{C(RMS)}$        | Capacitor RMS current       |

| J                   | Inertia                     |

| Κ                   | Basic lifetime              |

| k                   | Boltzmann's constant        |

| L                   | Load inductance             |

| $L_d$               | D axis stator inductance    |

| $L_q$               | Q axis stator inductance    |

| $L_{\sigma}$        | Parasitic inductance        |

| $L_{\sigma}$        | Stator leakage inductance   |

| n                   | Voltage stress factor       |

| $N_f$               | Number of cycles to failure |

| $Q_{GD}$            | Gate-drain charge           |

| $Q_{GS}$            | Gate-source charge          |

| $Q_g$               | Total gate charge           |

| Qiss                | Input gate charge           |

| $R_G$               | Gate resistance             |

| $R_s$               | Stator resistance           |

| R <sub>DS(on)</sub> | On-state resistance         |

| R <sub>ESR</sub> | Capacitor equivalent series resistance           |

|------------------|--------------------------------------------------|

| $R_{G_{int}}$    | Internal gate resistance                         |

| $R_{th,c-a}$     | Thermal resistance between capacitor and ambient |

| $R_{th,j-c}$     | Thermal resistance between junction and case     |

| $T_a$            | Ambient temperature                              |

| $T_e$            | Electromagnetic torque                           |

| $t_f$            | Fall time                                        |

| $T_j$            | Junction temperature                             |

| $T_m$            | Load torque                                      |

| t <sub>r</sub>   | Rise time                                        |

| $t_{d(off)}$     | Turn-off delay time                              |

| $t_{d(on)}$      | Turn-on delay time                               |

| $t_{d(on)}$      | Turn-on delay time                               |

| $T_{hs}$         | Heat sink temperature                            |

| $T_{jm}$         | Mean junction temperature                        |

| $T_{max}$        | Maximum operating temperature                    |

| ton              | Load pulse duration                              |

| V <sub>DD</sub>  | Applied drain voltage                            |

| V <sub>DS</sub>  | Drain-source voltage                             |

| $V_{GG}$         | Applied gate voltage                             |

| V <sub>GS</sub>     | Gate-source voltage    |

|---------------------|------------------------|

| V <sub>miller</sub> | Miller plateau voltage |

| Vovershoot          | Voltage overshoot      |

| $V_{pl}$            | Plateau voltage        |

| V <sub>th</sub>     | Threshold voltage      |

## Chapter 1

## Introduction

The transportation sector is a significant contributor to greenhouse gas emissions, with vehicles being responsible for approximately 14% of global emissions [1]. Governments and industry worldwide are moving towards a greener, more sustainable future with the UK setting a target of net zero carbon emissions by 2050 and ending the sale of new petrol and diesel cars by 2030 [2]. Recent studies have also highlighted the damaging health damage effects of the transport industry, with pollution from petrol and diesel vehicles linked to an estimated 40,000 early deaths in the UK and a cost to the NHS and society in general of more than £6 billion annually [3]. The emergence of electric vehicles (EVs) and the move to low emission transport provides one solution to these complex problems.

The global electric passenger car stock between 2010 and 2020 is shown in Figure 1.1. After a decade of rapid growth, global electric car stock reached 10 million in 2020, with a 43% increase in sales from 2019, the majority made up of all-electric battery electric vehicles (BEVs). The increasing demand for EVs is driving significant advancements in technology, resulting in improved performance, driving range, and charging times. The average driving range of new BEVs has been steadily increasing. In 2020, the weighted average range for a new battery electric car was about 350 kilometres (km), up from 200 km in 2015 [4]. Consumer doubts still remain when it comes to range, reliability and performance, but with continued investment and innovation, EVs have the potential to revolutionise the transportation sector.

Fig. 1.1 Global electric passenger car stock, 2010-2020 [4]

### **1.1 Integrated Motor Drives**

Power electronic (PE) converters in EVs determine a large part of the vehicle's efficiency and power output, with trends moving toward smaller, high-power-density components. Furthermore, the Department of Energy has set a power density target for automotive power electronics (PE) at 100 kW/L by 2025 due to the limited space in vehicles [5]. The integration of the power converter and electric machine results in a drive with high power density, low volume, and superior efficiency [6, 7]. This ultimately contributes to the development of lighter and more compact vehicles with extended range capabilities.

Current research has proposed a variety of techniques for the functional and structural integration of the PE converter with the machine, ranging from simple mounting of the converter on the machine housing to high levels of modular integration. Figure 1.2 shows some of the possible designs for IMDs used in automotive applications.

By combining the cooling and housing systems, both volume and weight are minimised. Additionally, in IMDs cabling connecting the power converter and machine can be eliminated, reducing electromagnetic interference (EMI) and making output filters redundant [8]. As a result, system reliability is enhanced, cost is reduced, and volume is further decreased.

Fig. 1.2 Four categories of IMDs (a) Rotor Housing Mounted (RHM); (b) Axial Housing Mounted (AHM); (c) Radial Stator-iron Mounted (RSM); (d) Axial Stator-iron Mounted (ASM) [6]

Despite the attractive opportunities that IMDs present for EVs, there are still challenges to optimise their design and achieve widespread use, especially when considering the system PE. The thermal coupling of the motor and converter poses new challenges for the heat dissipation of the system. Without a careful approach to the system-level design of IMDs, a combination of thermal and mechanical problems can cause damage to the components of the converter, leading to low reliability and performance issues.

### **1.2 Application of Wide bandgap Semiconductors**

Robust electronic components capable of withstanding the harsh environments required in IMDs have been a major focus of power electronic research and development in the last decade [9]. Wide bandgap (WBG) semiconductors such as GaN (gallium nitride) and SiC (silicon carbide) are regarded as the next-generation power semiconductor for automotive applications due to their superior properties such as high switching frequency, low switching loss, and better thermal capability [10, 11]. These properties translate into lower volume, high performance inverters capable of operating effectively in high temperature environment,

such as an IMD, and the efficiency benefits offered by SiC inverters can result in higher driving range or a lower requirement on the installed battery energy storage.

Discrete MOSFET packages and power modules are two common methods of packaging power SiC devices. Power modules can offer certain advantages in terms of convenience and until recently were far better suited to the high load currents in high power drives. However, discrete MOSFET packages are becoming more common due to recent developments, with discrete SiC MOSFETs available up to 225 A [12], alongside their greater design flexibility, thermal management, and more cost-effective nature.

### **1.3 Importance of Reliability**

The power train is one of the most critical components in electric vehicles (EVs) because it controls the transmission of power from the battery to the wheels. The reliability of the system is defined in this work as the probability that it will perform its required function without failure, under stated conditions for a specified period of time. Any malfunction in the power train can cause reduced performance, safety hazards, and complete failure of the vehicle. Therefore, high reliability is essential to ensure that the vehicle functions consistently and without significant issues or failure. A reliable power train is important to ensure that the EV can provide a smooth, consistent and safe driving experience.

Moreover, the power train in EVs is a costly component, and repairs can be timeconsuming and expensive [13]. Ensuring the reliability of the power train is critical to prevent unexpected downtime and repair costs, which can increase customer satisfaction and confidence in the technology. Reliability is of significant interest in IMDs for EVs because designs with high volumetric power density without consideration of the high temperature environment of the inverter can lead to highly unreliable systems with short lifetimes [14].

### **1.4 Research question and contribution**

The key question this thesis aims to answer is:

• How can an integrated motor drive be designed so that it is optimal?

The definition of optimal is dependent on the chosen application for the IMD, however a key new factor in this work is the importance of the reliability of the system. Much of the work in this thesis is about the design process for IMDs, with examples applied to show the effectiveness of the developed methods and the potential for the improvements in this research area. Below are the key outcomes from the thesis.

- Experimental investigation into SiC discrete family comparison enabling understanding of combined effects of MOSFET parameters and allowing validation of simulation models.

- Development of novel SiC discrete device selection tool, including the capability for paralleling and temperature input. Applicable to a range of MOSFETs from different manufacturers.

- 3. Novel use of TO-247 package lifetime prediction data to carry out a multi-objective optimisation methodology for a three-phase IMD using combination of PLECS and Matlab-Simulink to demonstrate a system-level electrothermal simulation. This is then used to find optimal design solutions in terms of volumetric power density and reliability optimisation.

- New lifetime calculation based on incremental damage theory suited for paralleled MOSFETs and fault tolerant inverter topologies.

- 5. Multi-objective of dual three-phase inverter and six-phase PMSM, using the novel reliability calculation and detailed computational fluid dynamics (CFD) analysis, allows comparison with the conventional three-phase IMD.

### **1.5** Thesis Structure

This thesis consists of six chapters. A brief description of each chapter is given below:

- **Chapter 1**: This chapter introduces the importance of EVs in the transition to a net-zero future, as the well as the potential improvement to health globally. Government policy and recent technological advances mean EV sales continue to grow, however further development and innovation is required to achieve the potential of EVs and increase their widespread use. Integrated motor drives that contain a wide bandgap transistor are identified as potential solutions to these challenges, but are a relatively immature technology that needs further investigation to provide an effective and reliable system for EVs.

- Chapter 2: This chapter includes a review of current integrated motor drives, their limitations and challenges. IMD inverter topologies, passive components and semiconductor transistor technologies are investigated with a focus on SiC discrete MOSFETs alongside relevant lifetime prediction methods and reliability analysis. Finally, methods for improving design through optimisation procedures, used throughout this thesis are discussed, particularly relating to IMDs for automotive traction applications.

- **Chapter 3**: This chapter focuses on the investigation of the electrical characteristics and device performance parameters of discrete SiC MOSFETs, with a particular reference to a 1200 V Infineon series. The knowledge gained and data presented is used to establish a device selection methodology for any application, but will be used in this thesis as part of the design of an integrated motor drive.

- Chapter 4: An electrothermal model of the entire power train is built in PLECS allowing component interactions and interdependencies to be investigated. Validated SiC MOSFET models were used in the simulation of a three-phase inverter, allowing system-level simulation under a range of operating conditions. An optimisation procedure to increase volumetric power density by reducing the size of the DC-link capacitor is presented and compared to analytical methods of individual component

sizing and design. A multi-objective optimisation allowed the lifetime, based on a recently developed lifetime model specific to transistors in a TO-247 package, to be considered as an objective function alongside the conflicting variable of inverter volume. A Pareto front identifies a range of possible solutions allowing a single optimal solution for the three-phase inverter to be selected, with its electrothermal performance and characteristics known.

- Chapter 5: A multi-phase integrated drive system is investigated and optimised using PLECS simulation, detailed thermal analysis and a novel lifetime prediction procedure in this chapter. These studies allow optimal parameter selection alongside other important design decisions such as control methods, including fault tolerant designs, as well as thermal management and physical layout considerations.

- **Chapter 6**: Finally, chapter 6 offers a summary of the work presented in this thesis and identifies areas for additional development if this work were to be taken forward in the future.

# **Chapter 2**

# **Literature Review**

## 2.1 Introduction

The ability to reduce volume, weight and increase efficiency of traction power trains is critical to the targets of increased range, performance and therefore popularity of electric vehicles (EV) and the move to a net zero future. The main scope of this project is to design an integrated motor drive (IMD) to meet these targets, while maintaining high reliability, which requires optimised component selection and application of new technologies. In the following chapter IMD are introduced and IMD specific power converters are examined. Wide bandgap semiconductors are discussed as a key enabling technology for development of IMDs with higher volumetric power density and increased reliability. Thermal management strategies for the inverters and machines in IMD systems are outlined before the reliability analysis of motor drives and the approaches to lifetime modelling for power semiconductor devices are presented.

Power converters in IMDs must be designed with consideration for the significant thermal, vibration, and electromagnetic challenges of close coupling with the machine. The use of different topologies and designs in IMDs is an area of further research, with current literature suggesting that the optimal topology choice is dependent on the IMDs application [15].

Aims to increase the power density, reliability, and efficiency of traction drives has prompted active research and development of smaller, more efficient, and reliable power systems. In IMD systems optimised design is required to overcome the challenges associated with limited volume, high temperatures and high mechanical stresses for the power electronic devices and machine components. Advancements in passives and semiconductor device material and packaging have improved the performance of high-power IMDs, making them commercially feasible. Previously a limit of 7.5 kW was acknowledged for commercial IMDs [16] because in early research into IMDs design did not consider the system-level considerations and interconnected nature of the design problem. However, increases in power and power density are expected as WBG devices, improved component materials are fully incorporated, and research continues to grow in regard to optimal configurations, topologies, and thermal design [17].

This thesis comprises research containing all aspects of the power train for a motor drive. Analysis and modelling of the semiconductor power electronics, with a focus on discrete silicon carbide (SiC) devices can lay the foundations for accurate and detailed IMD study. Holistic power train simulation, design and optimisation with a focus on system reliability and power density is then investigated. A comprehensive review of the current research and literature regarding IMD analysis, design and improvement allows novel research opportunities to be identified.

## 2.2 Integrated Motor Drives

Integrated motor drives (IMDs) are a novel concept that has been proposed where all components of the motor drive system are integrated into the motor housing, including power electronics, control electronics, passive components, and heat sink [7]. By doing so, the volumetric power density of the system can be enhanced significantly which is central to improvements in aerospace and electric traction applications [18], [19]. However, the physical integration of the inverter with the machine presents technical challenges that require solutions. Research has proposed constructive solutions to some of these problems and ensure that IMDs are optimised for power density and adaptability using novel technologies and processes [6]. Most of the literature and research exists as reviews of current IMD technologies [7] [20] and design improvements and analysis [21] [22].

### 2.2.1 IMD Topologies

Depending on the location of the power converter, IMDs are classified into four basic topologies: radially housing mounted (RHM), axially housing mounted (AHM), radially stator mounted (RSM) and axially stator mounted (ASM) [23]. These topologies will be presented and reviewed below.

#### **Housing Mounted**

In early IMDs the inverter was housed in a separate enclosure with a separate cooling structure, either on top of the machine housing in the RHM topology [24] or on the end plate in the axial direction in the AHM topology [25] [8].

Housing mounted topologies provide convenient integration without the need for complex design considerations [26]. However, this approach does not consider the entire system perspective, and, as a consequence, volume optimisation is limited. Figure 2.1 illustrates the mechanical construction of RHM and AHM integrated drives.

Fig. 2.1 Demonstration of housing mounted integration topologies (a) RHM: (1) power converter modules, (2) stator, (3) rotor, (4) housing, (5) end plate. (b) AHM: (1) power converter modules, (2) end plate [27]

Variations of housing mounted topology have been proposed with different levels of complexity, but all are generally attractive due to their simplicity, low cost, and ease of implementation [28]. In this topology, the housing provides thermal isolation between the converter and the machine, and by redesigning the housing to accommodate an active cooling system [24], it can also act as a heat sink for the inverter. The housing also improves mechanical stability and provides a mounting surface for the converter [18].

Many low-power housing mounted IMD configurations exist commercially, the majority being pumps, fans, and compressors [29, 16]. High power IMDs are becoming more popular, and with it the opportunity of traction applications, with the Siemens producing the SIVETEC series for EVs in the power range of 30-200 kW with power densities up to 2.6 W/kg [30]. Siemens operates at these power ratings through novel design of a water cooling system between the inverter and motor, leading to a 10-15% weight reduction due to removal of the inverter housing and connections[31].

Nidec has developed a 150 kW housing mounted IMD as the first fully integrated traction motor system . Through using SiC MOSFETs at high switching frequencies it could achieve a significantly reduced volume and weight of 68% and 31% compared to the conventional drive system [32]. UQM developed an AHM integrated electrical traction system for a permanent magnetic motor with a maximum power of 75 kW [33] where both the machine and the inverter are liquid-cooled. The examples provided illustrate the diversity of power ratings and capabilities, and potential of IMDs and show the limitations are mostly dependent on their current suitability to specific applications.

#### Stator mounted

The stator mounted topologies provide more compact integration compared to the housing mounted topologies, but this approach can make design more challenging. Coordination of the systems electrical and thermal design is required because of the heat generation and electromagnetic issues in close integration of IMDs [34]. Figure 2.2 illustrates the mechanical construction of RSM and ASM integrated drives.

Fig. 2.2 Demonstration of stator mounted integration topologies (a) RSM: (1) housing, (2) power converter modules, (3) shared cooling structure, (4) end plate. (b) ASM: (1) housing, (2) power converter modules, (3) shared cooling structure, (4) end plate [27]

The objective of the RSM and ASM configurations is to produce an IMD with an improved volumetric power density, however this often comes at the cost of reduced reliability and efficiency. Modular power converters can be utilised and with individual modules connected in series supplying independent machine windings [8].

The 83 kW Protean electric wheel [35, 36] is among a small number of stator mounted IMDs available commercially. Designing a converter capable of withstanding the high temperatures and high vibrations within the machine enclosure is even more challenging compared to housing mounted IMDs. A liquid cooling system is developed in [36] to cool the converter and machine windings simultaneously with a axial and orthogonal paths to improve heat dissipation.

#### **Integrated Modular Motor Drives**

Modular integration involves segmenting the power electronics into smaller modules that control dedicated stator winding sections. These modules are physically independent of each other and are usually electrically connected together in series or parallel for the purpose of control. Advantages of modular systems include fault tolerance, better thermal capabilities, power rating scalability and a possible reduction in the overall size and cost of the PE.

Drive modularisation is independent of converter position as mounting can occur on the motor housing [37] on the stator iron [17, 38], or on the end plate [39]. Fault tolerance is one obvious advantage as multiple modules exist which form a unit as opposed to a centralised power electronics module and so the system can be designed to allow for individual module failure. Current and voltage loading stress is also reduced in the power electronics (PE) as lower rated components are used in the modules to form a much larger rated unit [40].

Improved thermal capability is another advantage. This is as a result of having individual lower rated components and more evenly distributed heat dissipation [7]. Due to these potential benefits, modular drives are very beneficial for IMD design. In [17], both machine and drive are modularised (one converter phase leg per machine pole) resulting in better thermal performance due to lower rated devices, increase in machine lifespan as a result of low voltage change in the slot insulation layer, lower maintenance cost and fault tolerance. The possible drawbacks are the necessity for a complex control system for the individual power modules and the difficulty of mechanically and structurally integrating the modules with the motor [20].

To further increase the level of integration between the EM and inverter, the concept of an integrated modular motor drive (IMMD) has been proposed [8]. The modularisation of the machine into concentrated winding pole pieces each with integrated drive electronics allows a further reduction in the total drive volume and enables simultaneous optimisation of the machine and inverter characteristics. Lenze offer modular low to mid-range IMDs with power ratings ranging from 0.4-7.5 kW [41]. Commercial high power modular IMDs with ratings up to 16.5 MW are currently manufactured by Siemens under the integrated drive systems range [42].

A prototype nine-phase drivetrain including a PM machine, gearbox and integrated inverter has been developed to demonstrate the concept [43]. The integrated inverter is reported to achieve a power density of 35 kW/litre with the entire system capable of a peak mechanical output power of 60 kW [44].

### 2.2.2 Thermal Management

The complex thermal coupling between the motor and inverter in IMDs can lead to high temperatures in the motor and inverter system, reducing the performance and lifetime of the switching devices and DC-link capacitors. Extensive thermal analysis is required to maximise the potential of IMDs, including evaluation of the converter and machine individually and combined.

#### **Thermal Analysis**

Accurate IMD thermal models has become important as the basis for research and thermal analysis of IMDs, the research system is shown in Figure 2.3. Thermal resistance networks (TRNs) and numerical analysis are the main methods of thermal analysis for power electronics and drives. TRNs rapidly analyse conduction, convection, and thermal radiation resistance for each part of the system. Numerical analysis, consisting of finite element analysis (FEA) and computational fluid dynamics (CFD), is more accurate but more complex, requiring more design information from the inverter system such as detailed dimensions and fluid flow paths in many cases [45].

Fig. 2.3 IMDs integrated thermal design system [6]

#### **Cooling Systems**

Modern IMDs use a combination of active and passive cooling systems due to the extreme thermal demands on the system [46]. Passive cooling system utilises heat dissipation through natural convection, thermal mass, ventilation and thermal isolation. In active cooling system the base plate of the converter or motor can be cooled through forced convection. Generally, liquid cooling provides good heat transfer [47] however it can increase the volume of the system due to the complex heat sink and equipment used for coolant circulation. Forced air cooling increases design flexibility and has low maintenance costs but is less effective than liquid cooling [48]. Thermal coupling between semiconductors and heat sink and cooling mechanisms of passive components impacts the power density significantly. The European Center for Power Electronics (ECPE) has introduced a cooling system performance index to compare power density when using different heat sink designs and demonstrated two water cooled power electronics systems including a 75 kW/l IMD [49].

## 2.3 IMD Converter Topologies

Power converters in IMDs must be designed with consideration for the significant thermal, vibration, and electromagnetic challenges of close coupling with the machine. This section introduces the main converter configurations and topologies that have been analysed extensively in literature [15]. The use of different topologies and designs in IMDs requires more research and the optimal topology choice is dependent on the IMDs application. The main topologies analysed that are relevant to IMDs are:

- Two-level full bridge converter

- Three-level converters

- Multi-phase converters

#### Two-level full bridge converter

The most common converter used in traction system is the two-level full bridge due to its simplicity and flexible control. However, when compared to multi-level topologies it has relatively high current total harmonic distortion (THD), when operated in pulse width modulation (PWM) [50].

#### **Three-level converters**

Multi-level inverters can produce output voltage waveforms with lower harmonics [51], lower  $\frac{dV}{dt}$  and electromagnetic interference (EMI) emissions. Three-level neutral-point and T-type neutral-point converter (NPC) are the most commonly used multi-level inverter topologies [52].

For lower power and low-voltage applications, the NPC suffers from higher conduction loss due to the series connection of two devices in the conduction paths. By contrast, T-type topology has less number of devices in the conduction path, which notably decreases the conduction loss. However, the switching losses in the T-type topology may be higher than that of the NPC due to higher voltage stress over a single-switch position and devices with higher voltage ratings are needed. These issues can be potentially addressed by emerging WBG devices.

#### **Multi-phase converters**

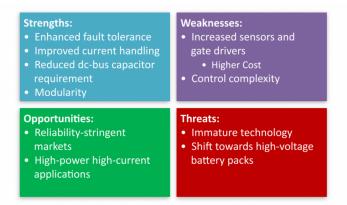

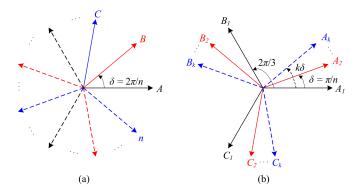

Multi-phase can deliver high-power, due to improved per-phase current handling [53], offer improved fault tolerance capability, lower torque pulsations, better noise characteristics, and modularity [54]. Multi-phase converters require more components and complex control, however lower per-phase current can result in easier structural integration into the machine, and more spatially distributed converter losses.

## 2.4 Semiconductor Power Devices

The growing demand for converters with improved volumetric power density, high efficiency and potential to operate in high temperature environments has led to research on wide bandgap (WBG) semiconductor devices [11]. The majority of research into WBG semiconductors focuses on Silicon Carbide (SiC) and Gallium Nitride (GaN), for which commercial devices are now widely available. IMD design could benefit from the ability of WBG semiconductor devices to operate at high blocking voltages, high temperatures, and high switching frequencies, resulting in a smaller system size while maintaining high efficiency and reliability.

### 2.4.1 Overview of WBG materials

The material properties of SiC and GaN are compared with those of Silicon in Table 2.1 [39]. To allow the comparison of semiconductor materials in power devices, Huang [55], devised figures of merit (FOM) for unipolar devices based on theoretical switching performance, power density and thermal capability. Only 4H-SiC is considered here for SiC, because of its dominance commercially.

|                                                                | Si   | 4H-SiC | GaN  |

|----------------------------------------------------------------|------|--------|------|

| Bandgap, $E_G$ (eV)                                            | 1.1  | 3.2    | 3.4  |

| Relative dielectric constant, $\varepsilon_r$                  | 11.7 | 9.7    | 9.0  |

| Electric breakdown field, $E_C$ (kV/cm)                        | 300  | 3500   | 3300 |

| Electron mobility, $\mu_n$ (cm <sup>2</sup> /Vs)               | 1400 | 650    | 990  |