## **Durham E-Theses**

# HIGH GAIN DC-DC CONVERTER TOPOLOGIES FOR POWER SYSTEMS

ALSAFRANI, ABDULRAHMAN, ESSA

#### How to cite:

ALSAFRANI, ABDULRAHMAN, ESSA (2023) HIGH~GAIN~DC-DC~CONVERTER~TOPOLOGIES~FOR~POWER~SYSTEMS, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/15137/

### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- $\bullet \;$  the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

# HIGH GAIN DC-DC CONVERTER TOPOLOGIES FOR POWER SYSTEMS

## A thesis submitted for the degree of Doctor of Philosophy

## Abdulrahman Essa Alsafrani

Supervised by

Professor Alton Horsfall and Dr Mahmoud Shahbazi

Electrical Engineering

Durham University

United Kingdom

June 2023

## **Abstract**

The voltage levels produced from renewable energy, particularly wave energy converters are relatively low and must be stepped up considerably to enable DC grid integration. This necessitates the use of high voltage gain DC-DC boost converters for power systems. These converters are designed for unidirectional power transfer and provide a high voltage gain (ten times or higher), supporting the high wave energy peak and low average power levels required for the integration of distribution networks. In theory, conventional boost converters are the common basic DC-DC stepup converters. However, these converters often operate with excessive duty cycles to obtain high voltage gain, causing severe voltage stress across devices. The main challenge of the high gain transformerless DC-DC converters is the requirement for an extreme (>80%) duty cycle to achieve the desired gain, resulting in poor efficiencies. This thesis presents the development, analysis, and design advanced high gain DC-DC converter topologies integrating magnetic and capacitive techniques and voltage multiplier circuits. The proposed converters could provide enhanced performance compared to currently available state-of-the-art converter topologies, the main advantages of which are the capability to achieve high voltage gain without the need for an extreme duty cycle, as well as low voltage stress on the switching device and self-balanced voltage levels at the output. In addition, the proposed converters require only a single switch, reducing the complexity of the control strategy. Four transformerless high gain DC-DC topologies are presented; Multilevel Boost Converter (MBC), Switched Inductor Multilevel Boost Converter (SIMBC), Voltage Lift Switched Inductor Multilevel Boost Converter (VLSIMBC) and Z-source Multilevel Boost Converter (ZSMBC), which could achieve the desired gains with

relatively high efficiencies. The operation principles, steady-state relations, and different input circuit strategies to further improve the voltage gain performance of the proposed converters are described. Furthermore, a theoretical analysis of power losses is provided. In addition, laboratory prototypes are developed to experimentally validate the given theories, simulation results and feasibility of the proposed topologies.

## Acknowledgements

First and foremost, I would like to express my sincerest and deepest gratitude to my primary supervisor Professor Alton Horsfall for his outstanding guidance, thoughtfulness, leadership, understanding and patience throughout my PhD research journey. Without his support and guidance, the research in this thesis would not have been completed. Secondly, I would also like to thank my second supervisor Dr Mahmoud Shahbazi for the great support and academic guidance that he has provided to me. I will always treasure his help, encouragement and advice.

I would like to express my special gratitude and thanks to the Kingdom of Saudi Arabia, Qassim University, the Saudi Arabian Cultural Mission, and the Ministry of Education for their financial support and the invaluable PhD Scholarship award.

I would like to acknowledge the support of Mr Ian Hutchinson and his technicians' team in helping with the practical work. I would also like to thank my office mates and colleagues for their assistance, advice and friendship throughout my PhD research at Durham University.

Finally, I would sincerely like to thank my family: my beloved parents and brothers, for their tremendous support. Great thanks to my wife for her support and understanding during my PhD research that made completing this thesis possible. She was always around and assisted in maintaining things in perspective. I appreciate my children Hana and Essa for the patience they showed during my PhD journey.

## **Table of Contents**

## Contents

| Abstr                                                     | act                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                                                                                                    |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Ackno                                                     | owledgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . iii                                                                                                                                |

| Table                                                     | of Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | iv                                                                                                                                   |

| List o                                                    | f Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | vii                                                                                                                                  |

| List o                                                    | f Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | xi                                                                                                                                   |

| List o                                                    | f Abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | xii.                                                                                                                                 |

| Public                                                    | cations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | xiii                                                                                                                                 |

| Chap                                                      | oter 1: Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                                                    |

| 1.1                                                       | Background and Motivation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                                                                                    |

| 1.2                                                       | Power System Distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3                                                                                                                                    |

| 1.3                                                       | High Step-Up DC-DC Converter Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                      |

|                                                           | 1.3.1 Grid Connected Wave Energy Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                      |

| 1.4                                                       | Thesis Objective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                      |

| 1.5                                                       | Thesis Structure.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                      |

| 1.0                                                       | oter 2: A Literature Review of High Step-Up DC-DC Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 12                                                                                                                                 |

| _                                                         | ologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15                                                                                                                                   |

|                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                      |

| 2.1                                                       | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 15                                                                                                                                 |

| 2.1                                                       | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                      |

|                                                           | Categories of DC-DC Boost Converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 17<br>. 18                                                                                                                         |

|                                                           | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 17<br>. 18                                                                                                                         |

|                                                           | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 17<br>. 18<br>. 20                                                                                                                 |

| 2.2                                                       | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 17<br>. 18<br>. 20<br>. 22<br>. 23                                                                                                 |

| 2.2                                                       | Introduction  Categories of DC-DC Boost Converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 17<br>. 18<br>. 20<br>. 22<br>. 23<br>. 24                                                                                         |

| 2.2                                                       | Introduction  Categories of DC-DC Boost Converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 17<br>. 18<br>. 20<br>. 22<br>. 23<br>. 24<br>. 26                                                                                 |

| 2.2                                                       | Introduction  Categories of DC-DC Boost Converters  2.2.1 Isolated/Non-Isolated Converters  2.2.2 Unidirectional/Bidirectional Converters  Topology evaluation of the State-of-the-Art High Gain DC-DC Boost Converters  2.3.1 Conventional Boost Converter  2.3.2 Cascaded Boost Converters  2.3.3 Quadratic Boost Converter  2.3.4 Three-Level Boost Converter                                                                                                                                                                                                                                                                                                                                   | . 17<br>. 18<br>. 20<br>. 22<br>. 23<br>. 24<br>. 26<br>. 27                                                                         |

| 2.2                                                       | Introduction  Categories of DC-DC Boost Converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 17<br>. 18<br>. 20<br>. 22<br>. 23<br>. 24<br>. 26<br>. 27                                                                         |

| 2.2                                                       | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 17<br>. 18<br>. 20<br>. 22<br>. 23<br>. 24<br>. 26<br>. 27<br>. 28                                                                 |

| 2.2                                                       | Introduction  Categories of DC-DC Boost Converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 17<br>. 18<br>. 20<br>. 22<br>. 23<br>. 24<br>. 26<br>. 27<br>. 28<br>. 30                                                         |

| 2.2                                                       | Introduction  Categories of DC-DC Boost Converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 17<br>. 18<br>. 20<br>. 22<br>. 23<br>. 24<br>. 26<br>. 27<br>. 28<br>. 30<br>. 31<br>. 32                                         |

| 2.2                                                       | Introduction  Categories of DC-DC Boost Converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 17<br>. 18<br>. 20<br>. 22<br>. 23<br>. 24<br>. 26<br>. 27<br>. 28<br>. 30<br>. 31<br>. 32<br>. 34                                 |

| 2.2                                                       | Introduction  Categories of DC-DC Boost Converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 17<br>. 18<br>. 20<br>. 22<br>. 23<br>. 24<br>. 26<br>. 27<br>. 28<br>. 30<br>. 31<br>. 32<br>. 34<br>. 36<br>. 38                 |

| 2.2                                                       | Introduction  Categories of DC-DC Boost Converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 17<br>. 18<br>. 20<br>. 22<br>. 23<br>. 24<br>. 26<br>. 27<br>. 28<br>. 30<br>. 31<br>. 32<br>. 34<br>. 36<br>. 38                 |

| 2.2 2.3                                                   | Introduction  Categories of DC-DC Boost Converters  2.2.1 Isolated/Non-Isolated Converters  2.2.2 Unidirectional/Bidirectional Converters  Topology evaluation of the State-of-the-Art High Gain DC-DC Boost Converters  2.3.1 Conventional Boost Converter  2.3.2 Cascaded Boost Converters  2.3.3 Quadratic Boost Converter  2.3.4 Three-Level Boost Converter  2.3.5 Switched Capacitor Converter  2.3.6 Switched Inductor Converter  2.3.7 Voltage Lift Converter  2.3.8 Voltage Multiplier Circuit  2.3.9 Isolated Boost Converters  2.3.10 Coupled Inductor Converters  2.3.11 Z-source Converter  2.3.12 Integrated Converters  Clasification of Step-Up DC-DC Converters with Voltage Gain | . 17<br>. 18<br>. 20<br>. 22<br>. 23<br>. 24<br>. 26<br>. 27<br>. 28<br>. 30<br>. 31<br>. 32<br>. 34<br>. 36<br>. 38<br>. 39<br>. 40 |

| <ul><li>2.2</li><li>2.3</li><li>2.4</li><li>2.5</li></ul> | Introduction  Categories of DC-DC Boost Converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 17<br>. 18<br>. 20<br>. 22<br>. 23<br>. 24<br>. 26<br>. 27<br>. 28<br>. 30<br>. 31<br>. 32<br>. 34<br>. 36<br>. 38<br>. 39<br>. 40 |

| 3.1   | Introduction                                                       | 43    |

|-------|--------------------------------------------------------------------|-------|

| 3.2   | Converter Modes of Operation                                       | 45    |

| J.2   | 3.2.1 Circuit Configuration and Description                        |       |

|       | 3.2.2 Converter Operation Principle                                |       |

| 226   | Steady State Performance Analysis                                  |       |

| 3.3 3 | 3.3.1 Voltage Gain                                                 |       |

|       | 3.3.2 Voltage Gaill                                                |       |

|       |                                                                    |       |

| 3.4 I | Design Consideration                                               |       |

|       | 3.4.1 Inductor Design                                              |       |

|       | 3.4.2 Capacitor Design                                             |       |

|       |                                                                    |       |

| 3.5 S | Simulation and Experimental Verification                           |       |

|       | 3.5.1 High Gain MBC Prototype                                      |       |

|       | 3.5.2 Simulation and Measured Experimental Waveforms               | 64    |

| 3.6 F | Power Loss Analysis and Efficiency Measurement                     | 72    |

|       | 3.6.1 Power Losses in Inductor                                     |       |

|       | 3.6.2 Power Losses in Capacitor                                    |       |

|       | 3.6.3 Power Losses in Switch                                       |       |

|       | 3.6.4 Power Losses in Diodes                                       |       |

|       | 3.6.5 Estimating the Efficiency                                    | 74    |

| 3.7 S | Summary                                                            | 76    |

| Cha   | pter 4: Analysis, Design, and Evaluation of High Gain Switched     |       |

|       | uctor and Voltage Lift Switched Inductor Multilevel Boost Converte | rs 79 |

|       | G                                                                  |       |

| 4.1   | Introduction                                                       | 78    |

| 4.2   | Converters' Operational Analysis                                   | 79    |

|       | 4.2.1 Circuits Architecture Description                            |       |

|       | 4.2.2 Modes of Operation                                           | 81    |

| 4.3   | Steady State Performance Analysis                                  | 86    |

| 11.5  | 4.3.1 Voltage Conversion Ratio                                     |       |

|       | 4.3.2 Voltage Stress                                               |       |

| 4.4   | Simulation and Experimental Verification                           | 0.4   |

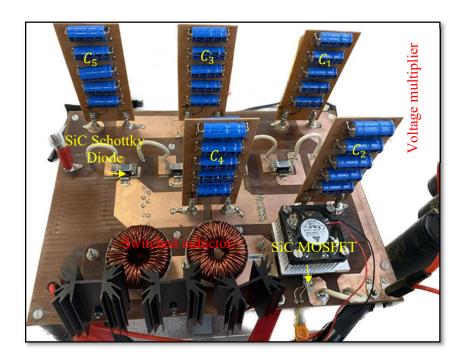

| 4.4   | 4.4.1 High Gain SIMBC and VLSIMBC Prototype                        |       |

|       | 4.4.2 Simulation and Measured Experiment Results                   |       |

|       | 4.4.2.1 Switched Inductor Multilevel Boost Converter               |       |

|       | 4.4.2.2 Voltage Lift Switched Inductor Multilevel Boost Converter  |       |

| 4.5   | Power Loss Analysis and Efficiency Measurement                     |       |

| 4.5   | 4.5.1 Power Losses in Inductor                                     |       |

|       | 4.5.2 Power Losses in Capacitor                                    |       |

|       | 4.5.3 Power Losses in Switch.                                      |       |

|       | 4.5.4 Power Losses in Diodes                                       |       |

|       | 4.5.5 Calculating the Efficiency                                   |       |

| 4.6   | Summary                                                            | 115   |

|       |                                                                    | 113   |

|       | upter 5: A Novel High Gain Z-source Multilevel Boost Converter     |       |

| Ana   | llysis and Design                                                  | 117   |

| 5.1   | Introduction                                                       | 117   |

|       |                                                                    |       |

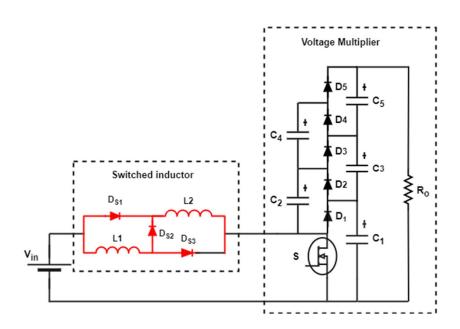

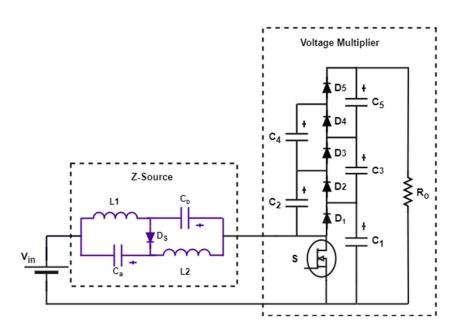

| 5.2   | Propsed Overview                                                   |       |

|       | J.Z.1 CHEUR TOPOLOGY DESCRIPTION                                   | 119   |

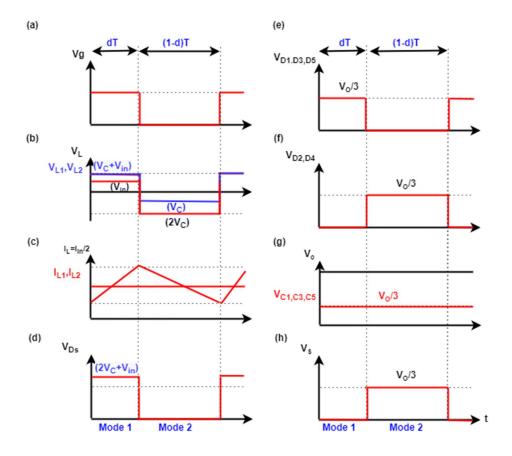

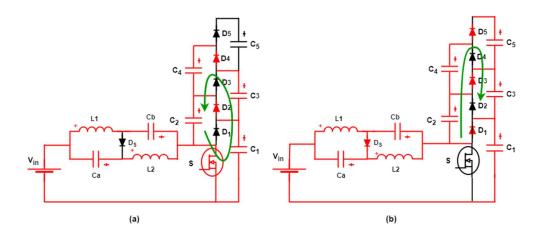

|       | 5.2.2 Circuit Operational Principle                                                                                                                                                                         | 121                      |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 5.3   | Steady State Analysis                                                                                                                                                                                       |                          |

|       | 5.3.2 Power Semiconductor Voltage Stress                                                                                                                                                                    |                          |

| 5.4   | Design Consideration                                                                                                                                                                                        | 130<br>131               |

|       | Range                                                                                                                                                                                                       | 132                      |

| 5.5   | Simulation and Experimental validation                                                                                                                                                                      | 134                      |

| 5.6   | Power Loss Analysis and Efficiency Measurement  5.6.1 Power Losses in Inductor  5.6.2 Power Losses in Capacitor  5.6.3 Power Losses in Switch  5.6.4 Power Losses in Diodes  5.6.5 Computing the Efficiency | 143<br>143<br>143<br>144 |

| 5.7   | Summary                                                                                                                                                                                                     | 147                      |

| Chaj  | pter 6: Conclusion and Future Work                                                                                                                                                                          | 149                      |

| 6.1   | Proposed Topologies Comparison                                                                                                                                                                              | 149                      |

| 6.2   | Summary                                                                                                                                                                                                     | 152                      |

| 6.3   | Future Work                                                                                                                                                                                                 | 156                      |

| Bibli | iography                                                                                                                                                                                                    | 159                      |

|       |                                                                                                                                                                                                             |                          |

## **List of Figures**

| Figure 1.1: Power system distribution.                                                                                                                                              | 5          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Figure 1.2: Schematic representation of a Wave Energy Converter (WEC) and Power Take Off (PTO) system.                                                                              | 7          |

| Figure 1.3: Output voltage from a WEC in Lysekil [27].                                                                                                                              | 8          |

| Figure 1.4: Schematic representation of the three stages SST                                                                                                                        | 10         |

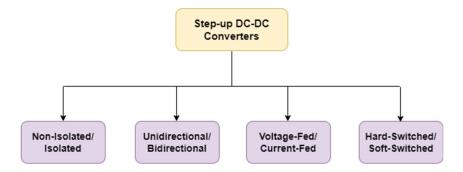

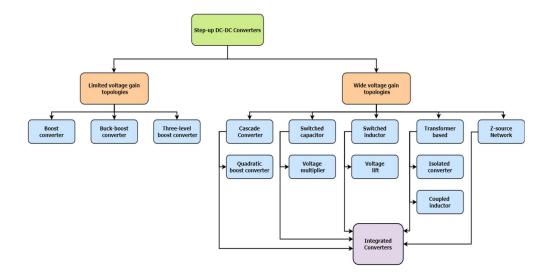

| Figure 2.1: Categories of DC-DC boost converters.                                                                                                                                   | 17         |

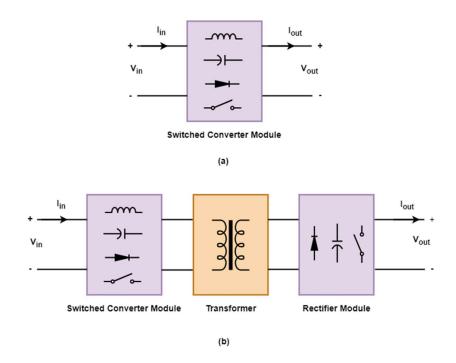

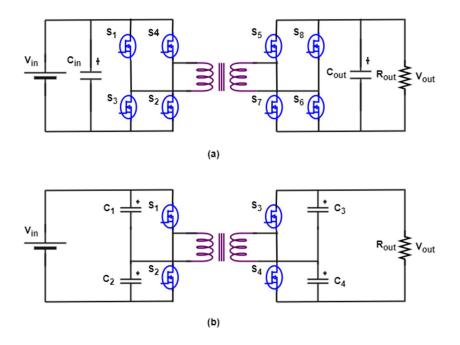

| Figure 2.2: Circuit diagram of non-isolated and isolated DC-DC converters: (a) non-isolated; (b) isolated                                                                           | 18         |

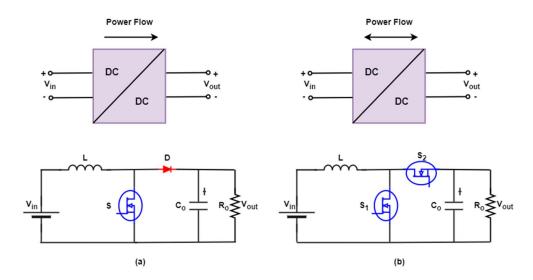

| Figure 2.3: Circuit power flow of non-isolated unidirectional/bidirectional DC-DC converters: (a) unidirectional boost converter; (b) bidirectional boost converter.                | 21         |

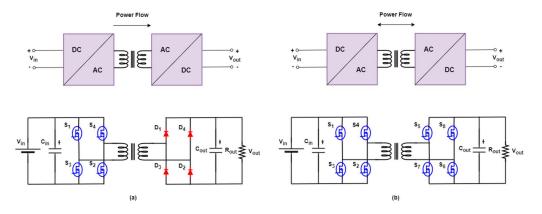

| Figure 2.4: Circuit power flow of isolated unidirectional/bidirectional DC-DC converters: (a) unidirectional full bridge converter; (b) bidirectional dual active bridge converter. | 22         |

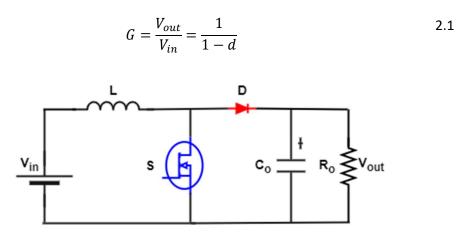

| Figure 2.5: Conventional DC-DC boost converter circuit.                                                                                                                             | 23         |

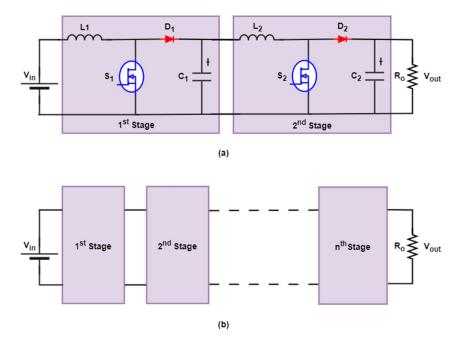

| Figure 2.6: Cascade DC-DC conventional boost converter: (a) two stages; (b) n stages.                                                                                               | 25         |

| Figure 2.7: Quadratic DC-DC boost converter.                                                                                                                                        | 26         |

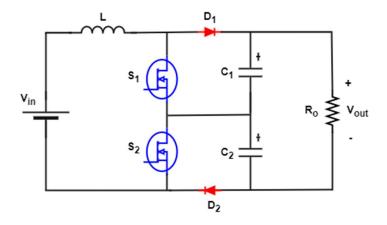

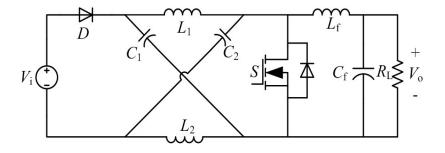

| Figure 2.8: Three level DC-DC boost converter                                                                                                                                       | 28         |

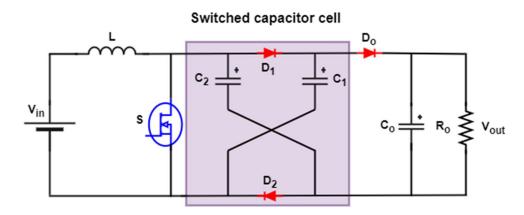

| Figure 2.9: Switched capacitor boost converter                                                                                                                                      | 29         |

| Figure 2.10: Switched inductor boost converter.                                                                                                                                     | 30         |

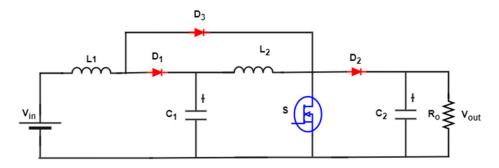

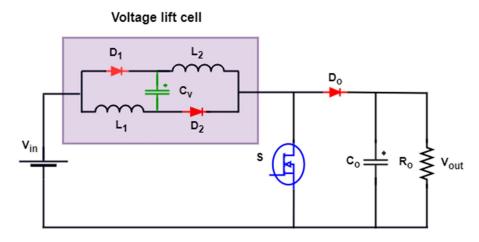

| Figure 2.11: Voltage lift boost converter.                                                                                                                                          | 32         |

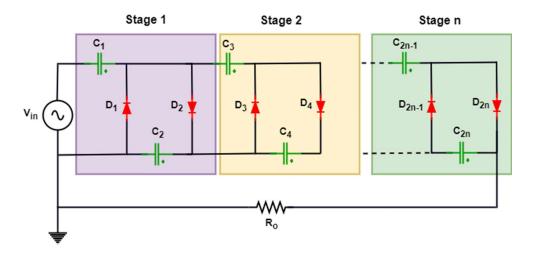

| Figure 2.12: Cockcroft Walton voltage multiplier rectifier circuit                                                                                                                  | 33         |

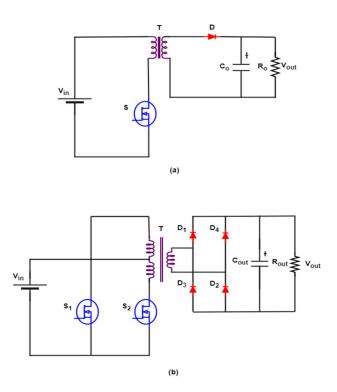

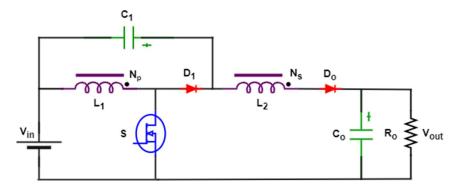

| Figure 2.13: Typical isolated DC-DC boost converter topologies: (a) flyback converter; (b) Push pull converter.                                                                     | 34         |

| Figure 2.14: Isolated DC-DC boost converter topologies: (a) dual active bridge converter; (b) dual half bridge converter.                                                           | 36         |

| Figure 2.15: Coupled inductor boost converter.                                                                                                                                      | 37         |

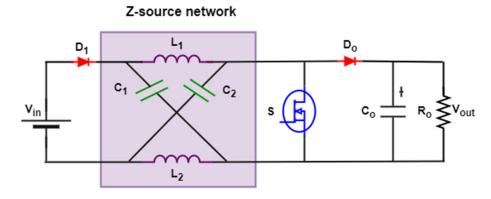

| Figure 2.16: Z-source boost converter.                                                                                                                                              | 38         |

| Figure 2.17: Classification of DC-DC step-up converter topologies with voltage gain                                                                                                 | 41         |

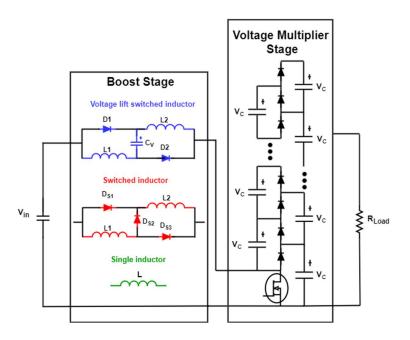

| Figure 3.1: Generalized platform for high voltage gain DC-DC conversion                                                                                                             | 43         |

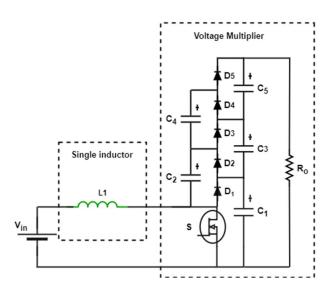

| Figure 3.2: Circuit diagram of the three-level high gain DC-DC MBC.                                                                                                                 | 46         |

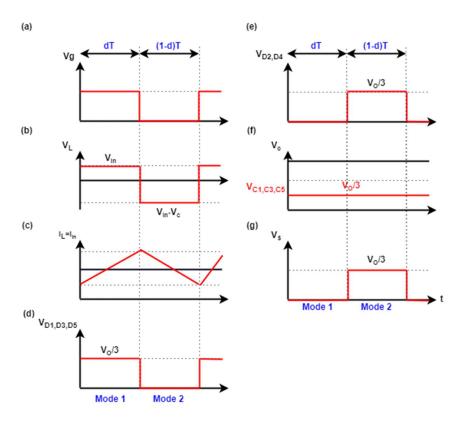

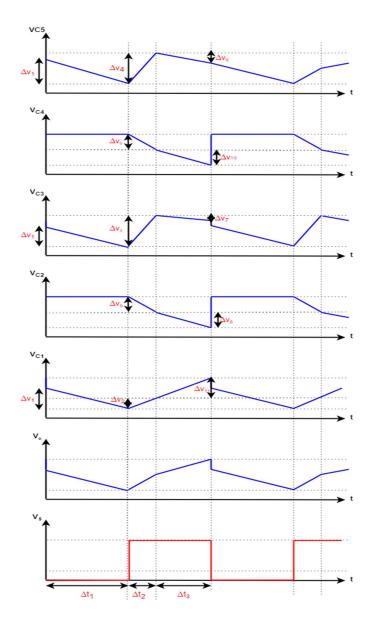

| Figure 3.3: Main steady state waveforms of gate voltage, inductor voltage and current, output diodes voltages, output capacitors voltages and switch voltage for MBC.               | <b>Δ</b> 7 |

| 101mg 101 mbc.                                                                                                                                                                      | т/         |

| Figure 3.4: Operation of the three- level MBC when the switch is ON                                                                                                                 | 48   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 3.5: Operation of the three-level MBC when the switch is OFF                                                                                                                 | 49   |

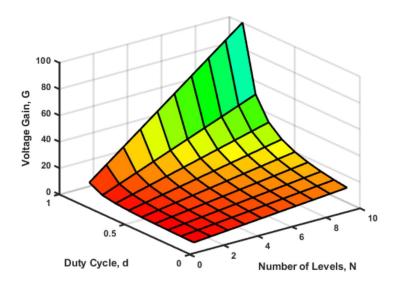

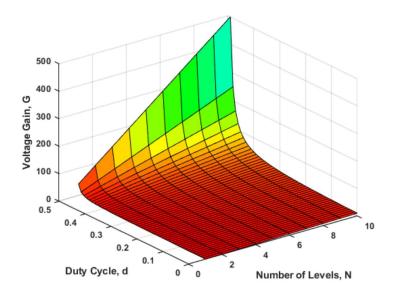

| Figure 3.6: Ideal Voltage gain characteristic of the MBC as a function of <i>d</i> and <i>N</i> values                                                                              |      |

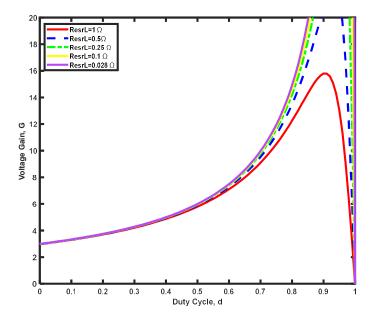

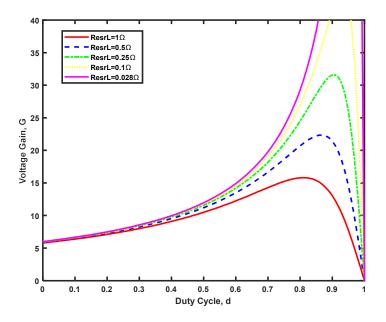

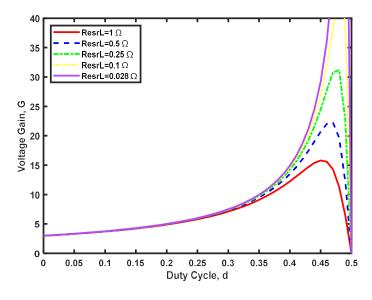

| Figure 3.7: Voltage gain characteristic of the MBC as a function of duty cycle for different values of <i>RESR</i> , <i>L</i>                                                       | 52   |

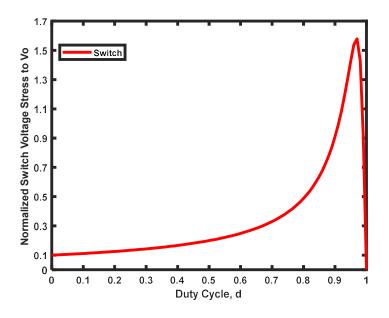

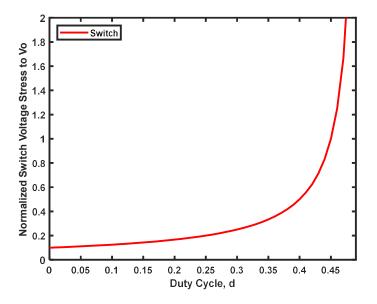

| Figure 3.8: Normalized voltage stress of MBC versus d.                                                                                                                              | 53   |

| Figure 3.9: Voltage ripple waveforms for all five capacitors in MBC with output voltage and switch voltage                                                                          | 60   |

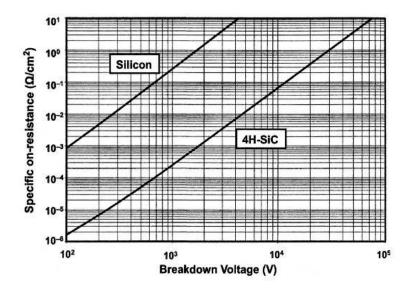

| Figure 3.10: Specific on-resistance for 4H-SiC and Silicon in power devices [15]                                                                                                    | 62   |

| Figure 3.11: Three-level MBC experimental prototype                                                                                                                                 | 63   |

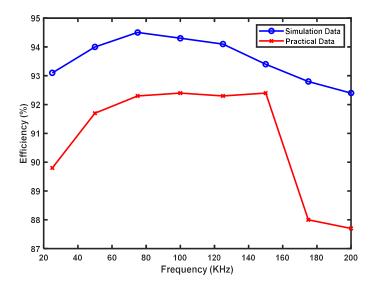

| Figure 3.12: Simulation and practical efficiency with respect to the switching frequency of the three-level MBC.                                                                    | 65   |

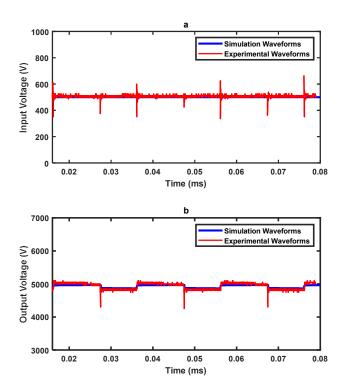

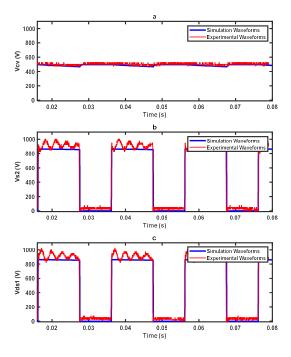

| Figure 3.13: Input and output voltage waveforms of the three-level MBC                                                                                                              | 66   |

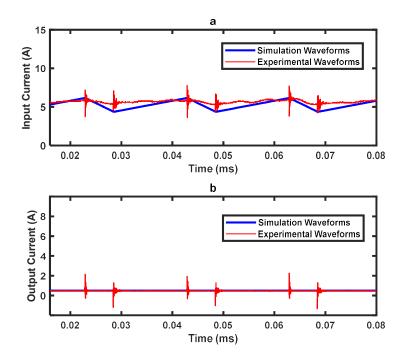

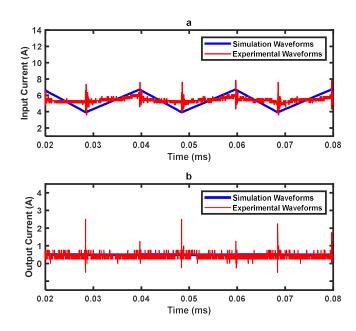

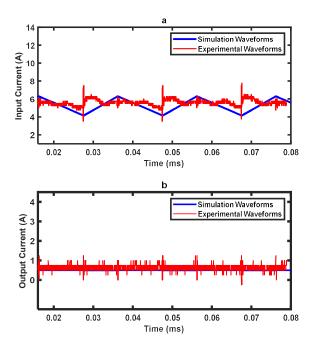

| Figure 3.14: Input and output current waveforms of the three-level MBC                                                                                                              | 67   |

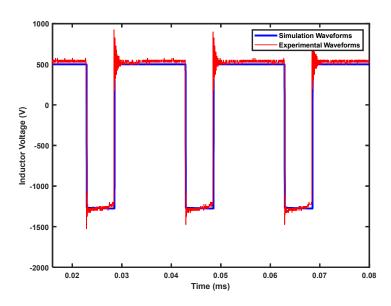

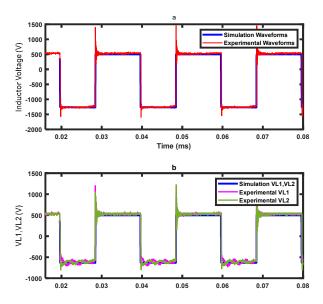

| Figure 3.15: Voltage waveform across the inductor of the three-level MBC                                                                                                            | 68   |

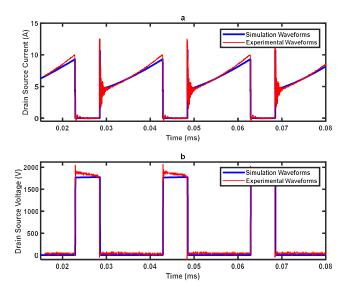

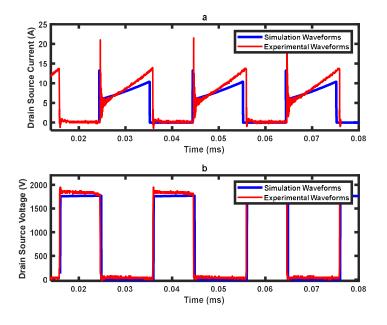

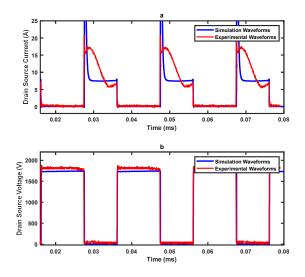

| Figure 3.16: Drain-source voltage and current across the switch of the three-level MBC.                                                                                             | 69   |

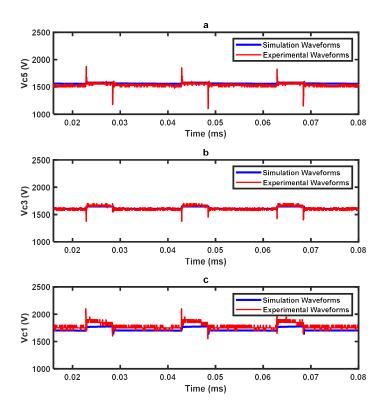

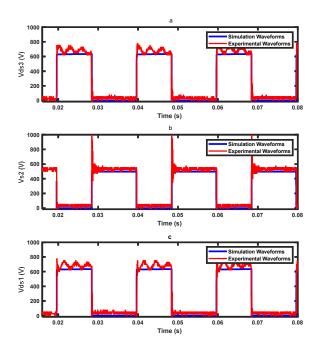

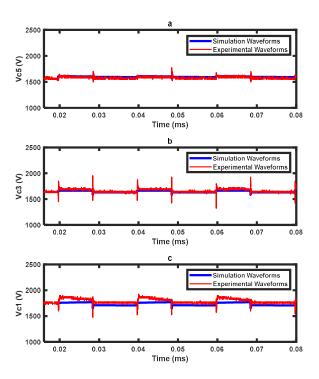

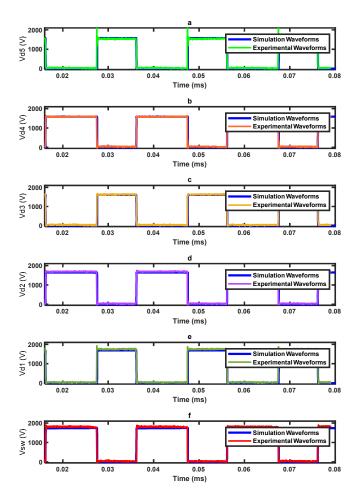

| Figure 3.17: Voltage across the output capacitors <i>C</i> 1, <i>C</i> 3 and <i>C</i> 5 of the three-level MBC.                                                                     | 70   |

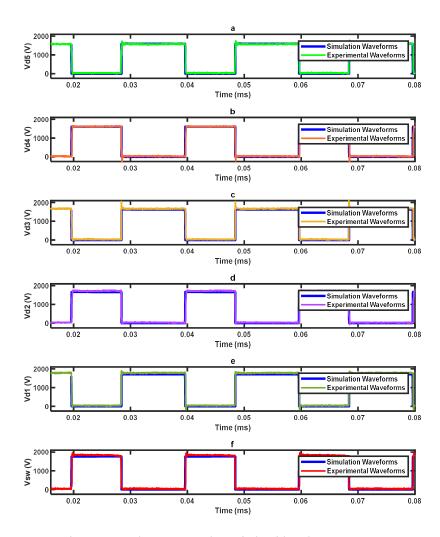

| Figure 3.18: Drain-source voltage across the switch with voltage across <i>D</i> 1, <i>D</i> 2, <i>D</i> 3, <i>D</i> 4, <i>D</i> 5 of the three-level MBC                           | 71   |

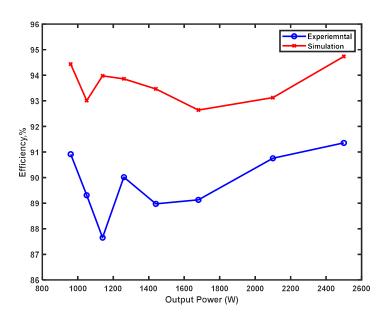

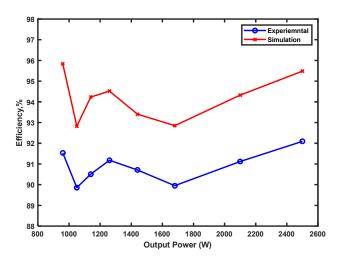

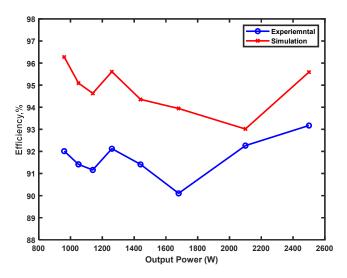

| Figure 3.19: Simulation and practical efficiency with respect to the output power of the three-level MBC.                                                                           | 74   |

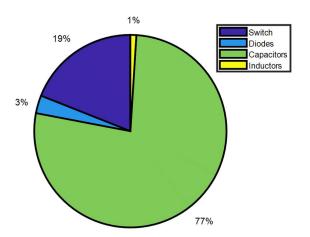

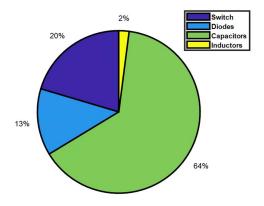

| Figure 3.20: Percentage distribution of losses of the three-level MBC                                                                                                               | 75   |

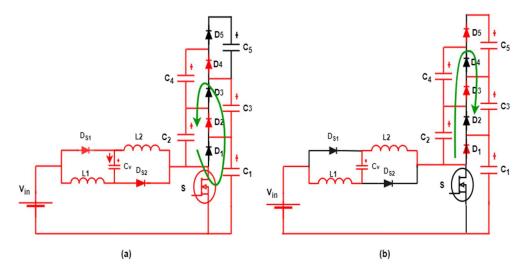

| Figure 4.1: Circuit diagram of the three-level high gain DC-DC SIMBC                                                                                                                | 80   |

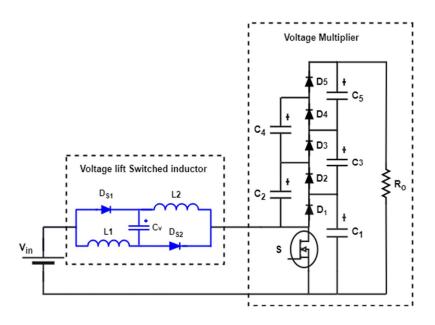

| Figure 4.2: Circuit diagram of the three-level high gain DC-DC VLSIMBC                                                                                                              | 81   |

| Figure 4.3: Main steady state waveforms of gate voltage, inductor voltage and current, input and output diodes voltages, output capacitors voltages and switch voltage for SIMBC    | 82   |

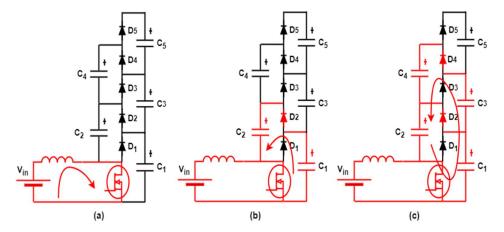

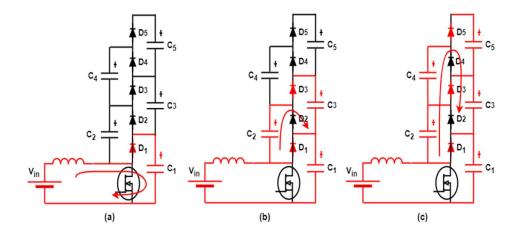

| Figure 4.4: Operation modes of the three-level SIMBC (a) Mode 1, (b) Mode 2                                                                                                         | 2 83 |

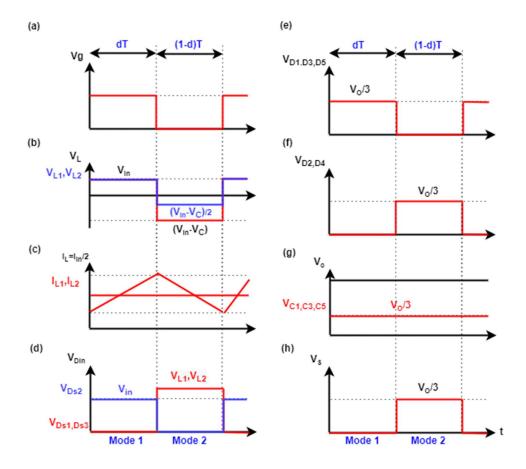

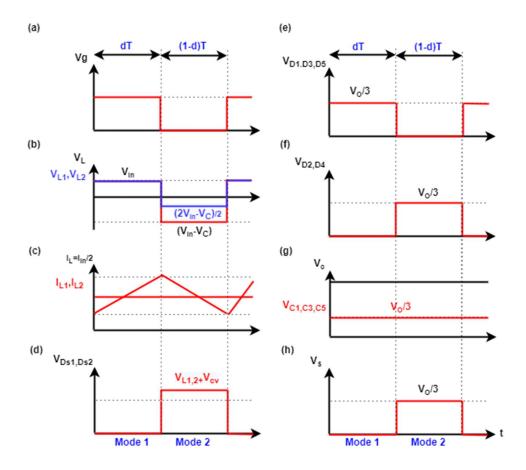

| Figure 4.5: Main steady-state waveforms of gate voltage, inductor voltage and current, input and output diodes voltages, output capacitors voltages and switch voltage for VLSIMBC. | 84   |

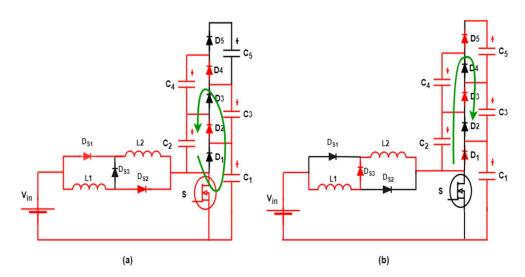

| Figure 4.6: Operation modes of the three-level VLSIMBC (a) Mode 1, (b)  Mode 2.                                                                                                     | 85   |

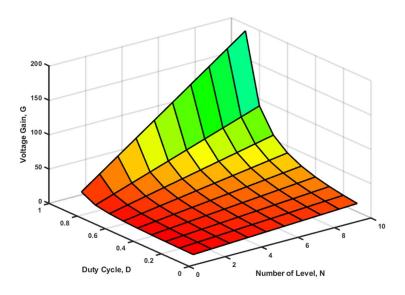

| Figure 4.7: Ideal Voltage gain characteristic of the SIMBC as a function of <i>d</i> and <i>N</i> values.                                                                           | 87   |

| Figure 4.8: Voltage gain characteristic of the SIMBC versus duty cycle for different values of <i>RESR</i> , <i>L</i>                                         | 89    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

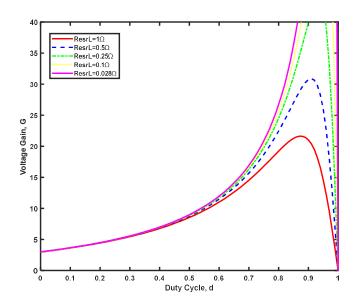

| Figure 4.9: Ideal Voltage gain characteristic of the VLSIMBC as a function of <i>d</i> and <i>N</i> values.                                                   | 90    |

| Figure 4.10: Voltage gain characteristic of the VLSIMBC versus <i>d</i> for different values of <i>RESR</i> , <i>L</i> .                                      | 92    |

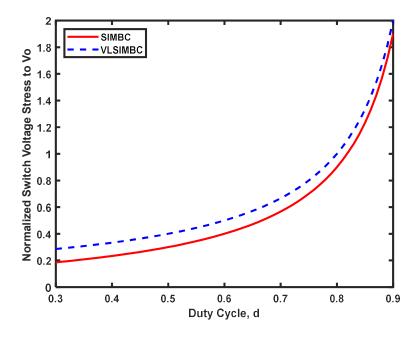

| Figure 4.11: Normalized voltage stress of SIMBC and VLSIMBC versus d                                                                                          | 93    |

| Figure 4.12: Three-level SIMBC experimental prototype.                                                                                                        | 95    |

| Figure 4.13: Three-level VLSIMBC experimental prototype                                                                                                       | 96    |

| Figure 4.14: Input and output voltage waveforms of the three-level SIMBC                                                                                      | 98    |

| Figure 4.15: Input and output current waveforms of the three-level SIMBC                                                                                      | 99    |

| Figure 4.16: Voltage across $L1$ , $L2$ and the effective inductor $L$ for the SIMBC                                                                          | . 100 |

| Figure 4.17: Voltage across <i>Ds</i> 1, <i>Ds</i> 2 and <i>Ds</i> 3 for the three-level SIMBC                                                                | . 100 |

| Figure 4.18: Drain-source voltage and current across the switch of the three-level SIMBC.                                                                     | . 101 |

| Figure 4.19: Voltage across the output capacitors <i>C</i> 1, <i>C</i> 3 and <i>C</i> 5 of the three-level SIMBC.                                             | . 102 |

| Figure 4.20: Drain-source voltage across the switch with voltage across <i>D</i> 1, <i>D</i> 2, <i>D</i> 3, <i>D</i> 4, <i>D</i> 5 of the three-level SIMBC   | . 103 |

| Figure 4.21: Input and output voltage waveforms of the three-level VLSIMBC                                                                                    | . 104 |

| Figure 4.22: Input and output current waveforms of the three-level VLSIMBC                                                                                    | . 105 |

| Figure 4.23: Voltage across <i>L</i> 1, <i>L</i> 2 and the effective inductor <i>L</i> for the VLSIMBC                                                        | . 106 |

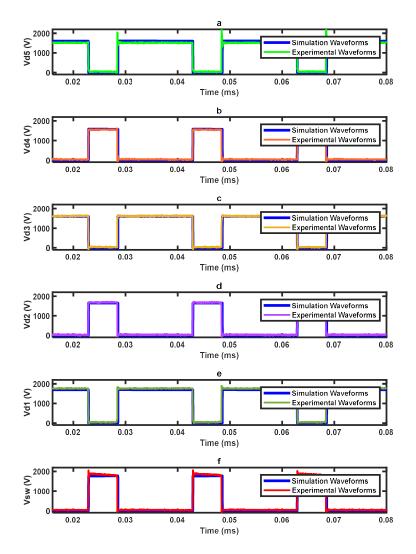

| Figure 4.24: Voltage across <i>Ds</i> 1, <i>Ds</i> 2 and <i>Vcv</i> for the three-level VLSIMBC                                                               | . 107 |

| Figure 4.25: Drain-source voltage and current across the switch of the three-level VLSIMBC.                                                                   | . 107 |

| Figure 4.26: Voltage across the output capacitors <i>C</i> 1, <i>C</i> 3 and <i>C</i> 5 of the three-level VLSIMBC.                                           | . 108 |

| Figure 4.27: Drain-source voltage across the switch with voltage across <i>D</i> 1, <i>D</i> 2, <i>D</i> 3, <i>D</i> 4, <i>D</i> 5 of the three-level VLSIMBC | . 109 |

| Figure 4.28: Simulation and practical efficiency with respect to the output power of the three-level SIMBC                                                    | . 113 |

| Figure 4.29: Simulation and practical efficiency with respect to the output power of the three-level VLSIMBC.                                                 | . 114 |

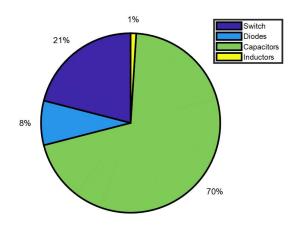

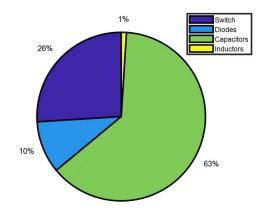

| Figure 4.30: Percentage distribution of losses of the three-level SIMBC                                                                                       | . 115 |

| Figure 4.31: Percentage distribution of losses of the three-level VLSIMBC                                                                                     | . 115 |

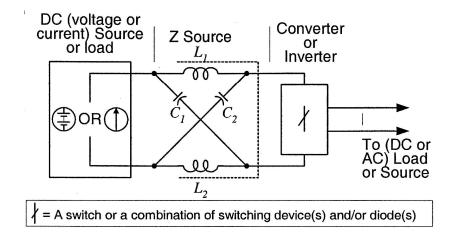

| Figure 5.1: Z-source converter structure [28].                                                                                                                | . 118 |

| Figure 5.2: Conventional Z-source DC-DC converter [29].                                                                                                       | . 118 |

| Figure 5.3: Circuit diagram of the three-level high gain DC-DC ZSMBC                                                                                          | . 120 |

| Figure 5.4: Main steady state waveforms of gate voltage, inductor voltage and current, input and output diodes voltages, output capacitors voltages and switch voltage for ZSMBC. | 122 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.5: Operating modes of the three-level ZSMBC (a) S ON, (b) S OFF                                                                                                          | 123 |

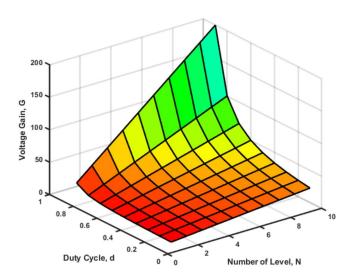

| Figure 5.6: Ideal Voltage gain characteristic of the ZSMBC as a function of d and N values.                                                                                       | 126 |

| Figure 5.7: Voltage gain characteristic of the ZSMBC as a function of <i>d</i> for different values of <i>RESR</i> , <i>L</i>                                                     | 127 |

| Figure 5.8: Normalized voltage stress of ZSMBC as a function of d                                                                                                                 | 129 |

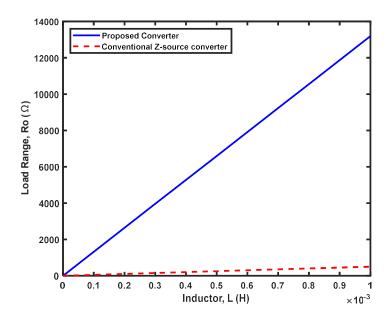

| Figure 5.9: CCM load range for the proposed converter and conventional Z-source DC-DC converter.                                                                                  | 133 |

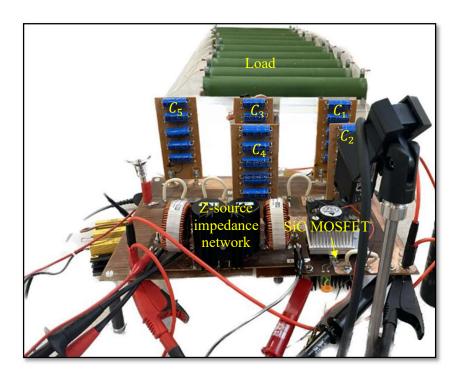

| Figure 5.10: Three-level ZSMBC experimental prototype.                                                                                                                            | 134 |

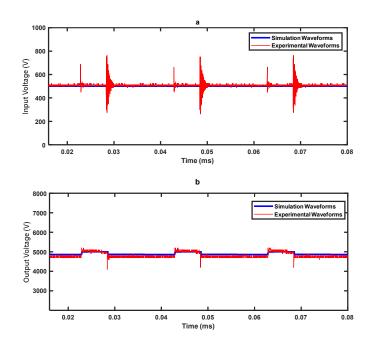

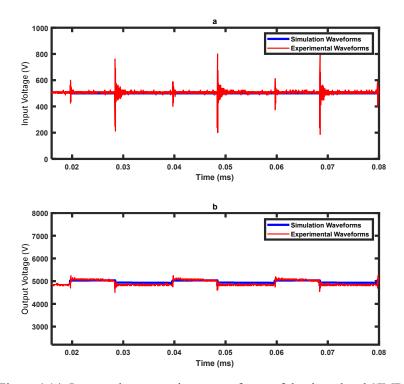

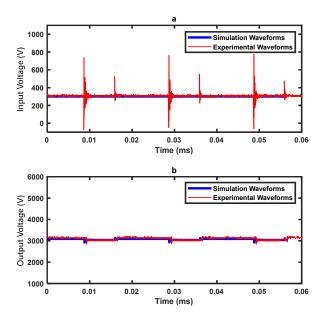

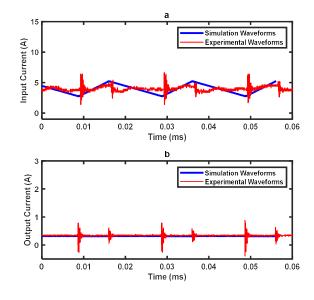

| Figure 5.11: Input and output voltage waveforms of the three-level ZSMBC                                                                                                          | 137 |

| Figure 5.12: Input and output current waveforms of the three-level ZSMBC                                                                                                          | 137 |

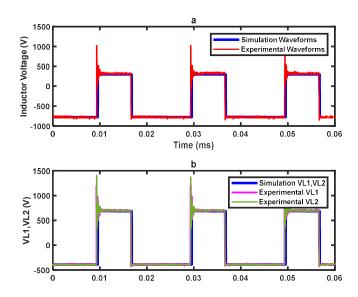

| Figure 5.13: Voltage across <i>L</i> 1, <i>L</i> 2 and the effective inductor <i>L</i> for the ZSMBC.                                                                             | 138 |

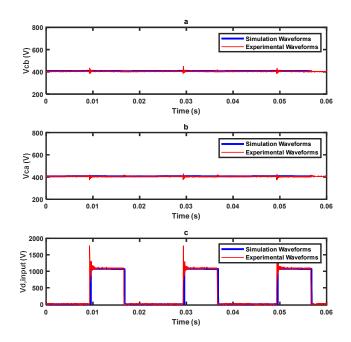

| Figure 5.14: Voltage across <i>DS</i> , <i>VCa</i> and <i>VCb</i> for the ZSMBC                                                                                                   | 139 |

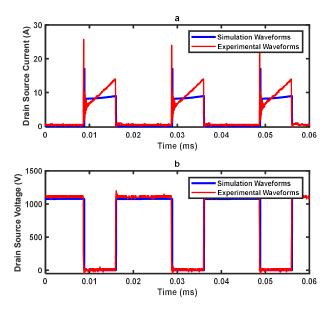

| Figure 5.15: Drain-source voltage and current across the switch of the ZSMBC.                                                                                                     | 140 |

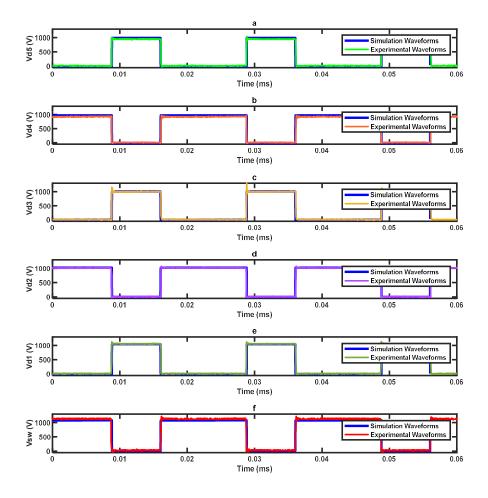

| Figure 5.16: Voltage across the output capacitors <i>C</i> 1, <i>C</i> 3 and <i>C</i> 5 of the ZSMBC.                                                                             | 141 |

| Figure 5.17: Drain-source voltage across the switch with voltage across <i>D</i> 1, <i>D</i> 2, <i>D</i> 3, <i>D</i> 4, <i>D</i> 5 of the ZSMBC.                                  | 142 |

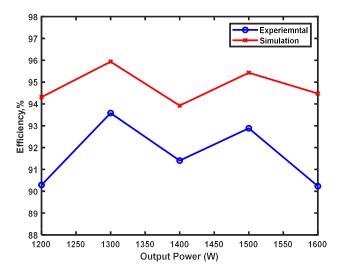

| Figure 5.18: Simulation and practical efficiency with respect to the output power of the three-level ZSMBC                                                                        | 146 |

| Figure 5.19: Percentage distribution of losses of the three-level ZSMBC                                                                                                           | 146 |

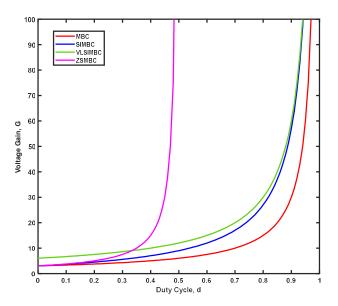

| Figure 6.1: Voltage gains against the duty cycle for the proposed converters                                                                                                      | 150 |

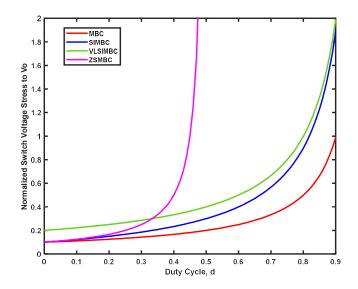

| Figure 6.2: Normalized voltage stress of the high gain topologies                                                                                                                 | 151 |

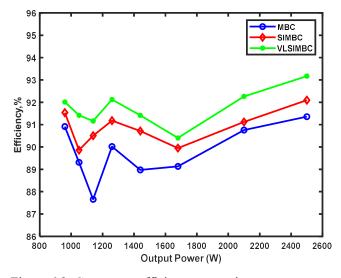

| Figure 6.3: Converters efficiency at varying output powers                                                                                                                        | 151 |

## **List of Tables**

| Table 3-1. Design Specification for Three-Level MBC               | 64  |

|-------------------------------------------------------------------|-----|

| Table 4-1. Design Specification for Three-Level SIMBC and VLSIMBC | 96  |

| Table 5-1. Design Specification for Three-Level ZSMBC             | 135 |

| Table 6-1. Comparison of the Three-Level MBC, SIMBC, VLSIMBC and  |     |

| ZSMBC Topologies                                                  | 149 |

## List of Abbreviations

RESs Renewable Energy Sources

WEC Wave Energy Converter

MVDC Medium Voltage Direct Current

$R_{DS,(ON)}$  Drain-Source Resistance On-State

CO<sub>2</sub> Carbon Dioxide

DPG Distributed Power Generation

ESS Energy Storage Systems

AC Alternating Current

SST Solid State Transformer

HFT High Frequency Transformers

MBC Multilevel Boost Converter

SIMBC Switched Inductor Multilevel Boost Converter

VLSIMBC Voltage Lift Switched Inductor Multilevel Boost Converter

ZSMBC Z-Source Multilevel Boost Converter

VM Voltage Multiplier

CBC Conventional Boost Converter

MOSFET Metal-oxide-semiconductor Field-effect-transistor

IGBT Insulated-Gate Bipolar Transistors

PWM Pulse Width Modulation

EMI Electromagnetic Interference

PV Photovoltaic

CCM Continuous Conduction Mode

DCM Discontinuous Conduction Mode

VMR Voltage Multiplier Rectifier

$R_{ESR,L}$  Equivalent Series Resistance of the Inductor

ESR Equivalent Series Resistance

SiC Silicon-Carbide

Si Silicon

RMS Root Mean Square

ZSI Z-Source Inverter

## **Publications**

- [1] A. Alsafrani, M. Parker, M. Shahbazi, and A. Horsfall, "High Gain DC-DC Multilevel Boost Converter to Enable Transformerless Grid Connection for Renewable Energy," in 2021 56th International Universities Power Engineering Conference (UPEC), 2021: IEEE, pp. 1-6.

- [2] A. Alsafrani, M. Shahbazi, and A. Horsfall, "High gain DC-DC voltage lift switched-inductor multilevel boost converter for supporting grid connection of wave energy conversion," in 11th International Conference on Power Electronics, Machines and Drives (PEMD), 2022: IEEE, pp. 1-5.

- [3] A. Alsafrani, M. Shahbazi, and A. Horsfall, "High gain DC-DC switched inductor multilevel boost converter to enable transformer less grid connection for wave energy," in 19th International Conference on AC and DC Power Transmission (ACDC 2023), 2023: IET p. 102 107.

- [4] A. Alsafrani, D. Blackhorse-Hull, N. Sarma, M. Shahbazi, and A. Horsfall, "Analysis of Transformerless, Single Switch, High Gain DC–DC Converters for Grid Connection of Wave Energy," has been submitted to IEEE Access Journal.

- [5] D. Blackhorse-Hull, A. Alsafrani, N. Sarma, and A. Horsfall, "Multi-Level Dual Polarity DC-DC Converter," To submitted to IEEE Transactions on Power Systems.

- [6] A. Alsafrani, M. Shahbazi, and A. Horsfall, "A Novel High Gain Z-source Multilevel Boost Converter Analysis and Design," To be submitted to Journal of Modern Power Systems and Clean Energy.

#### 1.1 BACKGROUND AND MOTIVATION

Non-renewable energy sources have been experiencing significant challenges. Global warming, rising oil prices, and the growing energy crisis are the most compelling reasons to choose more sustainable sources and environmentally friendly electric power generation options. Thus, the primary focus in electrical supply revolves around the providing clean, cheap, and sustainable power supply to consumers via the distribution grid. The advantages of renewable energy generation include increased reliability, improved power quality, reduced power loss, and the integration of renewable energy sources (RESs) [1].

Renewable energy sources have been widely adopted as an alternative to conventional energy generations [2]. RESs include wave energy, wind, solar, tidal, and geothermal. Wave energy is considered one of the most promising, exploitable renewable energy sources due to its abundant potential and pollution-free nature. Compared to other renewable energy sources, the arrival pattern of waves is relatively predictable, and waves have a high power density due to the density of water [3]. Wave energy converters can also be located far enough away from the coast so that they are not visible [4]. Therefore, wave energy conversion technology has been increasingly utilised to convert wave power into electric power. However, since wave energy has a low-capacity factor, electrical power systems that can produce a stable DC output over a wide variety of input voltages are required. To solve this concern, power take-off systems with high voltage gain DC-DC converters are needed to boost the rectified output voltage from the wave energy converter (WEC). This would also allow a wave energy installation to use a medium voltage direct current (MVDC) collection network

for many WECs without the requirement for complex synchronisation. The voltage levels produced by wave energy converters are relatively low and must be stepped up considerably to enable DC grid integration, necessitating high voltage gain DC-DC boost converters.

Various DC-DC converter topologies have been discussed in the literature to offer high voltage gain. These topologies involve isolated and non-isolated converters. By adjusting the transformer's turn ratio, isolated converters can realise a high voltage gain [5]. Furthermore, isolated topologies that employ a high-frequency transformer can provide isolation between input and output terminals [5, 6]. However, the main drawback of the isolated DC-DC converters is that the transformer leakage inductance causes power transformer losses and stray inductance originating from the circuit's layout; thus, these isolated converters are not appropriate for obtaining high conversion ratios. Besides, the size and weight of these converters make it challenging to include them in a wave energy converter [6]. High voltage gain with increased efficiency can be achieved without a transformer in non-isolated topologies [7-15]. There are two broad classes of non-isolated step-up DC-DC converters: coupledinductor-based [7-9] and non-coupled-inductor-based types such cascade boost, switched-capacitor and switched-inductor [10-15]. Coupled-inductor topologies improve efficiency and minimise voltage stress on the inductors, significantly increasing voltage gain. However, the linked inductor leakage issue creates a significant voltage spike on semiconductor components, and the circuits are challenging to design [7]. The dual-switch-based converters present high voltage conversion ratios with high input current ripple [11, 14]. Data published in the literature suggests that cascaded two-stage boost converters can achieve a high voltage gain [13]. In this converter, the switch experiences voltage stresses equal to the output

voltage, requiring a higher rated switch. Moreover, a switched-inductor structure has been proposed, which operates by charging two inductors in parallel and discharging them in series, increasing the voltage gain [14].

This thesis focuses on the design of high-gain DC-DC converters that demonstrate enhanced voltage gain, increased efficiency, and reduced voltage stresses across the active devices that are suitable for the integration of renewable energy, particularly wave energy, to the distribution grid in the UK via an MVDC collection network. Transferring energy from a wide range of input voltages requires a voltage gain that is significantly greater than what may be achieved with conventional boost converters, in particular, ten times or higher. Duty cycle operation is crucial in high step-up DC-DC converters since high duty cycle operation leads to limitations. The main drawback of operating converters with an extreme (>80%) duty cycle is the high voltage stress across the power devices, where the converters output voltage is equal to the power devices voltage of the conventional step-up converters. This results in the need for high rated devices. Power device rating is another concern associated with the performance of high step-up converters. For power MOSFETs, as the power rating rises, the on-state drain- source resistance  $(R_{ds,on})$  likewise increases, causing conduction losses that further impair the efficiency. Therefore, there is substantial motivation to improve the performance of high-gain step-up DC-DC converters by reducing the voltage stress across the power devices so that switching loss can be significantly decreased.

### 1.2 POWER SYSTEM DISTRIBUTION

Classical electrical power systems have a vertical configuration that includes generation, transmission, and distribution [16]. Following the present arrangement,

power must be transferred from the transmission and distribution networks to the consumer. As a consequence of these transmission losses, efficiency degrades. In addition, thermal power plants' carbon dioxide (CO<sub>2</sub>) emissions from consuming carbon-based fuels contribute to global warming. Hence, minimising generating power from conventional thermal power plants and increasing the penetration of distributed power generation (DPG) systems is one of the primary objectives in reducing global warming.

DPG systems are essential for future power grids because they generate energy and transmit it to numerous locations. Furthermore, DPGs can be used alongside renewable energy sources like solar energy, wave energy and wind power, as well as batteries and fuel cells to control, monitor, enhance power quality, find and isolate faults, and stabilise the grid [17]. DPG utilises microgrids that involve power networks and incorporate DPG systems and loads of varying types. Microgrids can function both independently and in conjunction with the larger power grid. Also, when properly controlled and operated, microgrids can improve the stability and quality of the power distribution system [16, 18].

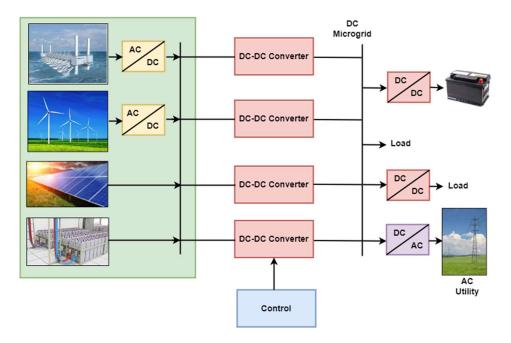

Furthermore, the DPG system is an essential element of a microgrids, and various arrangements enable microgrids to function either independently or connected to the grid. The block diagram of the power system distribution is shown in Figure 1.1. It can be noticed from this figure that before the generated power can be connected to the utility grid or fed to DC consumer loads, it must be converted and regulated by certain power electronics converters [19, 20]. Utilising the locally generated power to fulfil the demands of the loads necessitates using DC-DC converters that operate at different power levels.

Figure 1.1: Power system distribution.

In addition, DC microgrid systems have gained significant interest in the current era enabling implementation with technologies including RESs, energy storage systems (ESS), electric vehicle charging, and residential applications. Therefore, DC distribution systems have recently gained increasing interest from developers owing to their benefits which are highlighted as follows.

- Environmental groups increasingly demand limiting CO<sub>2</sub> and other harmful emissions during power generation. Incorporating RESs on a substantial scale and enhancing the performance of power generation and transmission may contribute to accomplishing this goal. Hence, a DC grid system could be an effective approach to verify such feasibility [21].

- In the event of grid disturbances, the DC microgrid system maintains stability, reliability, control flexibility and power quality [22].

- Since RESs synchronisation with the grid system and reactive power control are unnecessary, the system's complexity can be minimised [22].

Chapter 1: Introduction

5

• In a DC grid system, the skin effect phenomena does not occur, enabling current to flow through the entire cable, unlike in AC grid system. Employing a smaller-gauge cable for the same amount of current enhances transmission efficiency and reduces the cost of transmission and distribution [23].

In consideration of these merits, the DC microgrid system has the potential to replace the traditional transmission system gradually. Moving to MVDC for many applications is a useful ideal, especially when considering distribution level. However, interfacing some sort of connected devices and generators to MVDC needs high gain step-up converters, which is a challenge that is discussed in this thesis. Examples are grid connected wave energy generation units that have a lot of potential and are discussed in the following.

#### 1.3 HIGH STEP-UP DC-DC CONVERTER APPLICATIONS

## 1.3.1 Grid Connected Wave Energy Converter

Wave energy is an emerging technology that has the potential to provide a clean and sustainable source for the generation of renewable energy. The conversion of motion wave energy to electricity is considered one of the most environmentally friendly approaches to generating electricity, as it produces zero waste that must be kept or impacts the ecosystem [1]. It has the potential to fulfil up to 20% of the current UK electricity demand [24]. Compared to other renewable energy sources, the wave resource is highly predictable and possesses a significantly higher power density in comparison to wind [1, 3]. Additionally, it is one of the most affordable renewable energy sources due to its high-power density [1]. Wave energy systems can also be located offshore, hidden from public view [1, 4]. For wave energy to be viable, multiple spatially distributed converters need to be integrated into a power collection

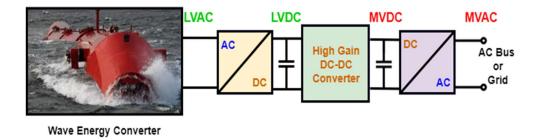

network. The temporal variation of the energy that can be collected in such a network gives rise to challenges in synchronising and balancing a conventional AC system. DC collection networks can be utilised in place of these conventional AC systems, eliminating the need to synchronise different generation frequencies. For this to be feasible, the integration of a MVDC transmission system for multiple WECs offers significant advantages [25, 26]. The intermittent nature of the ocean waves results in irregular power produced by the wave energy converters (WECs). Accordingly, WECs have significant challenges in integrating with the grid. For instance, to efficiently convert continuous wave motion into electrical energy, the challenge of harnessing wave power generated at low speeds yet with significant force is challenging. This strong motion has no single direction and differs from the conventional operation of electric generators, which operate optimally with high speeds and require constant input [3]. The recently suggested undersea storage system can overcome this obstacle by smoothing the WEC output power oscillations [26]. However, wave energy has a low-capacity factor, necessitating the use of electrical power systems to produce a stable DC output to the collection network over a wide range of input voltages. Power take-off systems that may boost the rectified output voltage from a WEC and feed a grid-connected inverter with high conversion ratio DC-DC converters are required to enable this, as shown in Figure 1.2.

Figure 1.2: Schematic representation of a Wave Energy Converter (WEC) and Power Take Off (PTO) system.

Chapter 1: Introduction

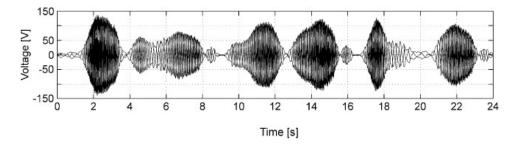

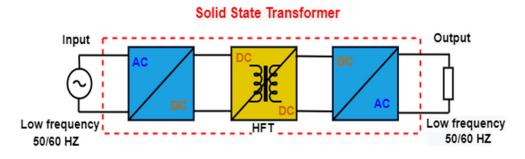

7