The copyright of this thesis rests with the author. No quotation from it should be published without his prior written consent and information derived from it should be acknowledged.

## The Characterisation of CdTe-based Epitaxial Solar Cell structures fabricated by MOVPE

by

Michelle. Y. Simmons

A thesis submitted for the degree of Doctor of Philosophy

Department of Physics The University of Durham

June 1992

This thesis is dedicated to my Mum and Dad, whom I love dearly.

.

.

## Declaration

I declare that the work submitted in this thesis, unless otherwise stated, was carried out by the candidate, that it has not previously been submitted for any degree and that it is not currently being submitted for any other degree.

Q. W. S. Kung

Dr. A. W. Brinkman Supervisor

Mysummons

• • • • • • • • • • • • • • • •

M. Y. Simmons Candidate

• • •

Copyright © 1992 by Michelle Simmons

The copyright of this thesis rests with the author. No quotation from it should be published without Michelle Simmons's prior written consent and information derived from it should be acknowledged.

#### Abstract

This work has principally been concerned with the fabrication and characterisation of a number of CdTe-based p-n and p-i-n solar cells by MOVPE, namely: (i) the n-CdS/p-CdTe cell on  $\{0001\}$ CdS, (ii) the n-CdTe/p-ZnTe cell on  $\{100\}$ CdTe, (iii) the p-ZnTe/i-CdTe/n-CdS cell on  $\{0001\}$ CdS and (iv) the p-ZnTe/i-CdTe/n-GaAs cell on  $\{100\}$ GaAs.

The effects of substrate polishing on the quality of the epitaxial CdTe layers were investigated, and for CdS, a CrO<sub>3</sub>/HNO<sub>3</sub>/H<sub>2</sub>O polish was found to give the best surfaces for epitaxy. Doping studies proved ammonia gas unsuitable for the production of high conductivity p-type ZnTe and CdTe, but epilayers with conductivities of 10  $\Omega$ cm and 0.5  $\Omega$ cm respectively were obtained, however, using elemental arsenic heated to 250°C. Thin films of CdTe were then deposited by MOVPE at 325°C onto the opposite polar faces of {0001} and {0116} oriented CdS single crystal substrates, the best morphologies being obtained on the non-metal or B faces of these planes. RHEED confirmed that the {111}<sub>CdTe</sub>||{0001}<sub>CdS</sub> and {375}<sub>CdTe</sub>||{0116}<sub>CdS</sub> epitaxial relationships were established whilst XTEM comfirmed that CdTe grown on both these planes contained a high density of lamellar twins lying parallel to the epilayer/substrate interface. Epitaxial n-CdS/p-CdTe cells were prepared on both (0001)A and (0001)B faces of CdS, where higher efficiencies were consistently found for A face devices despite better morphologies on B face devices, reasons for this remaining unclear.

Epitaxial ZnTe/CdTe/CdS and ZnTe/CdTe/GaAs p-i-n diode solar cells were also investigated, both devices giving similar conversion efficiencies. Analysis of current transport characteristics indicated that the current transport in the GaAsbased devices was dominated by a multistep tunneling process at all temperatures, whilst this mechanism was only important in the CdS-based devices at temperatures <250 K. Preliminary investigations into the growth of ZnTe/CdTe/ CdTe p-i-n cells on  $\{\bar{1}\bar{1}\bar{1}\}$ CdTe substrates and the growth of Cd<sub>1-x</sub>Zn<sub>x</sub>Te alloys, for use in graded absorber layer structures are also presented.

#### Acknowledgements

Initially, and with sadness, I would like to thank the late Graham Russell for encouraging me to stay on at Durham. His enthusiasm for the subject was infectious and despite his loss I believe that this remains within all those he knew. I am very grateful to Andy Brinkman for taking me on with an already heavy workload and for being there throughout. Thanks also to Ken Durose for providing necessary support at some of the most difficult stages of the work and to Professor Woods for reading my thesis at such short notice.

I feel lucky to have worked with such an excellent group ..... thanks to Paul Clifton for teaching me the intricacies of MOVPE, Paul Brown for his invaluable help with TEM analysis and to James, Abdullah and Murat for providing moral support and making me laugh!! I wish them all the best. A special thanks to Haider whom I respect for his ability to try anything and everything-the mark of a true scientist.

Technical support within the department has been excellent thanks to Davy, John, Colin, Julie, Kay, Pauline and Sharon. I would especially like to thank Norman and Frank, who were not only good at their jobs but made me feel at home in Durham. Collaborative work with other groups has also been invaluable and I would like to thank Professor Tanner and John Hudson for helping with DCXRD measurements and Mrs.O.D. Dosser from RSRE for calibrated EDAX measurements. Thanks also to Peter Simmons (my Dad) for help printing the photographs ... its a day I'll never forget.

On a personal note I would like to take this opportunity to thank my friends: Arv. Barv, Alex, Pete and Jen, Alastair, Tony, Norman, J.A.K, Anth, John and Noreen, Harvey and Sonia; and my family (who have been superb), thanks to my brother, Gary and my Mum and Dad for their support and encouragement.

Finally an extra special thanks to Dan for help with the graphics and for going where no man has gone before ?!

# Contents

|   | Abstr  | act                                                |

|---|--------|----------------------------------------------------|

|   | Ackno  | wledgements                                        |

| 1 | Introd | luction                                            |

|   | 1.1    | Solar Cell Devices                                 |

|   | 1.2    | Solar Cell Applications                            |

|   | 1.3    | CdTe Solar Cells                                   |

|   | 1.4    | The present study 23                               |

|   | 1.5    | References                                         |

| 2 | Solar  | cell and heterojunction theory                     |

|   | 2.1    | The solar cell                                     |

|   | 2.1.1  | The junction                                       |

|   | 2.1.2  | The solar spectrum                                 |

|   | 2.1.3  | Solar cell device parameters 32                    |

|   | 2.1.4  | Defects in epitaxial solar cells                   |

|   | 2.2    | Solar cell technologies                            |

|   | 2.2.1  | Solar cell structures                              |

|   | 2.2.2  | Fabrication technologies 40                        |

|   | 2.3    | CdTe-based solar cells 41                          |

|   | 2.3.1  | Introduction                                       |

|   | 2.3.2  | The n-CdS/p-CdTe solar cell 43                     |

|   | 2.3.3  | The n-CdTe/p-ZnTe solar cell                       |

|   | 2.3.4  | P-I-N solar cells based on CdTe as the absorber 45 |

|   | 2.4    | Heterojunction Theory 47                           |

|   | 2.4.1  | Introduction                                       |

|   | 2.4.2  | Formation of energy band diagrams 47               |

|   | 2.4.3  | Current-transport mechanisms 49                    |

|   | 2.4.4  | Junction capacitance                               |

|   | 2.4.5  | Spectral response                                  |

|   | 2.4.6  | Ohmic contacts                                     |

|   | 2.5    | References                                         |

| 3 | Chara | cterisation of device structures                       |

|---|-------|--------------------------------------------------------|

|   | 3.1   | Introduction                                           |

|   | 3.2   | Structural Assessment                                  |

|   | 3.2.1 | Reflection high energy electron diffraction (RHEED) 66 |

|   | 3.2.2 | Laue X-ray back reflection                             |

|   | 3.2.3 | X-ray diffractometry                                   |

|   | 3.2.4 | Double crystal x-ray diffraction                       |

|   | 3.2.5 | Scanning electron microscopy (SEM)                     |

|   | 3.2.6 | Transmission electron microscopy                       |

|   | 3.2.7 | Photoluminescence                                      |

|   | 3.3   | Electrical Assessment                                  |

|   | 3.3.1 | I-V characterisation                                   |

|   | 3.3.2 | Capacitance-voltage measurements                       |

|   | 3.3.3 | Spectral Response                                      |

|   | 3.3.4 | Hall effect and resistivity measurements               |

|   | 3.4   | References                                             |

|   |       |                                                        |

| 4 | Prepa | ration of substrates for epitaxy                       |

|   | 4.1   | Introduction                                           |

|   | 4.2   | Review of the CdS substrate preparation                |

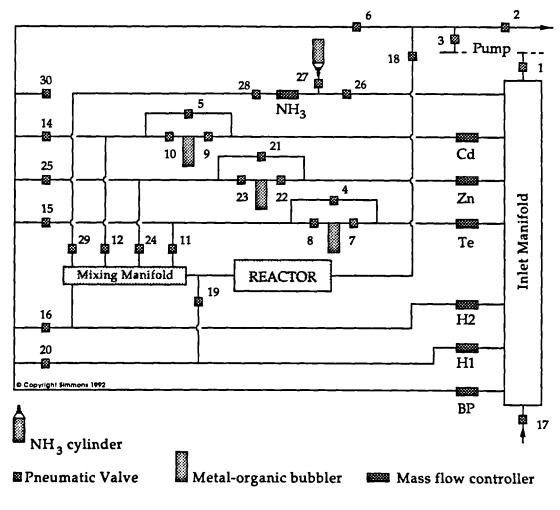

|   | 4.3   | Mechanical polishing of Cadmium Sulphide               |

|   | 4.3.1 | Experimental                                           |

|   | 4.3.2 | Results                                                |

|   | 4.4   | Chemical polishing of CdS                              |

|   | 4.4.1 | Experimental                                           |

|   | 4.4.2 | Results                                                |

|   | 4.5   | GaAs substrate preparation                             |

|   | 4.5.1 | Review of the chemical polishing of GaAs               |

|   | 4.5.2 | Experimental 100                                       |

|   | 4.6   | Preparation of CdTe substrates 100                     |

|   | 4.6.1 | Review of the polishing of CdTe 100                    |

|   | 4.6.2 | Experimental 102                                       |

|   | 4.7   | Heat cleaning of substrates                            |

|   |       | -                                                      |

| 5 | Grow  | th of epitaxial layers by MOVPE                                                  | 107 |

|---|-------|----------------------------------------------------------------------------------|-----|

|   | 5.1   | Introduction                                                                     | 107 |

|   | 5.2   | Principles of MOVPE                                                              | 109 |

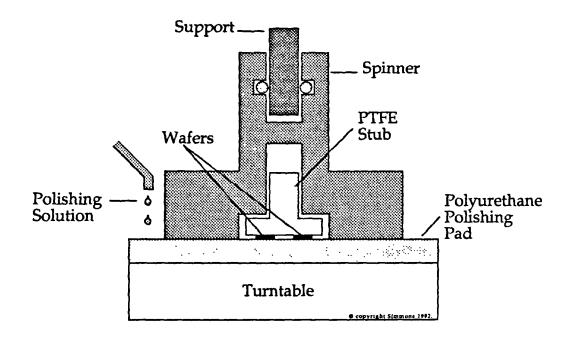

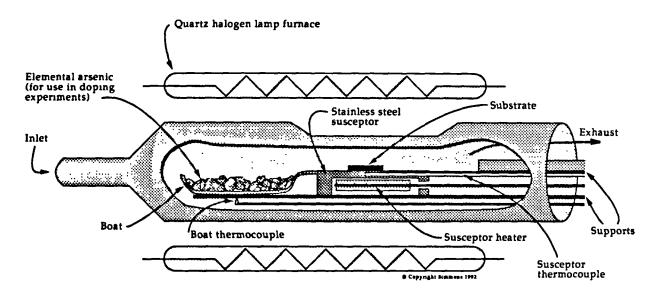

|   | 5.3   | The MOVPE growth system                                                          | 112 |

|   | 5.4   | CdTe layers on {100}GaAs substrates                                              | 115 |

|   | 5.4.1 | Introduction                                                                     | 115 |

|   | 5.4.2 | Growth Conditions                                                                | 117 |

|   | 5.4.3 | Properties of CdTe epilayers                                                     | 119 |

|   | 5.5   | CdTe on other substrates                                                         | 124 |

|   | 5.5.1 | Introduction                                                                     | 124 |

|   | 5.5.2 | Epitaxial growth of CdTe on $\{0001\}$ and $\{01\overline{1}6\}$ CdS             | 125 |

|   | 5.5.3 | Homoepitaxial growth on $(\overline{1}\overline{1}\overline{1})$ B CdTe $\ldots$ | 132 |

|   | 5.6   | Epitaxial growth of ZnTe                                                         | 134 |

|   | 5.6.1 | Introduction                                                                     | 134 |

|   | 5.6.2 | Growth conditions                                                                | 134 |

|   | 5.6.3 | Properties of ZnTe layers grown                                                  | 135 |

|   | 5.6.4 | Growth of p-ZnTe on n-substrate/i-CdTe heterojunctions .                         | 139 |

|   | 5.7   | The doping of ZnTe and CdTe                                                      | 140 |

|   | 5.7.1 | Introduction                                                                     | 140 |

|   | 5.7.2 | Doping of ZnTe using ammonia                                                     | 143 |

|   | 5.7.3 | Doping of ZnTe using elemental arsenic                                           | 145 |

|   | 5.7.4 | The doping of CdTe using elemental arsenic                                       | 147 |

|   | 5.7.5 | Discussion                                                                       | 148 |

|   | 5.8   | The Growth of $Cd_{1-x}Zn_xTe$                                                   | 149 |

|   | 5.8.1 | Introduction                                                                     | 149 |

|   | 5.8.2 | Growth conditions                                                                | 150 |

|   | 5.8.3 | Results and discussion                                                           | 150 |

|   | 5.8.4 | Conclusions                                                                      | 161 |

|   | 5.9   | Contacts to solar cell devices                                                   | 161 |

|   | 5.9.1 | Introduction                                                                     | 161 |

|   | 5.9.2 | Experimental                                                                     | 163 |

|   | 5.9.3 | Results                                                                          | 163 |

|   | 5.10  | References                                                                       | 164 |

| 6 | The n | -CdS/p-CdTe Solar Cell Grown by MOVPE                                          | 170 |

|---|-------|--------------------------------------------------------------------------------|-----|

|   | 6.1   | Introduction                                                                   | 170 |

|   | 6.2   | Diode Characteristics                                                          | 172 |

|   | 6.2.1 | Diodes prepared on the (0001)A face of CdS                                     | 172 |

|   | 6.2.2 | Diodes prepared on the $(000\overline{1})B$ face of CdS $\ldots \ldots \ldots$ | 174 |

|   | 6.3   | Current transport mechanisms                                                   | 175 |

|   | 6.3.1 | Diodes prepared on the (0001)A face of basal CdS $\ldots$ .                    | 176 |

|   | 6.3.2 | Diodes prepared on the $(000\overline{1})B$ face of CdS $\ldots \ldots \ldots$ | 184 |

|   | 6.4   | Capacitance - Voltage Characteristics                                          | 190 |

|   | 6.4.1 | Diodes prepared on the (0001)A face of CdS                                     | 190 |

|   | 6.4.2 | Diodes prepared on the $(000\overline{1})B$ face of CdS $\ldots \ldots \ldots$ | 193 |

|   | 6.5   | Spectral response                                                              | 195 |

|   | 6.6   | Photocapacitance Studies                                                       | 198 |

|   | 6.7   | Discussion                                                                     | 200 |

|   | 6.8   | References                                                                     | 206 |

| 7 | The n | -CdTe /p-ZnTe Solar Cell Grown by MOVPE                                        | 209 |

|   | 7.1   | Introduction                                                                   | 209 |

|   | 7.2   | Diode Characteristics                                                          | 209 |

|   | 7.3   | Current-transport mechanisms                                                   | 211 |

|   | 7.4   | Capacitance - Voltage Measurements                                             | 218 |

|   | 7.5   | Spectral Response                                                              | 220 |

|   | 7.6   | Photocapacitance Studies                                                       | 221 |

|   | 7.7   | Discussion                                                                     | 223 |

|   | 7.8   | References                                                                     | 227 |

| 8 | The p | -i-n Solar Cell Grown by MOVPE                                                 | 229 |

|   | 8.1   | Introduction                                                                   | 229 |

|   | 8.2   | The n-CdS/i-CdTe/p-ZnTe Solar Cell                                             | 231 |

|   | 8.2.1 | Introduction                                                                   | 231 |

|   | 8.2.2 | Experimental                                                                   | 232 |

|   | 8.2.3 | Diode Characteristics                                                          | 233 |

|   | 8.2.4 | Capacitance - Voltage measurements                                             | 241 |

|   | 8.2.5 | Spectral Response measurements                                                 | 242 |

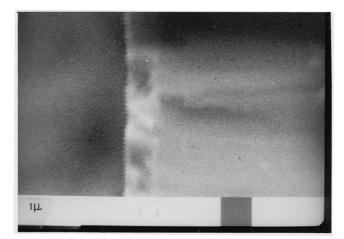

|   | 8.2.6 | EBIC measurements                                                              | 243 |

|   | 8.3   | Discussion                                                                     | 245 |

|   | 8.4   | The n-GaAs/i-CdTe/p-ZnTe Solar Cell                                            | 250 |

.

|   | 8.4.1  | Introduction                                                                             | 250         |

|---|--------|------------------------------------------------------------------------------------------|-------------|

|   | 8.4.2  | $\mathbf{Experimental}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 251         |

|   | 8.4.3  | Diode characteristics                                                                    | 252         |

|   | 8.4.4  | Current-transport properties                                                             | 253         |

|   | 8.4.5  | Capacitance-voltage characteristics                                                      | 256         |

|   | 8.4.6  | Spectral response measurements                                                           | 256         |

|   | 8.4.7  | Discussion                                                                               | 258         |

|   | 8.5    | Preliminary investigations into other device structures                                  | 260         |

|   | 8.5.1  | Introduction                                                                             | <b>2</b> 60 |

|   | 8.5.2  | Experimental                                                                             | 262         |

|   | 8.5.3  | Results and discussion                                                                   | 263         |

|   | 8.6    | References                                                                               | 266         |

| 9 | Conclu | usions and suggestions for further work                                                  | 269         |

| A | Calcul | ation of $\delta_n$ and $\delta_p$                                                       | 275         |

| B | Calcul | ation of the value of R                                                                  | 276         |

| С | Doubl  | e crystal rocking curve analysis                                                         | 277         |

| D | Altern | ative orientations of CdS                                                                | 278         |

# LIST OF FIGURES

1

11 .11

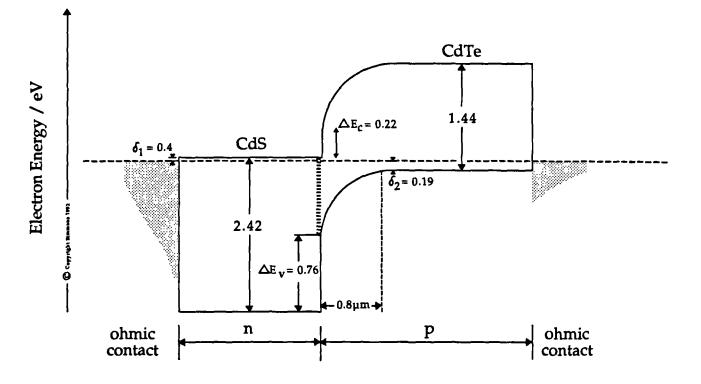

| 2.1  | Energy band diagram of a p-n heterojunction solar cell illus-                                                    |

|------|------------------------------------------------------------------------------------------------------------------|

|      | trating how the electron hole pair is separated by the internal                                                  |

|      | field across the junction                                                                                        |

| 2.2  | A schematic diagram of a heterojunction solar cell 26                                                            |

| 2.3  | The equivalent circuit for a solar cell                                                                          |

| 2.4  | Theoretical efficiencies of heterojunction solar cells as a func-                                                |

|      | tion of energy gap for various absorber and window materials                                                     |

|      | [1]                                                                                                              |

| 2.5  | Effect of the Solar Zenith Angle on Insolation at the surface of                                                 |

|      | the Earth $\ldots \ldots 31$ |

| 2.6  | Typical variation of the current, I as a function of the voltage,                                                |

|      | V for a solar cell in the dark and under illumination. The                                                       |

|      | magnitude of $I_o$ is exaggerated for clarity $\ldots \ldots \ldots 32$                                          |

| 2.7  | Spectral distribution of solar radiation under AM0, AM1 and                                                      |

|      | AM2 conditions [1]. $\ldots$ 34                                                                                  |

| 2.8  | Equilibrium energy band diagram for the CdS/CdTe hetero-                                                         |

|      | junction before (a) and after (b) the formation of an abrupt                                                     |

|      | p-n junction                                                                                                     |

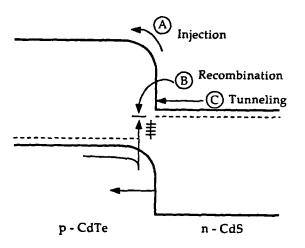

| 2.9  | Current-transport mechanisms in forward biased p-n junctions 50                                                  |

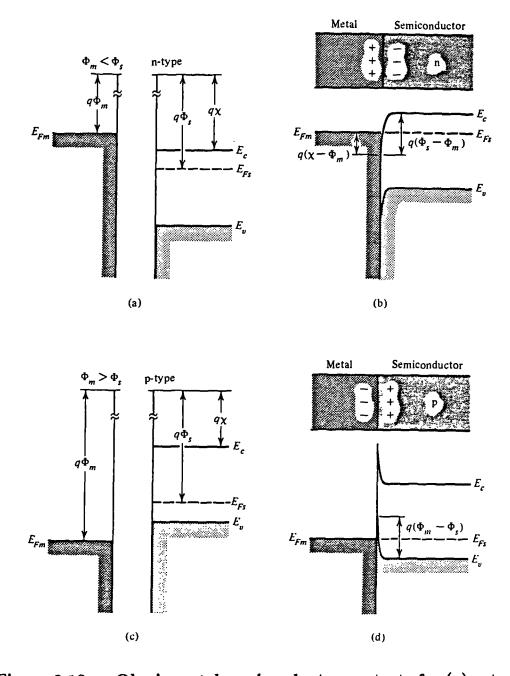

| 2.10 | Ohmic metal-semiconductor contacts for (a) n-type semicon-                                                       |

|      | ductor and (b) p-type semiconductor showing equilibrium                                                          |

|      | band diagrams before and after formation                                                                         |

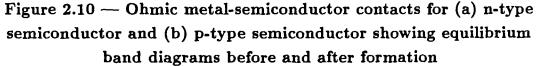

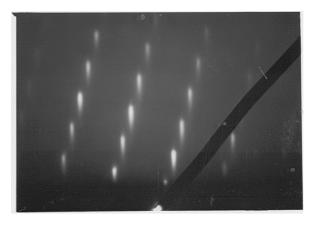

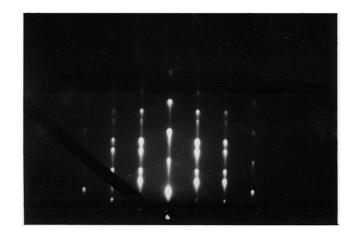

| 3.1  | Analysis of crystallinity using RHEED                                                                            |

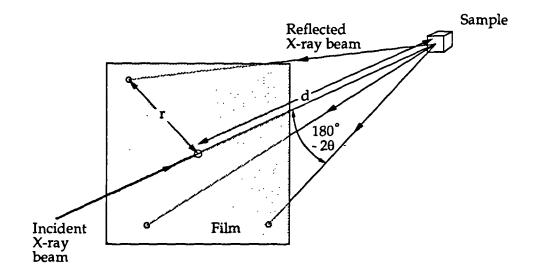

| 3.2  | Crystal orientation by Laue x-ray back reflection                                                                |

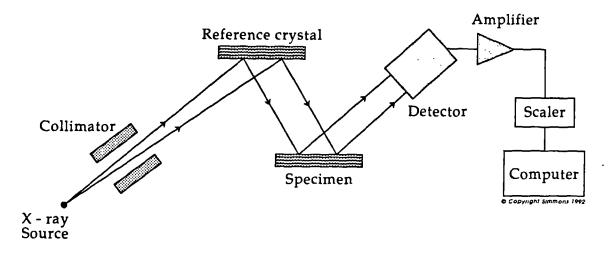

| 3.3  | Double crystal x-ray diffraction                                                                                 |

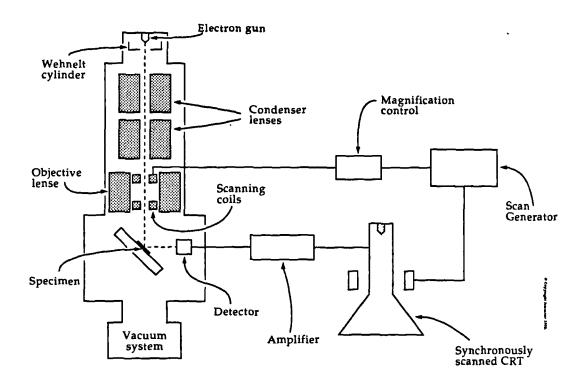

| 3.4        | Diagrammatic representation of the SEM                                                                                                                   |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

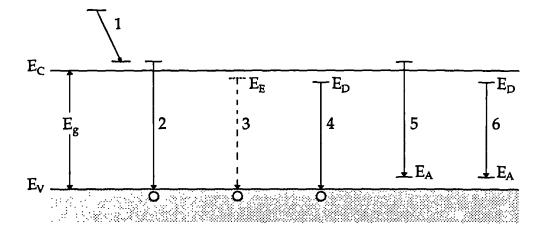

| 3.5        | Schematic diagram of radiative transitions                                                                                                               |

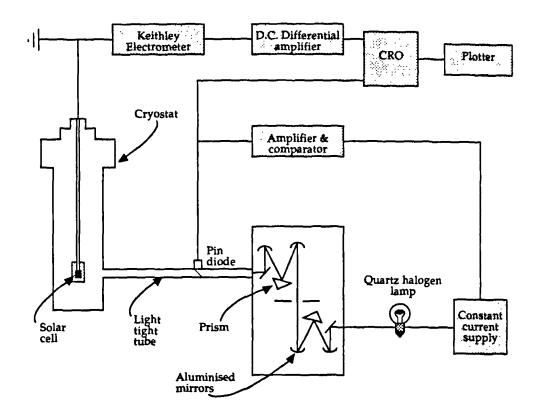

| 3.6        | Spectral response experimental set-up                                                                                                                    |

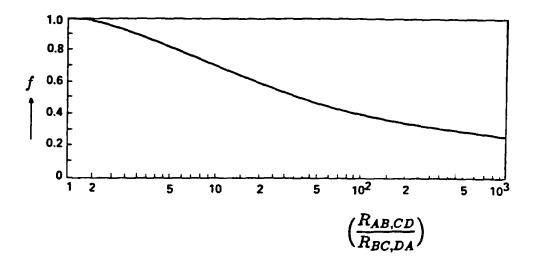

| 3.7        | The value of $f$ plotted as a function of $\left(\frac{R_{AB,CD}}{R_{BC,DA}}\right)$                                                                     |

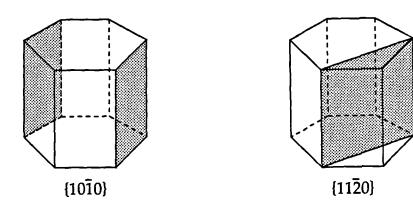

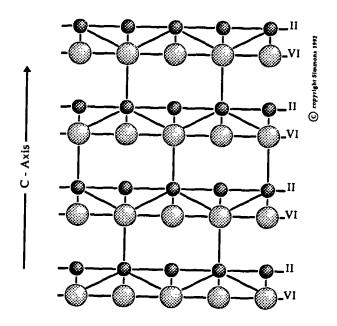

| 4.1        | Crystal lattice of CdS showing the layers of group II and group<br>VI atoms perpendicular to the c-axis in basal CdS                                     |

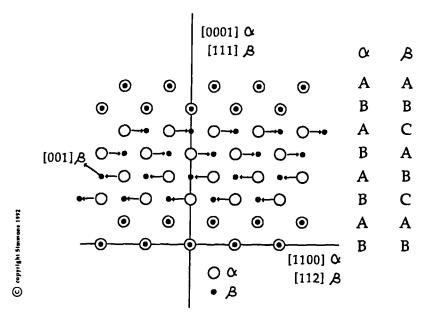

|            | $\alpha$ - $\beta$ phase transformation [21]                                                                                                             |

| 4.4        | the surfaces of basal CdS                                                                                                                                |

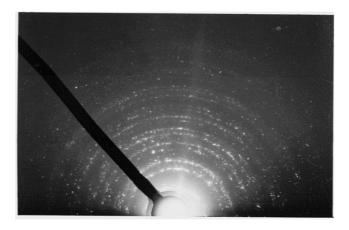

|            | RHEED micrographs of basal CdS after polishing in HCl/H <sub>2</sub> O 93<br>A RHEED micrograph of a CdS crystal polished in<br>HCl/KCl/H <sub>2</sub> O |

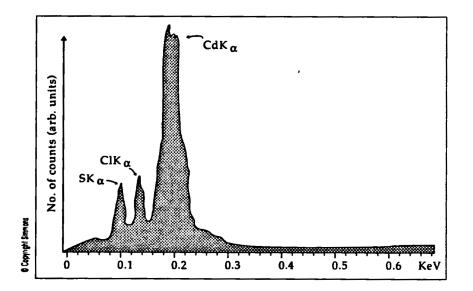

| 4.7<br>4.8 | EDAX trace of CdS surface etched in HCl/KCl/H <sub>2</sub> O                                                                                             |

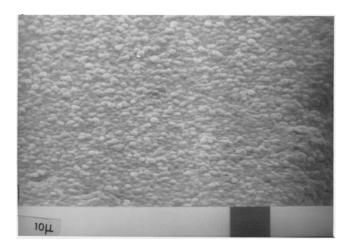

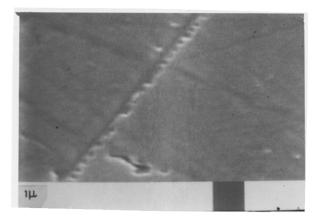

| 4.9        | a HCl/KCl/H <sub>2</sub> O polished surface                                                                                                              |

| 4.10       | The hydroplane polishing apparatus                                                                                                                       |

| 5.1        | The formation of an epitaxial layer by MOVPE 109                                                                                                         |

| 5.2        | A schematic diagram of the MOVPE reactor                                                                                                                 |

|            | The MOVPE reactor                                                                                                                                        |

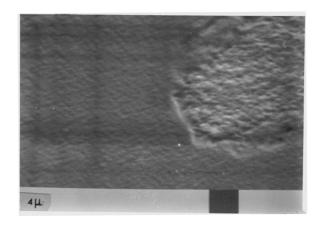

| 5.5        | An XTEM micrograph of a layer of CdTe grown at 325°C on<br>{100} GaAs                                                                                    |

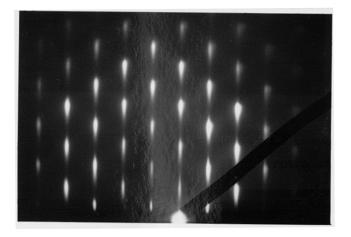

| 5.6        | A RHEED micrograph of a layer of CdTe grown at 325°C with<br>a II:VI ratio of 1:1                                                                        |

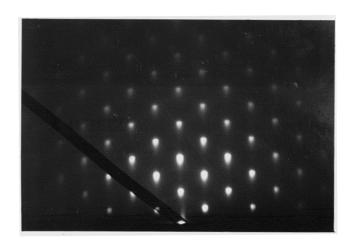

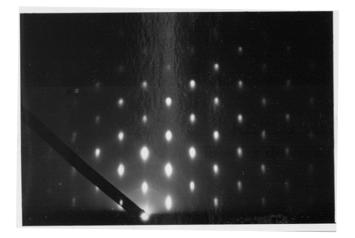

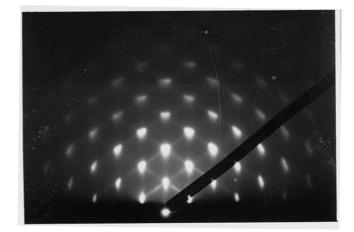

| 5.7        | RHEED analysis of a Te-rich CdTe epilayer on {100} GaAs<br>looking down a (a) <110> and (b) <110> zone axis                                              |

|            |                                                                                                                                                          |

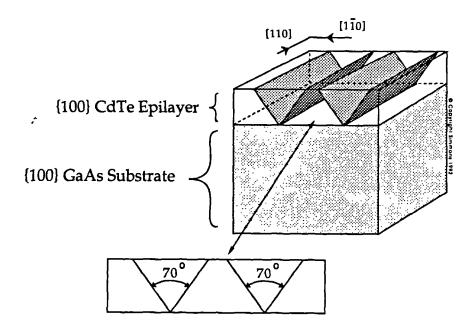

| 5.8          | Crystallographic orientation of defects within the {100} ori-<br>ented CdTe epilayer                                                                                                          |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.9          | A double crystal rocking curve of a CdTe layer grown on {100}                                                                                                                                 |

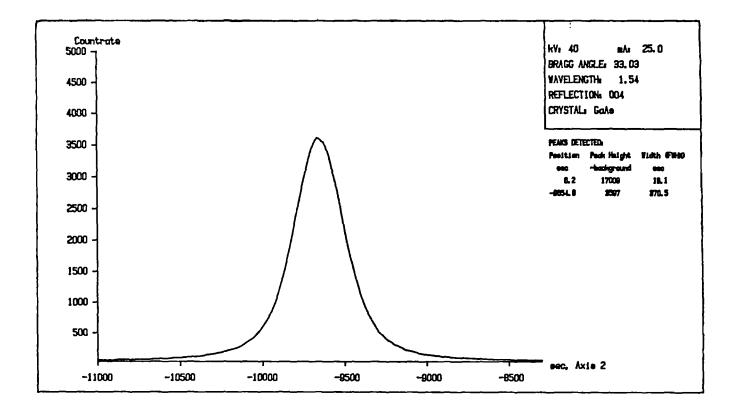

|              | GaAs                                                                                                                                                                                          |

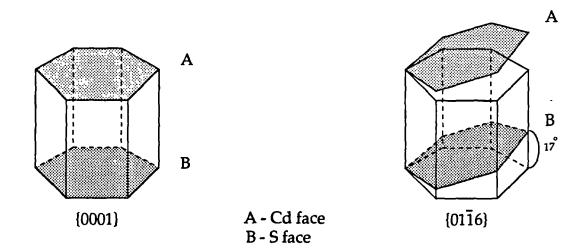

| 5.10         | The $\{0001\}$ and $\{01\overline{1}6\}$ planes in single crystal CdS                                                                                                                         |

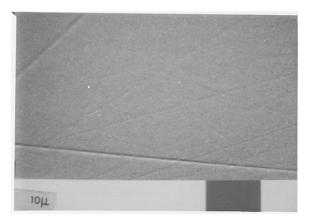

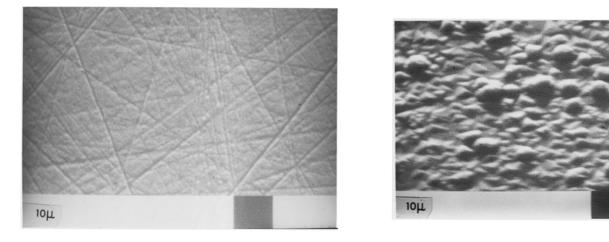

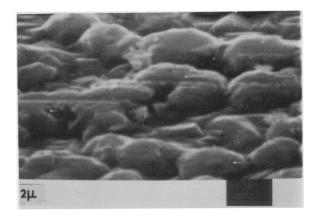

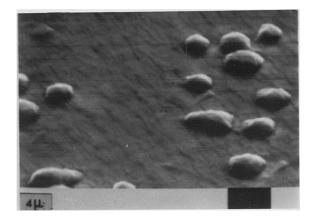

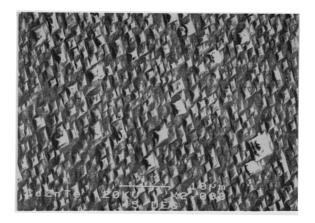

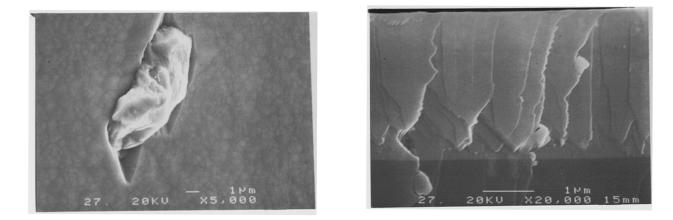

| 5.11         | An SEM micrograph of a CdTe epilayer on (0001)A CdS 126                                                                                                                                       |

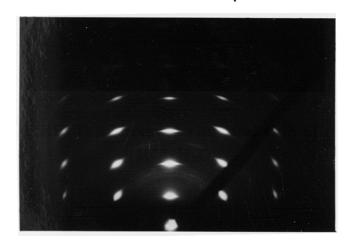

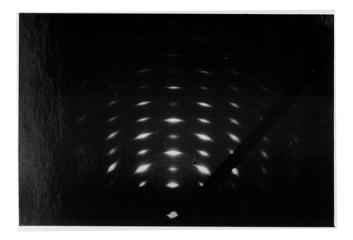

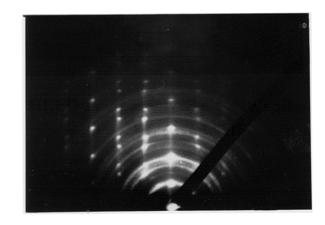

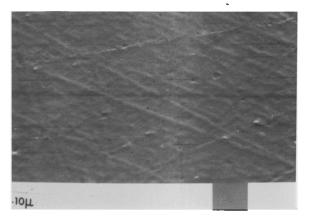

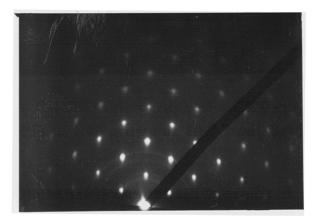

| 5.12         | RHEED micrograph of a CdTe epilayer formed on the $(000\overline{1})B$                                                                                                                        |

| 5.13         | face of CdS                                                                                                                                                                                   |

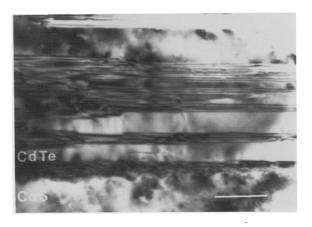

|              | the $(000\overline{1})B$ face of CdS $\dots \dots \dots$                                      |

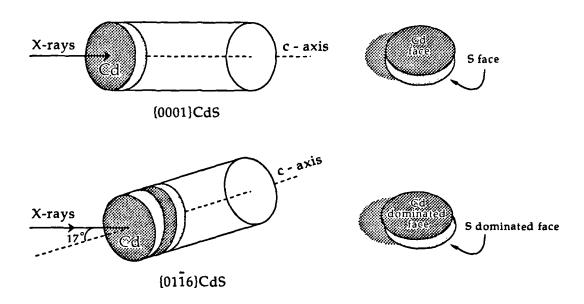

| 5.14         | The polarity of the $\{01\overline{1}6\}$ CdS surfaces $\ldots \ldots \ldots$ |

| 5.15         |                                                                                                                                                                                               |

| 5 16         | of CdS                                                                                                                                                                                        |

| 0.10         | on the $(01\overline{16})$ B face of CdS                                                                                                                                                      |

| 5.17         | (a) An XTEM micrograph and (b) selected area diffraction                                                                                                                                      |

|              | pattern of the CdTe epilayer on the $(01\overline{1}\overline{6})B$ face of CdS $\ldots$ 130                                                                                                  |

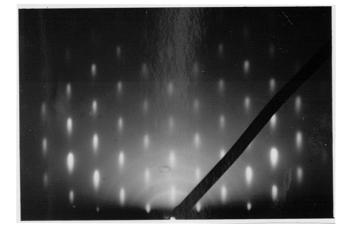

| 5.18         | RHEED pattern taken along the <110> zone axis of a                                                                                                                                            |

|              | twinned CdTe layer grown on $(\overline{1}\overline{1}\overline{1})$ CdTe $\ldots \ldots \ldots \ldots \ldots 132$                                                                            |

| 5.19         | (a) A RHEED and (b) SEM micrograph of a ZnTe layer grown                                                                                                                                      |

|              | on {100} GaAs 135                                                                                                                                                                             |

| 5.20         |                                                                                                                                                                                               |

|              | GaAs grown at 325°C 135                                                                                                                                                                       |

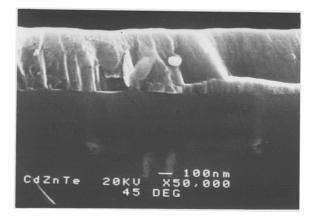

| 5.21         | XTEM micrograph of a ZnTe layer grown on {100} GaAs at                                                                                                                                        |

|              | 350°C 135                                                                                                                                                                                     |

| 5.22         | DCXRD rocking curve for a layer of ZnTe grown on {100}                                                                                                                                        |

|              | GaAs at 325°C                                                                                                                                                                                 |

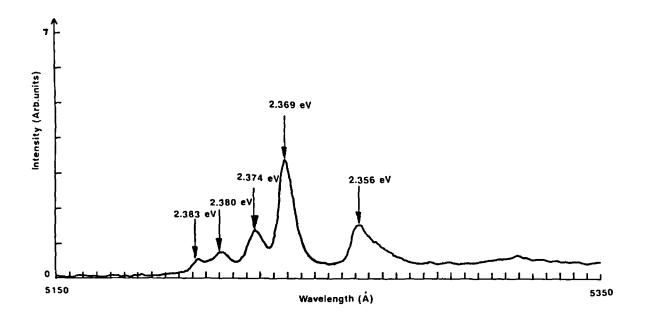

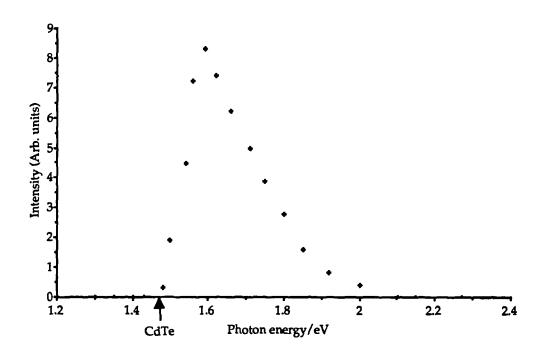

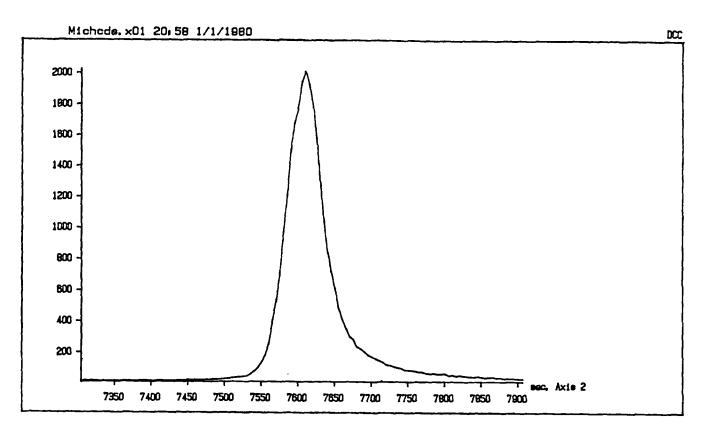

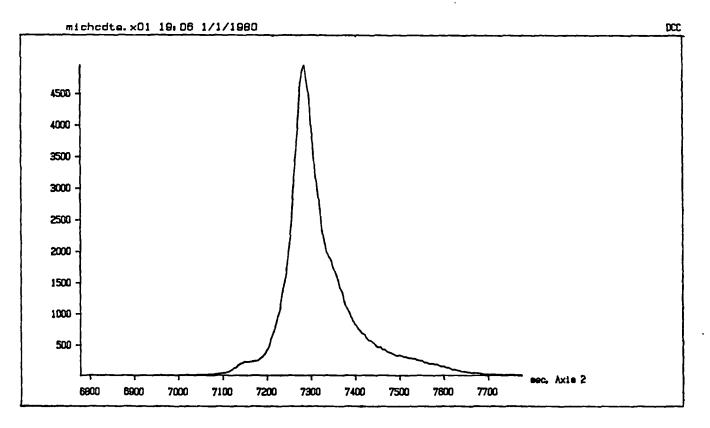

| 5.23         | Photoluminescence spectrum of a ZnTe layer grown at 325°C 137                                                                                                                                 |

| 5.24         | RHEED pattern of a CdTe/ZnTe epilayer on $\{0001\}CdS$ 140                                                                                                                                    |

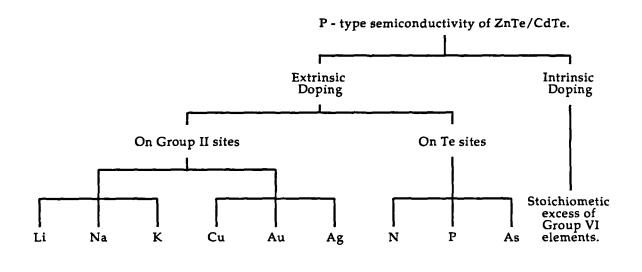

| 5.25         | A diagram illustrating the p-type semiconductivity of                                                                                                                                         |

| E 00         | CdTe/ZnTe                                                                                                                                                                                     |

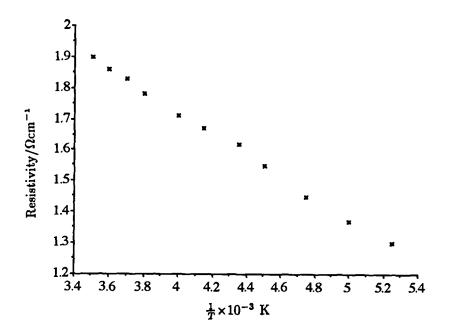

| <b>J.</b> 20 | Temperature-dependent carrier conductivity for p-ZnTe lay-                                                                                                                                    |

|              | ers doped with arsenic                                                                                                                                                                        |

.

•

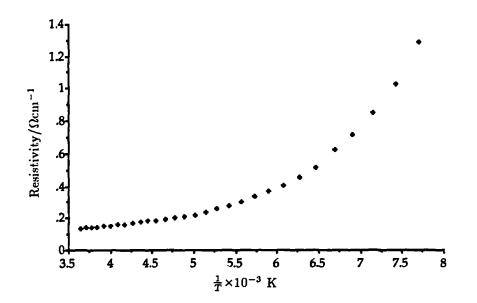

| 5.27 | Temperature-dependent carrier conductivity for p-CdTe lay-               |

|------|--------------------------------------------------------------------------|

|      | ers doped with arsenic 146                                               |

| 5.28 |                                                                          |

| ~ ~~ | $\{100\}$ GaAs                                                           |

| 5.29 |                                                                          |

|      | of 1:69 grown at 400°C on {100}GaAs 150                                  |

| 5.30 |                                                                          |

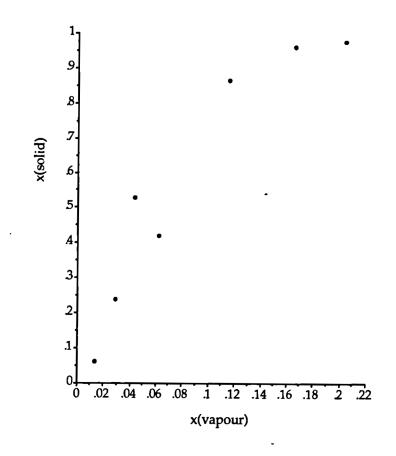

| F 01 | the Cd mole fraction                                                     |

| 5.31 | <b>- - -</b>                                                             |

|      | of the CZT epilayer 151                                                  |

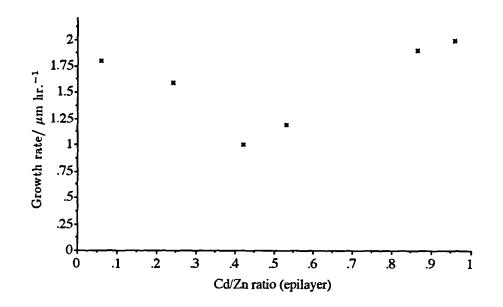

| 5.32 | Growth rate versus composition for the CZT epilayers 154                 |

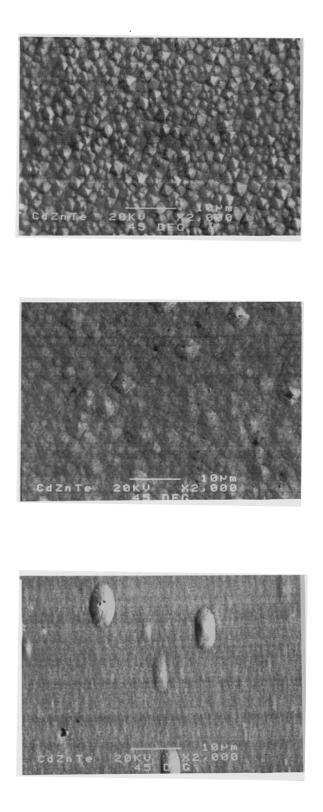

| 5.33 | SEM micrographs of CZT epilayers with (a) $x=0.06$ , (b) $x=$            |

|      | 0.24, and (c) $x=0.5$ , illustrating the change in surface mor-          |

|      | phology with composition                                                 |

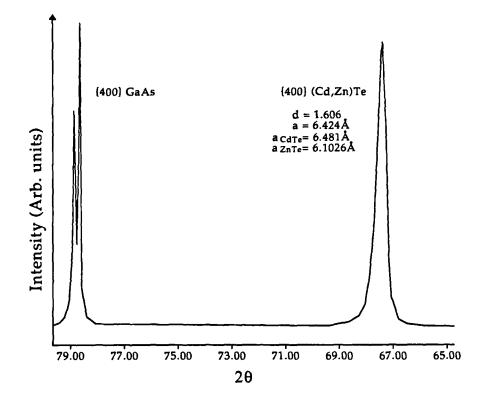

| 5.34 | X-ray diffraction data for a $Cd_{1-x}Zn_xTe$ epilayer where             |

|      | x=0.04                                                                   |

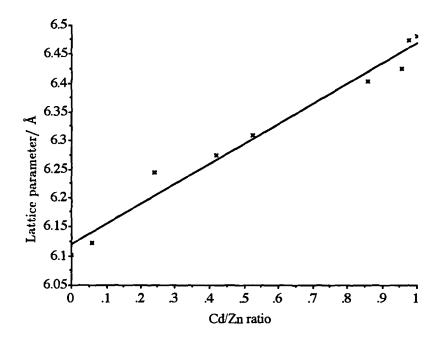

| 5.35 | The variation of the lattice parameter for CZT alloys with               |

|      | change in composition                                                    |

| 5.36 | A photoconductivity trace of a CZT alloy where the value of              |

|      | Cd/Zn=0.956                                                              |

| 5.37 | The band gap versus $Cd/Zn$ molar ratio for the CZT alloys               |

|      | of varying composition                                                   |

| 5.38 | An XTEM micrograph of a $Cd_{0.06}Zn_{0.94}$ Te epilayer illustrat-      |

|      | ing the dense array of misfit dislocations at the interface $\ldots$ 154 |

| 5.39 | (a) An SEM micrograph of a CZT epilayer where $Cd/Zn=0.09$               |

|      | and (b) the corresponding XSEM micrograph illustrating                   |

|      | the thickness of the layer                                               |

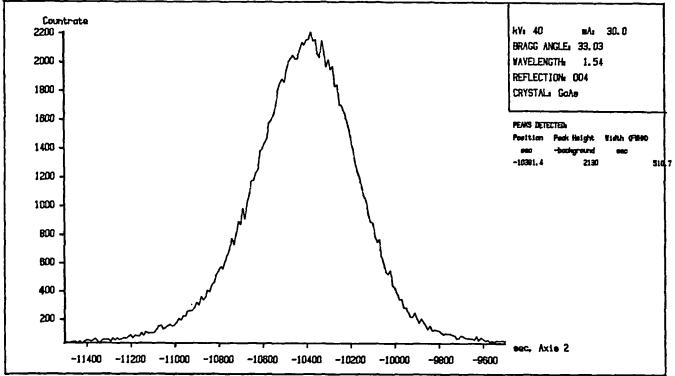

| 5.40 | A DCXRD trace of the CZT epilayer where $Cd/Zn=0.09$ 154                 |

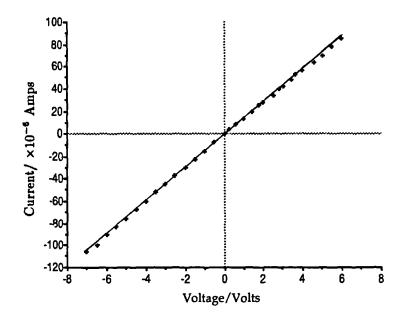

| 5.41 | I-V characteristic for a carbon paste contact on p-CdTe 163              |

|      | The band structure diagram of the n-CdS/p-CdTe heterojunc-               |

|      | tion                                                                     |

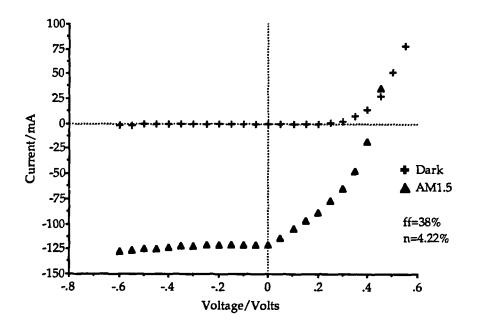

| 6.2  | Solar output characteristics of a n-CdS/p-CdTe solar cell grown          |

|      | on the Cd face of basal CdS under AM1.5 illumination                     |

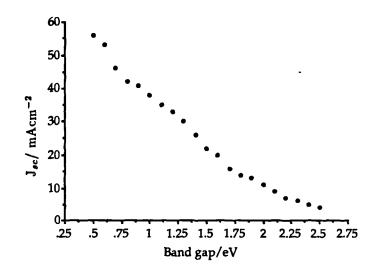

| 6.3  | Theoretical photon currents generated as a function of band              |

|      | gap energy for AM1.5 illumination [10]                                   |

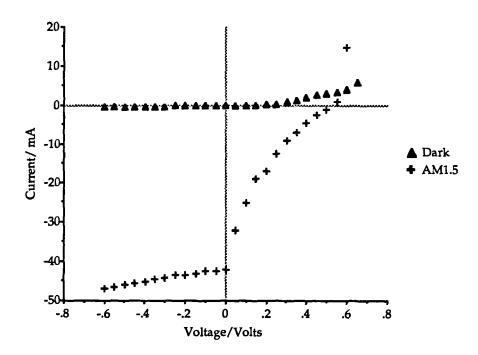

| 6.4  | Solar output characteristics of a n-CdS/p-CdTe solar cell grown                                                                                                                   |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

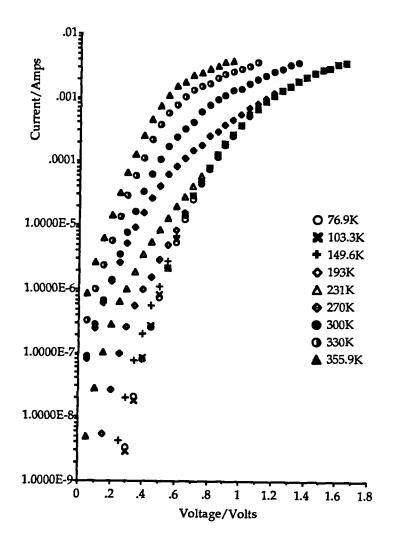

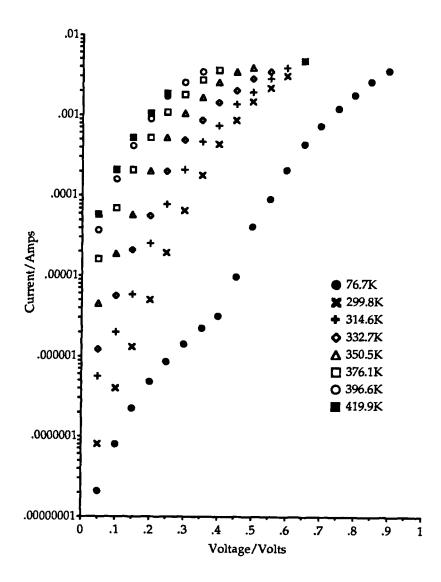

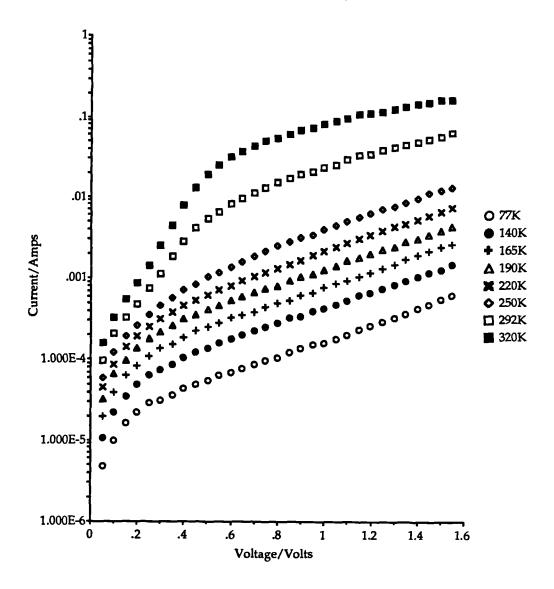

| 6.5  | on the S face of basal CdS under AM1.5 illumination $\ldots \ldots 1$<br>Dark I <sub>f</sub> -V characteristics of a n-CdS/p-CdTe diode grown on                                  | 174 |

|      | the Cd face of basal CdS at temperatures between 70-350                                                                                                                           |     |

|      | К 1                                                                                                                                                                               | 176 |

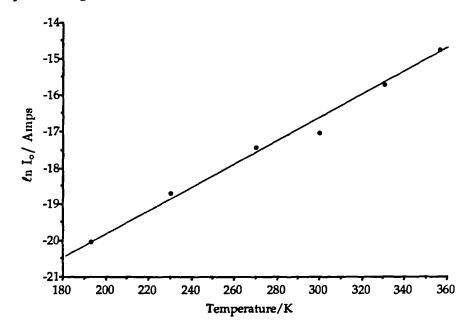

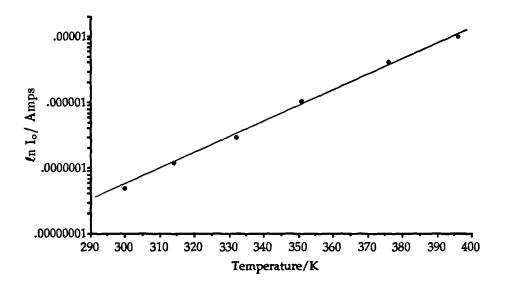

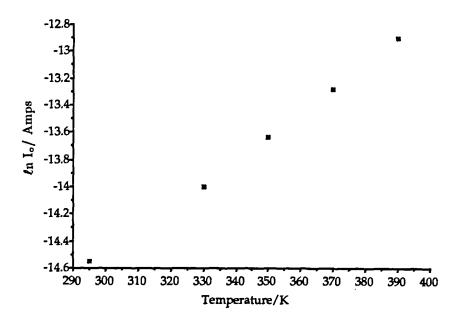

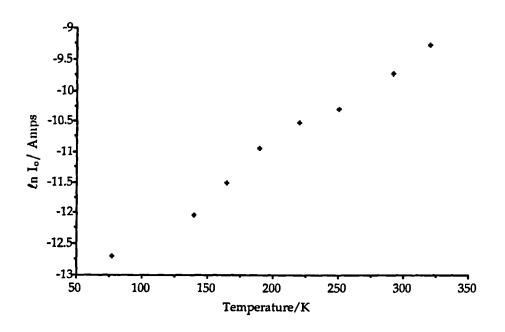

| 6.6  | A graph of $\ell n I_o$ versus temperature $\ldots \ldots \ldots$ | 178 |

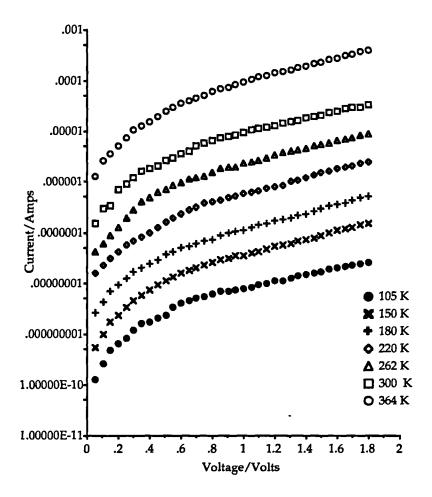

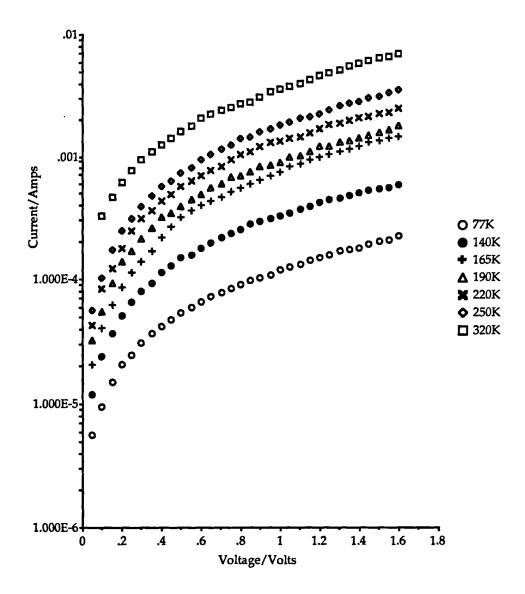

|      | Dark Ir-V characteristics for a n-CdS/p-CdTe diode grown on                                                                                                                       |     |

|      | the Cd face of basal CdS at temperatures between 105-364                                                                                                                          |     |

|      | К 1                                                                                                                                                                               | 180 |

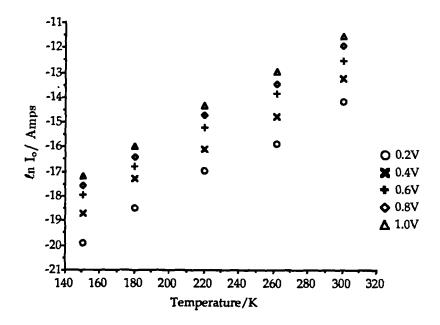

| 6.8  | The variation of $\ell n I_0$ with temperature $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 1$                                                                        | 183 |

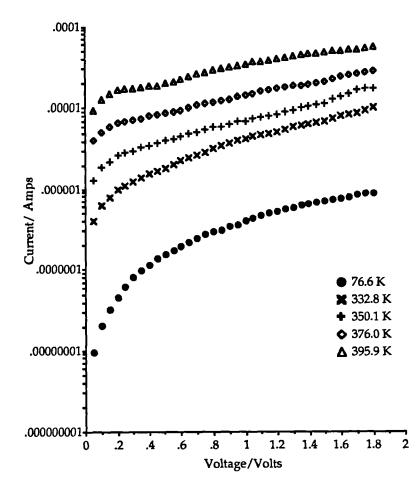

| 6.9  | Dark I <sub>f</sub> -V characteristics for a n-CdS/p-CdTe diode grown on                                                                                                          |     |

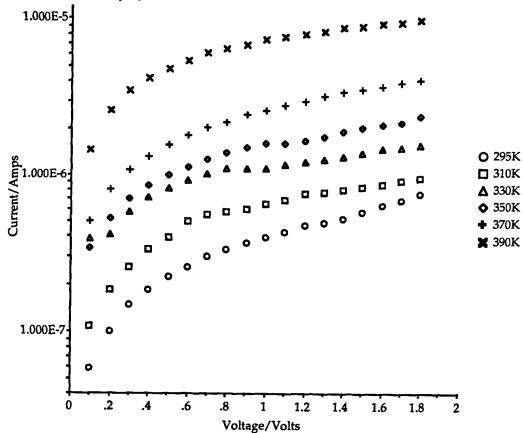

|      | the S face of basal CdS at temperatures between 300-397 K $\ldots$ 1                                                                                                              | 184 |

| 6.10 | The variation of $ln I_0$ with temperature $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 1$                                                                                   | 86  |

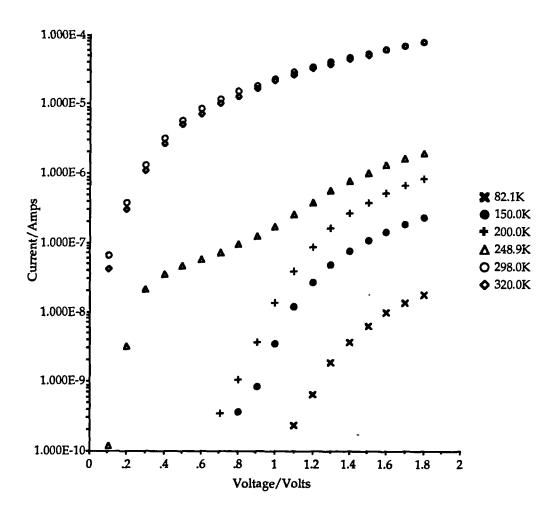

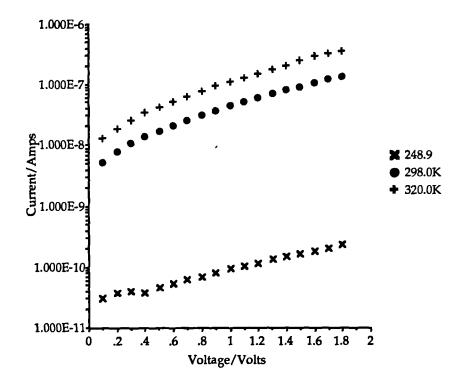

| 6.11 |                                                                                                                                                                                   |     |

|      | the S face of basal CdS at temperatures 77-400 K                                                                                                                                  | 86  |

| A 10 | -                                                                                                                                                                                 |     |

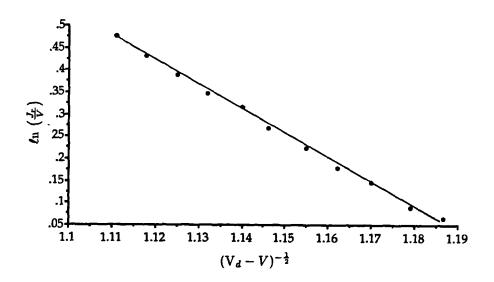

| 6.12 | A graph of $ln\left(\frac{J_r}{V}\right)$ versus $(V_d - V)^{-\frac{1}{2}}$ 1                                                                                                     | 187 |

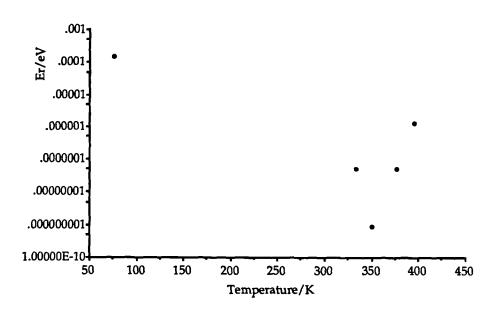

| 6.13 | A plot of $E_r$ versus temperature $\ldots \ldots \ldots$         | 88  |

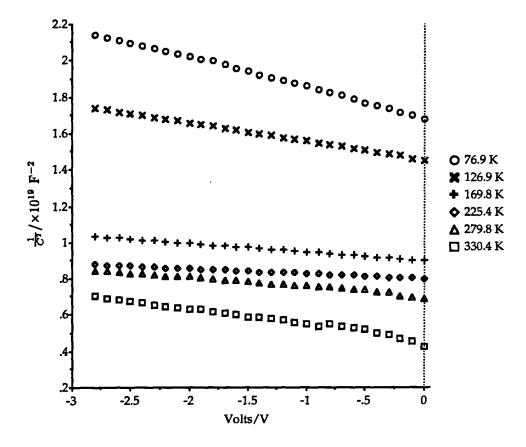

| 6.14 | $C^{-2}$ versus reverse applied voltage for n-CdS/p-CdTe diode                                                                                                                    |     |

|      | grown on the Cd face                                                                                                                                                              | 91  |

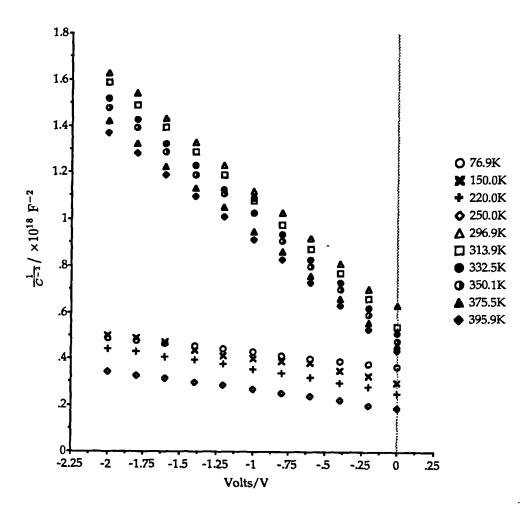

| 6.15 | $C^{-2}$ versus reverse applied voltage for n-CdS/p-CdTe diode                                                                                                                    |     |

|      | grown on the S face 1                                                                                                                                                             | 93  |

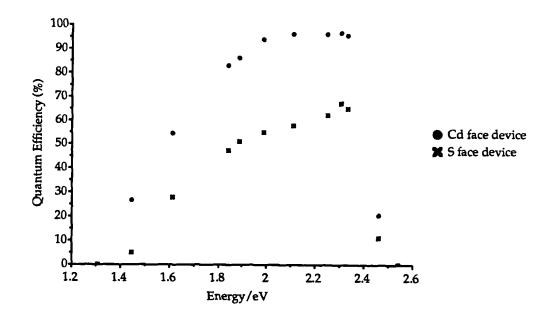

| 6.16 | The spectral response of n-CdS/p-CdTe diodes grown on the                                                                                                                         |     |

| _    | Cd and S faces of basal CdS 1                                                                                                                                                     | 95  |

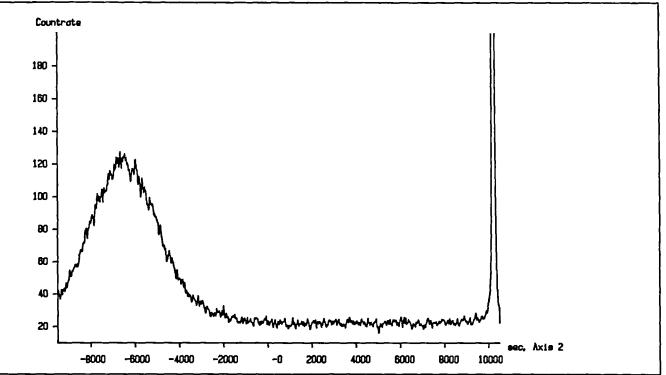

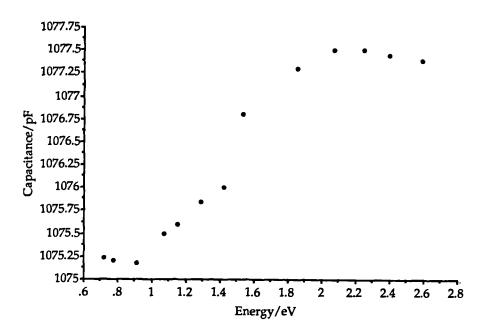

| 6.17 | The photocapacitance spectrum of a diode grown on the Cd                                                                                                                          |     |

|      | face                                                                                                                                                                              | 98  |

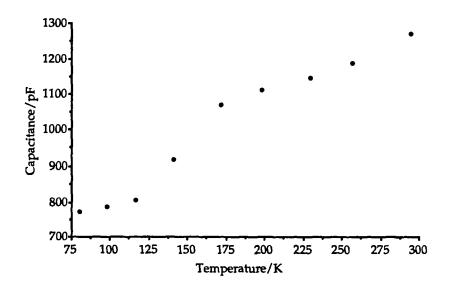

| 6.18 | The variation of capacitance with T for a Cd face device $\ldots \ldots 2$                                                                                                        | 205 |

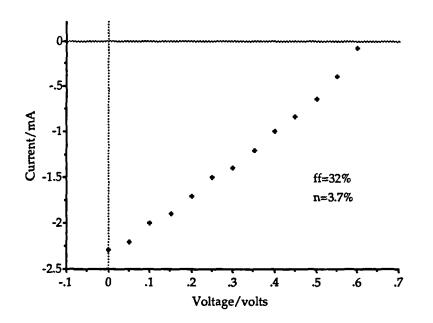

| 7.1  | The solar output of a n-CdTe/p-ZnTe diode under AM1.5 il-                                                                                                                         |     |

|      | lumination                                                                                                                                                                        | 210 |

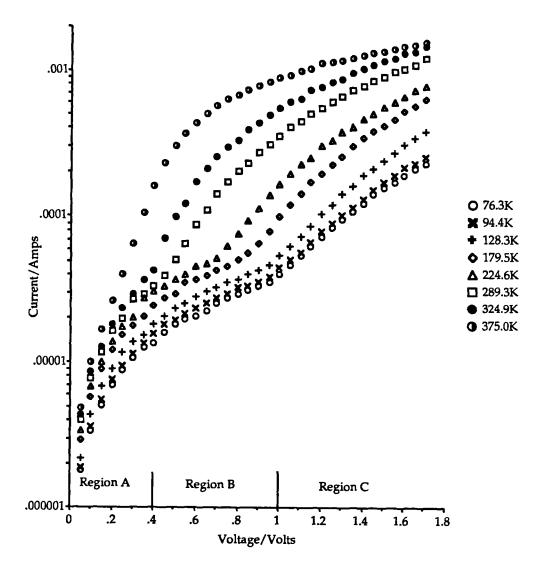

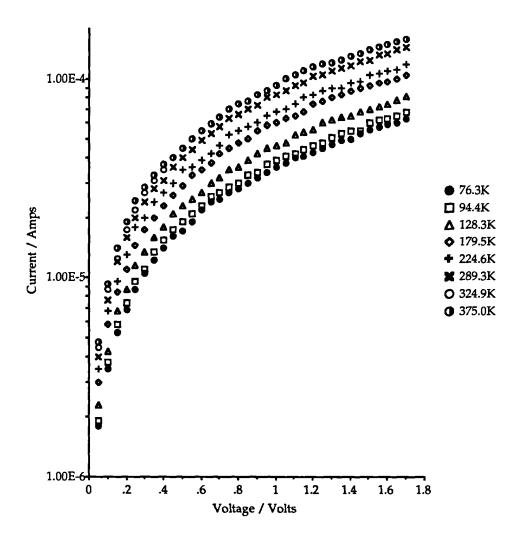

| 7.2  | The forward, dark I-V characteristics for the n-CdTe/p-ZnTe                                                                                                                       |     |

|      | diode $\ldots \ldots 2$                                                                                            | 211 |

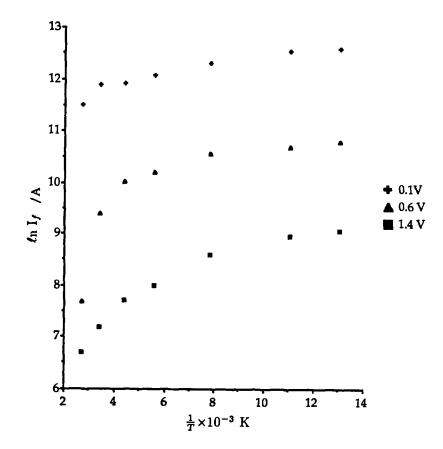

| 7.3  | A plot of $ln I_f$ vs. $\frac{1}{T}$ for n-CdTe/pZnTe diode                                                                                                                       | 213 |

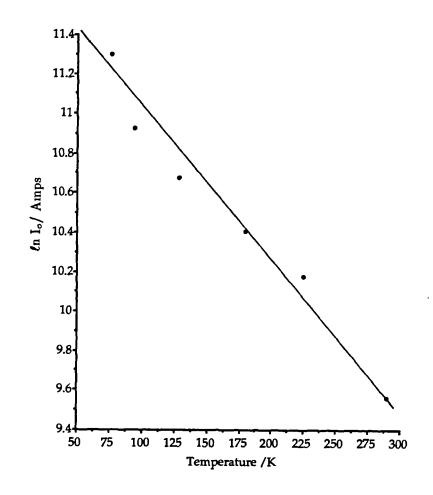

| 7.4  | A plot of $\ell n I_o$ versus temperature for the n-CdTe/p-ZnTe                                                                                                                   |     |

|      | diode                                                                                                                                                                             | 14  |

| 7.5   | The reverse dark I-V characteristics for the n-CdTe/p-ZnTe                                     |

|-------|------------------------------------------------------------------------------------------------|

|       | diode                                                                                          |

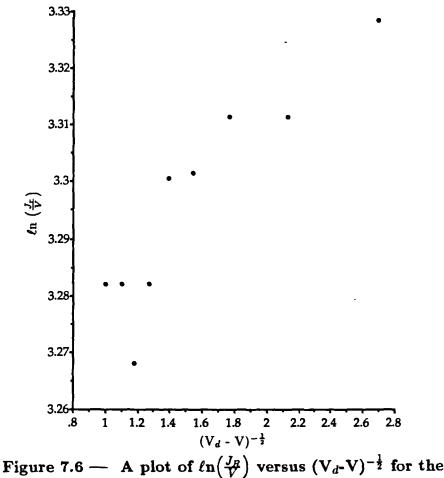

| 7.6   | A plot of $ln\left(\frac{J_R}{V}\right)$ versus $(V_d-V)^{-\frac{1}{2}}$ for the n-CdTe/p-ZnTe |

|       | diode                                                                                          |

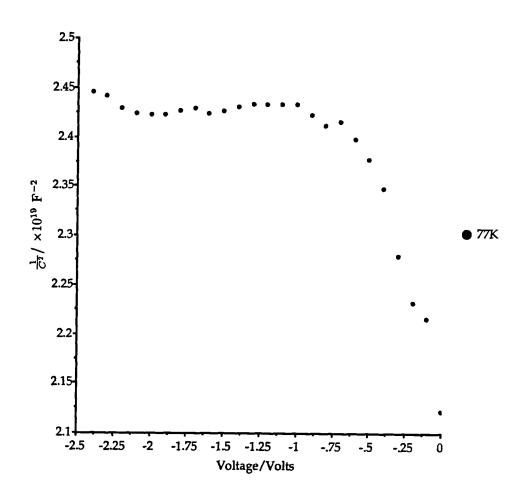

| 7.7   | The $C^{-2}$ versus V curves for the n-CdTe/p-ZnTe diode at dif-                               |

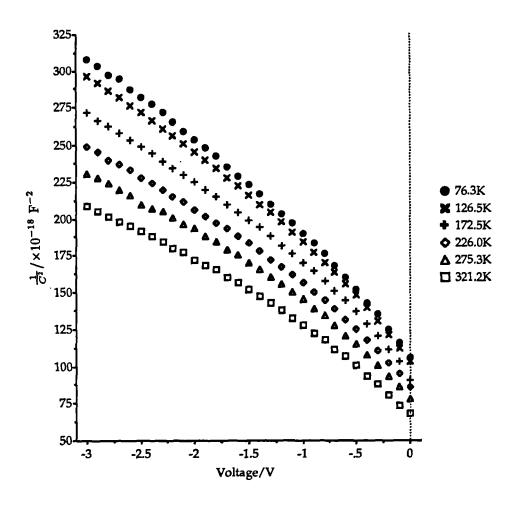

|       | ferent temperatures 218                                                                        |

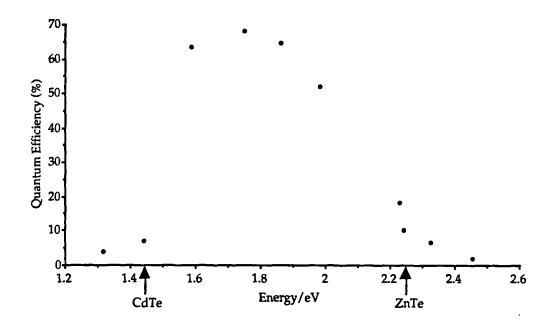

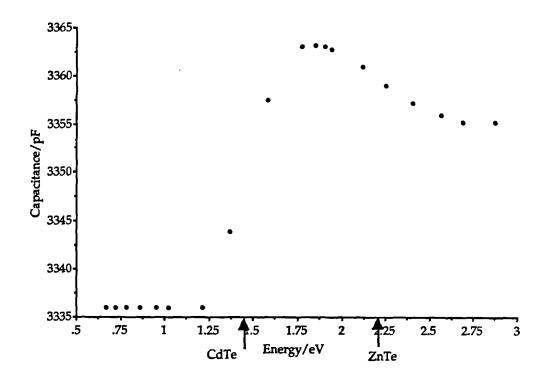

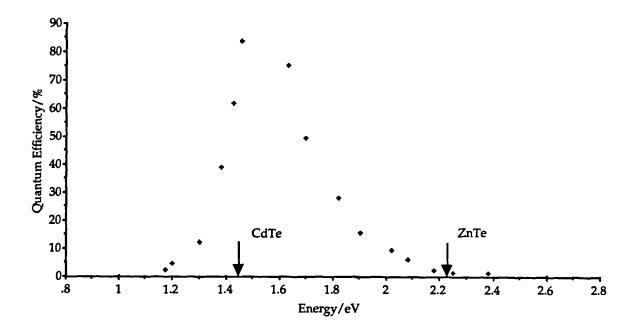

| 7.8   | The spectral response curve of the n-CdTe/p-ZnTe diode 220                                     |

| 7.9   | The photocapacitance spectra of the n-CdTe/p-ZnTe diode 221                                    |

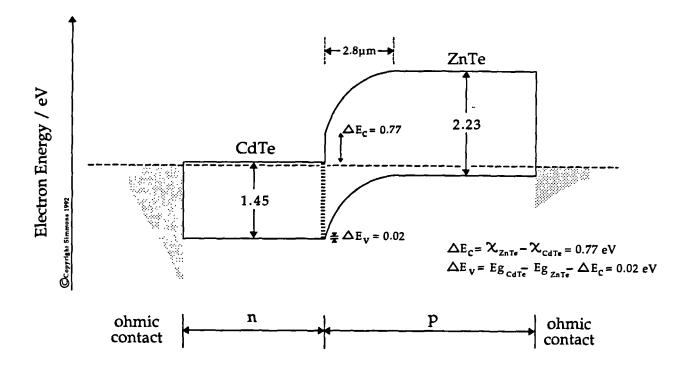

| 7.10  | The expected band structure diagram of the n-CdTe/p-ZnTe                                       |

| 0.1   | solar cell                                                                                     |

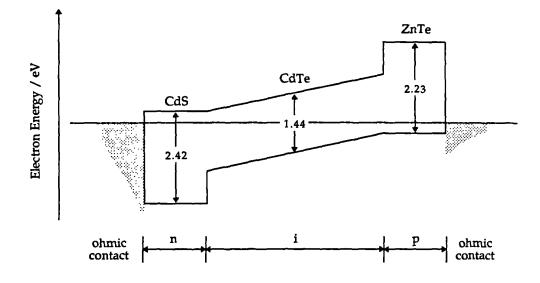

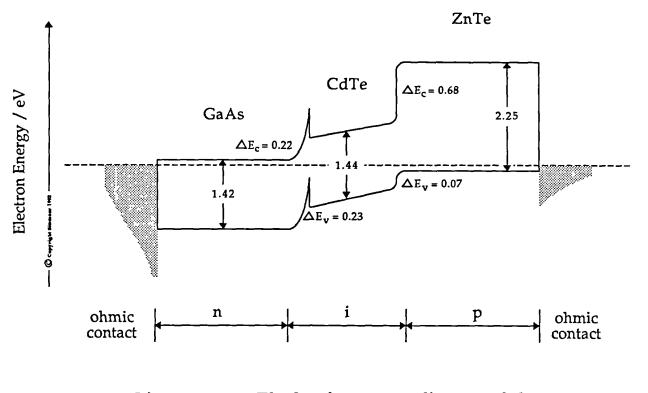

| 8.1   | The idealised band structure diagram of the n-CdS/i-CdTe/p-<br>ZnTe solar cell                 |

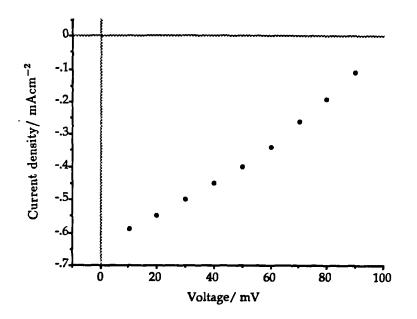

| 8.2   | Photovoltaic output characteristics for an undoped p-i-n device                                |

| 0.2   | under AM1.5 illumination                                                                       |

| 8.3   | Photovoltaic output characteristics for a doped p-i-n device                                   |

|       | under AM1.5 illumination 233                                                                   |

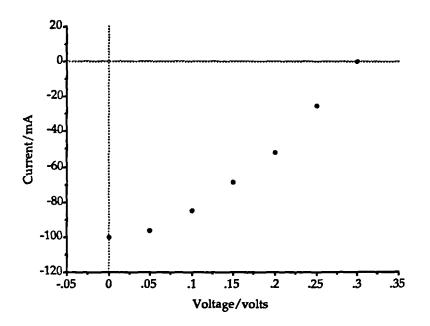

| 8.4   | The dark forward $I_f$ - V characteristics for an undoped p-i-n                                |

| 0 5   | diode                                                                                          |

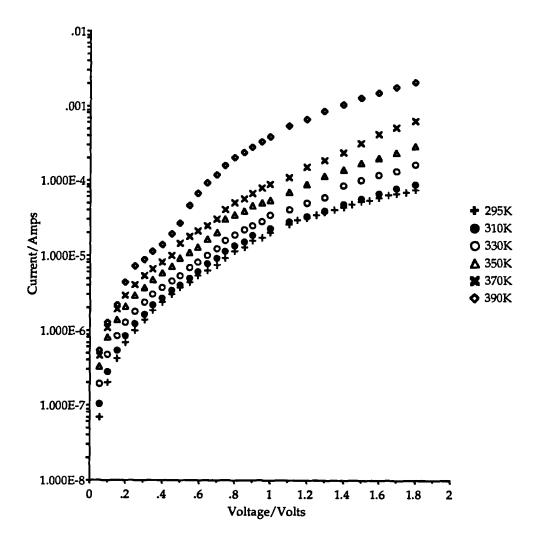

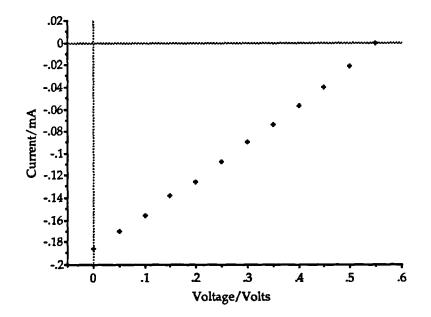

| 0.0   | The dark reverse $I_r$ - V characteristics for an undoped p-i-n<br>diode                       |

|       |                                                                                                |

| 8.6   | • • •                                                                                          |

| 8.7   | · · ·                                                                                          |

| 0 0   | p-i-n diode                                                                                    |

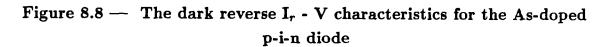

| 0.0   | The dark reverse $I_r$ - V characteristics for the As-doped p-i-n<br>diode                     |

|       |                                                                                                |

|       | A plot of $ln I_0$ with temperature                                                            |

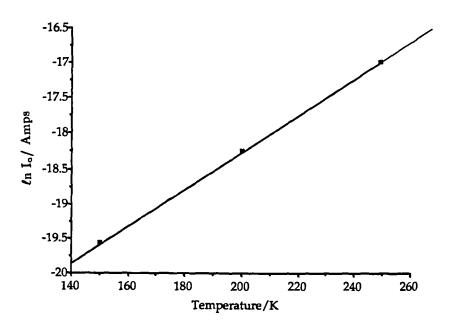

| 8.10  | The C-V characteristics for the As-doped p-i-n diode at 295.0                                  |

| 8 1 1 | K                                                                                              |

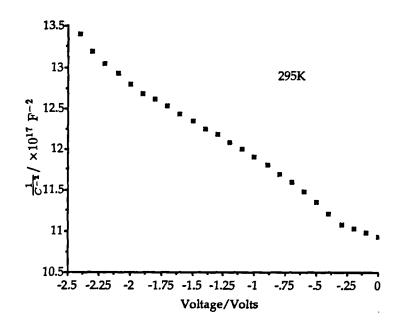

| 0.11  | diode                                                                                          |

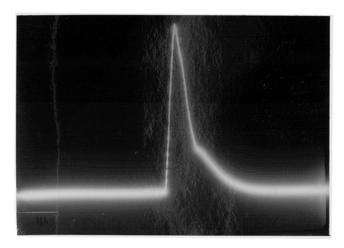

| 8.12  | The EBIC signal across the heterojuntion interface for the                                     |

|       | p-i-n diode                                                                                    |

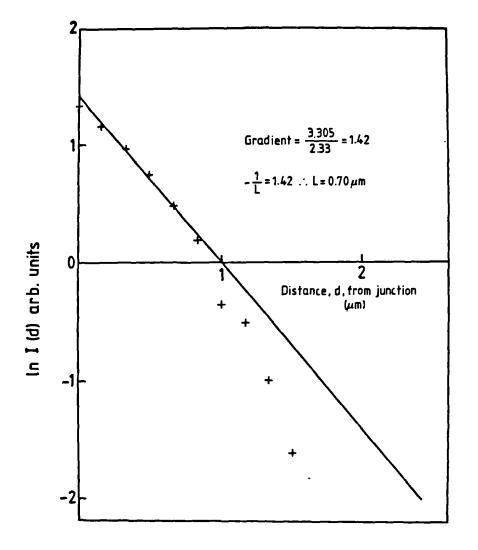

| 8.13  | A plot of $ln I(d)$ versus d for the undoped p-i-n structure                                   |

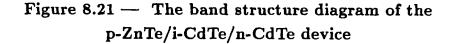

| 8.14 | The band structure diagram of the p-ZnTe/i-CdTe/n-GaAs          |             |

|------|-----------------------------------------------------------------|-------------|

|      | device                                                          | 250         |

| 8.15 | The Photovoltaic output charactersistics for the p-ZnTe/i-      |             |

|      | CdTe/n-GaAs diode under AM1.5 illumination                      | 252         |

| 8.16 | The dark forward $I_f$ -V charactersistics for the p-ZnTe/i-    |             |

|      | CdTe/n-GaAs diode                                               | 253         |

| 8.17 | The dark reverse $I_r$ -V charactersistics for the p-ZnTe/i-    |             |

|      | CdTe/n-GaAs diode                                               | 254         |

| 8.18 | A plot of $\ell n I_o$ versus temperature                       | <b>2</b> 54 |

| 8.19 | The Capacitance-voltage characteristic at 295 K                 | 256         |

| 8.20 | The spectral response curve of the p-ZnTe/i-CdTe/n-GaAs         |             |

|      | diode                                                           | 256         |

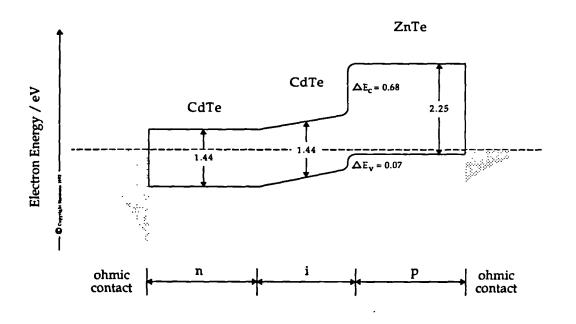

| 8.21 | The band structure diagram of the p-ZnTe/i-CdTe/n-CdTe          |             |

|      | device                                                          | 261         |

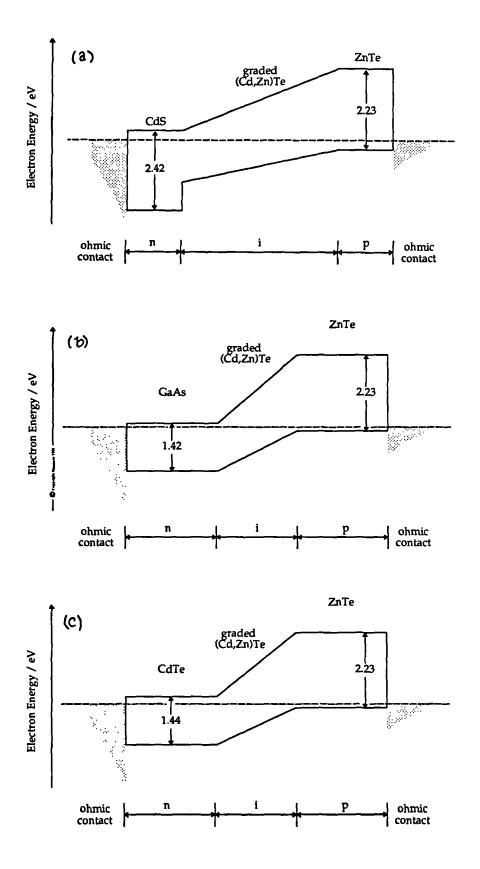

| 8.22 | The band structure diagrams for the graded $Cd_{1-x}Zn_xTe$ ab- |             |

|      | sorber layers on (a) n-CdS, (b) n-GaAs and (c) n-CdTe sub-      |             |

|      | strates respectively                                            | 263         |

# LIST OF TABLES

| 2.1        | Summary of fabrication techniques 40                                             |

|------------|----------------------------------------------------------------------------------|

| 2.2        | The material parameters for the compounds used in this thesis $\ldots \ldots 42$ |

| 2.3        | Current status of the n-CdS/p-CdTe solar cell                                    |

| 2.4        | Summary of p-i-n solar cells 46                                                  |

| 3.1<br>4.1 | Van der Pauw Configurations                                                      |

| 4.2<br>4.3 | Effects of various etchants on the polar faces of CdS                            |

| 4.4        | Analysis of the RHEED pattern for CdS etched in HCl/KCl 95                       |

| 4.5<br>4.6 | A summary of the polishes for GaAs substrate                                     |

| 5.1        | Comparison of Epitaxial Techniques                                               |

| 5.2        | Properties of Organometallic Precursors used in this thesis 112                  |

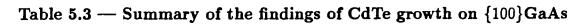

| 5.3        | Summary of the findings of CdTe growth on {100}GaAs 116                          |

| 5.4        | CdTe growth parameters 117                                                       |

| 5.5        | The results of CdTe growth optimisation                                          |

| 5.6        | The growth conditions of ZnTe epilayers on $\{100\}$ GaAs 135                    |

| 5.7        | Summary of the ZnTe growth properties 135                                        |

•

| 5.8          | Acceptor levels in p-type ZnTe and CdTe (all values are in                                                          |

|--------------|---------------------------------------------------------------------------------------------------------------------|

|              | meV)                                                                                                                |

| 5.9          | Metalorganic precursors for p-type doping of CdTe/ZnTe 143                                                          |

| 5.10         | The growth parameters for the As-doping of ZnTe 146                                                                 |

| 5.11<br>5.12 | The growth parameters for the As-doping of CdTe148Growth conditions for the CZT epilayers of varying composition151 |

| 6.1          | Dark I <sub>f</sub> -V characteristics for a diode grown on the Cd face $\dots \dots \dots 179$                     |

| 6.2<br>6.3   | The change in E <sub>r</sub> with temperature                                                                       |

| 6.4          | The change in $E_r$ with temperature                                                                                |

| 6.5          | C-V data for n-CdS/p-CdTe cell grown on Cd face 192                                                                 |

| 6.6          | C-V data for n-CdS/p-CdTe cell grown on the S face 194                                                              |

| 6.7<br>7.1   | Summary of n-CdS/p-CdTe device characteristics                                                                      |

| 7.2          | The values of S and R from the forward $I_f - V$ data 214                                                           |

| 7.3          | The analysis of the C-V data for the n-CdTe/p-ZnTe diode 220                                                        |

| 7.4<br>7.5   | A summary of the n-CdTe/p-ZnTe diode characteristics                                                                |

| 8.1          | diode                                                                                                               |

| 8.2          | ZnTe/i-CdTe/n-CdS diode                                                                                             |

| 8.3          | ZnTe/i-CdTe/n-CdS diode                                                                                             |

| 8.4          | Comparison of p-i-n devices                                                                                         |

|              | Comparison of p-i-n and p-n devices                                                                                 |

| 8.6 | Analysis of the forward I-V data for the p-ZnTe/i-CdTe/n-    |             |

|-----|--------------------------------------------------------------|-------------|

|     | GaAs device                                                  | 256         |

| 8.7 | A comparison of the p-ZnTe/i-CdTe/n-GaAs and the p-          |             |

|     | ZnTe/i-CdTe/n-CdS devices                                    | <b>2</b> 60 |

| 8.8 | Graded $Cd_{1-x}Zn_xTe$ growth procedure                     | 263         |

| 8.9 | Summary of preliminary device characteristics of novel solar |             |

|     | cell structures                                              | 265         |

| 9.1 | Summary of device parameters                                 | 271         |

| 9.2 | Suggestions for future work                                  | 273         |

-

# Chapter I

#### Introduction

As a source of energy the sun has many advantages over other coventional sources. Its energy is free, non-polluting, inexhaustible and is evenly distributed across the earth's surface. The energy from the sun which reaches the earth's surface each year is ten thousand times greater than the worlds annual production from other sources [1]. The direct conversion of this solar energy into electricity by terrestrial photovoltaic devices provides an important contribution towards meeting the increasing energy demands of the future and lessens the dependence on fossil fuels. The use of petroleum fuels is causing a number of serious problems that are degrading the global environment continually. Examples of the damage include the pollution created by burning petroleum fuels in rain, to form acid rain and the increasing  $CO_2$  concentration, exacerbating the greenhouse effect.

Despite a drop in price by nearly a factor of ten in the last decade (from  $\approx \pounds 17$ per watt in 1981 to  $\approx \pounds 2$  per watt in 1992) solar cell power is still too expensive to compete with fossil fuel and nuclear power [2]. Current trends, however indicate that during the same time period the cost of fossil fuels and nuclear power has, and is continuing to increase. Thus the major objectives of research and development programmes within the photovoltaic industry have been to improve efficiency, stability, lifetime and reduce the costs of solar cell devices. In the 1970's the solar power industry was regarded with scepticism, the nuclear industry taking a leading role. Nuclear scientists even petitioned the White House to step up the use of coal and nuclear energy as "the only hope for achieving energy independence in the foreseeable future". Alternative energy sources were believed to be "flawed by geographical and technological limitations" [3]. It was the oil crisis in the 1970's that changed the picture, causing investment in the solar cell industry which has since made impressive technological advances and has experienced dramatic price reductions. As energy prices have risen photovoltaic systems have become a competitive energy source for a variety of applications.

# 1.1 Solar Cell Devices

Initial efforts concentrated on improving the cell efficiency, thus bettering the cost to performance ratio of the photovoltaic systems. Most of the photovoltaic products developed today use single crystal silicon cells, since amorphous silicon, GaAs and polycrystalline thin films are still being perfected. Of these the GaAs cells lead the field in efficiency, but are confined to laboratory development, single crystal silicon maintaining the lead in commercial products.

The efficiency of industrial crystalline silicon solar cells ranges from 10-15%, however laboratory type cells have efficiencies exceeding 24% [4]. This efficiency gap is caused by the usage of two different qualities of silicon substrate material, and by different cell processing. Laboratory cells are often made with techniques borrowed from microelectronics technology, while industrial cells are made using high throughput non-vacuum techniques. Advances in gettering and passivation have made it possible to obtain reasonable efficiencies using lower grade materials and it is expected that the two technologies will soon coexist.

The high production costs of III-V solar cells has meant that development efforts have focussed on space and concentrator applications. If these production costs can be brought down the high efficiency potential of III-V solar cells may make them an attractive option for terrestrial flat plate applications in countries with relatively low irradiation levels. Much of the interest in GaAs is attributed to the potential for use in tandem cell structures with potential efficiencies of  $\approx 30\%$ . These structures are however, complex and employ a large number of component layers. GaAs/InGaP tandem cells of 27.3% have been reported using GaAs as the lower band gap cell which is lattice matched to the wide band gap InGaP top cell [5]. Epitaxial layers of GaAs grown directly on silicon substrates have the attractive potentiality of reducing both cost and weight of GaAs single band gap solar cells as well as enabling a III-V/Si monolithic two band gap technology. The large lattice mismatch of 4% gives rise to a large dislocation density in the epilayer but efficiencies of  $\approx 12\%$  have been reported [6].

Polycrystalline cells are made of compound semiconductors, most common of which are the so-called II-VI compounds such as CdTe and the I-III-VI compounds such as CuInSe<sub>2</sub> (CIS). Polycrystalline cells are easily and reliably produced with thin film techniques, their greatest attribute being that they can be mass produced economically. Problems remain with the deposition of photovoltaic grade material over very large areas, since processing control can only be maintained with thin film areas at best of 0.4 m<sup>2</sup>. Processing technologies are being scaled up in dimension but care is needed over control of process related parameters e.g choice of substrate, carrier concentration, grain boundaries and surface recombination which affect the efficiencies of thin films produced. The advantages of CIS technology include large area modules and the low cost production processing techniques. Single junction large area submodules (0.4 m<sup>2</sup>) with efficiencies of 9.7% have been fabricated and are expected to exceed 10% in the near future [7]. Over smaller areas, efficiencies of 14.1% have been observed [8]. Stability results taken from modules subjected to continous outdoor exposure indicate that less than 5% power loss occurs over 18 months. CIS is also being considered as a low band gap candidate for tandem photovoltaic modules, using either an advanced amorphous silicon alloy or a large band gap polycrystalline thin film material such as CuGaSe<sub>2</sub> or CuInS<sub>2</sub> to give module efficiencies of up to  $\approx 17\%$ . Despite showing promise, problems related to the reproducibility and stoichiometry of the CIS remain and the cell offers no advantages over CdTe cells (discussed in section 1.3). Not only are CIS cells less stable but they contain indium which is a rare, expensive and toxic metal.

The first amorphous silicon cells were fabricated in the early 1970's and by 1983 constituted 25% of all photovoltaic cells produced [9]. Problems with the trapping of current carrying electrons and holes within the amorphous atomic structure has however, caused a decrease in the electric current and hence cell efficiencies. When light shines on these structures the recombination of these electron-hole pairs has led to the incorporation of atomic impurities and microcracks within the atomic structure. This instability problem has been alleviated to some extent by passivating the films with hydrogen, but even these passivated layers contain voids and inhomogeneities [10]. The exact role that these light induced defects have in determining the performance and stability is still not fully resolved [11].

# **1.2** Solar Cell Applications

Once cells are produced they are generally joined to form conventional flat panels. These panels are then designed for use in either a fixed position or as mechanically moveable units that track the moving sun. Cells are fitted with condensing lenses to form concentrators which operate much as magnifying lens to condense sunlight into a highly defined dense beam. Alternatively thin film cells are cut into smaller devices to power consumer products such as calculators.

Japanese industry improved and innovated photovoltaic devices and production methods by investing large sums of money in order to end the dependence on oil. Most of the Japanese market for photovoltaic devices is in consumer electronic applications including calculators, radios, watches, battery chargers etc.. and for domestic uses such as lighting, water heating and other stand alone applications. Photovoltaic power plants were not considered feasible due to limited availability of land in Japan, but investment was encouraged in roof mounted arrays. Recent advances in this field have been to produce solar cell roofing tiles, aimed at reducing costs by eliminating solar cell frames (thought to constitute 30-40% of total product costs) [2].

Crystalline silicon photovoltaic power technologies have demonstrated highly reliable performance with very low operating and maintenance costs. A 350 kW concentrator photovoltaic power system, the largest at the time was installed in 1981 in Riyadh, Saudi Arabia to provide power to remote villages to supply energy for lighting, air conditioning, water pumping and small appliances. The source consisted of 160 concentrator arrays with the energy stored in batteries with a diesel back-up generator. Recent analysis of the performance of these arrays found an 18% degradation over 9 years resulting mainly from solder delamination rather than cell damage [12]. Recent generators such as the ARCO 1 megawatt plant in Hesperia, California have now made photovoltaics a good option for future largescale energy supply [13].

Whilst competitive with stand alone power systems such as diesel generators, photovoltaic systems are still too capital intensive to compete with utility supplied electricity or with fossil fuel boilers scaled for large industries. Small scale grid connected photovoltaic systems in residential applications are considered the most promising and cost effective way of introducing photovoltaics to wider use. Technological advances have permitted modules to be sold today that are 15-20 times less costly than they were in 1975, but this still needs to be reduced by about 2.5 times again, before they can move more convincingly into the successful multibillion dollar market [14].

## 1.3 CdTe Solar Cells

Recent advances in CdTe thin film technology are demonstrating the prospect for significant cost reduction for photovoltaic power compared to conventional crystalline silicon solar cells. This thin film technology offers excellent potential for future developments towards a high yield, low cost manufacturing process. Thin film CdTe solar cells have been produced since the 1960's when Vodakov produced a homojunction cell of 4% efficiency [15]. Since then CdTe based cells have been produced by a variety of techniques e.g precipitation, evaporation, chemical vapour deposition, spray pyrolysis, close spaced vapour transport, and screen printing and with different junctions e.g homojunction, CdTe/Cu<sub>2</sub>Te, CdTe/CdS, ZnCdS/CdTe, ITO/CdTe, and ZnO/CdTe cells.

The highest predicted theoretical efficiency of these systems lies with the CdTe/CdS heterojunction, with an efficiency of  $\approx 25\%$  [16]. The highest practical efficiency has however been 14.1% [17], whilst BP Solar are producing 0.4 m<sup>2</sup> modules with an efficiency of 10% which are stable over 18 months [16]. One of the major advantages of these cells is that they seem to suffer from significantly small degradation. Cells after 10 years of storage in an uncapsulated state have shown unimpaired device values, and additional irradiation over 4 months did not lead to any degradation [18].

In order to determine the optimum device performance of CdTe-based solar cells a fabrication technique capable of reducing defect content within the cell structure is necessary to be able to monitor device parameters in the absence of polycrystalline grain boundaries. These defects affect current-transport mechanisms across the junction and are known to severly degrade device performance. The use of metal organic vapour phase epitaxy (MOVPE) to grow epitaxial device structures allows investigation into the potential of these CdTe-based cells.

#### **1.4** The present study

The primary motivation behind the present study was to develop the various

stages of the device fabrication procedure in order to be able to make preliminary investigations into MOVPE-grown CdTe-based solar cells. Chapter 2 introduces the relevant background in CdTe based cells and discusses the general characteristics of solar cell devices. More detailed theory on current-transport mechanisms and principles of operation are also presented. The details of the experimental set-ups used for the structural and electrical characterisation of the epilayers and devices are outlined in chapter 3.

The experimental results obtained during the course of this study are contained within chapters 4 to 8; chapters 4 and 5 describing the development of the various fabrication stages in the production of MOVPE-grown devices, and chapters 6, 7 and 8 presenting preliminary device measurements. Chapter 4 discusses the methods of substrate preparation employed to obtain optimum surfaces for epitaxy. A detailed study of the effects of various chemical polishes on the substrate surfaces is also presented. Chapter 5 describes the MOVPE growth process, including the optimisation of the growth of the binaries, CdTe and ZnTe, and of the ternary,  $Cd_{1-x}Zn_xTe$ . Studies on the p-type doping of CdTe and ZnTe for incorporation in device structures is also discussed.

Chapter 6 details the electrical and optical properties of the CdS/CdTe cells grown on single crystal CdS substrates, including findings on substrate orientation, polarity and current-transport mechanisms. The results of measurements of the electrical and optical properties of n-CdTe/p-ZnTe cells are given in chapter 7. Chapter 8 decribes the results of epitaxial p-i-n structures based on n- type substrates with epitaxial i-CdTe/p-ZnTe, where the substrate was either n-CdS, n-GaAs or n-CdTe respectively. Preliminary results as to the effects of grading the i-layer are also produced and a comparison of these p-i-n devices with conventional p-n structures is discussed. Chapter 9 concludes the experimental findings indicating the major objectives achieved whilst providing suggestions for future work in the field of MOVPE-grown solar cell devices.

## 1.5 References

- [1] S247 Case Study 2, Open University, pg 5

- [2] T.Matsuoka, H. Yagi, Y. Waki, K. Houma, S. Sakai Solar cells 29(1990)361

- [3] Energy report, IEEE Spectrum(1976)18

- [4] M.A. Green 10th European Photovoltaic Solar Energy Conf. (1991) Lisbon

- [5] A van.van Geelen, P.R. Hageman, W. Gabrielse, L.J. Giling 10th European Photovoltaic Solar Energy Conf. (1991) Lisbon

- [6] M.F. Viela, A. Leycuras 10th European Photovoltaic Solar Energy Conf. Lisbon(1991)

- [7] J. Ermer, C. Fredric, J. Hummel 21st IEEE Photovoltaics Specialist Conference, Kissimmee, U.S.A May 1990

- [8] K.W. Mitchell, C. Eberspacker, J. Ermer 4th Int. Sci. Eng. Conference, Sydney, Australia 1989

- [9] M.A. Fischetti IEEE Spectrum (1984)40

- [10] M. Varecek, D. Cervinka, M. Faure, H. Curtains, A. Shah MRS Spring meeting April 1990 San Fransisco

- [11] S. Nag, J.L. Nicque, J. Arch, C. Malone, S. Fonash, C.R. Wronski 10th European Photovoltaic Solar Energy Conf. (1991) Lisbon

- [12] A.A. Salim, N.N. Eugenio Solar Cells 29(1990)1

- [13] ARCO Solar Inc., Woodlands Hills, California.

- [14] W.T. Callaghan 10th European Photovoltaic Solar Energy Conf. (1991) Lisbon

- [15] Y.A. Vodakov, G.A. Lomakina Sov. Phys. Solid State 2(1960)1

- [16] BP Solar, Solar House, Bridge Street, Leatherhead, Surrey KT22 8B2: Private Communication.

- [17] J. Skarp 10th European Photovoltaic Solar Energy Conf. Lisbon(1991)

- [18] D. Bonnet Proc. 5th Photovoltaics Specialist Conference (1983)897

## Chapter II

#### Solar cell and heterojunction theory

## 2.1 The solar cell

#### 2.1.1 The junction

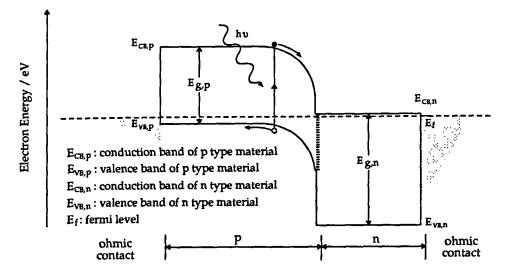

When solar radiation falls on a semiconducting material and is absorbed, electron-hole pairs are generated. The minimum energy that a photon must have to create an electron-hole pair is the band gap energy,  $E_g$  of the absorbing material. A photon with energy less than  $E_g$  cannot create these electron-hole pairs and in principle is not therefore absorbed, whilst a photon with an energy greater than  $E_g$  still contibutes only one electron-hole pair, the excess energy being wasted as heat. In order for these electron-hole pairs to contribute to a current in an external circuit they must be separated from each other. The p-n junction is ideally suited for this purpose and provides the cornerstone for photovoltaic technology. Used in this way, a p-n junction is generally referred to as a photovoltaic solar cell. Figure 2.1 describes the energy band diagram of a p-n junction heterojunction solar cell where an incoming photon has created an electron-hole pair (in this case in the p-side, close to the junction). The built-in potential at the junction has then separated the electron and hole, sweeping the electron across the barrier into the n-side, while repelling the hole.

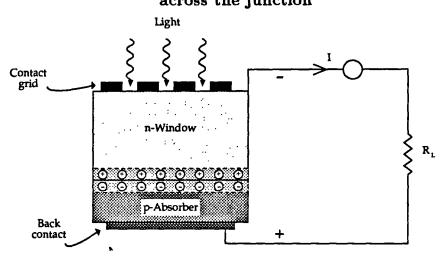

Figure 2.2 illustrates one type of schematic diagram for a p-n junction solar cell, comprising of a top "window" layer, generally a semiconductor with a large band gap through which the light can pass to the absorber layer to create electronhole pairs. A contact grid structure is applied to the window layer and the absorber layer is covered by another contact, both of which are ohmic. If the incident light passes though a grid on the larger band gap window layer it is termed "backwall illumination", but if the illumination occurs through the absorber layer it is called "frontwall illumination".

Figure 2.1 — Energy band diagram of a p-n heterojunction solar cell illustrating how the electron hole pair is separated by the internal field across the junction

Figure 2.2 — A schematic diagram of a heterojunction solar cell

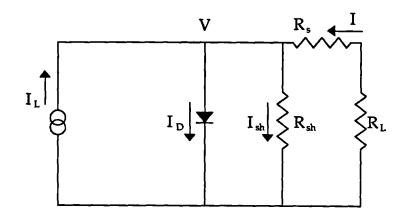

Figure 2.3 — The equivalent circuit for a solar cell

Various electronic processes occur within the solar cell, and these can be divided into 6 separate regions existing within the device itself.

(1) the metal contact to the absorbing (in this case the p-type) semiconductor, introducing a contact resistance.

(2) the bulk of the absorber region where electron-hole pairs are generated by the absorption of light and where the minority carriers are transported by diffusion to the junction and partially lost by recombination.

(3) the junction region itself where interface states arising from the difference in the lattice parameters of the two materials leads to recombination. Across the junction is the built-in electric field which separates the carriers.

(4) the bulk (n-type) window layer which, although essential to the operation of the cell nevertheless, constitutes added internal resistance.

(5) the contact to the n-type semiconductor introducing a second contact resistance and

(6) the front surface, where surface recombination loss of minority carriers can occur.

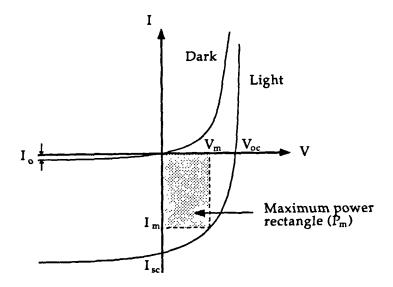

The corresponding equivalent circuit for such a solar cell device under illumination is shown in figure 2.3. The p-n junction (assumed to be ideal) is in parallel with a light dependent current generator,  $I_L$ , and a resistance,  $R_{sh}$ . The current to the external load,  $R_L$ , encounters an internal series resistance,  $R_s$  and is given by

$$I_L - I_D - I_{sh} + I = 0 [2.1]$$

These loss mechanisms can be lumped together in an electrical equivalent circuit as shunt and series resistive elements.

$$I_D = I_o \left\{ exp \left[ \frac{q(V - IR_s)}{nkT} \right] - 1 \right\}$$

[2.2]

$$I_{sh} = \frac{V - IR_s}{R_{sh}}$$

[2.3]

Thus combining equations 2.2 and 2.3 gives

$$I = I_{o} \left\{ exp \left[ \frac{q(V - IR_{s})}{nkT} \right] - 1 \right\} + \frac{V - IR_{s}}{R_{sh}} - I_{L} \qquad [2.4]$$

The shunt resistance,  $R_{sh}$  accounts for all leakage currents such as those associated with localised states near the interface of the heterojunction and within the junction itself, that act as additional recombination pathways. The series resistance element represents internal resistive and dissipative losses such as bulk and contact resistances. The equivalent circuit response can also be considered as consisting of two diodes rather than one. As the temperature of the device changes, the dark I-V behaviour can be dominated by either space-charge recombination (one diode) or by a tunneling mechanism (the other diode). For an ideal cell,  $I_o$ and n are not functions of illumination and any parallel shunting resistance across the junction is effectively infinite.

In choosing the semiconductors for a solar cell application there are a number of material parameters that need to be considered, including the band gap, absorption coefficient, diffusion lengths, minority carrier lifetimes, doping, lattice parameters and surface recombination states. These parameters are discussed in detail below.

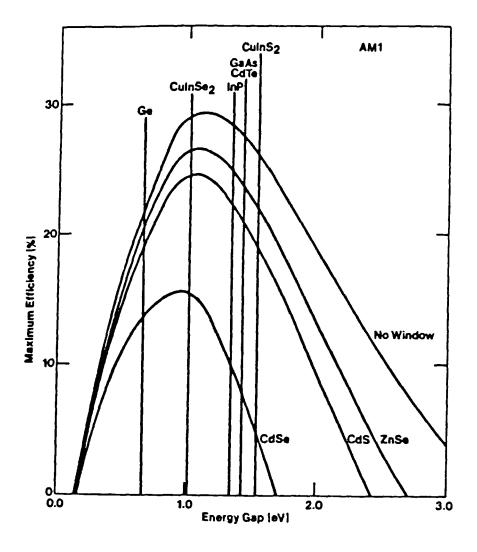

As the band gap of the absorbing region increases the diode parameter, I<sub>o</sub> decreases strongly which in turn increases the voltage obtainable from the cell. Increasing the band gap however, also decreases the photogenerated current available since a smaller fraction of the solar spectrum is absorbed. The compromise between these two effects produces a maximum in the solar efficiency at band gap energies of 1.4-1.5 eV, as illustrated in figure 2.4. The window layer should be a large band gap semiconductor that does not absorb any significant proportion of the incident photons, whilst forming the junction that yields the photovoltaic effect. For solar cell applications, the thickness of the absorber layer required to absorb all the photons incident at its surface is given by approximately  $\frac{1}{\alpha}$  [1], where  $\alpha$  is the absorption coefficient of the absorber material. Direct band gap semiconductors have higher absorption coefficients and as such thinner layers are necessary for the absorption of the same number of photons than with indirect semiconductor.

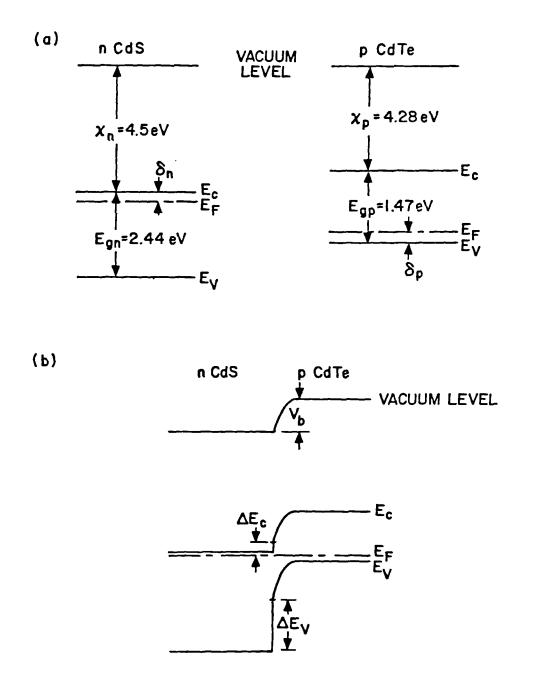

Figure 2.4 — Theoretical efficiencies of heterojunction solar cells as a function of energy gap for various absorber and window materials [1].

ultimately reduces the material costs and, as such, is favourable in the fabrication processes of solar cell devices.

Electron-hole pairs generated in the junction region are immediately separated by the built-in field. However, electron-hole pairs generated outside the depletion region have to be able to move across the absorption region to the junction, any that recombine before this stage do not contribute to the photocurrent. The minority carriers rely on diffusion to reach the junction and thus the minority carrier diffusion length, L (i.e the length the minority carriers are able to diffuse before recombining) is an important parameter in determining collection efficiency. This diffusion length is dependent on the crystallinity, defect content, and stoichiometry of the material involved. Similarly, large values of minority carrier lifetimes are desirable for efficient devices and the presence of a high density of localised states or deep impurity levels is known to seriously reduce these lifetimes. The lattice parameter mismatch between the two different semiconductors can lead to the formation of misfit dislocations and interface states. These act as recombination centers, again reducing the photogenerated current reaching the junction. The source of these interface states created in the MOVPE growth of semiconductors is discussed in section 2.1.5

The incorporation of dopants has a profound effect on the absorption coefficient, diffusion length and energy band gap [2]. In order to obtain a high photovoltage high levels of doping are required, however excessive doping can lead to smaller lifetimes. Again a compromise has to be reached to ascertain the optimum doping levels within the device. Another less obvious problem that affects the solar efficiency is the surface states on the window material. Surface states arise from dangling bonds, oxide layers and chemical residues that lead to recombination of carriers thus limiting the cell performance. This results in an increase in contact resistance and various passivation techniques have been developed to minimise these losses [3].

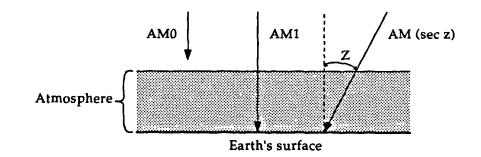

#### 2.1.2 The solar spectrum

# Figure 2.5 — Effect of the Solar Zenith Angle on Insolation at the surface of the Earth

The solar efficiency of a photovoltaic system depends critically on the spectral distribution arising at the surface from the earths atmosphere, which depends not only on the composition of the atmosphere but the path length of the radiation through the atmosphere. Factors such as the water content, turbidity, ozone content, cloudiness, haziness, and ground reflections all affect the solar radiation reaching the Earth's surface. Another important parameter is the Sun's declination angle which varies the path length through the atmosphere. This geometric effect is described by specifying a zenith angle of the sun, z, the angle between the earth-sun radius and the normal to the Earth's surface, as illustrated in figure 2.5. The path length through the atmosphere is described in terms of an equivalent air mass,  $m_r$ . Thus specific solar spectra are labelled AMm<sub>r</sub>, with AM0 corresponding to the solar spectrum at the outer edge of the Earth's atmosphere, AM1 to that at the Earth's surface for normal incidence and AMm<sub>r</sub> is at the Earth's surface with  $m_r$ =sec z, i.e the deviation from normal incidence. All solar cells are tested under one of these standard air mass conditions for comparative purposes and the AM1.5 spectrum representing the sun at 45° to the zenith, with an incident power of  $\approx 875$  Wm<sup>-2</sup>, is used for this thesis.