# **Durham E-Theses**

# Operation of Grid-Connected Inverter under Unbalanced Grid Conditions Using Indirect Voltage Sensoring

HAO, TIANQU

#### How to cite:

HAO, TIANQU (2016) Operation of Grid-Connected Inverter under Unbalanced Grid Conditions Using Indirect Voltage Sensoring, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/11799/

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- ullet a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

# Operation of Grid-Connected Inverter under Unbalanced Grid Conditions Using Indirect Voltage Sensoring

# Tianqu Hao

A Thesis presented for the degree of Doctor of Philosophy

School of Engineering and Computer Sciences

Durham University

United Kingdom

May 2016

## **Declaration**

No part of this thesis has been submitted elsewhere for any other degree or qualification and it is all my own work unless referenced to the contrary in the text.

# Copyright © 2016 by Tianqu Hao

"The copyright of this thesis rests with the author. No quotations from it should be published without the author's prior written consent and information derived from it should be acknowledged".

# Acknowledgements

By the end of the long running towards the PhD degree, I shall say thank you, first to my supervisor Professor Li Ran. Thank you for your patience and guidance throughout the years I have spent in the UK. Thank you for continuing working with me after you moved to University of Warwick. Thank you for taking care of me when I was sick in bed. Thank you, my best teacher and dearest friend.

Thank you to Professor Feng Gao for his precious advices and encouragement.

I would thank my supervisor in Durham University Doctor Christopher Crabtree for his help on the communication and administration with Durham University during the last two years when I am based in Coventry. I also owe my thanks to Professor Phil Mawby and other fellow researchers of University of Warwick. Thank you for accepting me and allowing me to share the research facilities. Special thanks to my friends Han Qin, Ruizhu Wu and Yuan Tang. Thank you for your company during the time spent in the lab.

Last but most importantly, thank you to my family. Thank you for the endless support. Thank you mom, for listening to me no matter I am cheering or shouting or crying. Thank you for enduring my short temper, yet taking away all my negative emotion. Without your support, I shall never make it here. Thank you my wife, I shall return to you soon. Thank you dad, I understand your best wish and wordless support. And thank you my daughter for smiling to me for the first time you are in my arms, even I was late for three days for your birth. I love you my angel.

#### **Abstract**

The grid connected voltage source inverter is now the most widely used interface for connecting renewable power generation to the grid. Control of this device is a key aspect to ensure the performance, reliability and life span of the renewable power generation system.

Conventionally, the current control of the grid connected inverter is based on the measured grid side voltage. The power and the power factor at the receiving end, which is usually defined as the point of common coupling, can be controlled accurately. This controller topology has been widely used and many control methods have been developed aiming at objectives such as increasing system stability, decreasing harmonic injection, and improving transient response of the system. However, in case of the voltage measurement is not available, i.e. a faulty voltage sensor, the conventional current control topology will be disabled for lack of information of the grid voltage. This would decrease the reliability and efficiency of the system thus should be improved.

voltage-sensor-less In this research, a current control system for the grid connected inverter system not relying on the information provided by the a.c. side voltage sensors will be developed with compliance to the recommendations issued to the performances of the distribution generations such as the harmonic limitations and the fault-ride-through capabilities. Three problem will be addressed and solved.

Firstly, the a.c. side voltage should be acquired without the use of a.c. side voltage sensors. This is achieved by adopting an a.c. side voltage estimation algorithm. Secondly, the grid connected inverter should be able to start-up without synchronising to the grid while keep the current injected in a safe range. This is achieved by the newly designed start-up process. Thirdly, the grid connected inverter should be able to ride-through grid faults and providing

support to the grid. The transient response of the grid connected inverter is the key measure to define the performance. In this study, a faster symmetrical component decomposition method is proposed to improve the transient response of the current control, without relying on grid voltage sensors.

The proposed system is verified by both simulation and experimental tests, with analyses and insight aiming at general applications of the proposed method and algorithms.

# Contents

| List o | of Figures                                                               | .VIII  |

|--------|--------------------------------------------------------------------------|--------|

| Nom    | nenclature                                                               | . XIII |

| List o | of Abbreviation                                                          | XIV    |

| Chap   | oter 1 Introduction                                                      | 1      |

|        | 1.1 Motivation of the research                                           | 1      |

|        | 1.2 Technical challenges                                                 | 3      |

|        | 1.3 Compliance to grid code                                              | 7      |

|        | 1.3.1 Harmonic limits                                                    | 8      |

|        | 1.3.2 Requirements during normal operation                               | 9      |

|        | 1.3.3 Fault-ride-through capability                                      | 11     |

|        | 1.3.4 Standalone mode                                                    | 13     |

|        | 1.3.5 Cost effectiveness and reliability issue of distributed generation | 14     |

|        | 1.4 Project Objectives                                                   | 16     |

|        | 1.5 Main Contributions of the Study                                      | 18     |

| Chap   | oter 2 Current Control of Voltage Source Converter                       | 20     |

|        | 2.1 Introduction                                                         | 20     |

|        | 2.2 None-linear current control: hysteresis control                      | 21     |

|        | 2.3 Linear current control methods                                       | 25     |

|        | 2.3.1 Ramp comparison current control                                    | 25     |

|        | 2.3.2 Dq-decoupled current control                                       | 27     |

|        | 2.3.3 Proportional-resonant current control                              | 31     |

|        | 2.3.4 Harmonic reduction                                                 | 32     |

|        | 2.4 Chapter Summary                                                      | 33     |

| Chap   | oter 3 Grid Synchronisation Techniques for Grid Connected Inverter       | 35     |

|        | 3.1 Introduction                                                         | 35     |

|        | 3.2 Grid synchronisation methods                                         | 36     |

|        | 3.3 Decoupled double synchronous reference frame phase locked loop       | 45     |

|        | 3.4 Cascaded delay method                                                | 47     |

|        | 3.5 Notch-filtering method                                               | 50     |

|        | 3.6 A new decomposing method proposed in this study                      | 55     |

| Cha | ter 4 Technical challenges to the grid connected converter system                                    | 52        |

|-----|------------------------------------------------------------------------------------------------------|-----------|

|     | 4.1 Voltage dips and phase jump                                                                      | <b>52</b> |

|     | 4.2 Current control objectives of VSI under different constraints                                    | 56        |

|     | 4.3 Voltage oriented current control and comparison                                                  | 71        |

|     | 4.4 Weak Grid Characteristic                                                                         | 72        |

|     | 4.5 Sensor reduction and sensor-less control                                                         | 73        |

|     | 4.6 Chapter summary                                                                                  | 75        |

| Cha | ter 5 Control System Design                                                                          | 76        |

|     | 5.1 Introduction                                                                                     | 76        |

|     | 5.2 Current controller                                                                               | 77        |

|     | 5.2.1 SRF-PI based dq decoupled current control                                                      | 78        |

|     | 5.2.2 Effect of symmetrical component decomposition of the current signals to the current control    |           |

|     | 5.2.3 Performance of SRF-PI based dq-decoupled current control under variation of grid impedance     | 90        |

|     | 5.2.4 Performance of SRF-PI based dq-decoupled current control under variation of the grid frequency | 99        |

|     | 5.2.5 Performance of the SRF-PI based dq-decoupled current control with voltage feed-forward delay10 | 03        |

|     | 5.3 Grid voltage observer10                                                                          | 06        |

|     | 5.4 A.c. voltage-sensor-less current control10                                                       | 09        |

|     | 5.5 Chapter summary1                                                                                 | 15        |

| Cha | ter 6 D.C. Bus Voltage Control and Initial Synchronisation to the Grid1                              | 17        |

|     | 6.1 Introduction1                                                                                    | 17        |

|     | 6.2 D.c. bus voltage control and capacitor design1                                                   | 17        |

|     | 6.2.1 D.c. natural voltage variation1                                                                | 18        |

|     | 6.2.2 D.c. natured voltage controller design12                                                       | 21        |

|     | 6.2.3 A.c. natural voltage variation1                                                                | 25        |

|     | 6.3 Initial transient ride through with ensured safety of the power modules1                         | 28        |

|     | 6.3.1 Current hysteresis control                                                                     | 28        |

|     | 6.3.2 Tuning of the hysteresis control, hysteresis band design                                       | 29        |

|     | 6.3.3 Voltage estimation                                                                             | 34        |

| 6.4 Chapter summary                                                                            | 135 |

|------------------------------------------------------------------------------------------------|-----|

| Chapter 7 Simulation Study of A.C. Voltage-sensor-less Control System and Simulation Results . | 136 |

| 7.1 Proposed symmetrical component decomposition                                               | 136 |

| 7.2 System initialization and start up                                                         | 140 |

| 7.3 d.c. bus voltage control simulation                                                        | 147 |

| 7.4 Power control behaviour and transient of the a.c. voltage-sensor-less control              | 148 |

| 7.5 Inverter operation under unbalanced grid voltage                                           | 159 |

| 7.6 Chapter summary                                                                            | 166 |

| Chapter 8 Experiment Set-up and Experimental Result Analysis                                   | 167 |

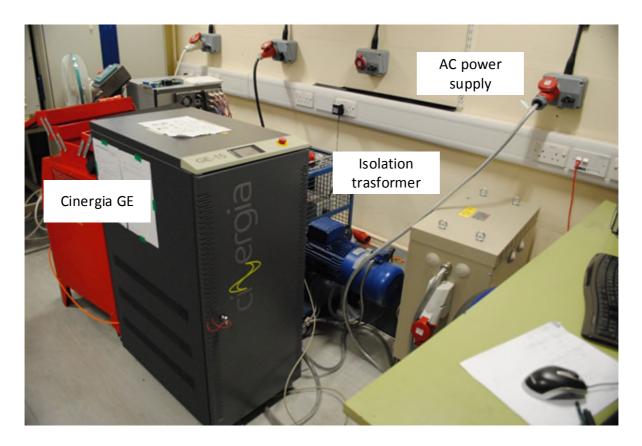

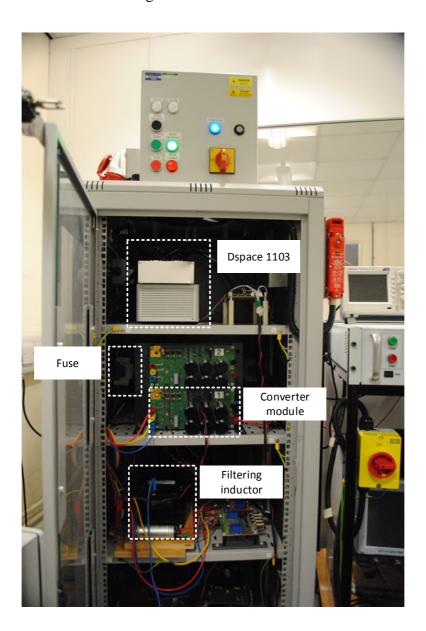

| 8.1 Experimental test rig set up                                                               | 167 |

| 8.2 Experiment results                                                                         | 170 |

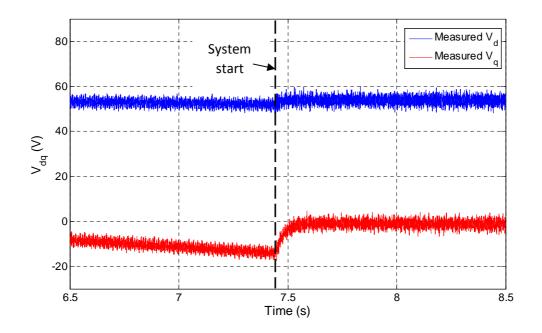

| 8.2.1 Start-up and initial synchronisation                                                     | 170 |

| 8.2.2 A.c. voltage-sensor-less current control under balanced grid voltage                     | 174 |

| 8.2.3 Unbalanced grid voltage                                                                  | 182 |

| 8.3 Chapter summary                                                                            | 189 |

| Chapter 9 Conclusion and Future Work                                                           | 191 |

| 9.1 Conclusions                                                                                | 191 |

| 9.2 Future work                                                                                | 194 |

| Reference                                                                                      | 195 |

| Publications                                                                                   | 214 |

# **List of Figures**

| Figure 1.1 Carbon footprint of electricity generation                                            | 1  |

|--------------------------------------------------------------------------------------------------|----|

| Figure 1.2 General layout of renewable generation system                                         | 3  |

| Figure 1.3. Controller block diagram of a grid connected VSC with internal current control       | 6  |

| Figure 1.4. Grid code requirement for wind farm output during frequency variation                | 9  |

| Figure 1.5. Wind farm active power output under frequency variation                              | 10 |

| Figure 1.6 Grid code requirement for wind generation supporting the grid during grid faults      | 11 |

| Figure 1.7 Normalised overall failure rates of sub-systems and assemblies of wind                |    |

| turbines of multiple manufacturers                                                               | 14 |

| Figure 2.1 Circuit diagram of a two-level single-phase inverter                                  | 20 |

| Figure 2.2 Illustration of current hysteresis control                                            | 21 |

| Figure 2.3 System diagram of ramp comparison current control                                     | 24 |

| Figure 2.4 Tracking error of the ramp comparison current control                                 | 25 |

| Figure 2.5 Dq-decoupled current controller structure                                             | 26 |

| Figure 2.6 Simulation result of $dq$ -decoupled current control tracking constant $dq$ reference | 27 |

| Figure 2.7 Tracking error of $dq$ -decoupled current control tracking sinusoidal $dq$ reference  | 27 |

| Figure 2.8 Sinusoidal dq reference                                                               | 28 |

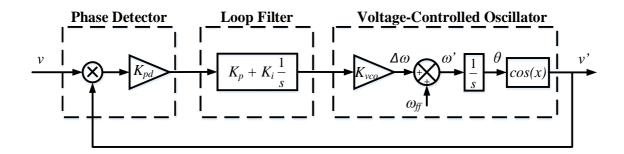

| Figure 3.1 Block diagram of a basic phase-locked-loop                                            | 35 |

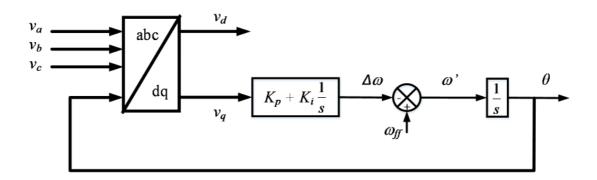

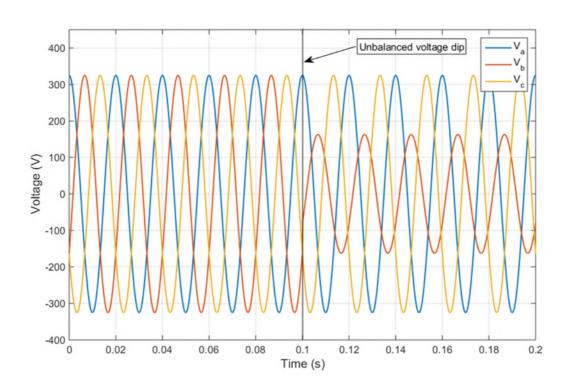

| Figure 3.2 Block diagram of the SRF-PLL for three phase system                                   | 36 |

| Figure 3.3 Block diagram of SRF-PLL small signal model                                           | 36 |

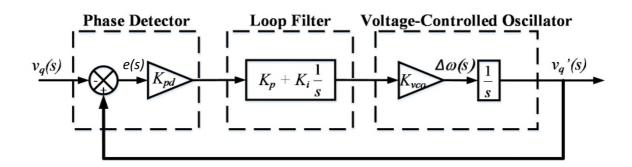

| Figure 3.4 Transient response of the SRF-PLL to phase jump with parameters set to produce        |    |

| critical-damping, over-damping and under-damping following a small signal model (a) three-       |    |

| phase voltage waveform; (b) response of $V_d$ estimation; (c) response of $V_q$ estimation       | 39 |

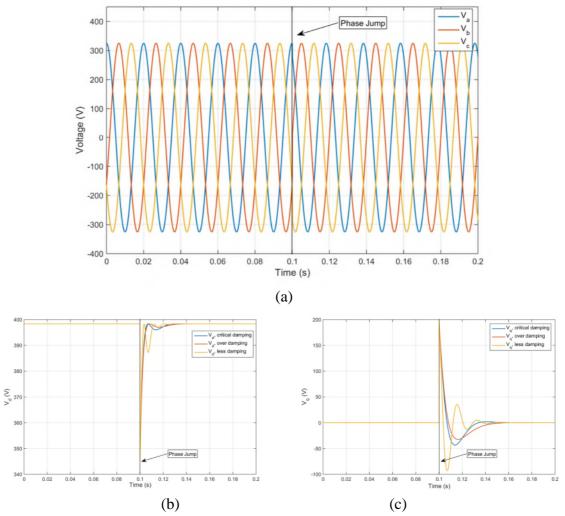

| Figure 3.5 Three phase voltage during single phase voltage dip                                   | 41 |

| Figure 3.6 Output of the SRF-PLL during single-phase voltage dip and tracking error: (a)         |    |

| Phase A output and actual value; (b) Phase B output and actual value; (c) Phase C output and     |    |

| actual value; (d) dq values                                                                      | 42 |

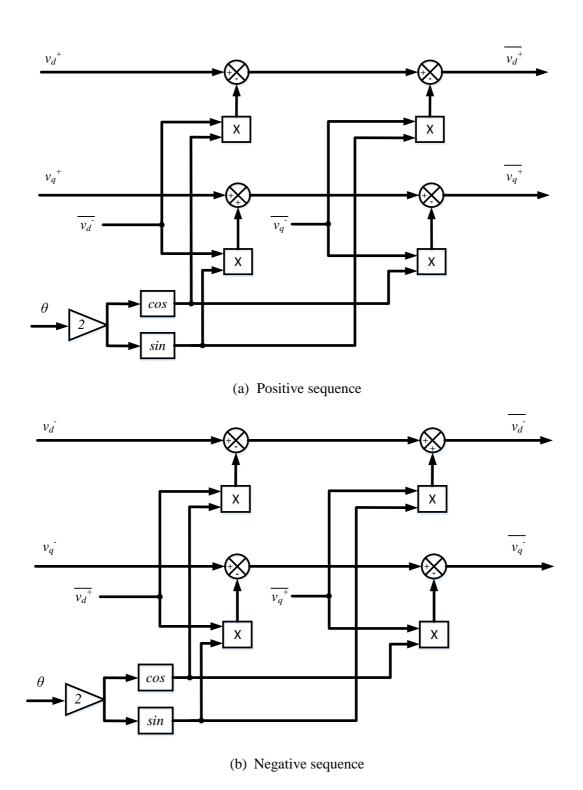

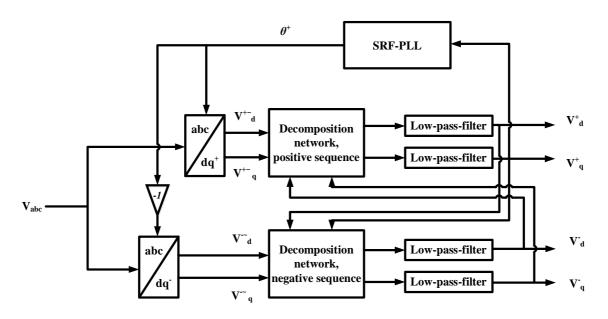

| Figure 3.7 Decomposition network of DD PLL: (a) positive sequence; (b) Negative sequence         | 44 |

| Figure 3.8 Close loop diagram of DD PLL                                                          | 45 |

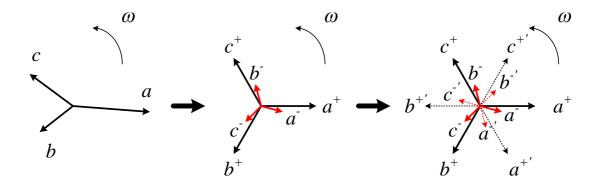

| Figure 3.9 Unbalanced three phase signals and the vector placement of the symmetrical            |    |

| components before and after applying 1/6 fundamental period delay                                | 46 |

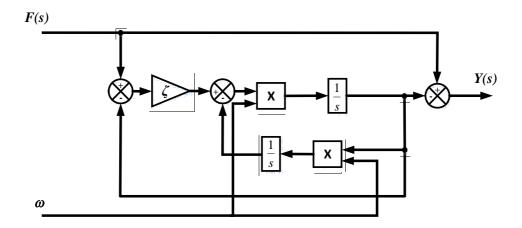

| Figure 3.10 Block diagram of frequency adaptive notch filter                                     | 51 |

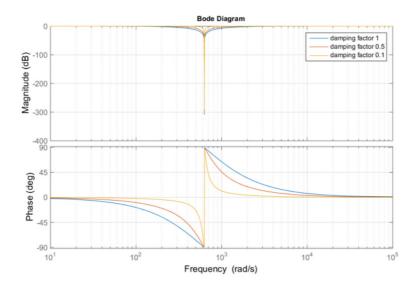

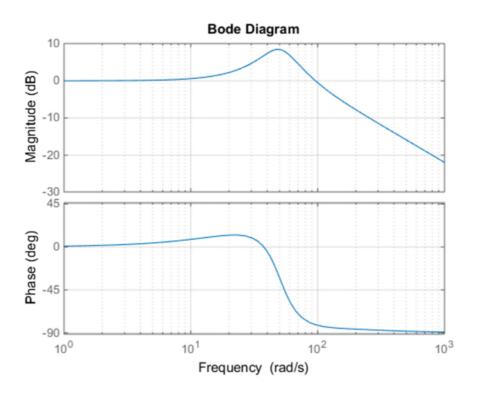

| Figure 3.11 Bode diagram of the notch filter                                               | 51  |

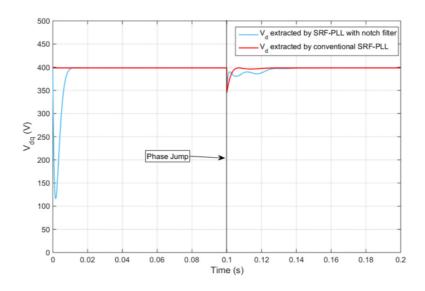

|--------------------------------------------------------------------------------------------|-----|

| Figure 3.12 Effect of delay caused by notch filter responding to a phase jump              | 52  |

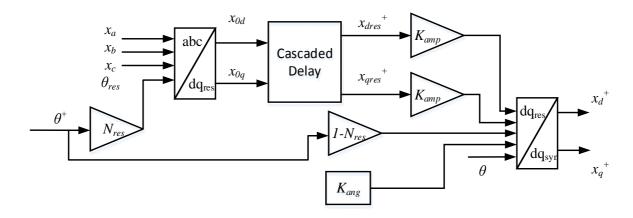

| Figure 3.13 Proposed decomposing system for extracting the positive sequence signal        |     |

|                                                                                            |     |

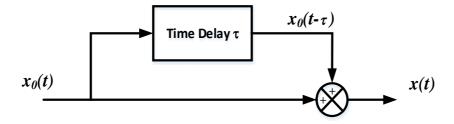

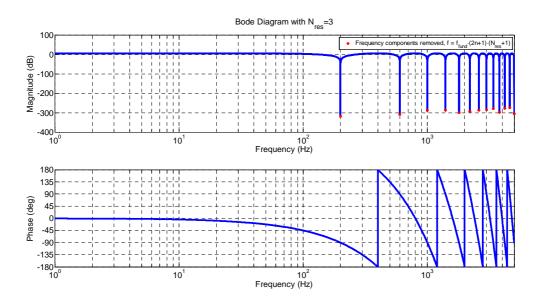

| Figure 3.14 Structure of cascaded delay unit                                               |     |

| Figure 3.15 Bode diagram of cascaded delay unit                                            |     |

| Figure 4.1 Unbalanced three phase voltage                                                  |     |

| Figure 4.2 Current waveform of (a) balanced power, (b) balanced current                    |     |

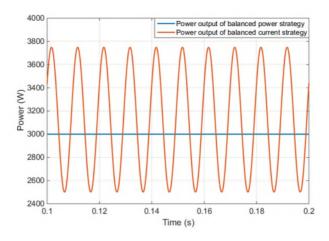

| Figure 4.3 Comparison of power output of different current control strategies              |     |

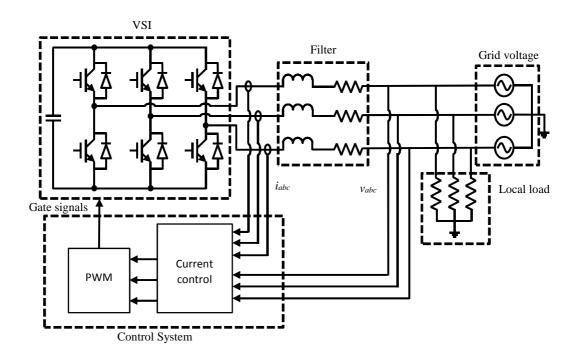

| Figure 5.1. Three phase VSI under study                                                    |     |

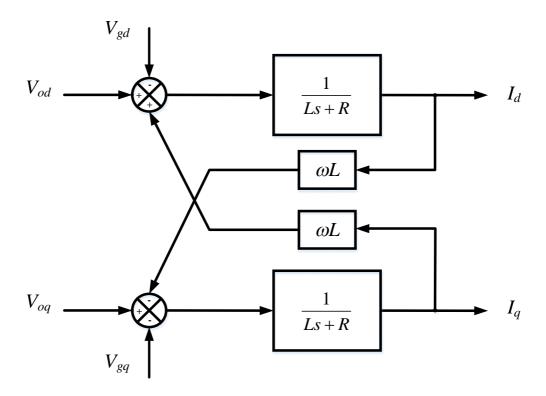

| Figure 5.2. Equivalent model of filtering inductor on <i>dq</i> reference frame            |     |

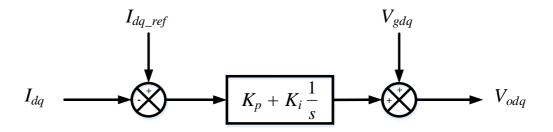

| Figure 5.3 Primary SRF-PI based current control                                            |     |

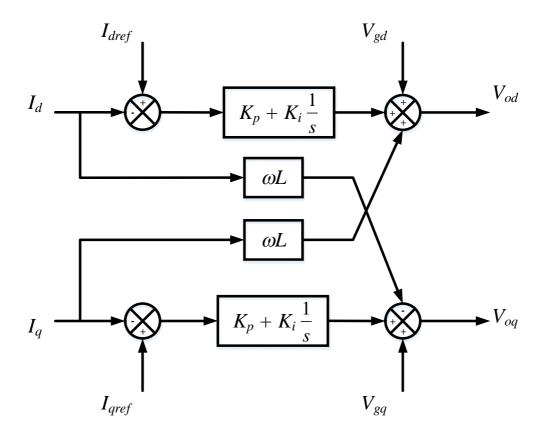

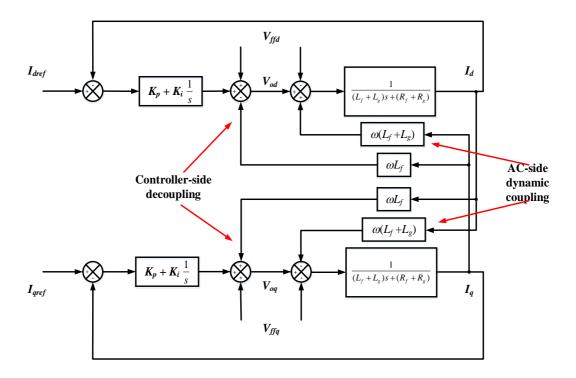

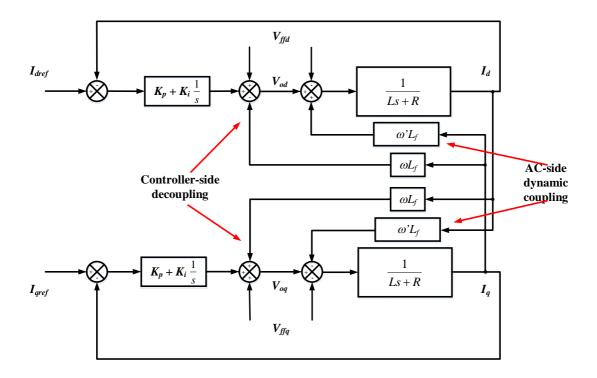

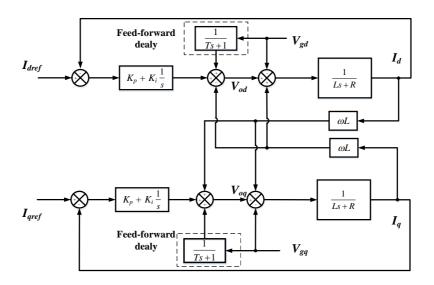

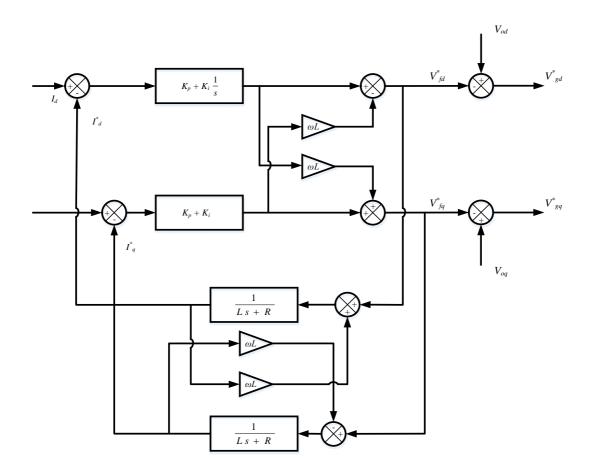

| Figure 5.4 SRF-PI based <i>dq</i> -decoupled current control                               | 80  |

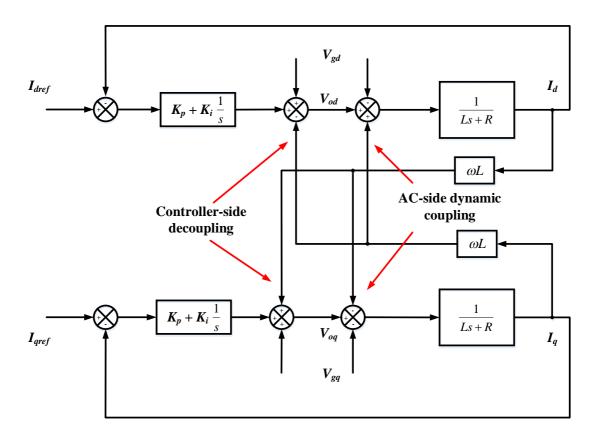

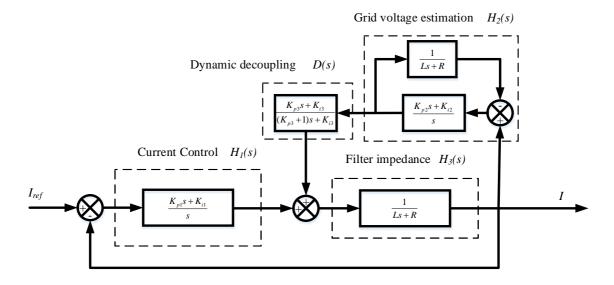

| Figure 5.5. Block diagram of VSI control system and the grid side                          | 81  |

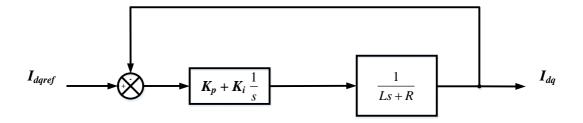

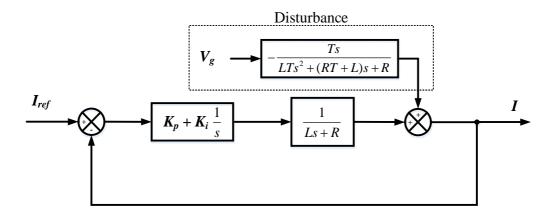

| Figure 5.6. Simplified block diagram of the system under study                             | 82  |

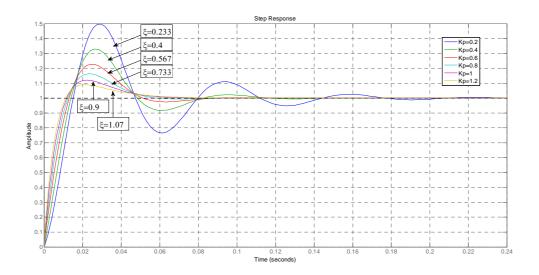

| Figure 5.7. Unit step response of the $dq$ -decoupled current control                      | 84  |

| Figure 5.8 Block diagram of the current control system with feed-back delay                | 86  |

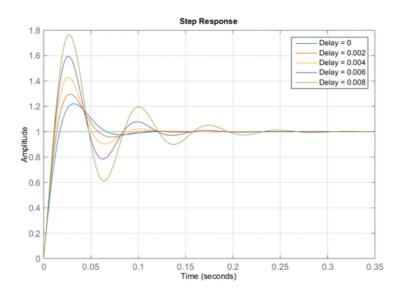

| Figure 5.9. Unit step response of the system under different feedback delay                | 87  |

| Figure 5.10 System under inaccurate dq decoupling                                          | 89  |

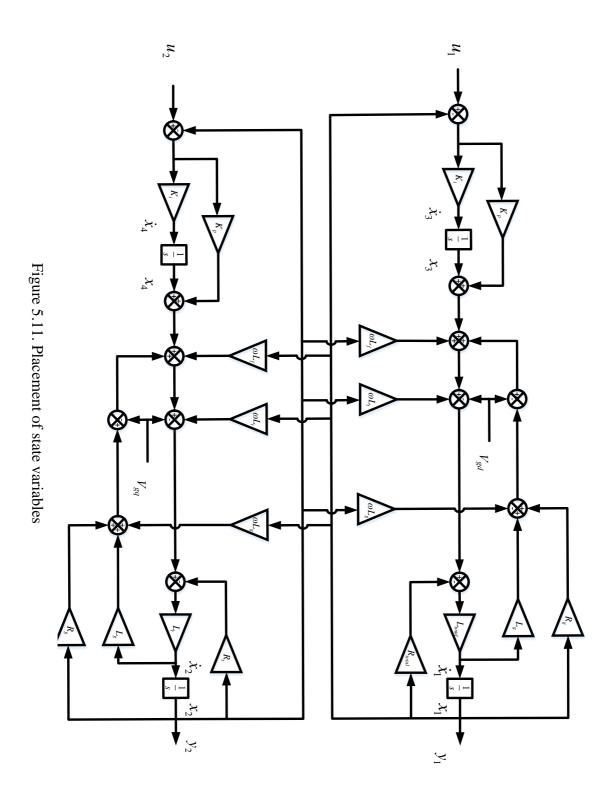

| Figure 5.11. Placement of state variables                                                  | 92  |

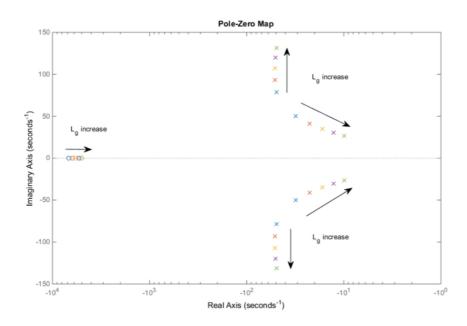

| Figure 5.12. Pole-zero map of the system under study with increasing $L_g$                 | 94  |

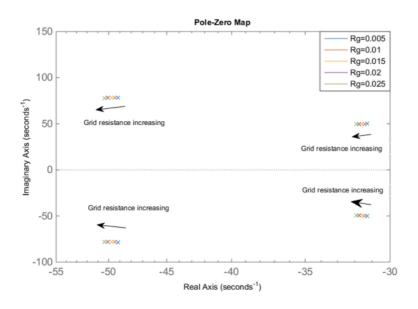

| Figure 5.13 Pole-zero map of the system under study with increasing $R_g$                  | 94  |

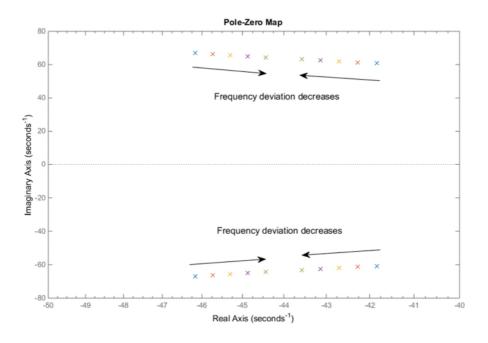

| Figure 5.14 Pole and zero placing under different grid frequency                           | 97  |

| Figure 5.15 Pole and zero placing under different grid frequency                           | 98  |

| Figure 5.14. Block diagram of the system under grid voltage feed-forward delay             | 100 |

| Figure 5.15. Small signal model of the system under study                                  | 101 |

| Figure 5.16. Block diagram of proposed voltage observer                                    | 103 |

| Figure 5.17. Small signal model of the voltage estimation system                           | 104 |

| Figure 5.18 Diagram of the dynamic decoupling stage                                        | 106 |

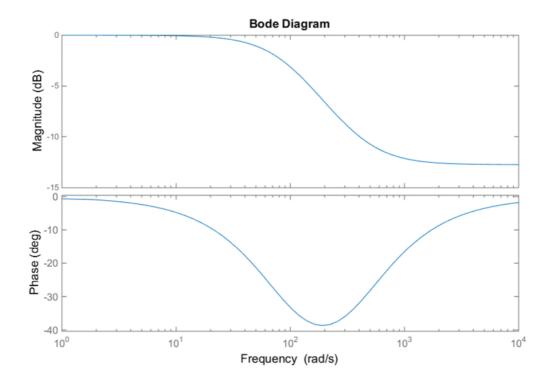

| Figure 5.19 Bode diagram showing the low-pass character of dynamic decoupling stage        | 107 |

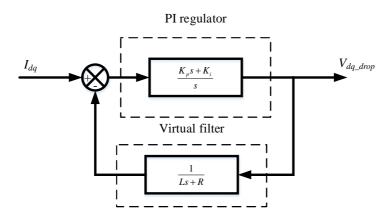

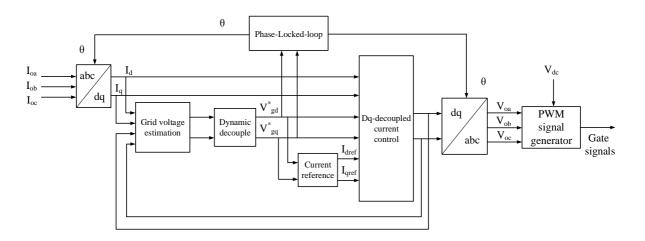

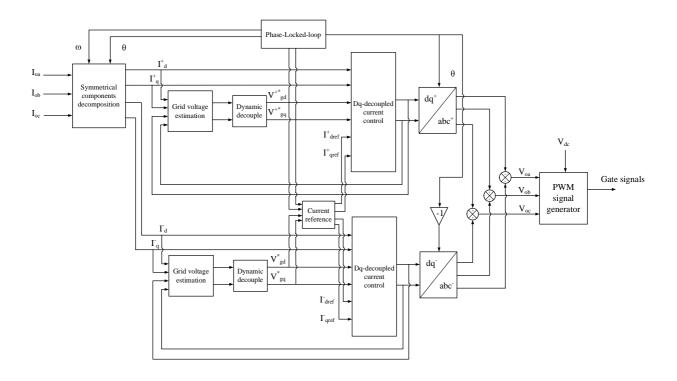

| Figure 5.20 Block diagram of the basic a.c. voltage-sensor-less current controller         | 107 |

| Figure 5.21 Block diagram of small signal model of the a.c. voltage-sensor-less controller | 108 |

| Figure 5.22 Bode diagram of the closed-loop system.                                        | 109 |

| Figure 5.23 Diagram of a.c. voltage-sensor-less current controller for riding through                    |     |

|----------------------------------------------------------------------------------------------------------|-----|

| unbalanced grid fault                                                                                    | 111 |

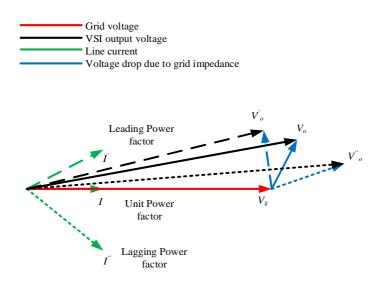

| Figure 6.1. Phasor diagram, output voltage under different power factors                                 | 115 |

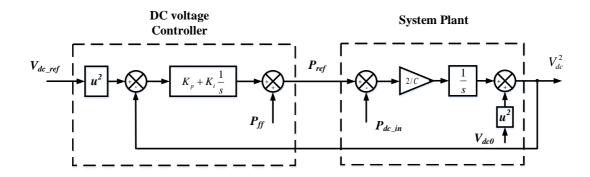

| Figure 6.2. d.c. voltage control, open-loop approach, closed-loop diagram                                | 118 |

| Figure 6.3. d.c. voltage control loop taken dynamic of the current control into consideration            | 118 |

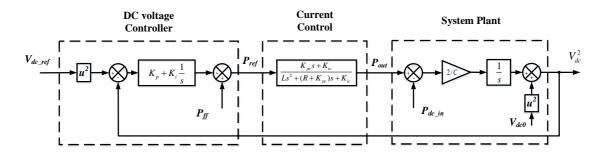

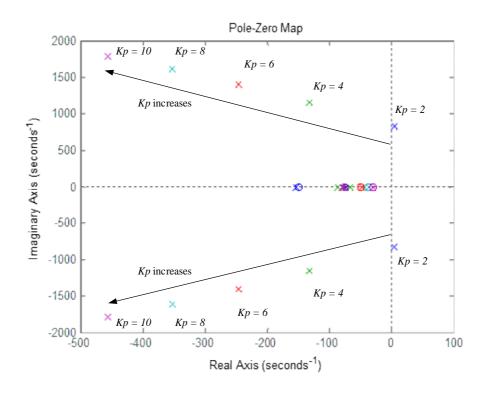

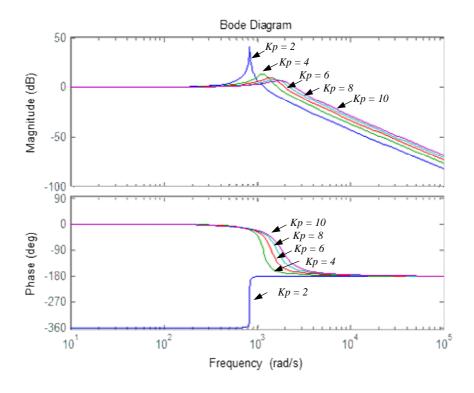

| Figure 6.4: Pole-zero map of the system under study                                                      | 120 |

| Figure 6.5: Bode plot of the system under study                                                          | 120 |

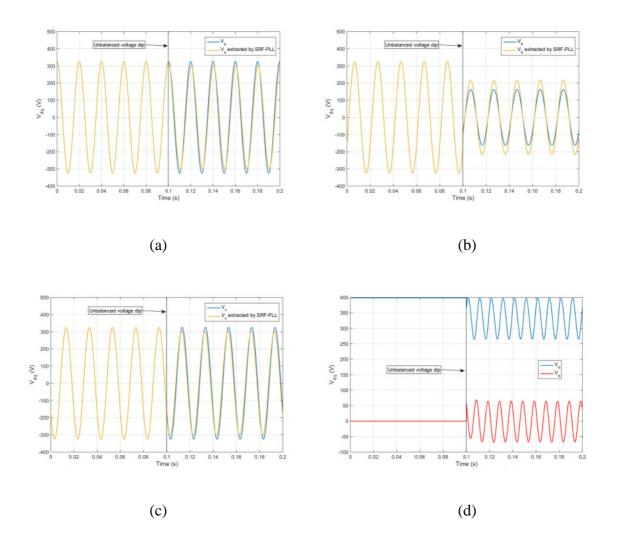

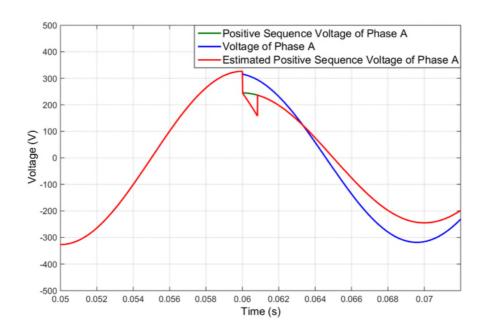

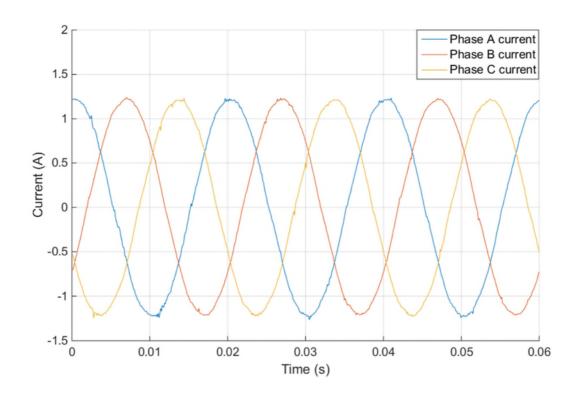

| Figure 7.1 Sinusoidal signal of positive sequence extracted by proposed symmetrical                      |     |

| components decomposition network with $N_{res}$ =21                                                      | 132 |

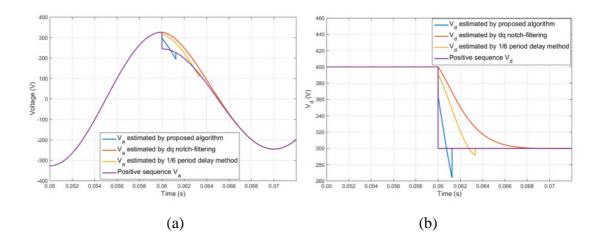

| Figure 7.2 Comparison of transient between the proposed and other algorithms                             | 133 |

| Figure 7.3 Comparison of transient of the estimated positive sequence between different $N_{res}$ :      |     |

| (a) a.c. value; (b) $dq$ value                                                                           | 133 |

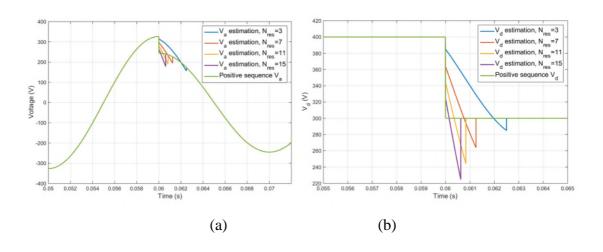

| Figure. 7.4 IAE of $V_d$ and $V_q$ during transient caused by 1 p.u. step change of: (a) $V_d$ of        |     |

| positive sequence; (b) $V_q$ of positive sequence; (c) $V_d$ of negative sequence; (d) $V_q$ of negative |     |

| sequence                                                                                                 | 134 |

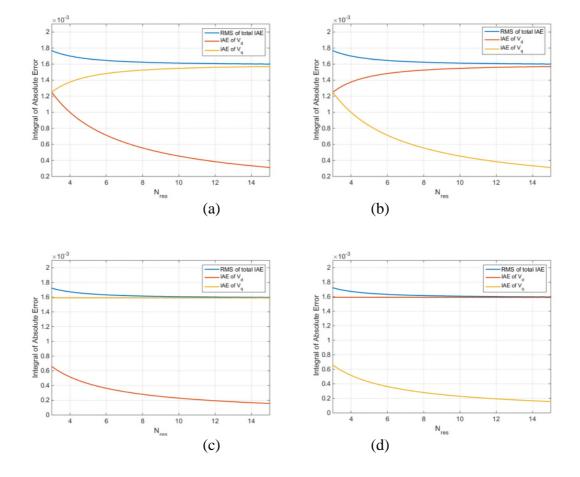

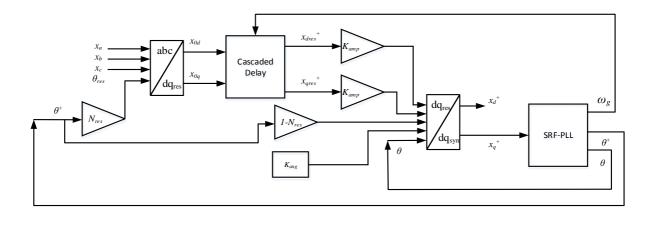

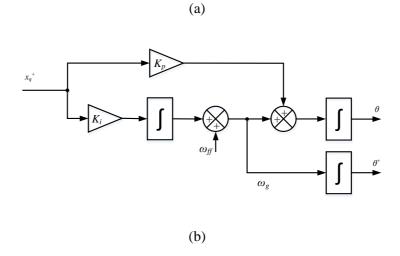

| Figure 7.5 (a) Structure of symmetrical component decomposition system with PLL to track                 |     |

| positive sequence signal; (b) structure of SRF-PLL                                                       | 135 |

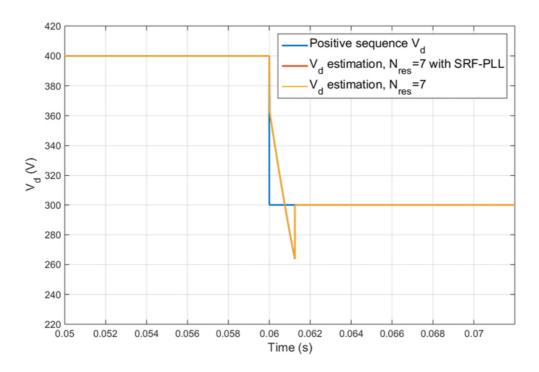

| Figure 7.6 Effect of SRF-PLL dynamics on decomposition output                                            | 136 |

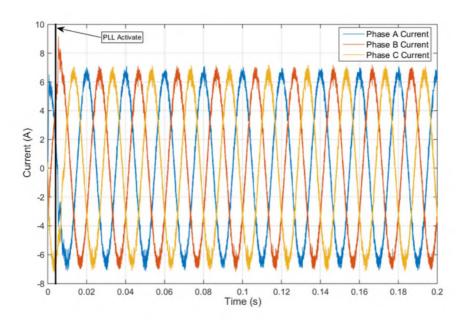

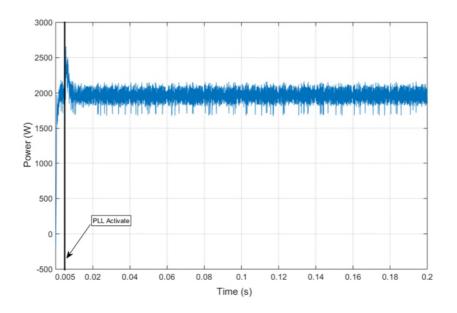

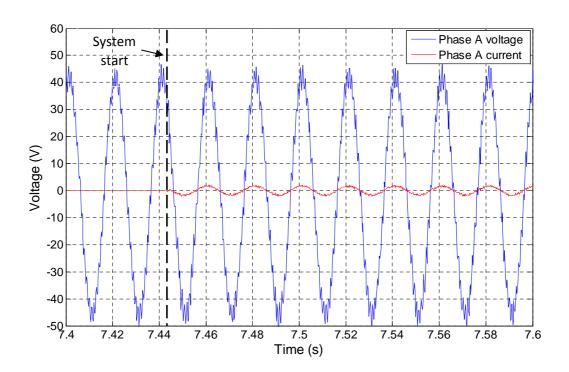

| Figure 7.7 Current waveform during the initial start-up process                                          | 138 |

| Figure 7.8 Power output during the initial synchronisation process                                       | 139 |

| Figure 7.9 Current reference during the initial start-up                                                 | 140 |

| Figure 7.10 The estimated voltage dq components                                                          | 140 |

| Figure 7.11 The estimated grid voltage waveform                                                          | 141 |

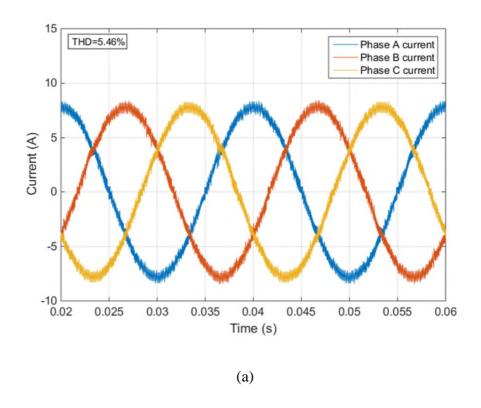

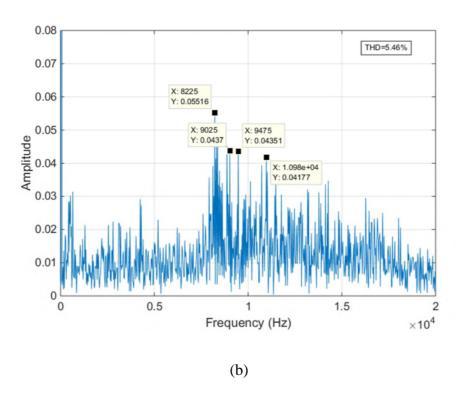

| Figure 7.12 Results of (a) the current waveform and (b) the FFT spectrum                                 | 142 |

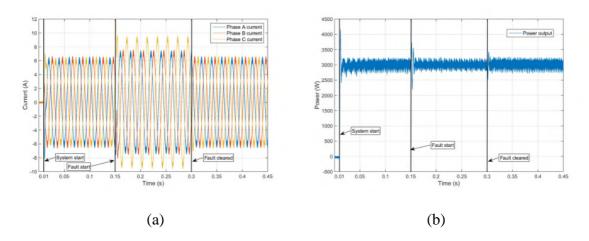

| Figure 7.13 Current injected when the system starts and the power flowing into the d.c. side             |     |

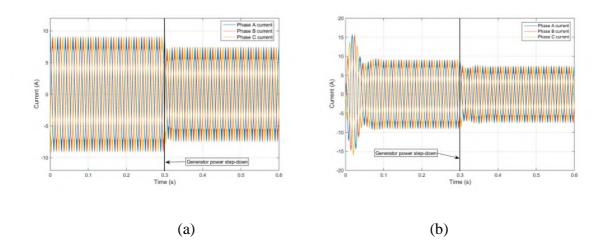

| steps down with: (a) faster current control; (b) slower current control                                  | 143 |

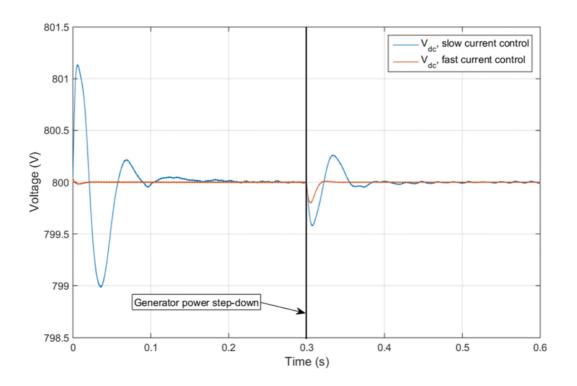

| Figure 7.14 The d.c. bus voltage response                                                                | 143 |

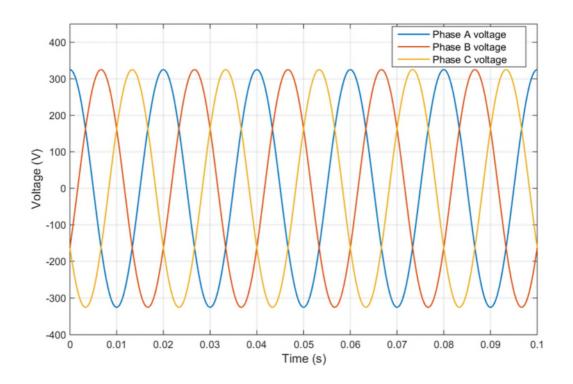

| Figure 7.15 Waveform of the grid voltage                                                                 | 145 |

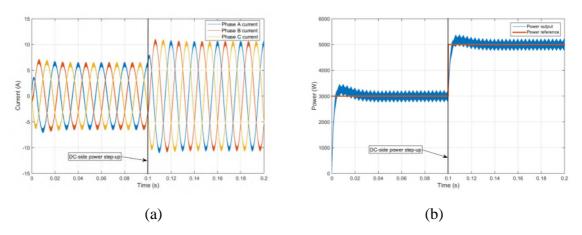

| Figure 7.16 Initial current (a) and power (b) transient response of the a.c. voltage-sensor-less         |     |

| current control with 50% of grid voltage amplitude feed-forward error                                    | 146 |

| Figure 7.17 Initial current (a) and power (b) transient response of the a.c. voltage-sensor-less         |     |

| current control with 30 degree of grid voltage phase angle feed-forward error                            | 146 |

| Figure 7.18 Initial current (a) and power (b) transient response of the a.c. voltage-sensor-less         |     |

| current control with accurate feed-forward grid voltage                                                  | 146 |

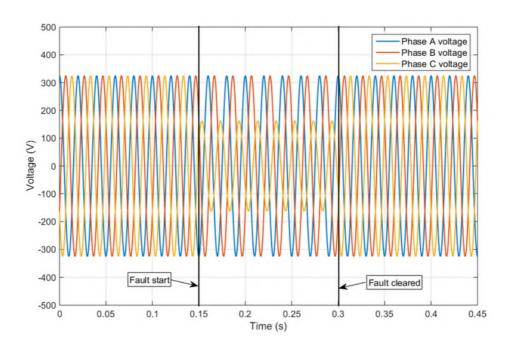

| Figure 7.19 Waveform of the grid voltage                                                           | 148 |

|----------------------------------------------------------------------------------------------------|-----|

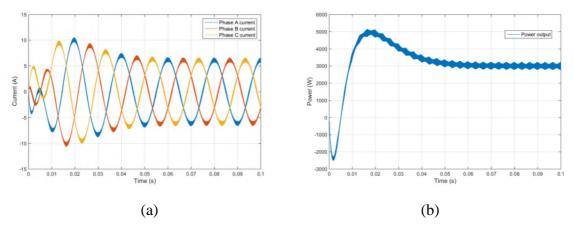

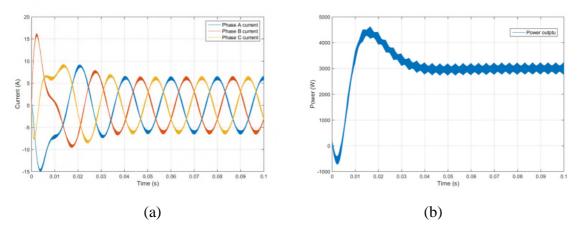

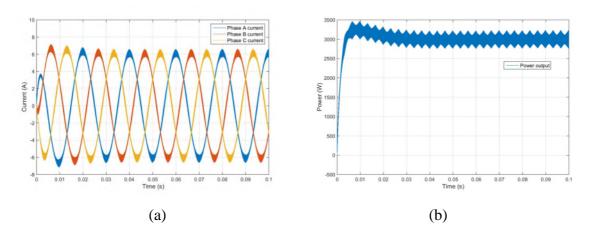

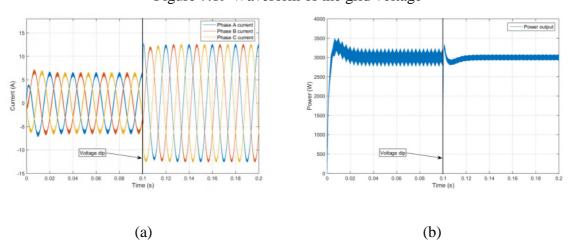

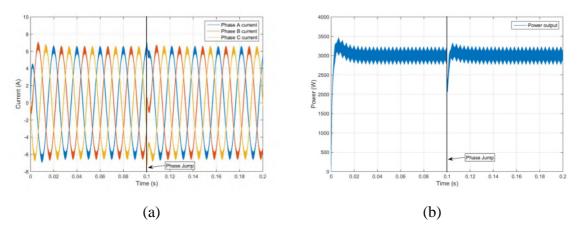

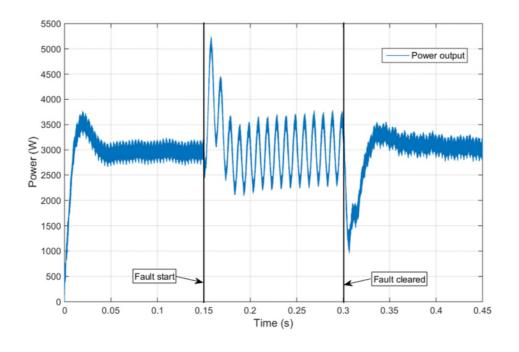

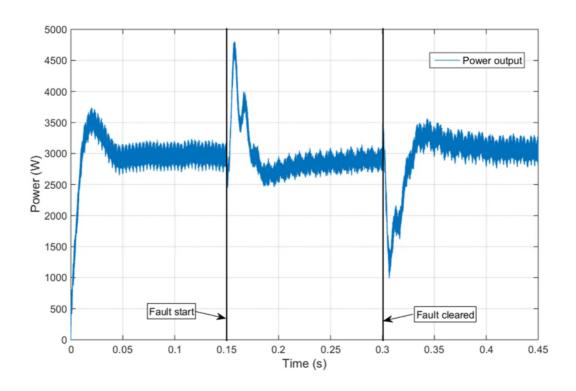

| Figure 7.20 Current (a) and power (b) response to the a.c. voltage dip                             | 149 |

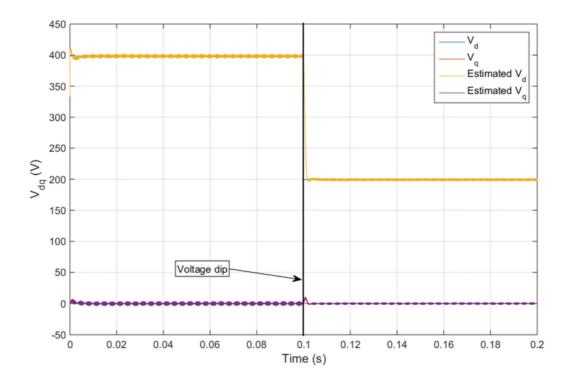

| Figure 7.21 Estimated grid voltage $V_d$ and $V_q$                                                 | 149 |

| Figure 7.22 Current (a) and power (b) response with a slow grid voltage estimation system          | 150 |

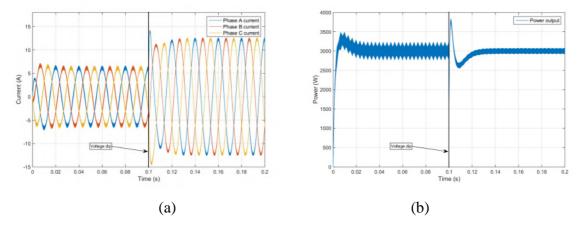

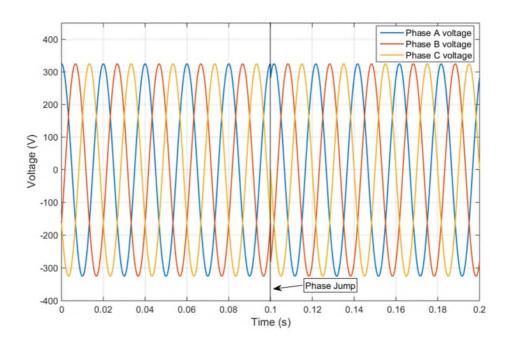

| Figure 7.23 Waveform of the grid voltage with 30 degree phase jump                                 | 150 |

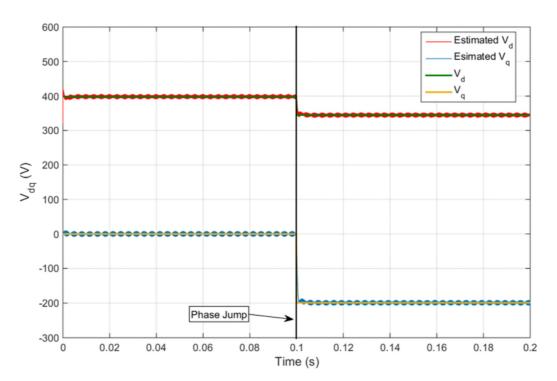

| Figure 7.24 Current (a) and power (b) response under 30 degree grid voltage phase jump             | 151 |

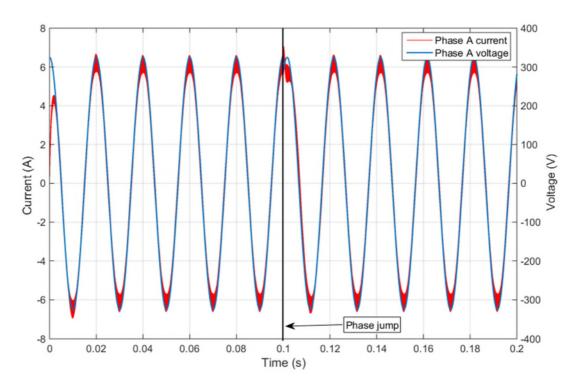

| Figure 7.25 Estimated grid dq components comparing to the actual values                            | 152 |

| Figure 7.26 Phase A current and the phase voltage before and after phase jump                      | 152 |

| Figure 7.27 Current (a) and power (b) response to a reference power step change                    | 153 |

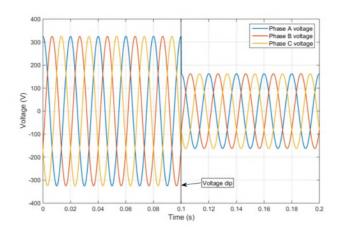

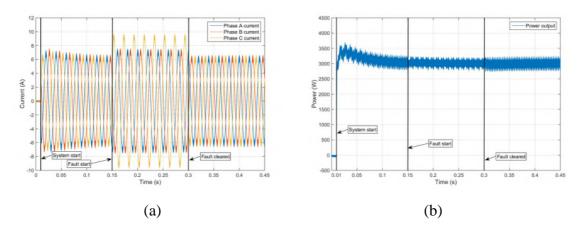

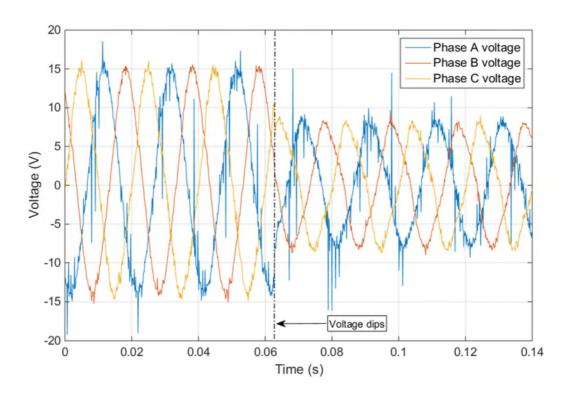

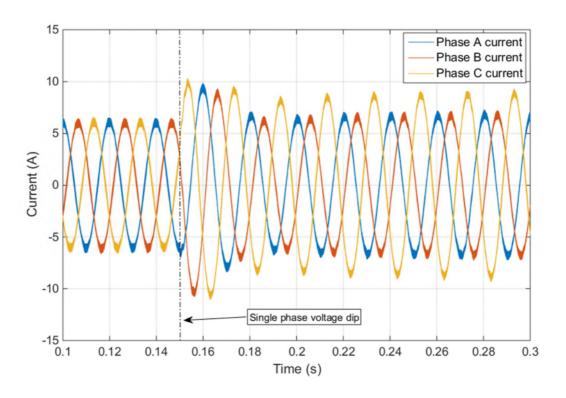

| Figure 7.28 Grid voltage with single phase voltage dip.                                            | 155 |

| Figure 7.29 Response of the current control equipped with voltage sensors and using new            |     |

| proposed symmetrical components decomposition method against single phase voltage dip:             |     |

| (a) current waveform; (b) output power at PCC                                                      | 155 |

| Figure 7.30 Response of the current control equipped with voltage sensors and using notch          |     |

| filter to decompose symmetrical components against single phase voltage dip: (a) current           |     |

| waveform; (b) power output at PCC                                                                  | 156 |

| Figure 7.31 Current response to single phase voltage dip aiming at balanced current                | 157 |

| Figure 7.32 $I_d$ and $I_q$ responding to the single phase voltage dip: (a) positive sequence; (b) |     |

| negative sequence                                                                                  | 158 |

| Figure 7.33 Active power output measured at PCC                                                    | 158 |

| Figure 7.34 Current response to the single phase voltage dip aiming at constant power              | 159 |

| Figure 7.35 $I_d$ and $I_q$ response to the single phase voltage dip: (a) positive sequence; (b)   |     |

| negative sequence                                                                                  | 160 |

| Figure 7.36 Active power measured at PCC                                                           | 160 |

| Figure 8.1 A.c. side power voltage source of experiment test rig                                   | 162 |

| Figure 8.2 D.c. power source                                                                       | 163 |

| Figure 8.3 Inverter board                                                                          | 164 |

| Figure 8.4 Converter Board mounting and casing                                                     | 164 |

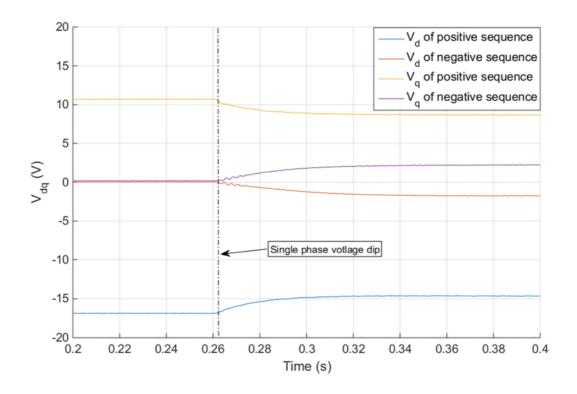

| Figure 8.5 Measured grid voltage dq components                                                     | 166 |

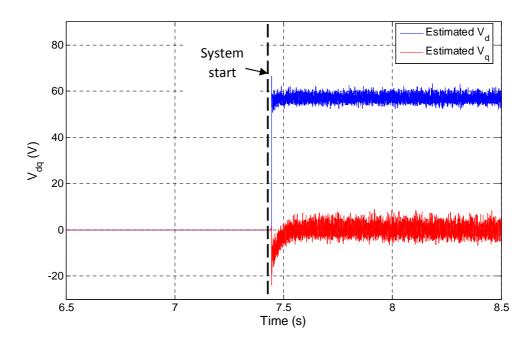

| Figure 8.6 Estimated grid voltage dq components                                                    | 166 |

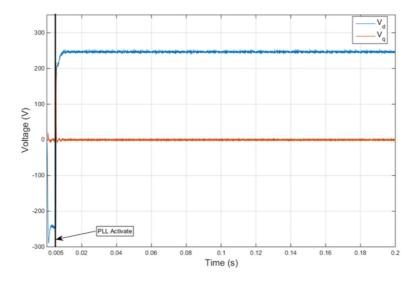

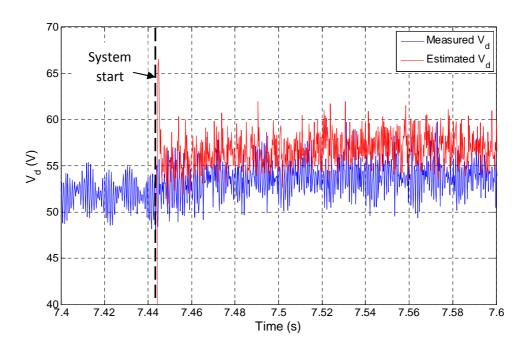

| Figure 8.7 Comparison between measured and estimated grid voltage                                  | 167 |

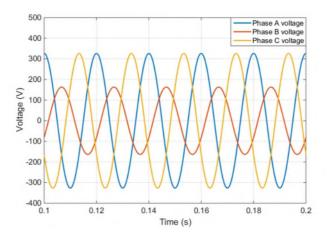

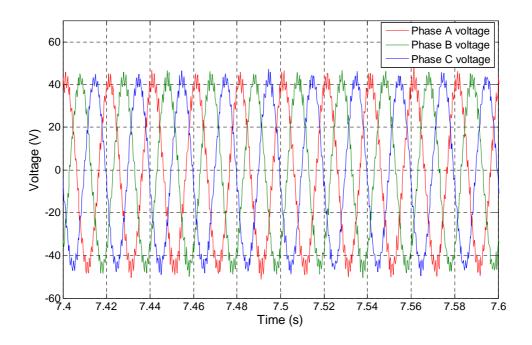

| Figure 8.8 Three phase voltage of the grid                                                         | 168 |

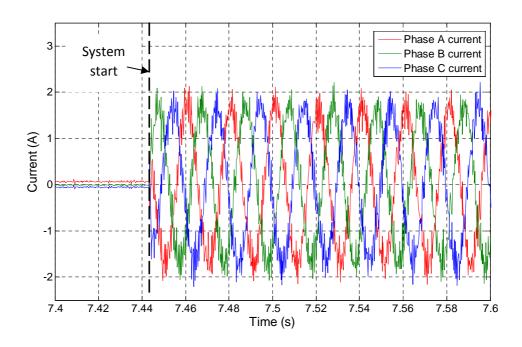

| Figure 8.9 Current injected                                                                        | 168 |

| Figure 8.10 Scaled view of the phase current and voltage                                           | 169 |

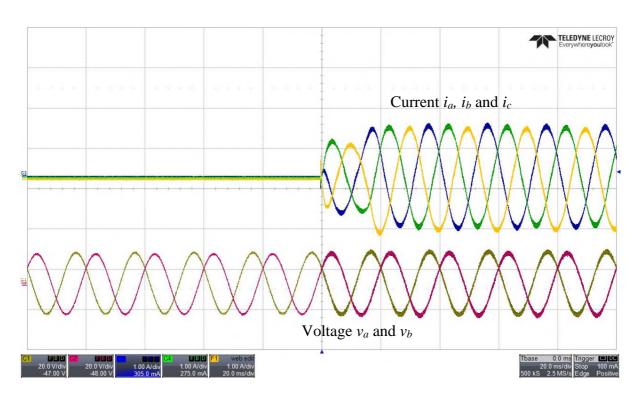

| Figure 8.11 Initial current response with accurate grid synchronisation                     | 170 |

|---------------------------------------------------------------------------------------------|-----|

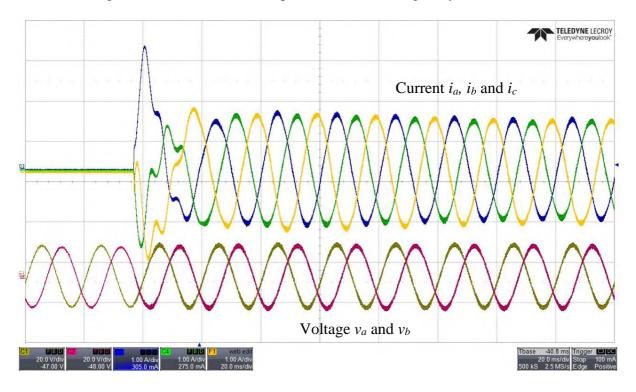

| Figure 8.12 Initial current response without accurate grid synchronisation                  | 170 |

| Figure 8.13: The control system put into experiment                                         | 171 |

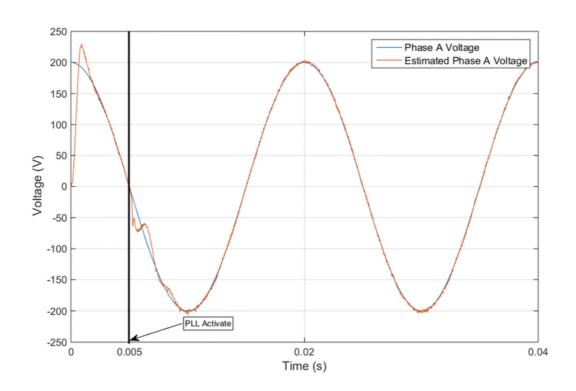

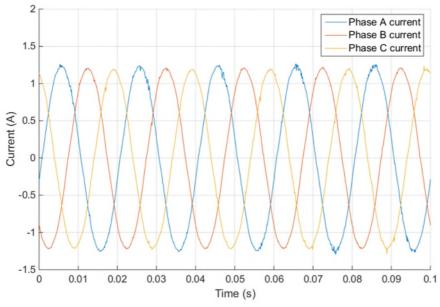

| Figure 8.14 Steady state current                                                            | 172 |

| Figure 8.15 Measured three phase voltage of the a.c. side                                   | 173 |

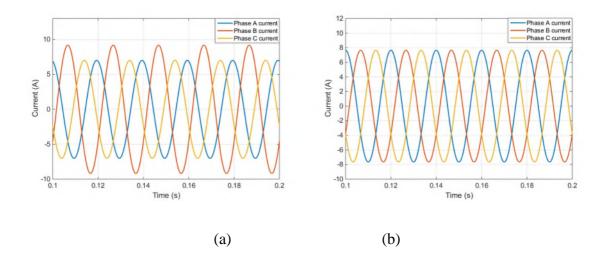

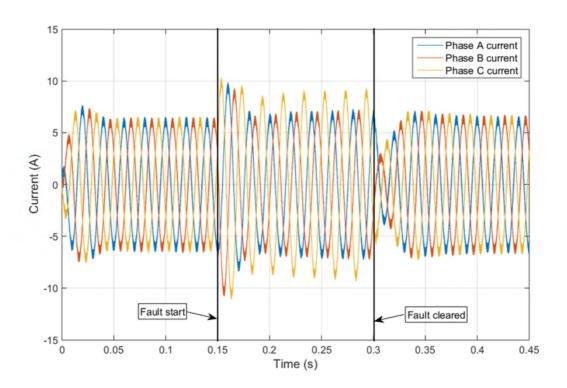

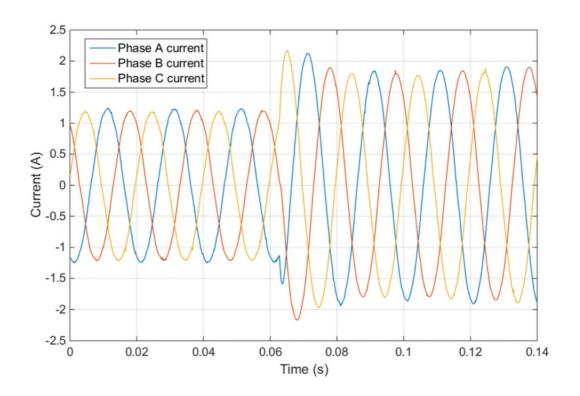

| Figure 8.16 Three phase currents                                                            | 174 |

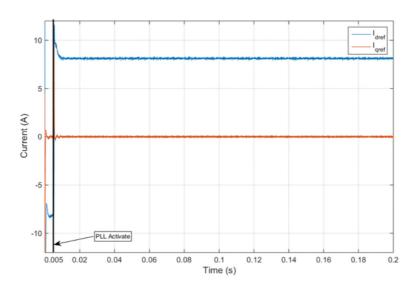

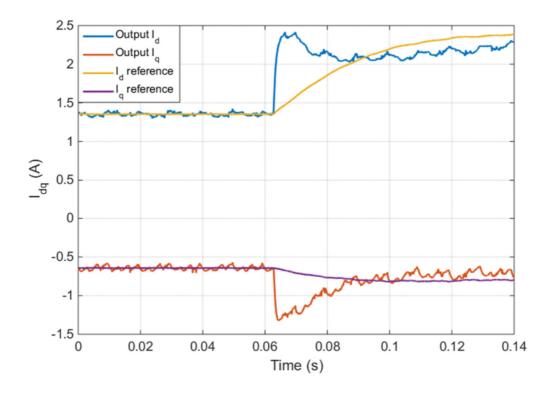

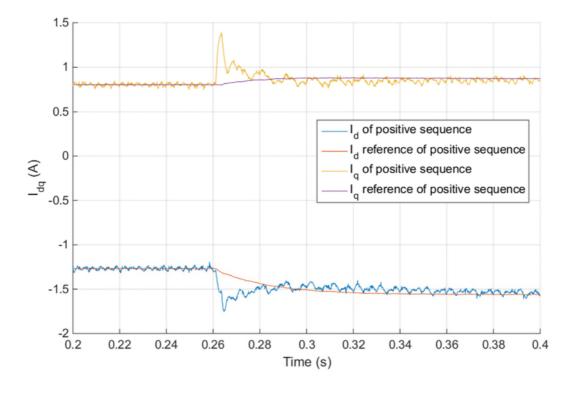

| Figure 8.17 Current dq components tracking their reference                                  | 174 |

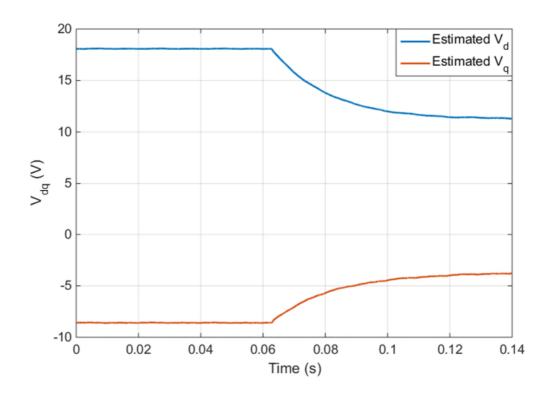

| Figure 8.18 Estimated a.c. side voltage dq components                                       | 175 |

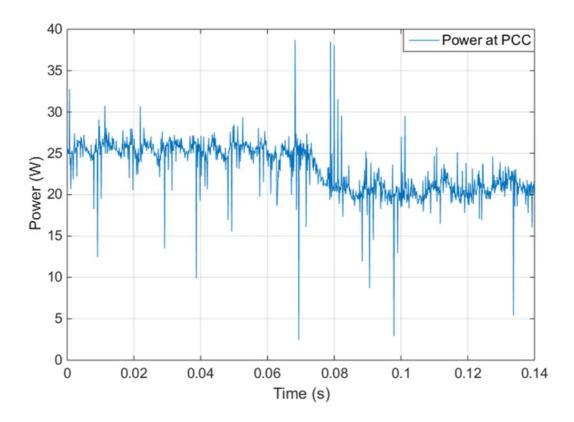

| Figure 8.19 Output power at PCC                                                             | 177 |

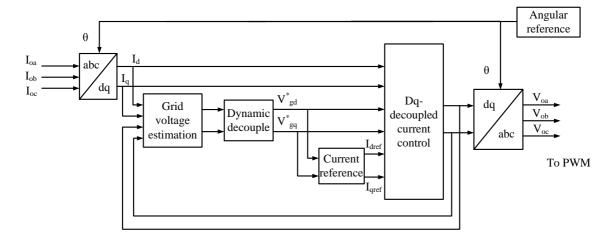

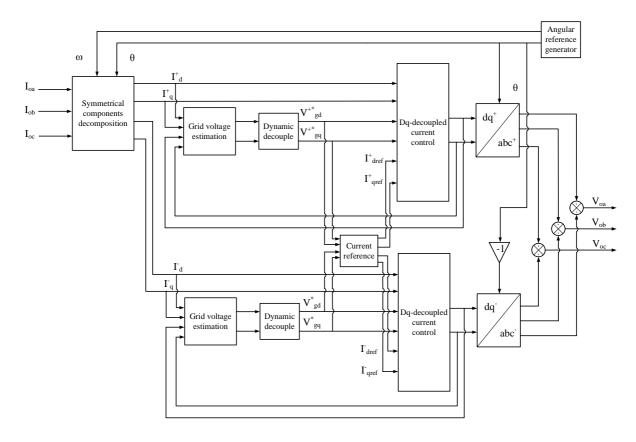

| Figure 8.20 Control system structure under test                                             | 178 |

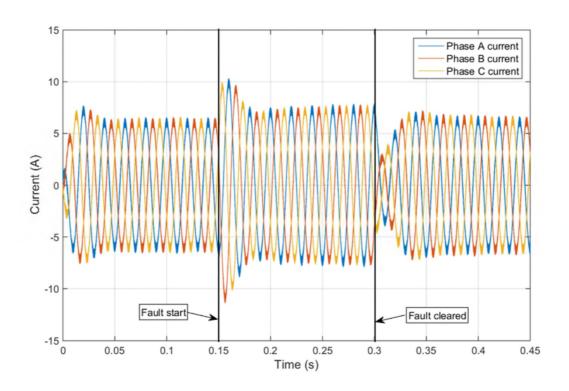

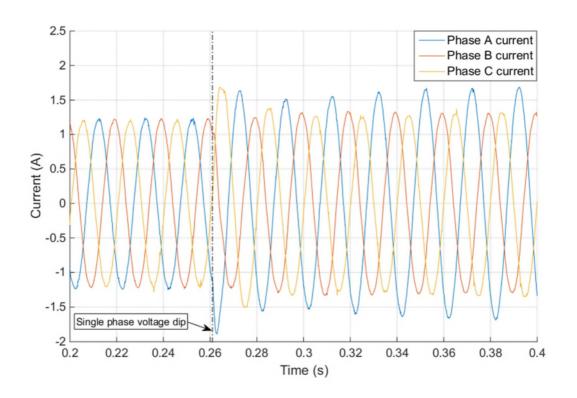

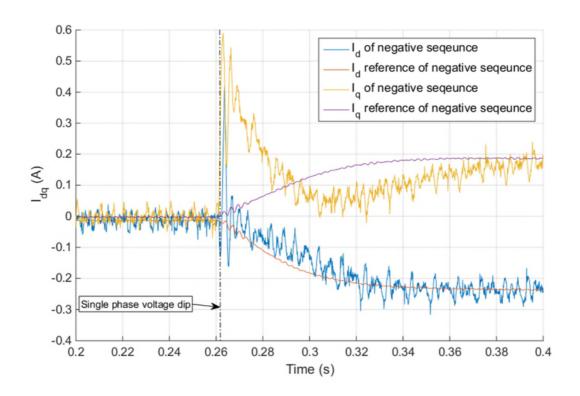

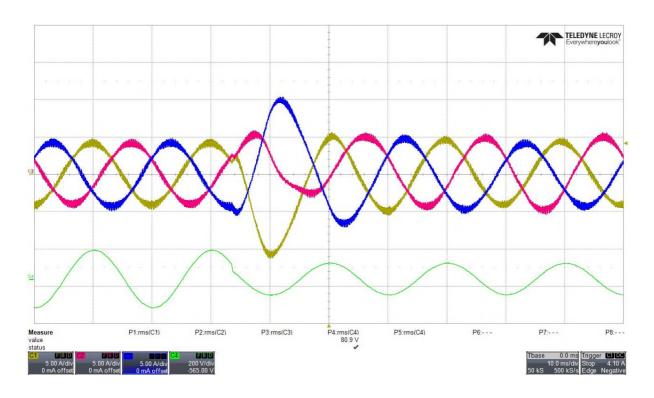

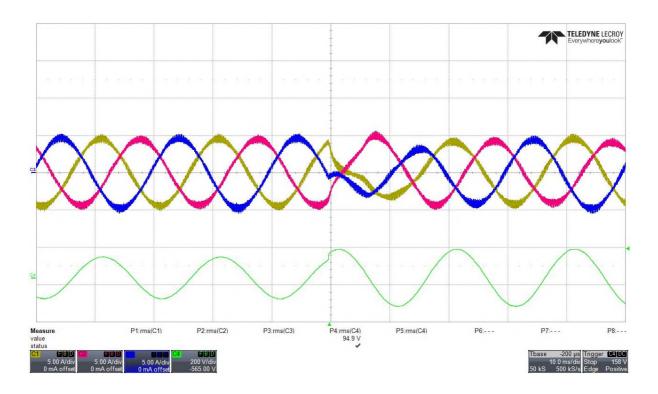

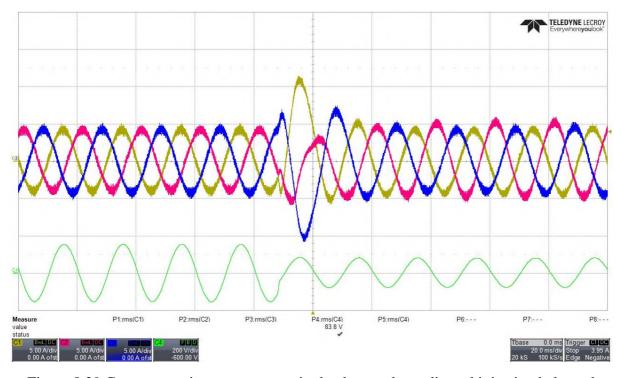

| Figure 8.21 Current sampled during experiment                                               | 179 |

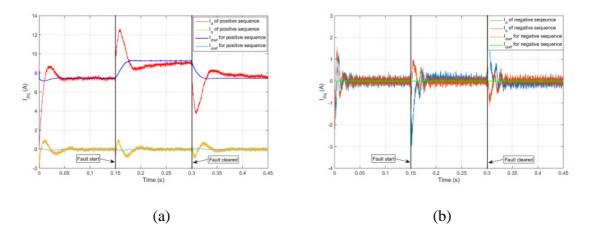

| Figure 8.22 Current response during unbalanced fault from simulation                        | 179 |

| Figure 8.23 Estimated symmetrical components of the grid voltage                            | 180 |

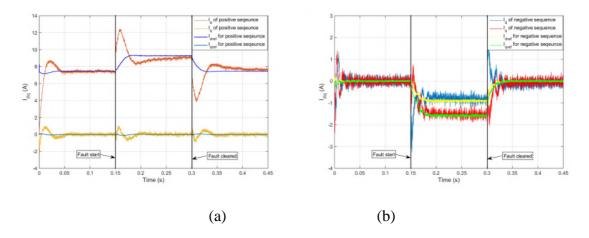

| Figure 8.24 The positive sequence current dq-components tracking their reference            | 180 |

| Figure 8.25 The negative sequence current dq-components tracking their reference            | 181 |

| Figure 8.26 Steady state current of proposed system                                         | 182 |

| Figure 8.27 Current control transient response at a single phase voltage dip and injecting  |     |

| balanced three phase current                                                                | 182 |

| Figure 8.28 Current control transient response when the single phase voltage dip is cleared | 183 |

| Figure 8.29 Current transient response at single phase voltage dip and injection balanced   |     |

| three phase power                                                                           | 183 |

# Nomenclature

fFrequency i Current Real power P Q Reactive power R Resistance Voltage v ξ Damping-ratio Angular velocity ω

## **List of Abbreviation**

a.c. Alternating Current

d.c. Direct Current

dq Direct-Quadrature

DD SRF-PLL Decoupled-Double Synchronous-Frame-Phase-Locked-Loop

IAE Integral of Absolute Error

IGBT Insulated-Gate Bipolar Transistor

MPPT Maximum Power Point Tracking

PCC Point of Common Coupling

PI Proportional-Integral

PR Proportional-Resonant

PLL Phase-Locked-Loop

PWM Pulse-Width-Modulation

VAR Volt-Ampere Reactive

HVDC High Voltage Direct Current

## **Chapter 1 Introduction**

#### 1.1 Motivation of the research

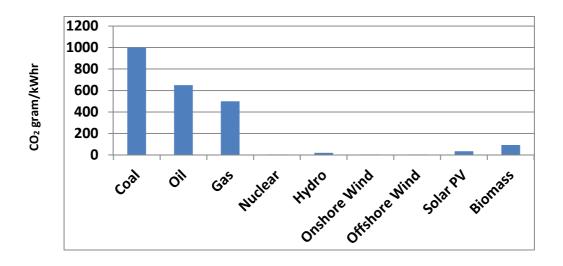

It is a relatively familiar but still on-going topic that human activities are changing the global climate particularly due to the emission of carbine-dioxide (CO<sub>2</sub>) associated with the large scale energy production using fossil fuels [1, 2]. The traditional electrical power systems are largely dependent on centralized power generation stations using systems such as gas turbines and steam turbines which contribute majority of the green-house gas emissions [3]. Arguably cleaner, but also large hydro power stations and nuclear power plants are used but this is not always possible and they can still cause different kinds of environmental and social-economic issues. Strictly speaking, none of the commercial electrical power generation technologies is carbon free because of the carbon footprint associated with the manufacturing and maintenance of the technical system, but given the expected lifetime of a system in 20-50 years the systems using renewable rather than fossil fuel resources are of much lower carbon footprint [4]. Figure 1.1 shows the typical values of CO<sub>2</sub> emission for different types of technologies for generating 1 kWhr electricity levellized over their respective lifetimes [5].

Figure 1.1 Carbon footprint of electricity generation

The power generated from the relatively large and dispatch-able power sources is transmitted and then distributed through the power networks or grids. This is regarded as the conventional configuration of the power systems before the rise of the cleaner generation technologies which are usually less dispatch-able because of the random variations of the primary resources. Wind turbines, solar panels and tidal energy devices as well as CHPs (combined heat and power) using biomass fuels are reshaping the electrical power industry in terms of the grid configurations and the relationships between the energy providers and consumers [6-10].

To constrain the emissions, more and more generation is now provided by renewable generators which are directly connected to the grid including the distribution networks. It attracts investment because of the environmental protection and economic reasons which have influenced the government policies as exemplified by numerous subsidy schemes all over the world [11]. Many clean energy generation systems could be installed domestically, such as solar panels and small scale wind turbines to harvest the locally available resources. This situation allows the microgrid operation mode in which the generated power can be utilized locally to give direct economic incentive and the customers are less likely to suffer from a loss of supply caused by outages in the traditionally upstream systems. Also the owners of the generators are usually interested in selling the additional power or energy generated to the grid to make a direct income. The grid interfaces are usually through a power electronics stage. However, the rise of distributed generation not only brings about opportunities but also presents challenges to the management and stability of the existing power systems. Stringent requirements are being proposed by the transmission and distribution network operators as will be illustrated in the following sections.

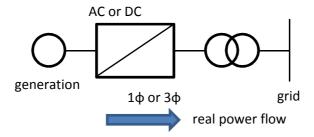

Partially because of the random variation of the primary resources, renewable power generation systems are usually interfaced to the grid through power electronic converters as shown in Figure 1.2. Power electronics which uses power semiconductors to convert electrical power

from one form to another can establish a variable condition for the generator and also suit the more fixed frequency and voltage of the a.c. grid. Until recently, power electronics has been predominantly used for loads such as motor drives, lighting a switched mode power supplies (SMPS). In pure grid applications, power electronics has been mainly used for HVDC (high voltage d.c.) transmission [12-15], static VAr compensation (SVC) [16], active filtering [17-19] and some presently miscellaneous applications including solid state fault current limiting [20], on-load transformer tap changing and seamless supply transferring [21].

Although the system configuration shown in Figure 2 is apparently a reverse of a typical load system, the requirements would inherently be different for a generation technology to a load technology. In addition to the technical challenges which are to be discussed in the following sections, reliability and cost are also important issues given that the investors would naturally expect short payback times and the power electronic converters are expected to work for a long time in environments which are not easily accessible to professional engineers. These are some of the key issues and the study of this thesis was planned in such a context.

Figure 1.2 General layout of renewable generation system

### 1.2 Technical challenges

Increasing Increasing the penetration level of distributed generation is one of the top interests among researchers and the power industry. As implied before, the rise is driven by, firstly the interest of increasing the power generation from non-fossil fuels such as renewable resources,

which is desirable from an environment protection point of view; secondly, the benefit from the changed role of the consumers to participators, which injects dynamism into the market; thirdly, increasing the overall efficiency of the existing power system, which could potentially benefit the network owners and operators. However, the power distribution network is a relatively weak system where voltage fluctuation and frequency variation (when in a microgid operating mode) can happen easily [22]. Fault level contribution of distributed generation has recently become another issue in some systems particularly urban distribution networks where the power density in MW/km² is high [23]. Furthermore, the concerns about the availability and reliability of distributed generation never fade away in the mind of all players involved in the power industry. Apart from the numerous methods that aim at increasing the distribution network robustness, the quality of the control of the distributed generation devices directly affects the stability of the system.

It was a quite simple role that the renewable generation used to play in the distant past: to generate and providing power to the utility grid. When the penetration level was low, they were usually regarded as 'negative loads'. During grid faults, the distributed generation were allowed to disconnect in order to protect the equipment from being damaged. However, with more and more renewable generation connected to the grid, such a pure negative power source operation could cause problems. The generation systems would naturally be required to provide grid support in terms of voltage and frequency control during normal operation. Another stringent requirement which has presented challenges to most manufacturers is grid fault ridethrough or low voltage ride-through [24]. When a fault happens in an adjacent area of where a considerable amount of renewable or embedded generators are providing power, which could cause the generators to quit, the loss of power provided by the generators could make the utility voltage drops even more and cause further problems. Reconnection after fault clearance would take time. The situation has generally changed nowadays. The renewable and/or distributed

generation is now generally required to remain connected during the fault to provide support to the grid immediately after the fault clearance. This brought challenges to the control system design, particularly associated with grid connected inverters. These requirements are special to generation rather than load technologies.

Three-phase inverters are often used to interface the renewable or distributed generation devices to the grid in order to cope with inherent variability of the sources. For large wind turbines, sometimes the generator is directly connected to the grid but not always. For off shore wind farm, the connection to the main grid is usually via a HVDC where an inverter is necessary to covert the power from d.c. to a.c.. For small wind power generators, a grid interfacing inverter is often required as the power from the generator is usually converted to d.c. for power quality control and maximum power tracking purposes etc. The solar panels will necessarily require a grid interfacing inverter as their power output is in term of d.c.. Among many situations that would cause the grid connection of the inverter to trip, the unbalanced faults are some of the most challenging and important because the commonly used voltage source converters (VSC) are very sensitive to a.c. side voltage unbalances; a commercial drive system with an active front-end rectifier (which is a VSC) would usually trip upon detecting a 2% content of negative sequence voltage [24]. The conventional control schemes designed for operation under balanced utility voltage, e.g. the voltage oriented current control with simple synchronised reference frame phase-locked-loop, are not able to yield satisfactory results during the unbalanced grid fault ride-through. The consequences include low order and even order harmonic injections and even damage to the power modules as well as capacitors in the inverter due to excessive currents. Apart from the gird faults, unbalanced loads and unbalanced generation on the three phases can also cause sustained voltage unbalance at the point of common coupling (PCC) with respect to the converter connection. As the grid operators are always aiming at balancing the network, the level of unbalance due to the unbalanced load or generation is usually very small but could last much longer than the fault. Therefore, a control strategy with unbalanced utility voltage tolerance is necessary for grid connected inverter systems. Many researches have addressed this issue and several solutions have been reported [25-28]. However, previous studies usually focused on the steady-state performance while fast response with adequate transient stability needs further investigation; the key is to quickly identify the positive and negative sequences in the reference voltage for control. This defines part of the context of this study.

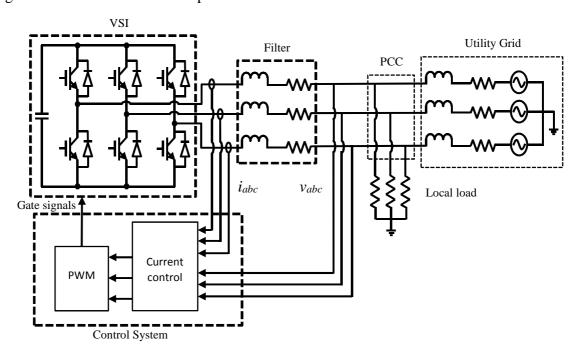

As analysed above, there is the need to reduce the system cost and improve reliability. This has given rise to the incentive to develop control techniques without using some of the sensors in a standard system which is shown in Figure 1.3. This study concentrates on achieving the above control objective without using the sensors to measure the grid voltage at the PCC. The current sensors are retained because the semiconductor devices require that the converter currents are always under strict control to avoid overloading. A brief analysis on the performance of the voltage-sensor-less control will be provided in Section 1.3.5.

Figure 1.3. Controller block diagram of a grid connected VSC with internal current control

# 1.3 Compliance to grid code

When renewable power was only a small part of power generation in the system, the renewable generating units were treated just as negative, passive loads which took little responsibility towards the reliable and stable operation of the power system. As the penetration of renewables increases, grid codes are modified to specify the requirements on their performance and functionalities during normal operation and system abnormalities, such as faults. Requirements are imposed on renewable generation connected to both transmission and distribution networks [29]. In this section, the requirements issued by grid codes and technical recommendations are introduced. For large scale generations, some of the functions required by the grid code such as frequency adjustment and reactive power compensation will be done by adding additional control loop to the control system, which are not included in this research. Further research should be done in the future. For the small scale generations, it is not possible to affect the grid frequency or dealing large impact on the grid voltage. These grid code requirements are only mentioned to clarify the different situations that an inverter could encounter during on-line operation.

Traditional synchronous generators are connected to the grids directly while many renewable power generation systems are connected through a power electronics conversion stage. Therefore, the control capability and limitations of the converters are of serious importance in terms of grid code compliance. Nowadays, voltage source converters (VSCs) are used as standard in most systems, and this thesis will focus on the standard 2-level VSCs which are commonly found in wind turbines and PV systems. The study further focuses on the grid side converter. The relevant aspects of grid codes are harmonics, restrictions on the variation of power generated and grid fault ride-through capabilities. This section briefly reviews the main points of these aspects.

#### 1.3.1 Harmonic limits

It is the responsibility of the utilities to make sure that the voltage at the connection point of the generation, which is usually also the point of common coupling (PCC) other circuits, is phase-balanced and the harmonic content is below certain level. Current harmonic injection into the grid by the inverters should follow the requirements to the general load [30]. The harmonic requirements provided by IEEE Std 519-1992 is generally accepted and followed by many grid codes of different countries. Table 1.1 summarizes these requirements, taken from IEEE Std 519-1992.

The harmonic content in the current produced by the grid connected inverter is usually regarded as low because of the high switching frequency of modern PWM (pulse-width modulation) processes, >2 kHz. Multiple level inverters are increasingly used for high power applications. The equivalent switching frequency is high although the actual switching frequency of individual devices is kept low to constrain the switching losses [24]. However for the reason to be shown in Chapter 2, there is the risk that some unusual harmonics, such as even order harmonics, injected into the grid could exceed the limit in poorly designed converters due to incomplete understanding of the physical phenomena in the converter and its control system. The non-ideal characteristics of the devices can also cause harmonics as shown in [32]. The main objective of this study is about control of the grid interfaced inverters under abnormal grid conditions, harmonics are not a major concern and the main purpose of harmonic analysis in this thesis is to guide the controller design and identify the cause of the harmonics that have not been eliminated in the test results.

| $\label{eq:maximum Harmonic Current Distortion in Percent of I_L} \\ Individual Harmonic Order (Odd Harmonics)$ |      |     |     |     |     |              |

|-----------------------------------------------------------------------------------------------------------------|------|-----|-----|-----|-----|--------------|

|                                                                                                                 |      |     |     |     |     | $I_{SC}/I_L$ |

| <20*                                                                                                            | 4.0  | 2.0 | 1.5 | 0.6 | 0.3 | 5.0          |

| 20<50                                                                                                           | 7.0  | 3.5 | 2.5 | 1.0 | 0.5 | 8.0          |

| 50<100                                                                                                          | 10.0 | 4.5 | 4.0 | 1.5 | 0.7 | 12.0         |

| 100<1000                                                                                                        | 12.0 | 5.5 | 5.0 | 2.0 | 1.0 | 15.0         |

| >1000                                                                                                           | 15.0 | 7.0 | 6.0 | 2.5 | 1.4 | 20.0         |

Even harmonics are limited to 25% of the odd harmonic limits above.

Current distortions that result in a dc offset, e.g. half-wave converters, are not allowed.

Where

$I_{SC}$  = maximum short-circuit current at PCC

$I_L$  = Maximum demand load current (fundamental frequency component) at PCC.

TDD = Total demand distortion (RSS), harmonic current distortion in % of maximum demand load current (15 to 30 min demand)

**PCC** = Point of common coupling.

Table 1.1 Customer current harmonic limits, taken from [30]

#### 1.3.2 Requirements during normal operation

A feature of renewable power generation, particularly wind and solar PV, is the unpredictability of the input power. For economic reasons a power system is designed to withstand a limited amount of sudden power change and in practice this is usually set as the loss of a maximum power plant [33]. The way to provide the support is traditional spinning reserve although energy storage is being actively developed as a more efficient alternative.

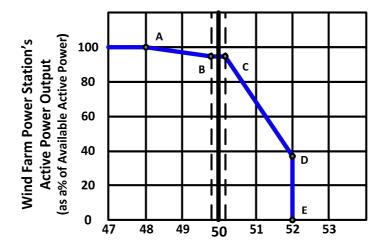

As wind power become a significant part of the overall generation, it has been required to share the duty of frequency regulation in the power system. Figure 1.4, taken from Irish grid code [34], shows the requirement to wind farms during grid frequency deviation. About 5% headroom is kept during normal operation so that the wind farm can produce more real power

<sup>\*</sup>All power generation equipment is limited to these values of current distortion, regardless of actual  $I_{SC}/I_L$ .

when called upon. This can be wasteful as on average for every 20 turbines built, 1 is kept as reserve which is not generating power. Figure 1.5 shows that as the grid frequency reduces by 2 Hz, the wind farm output would increase by 5% of the initial power. Even assume that the wind farm was initially operating near its maximum power, this is about 25 times weaker than the frequency response of a traditional thermal or hydropower plant with a typical 4% power-frequency droop, suggesting that other means of frequency regulation such as energy storage and spinning reserves would still be needed.

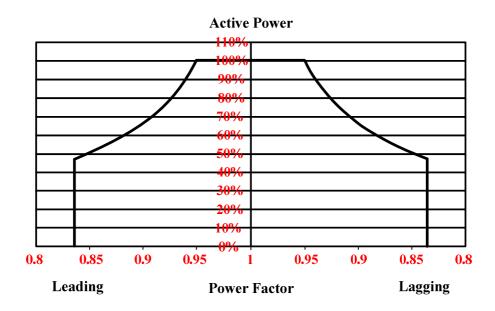

Figure 1.4. Grid code requirement for wind farm output during frequency variation, taken from [34]

However the power output of a modern turbine can respond very quickly owing to the modern power electronic converters included in the system. It is partially for this reason that recently in some countries, it has been seriously considered to require renewable power generation systems to provide fast and aggressive response to small deviations of system frequency. This is typically implemented through the concept of synthetic inertia emulating the change of kinetic energy in a synchronous generator [35]:

$$\Delta P = -2H \frac{df_{pu}}{dt}$$

1.1

where H is the H-inertia constant of the emulated power plant, typically 4-5 seconds,  $f_{pu}$  the per unit frequency of the a.c. system and  $\Delta P$  the per unit power increment of the wind or renewable power plant. t is the time.

The wind farms are now also responsible to the voltage and reactive power control of the power system. This is usually specified as the range of lead to lagging power factor to be provided by the farm at different real power levels.

Figure 1.5. Wind farm active power output under frequency variation, taken from [34]

#### 1.3.3 Fault-ride-through capability

Large synchronous generators can usually remain connected during a short circuit fault in the transmission network lasting for about 100-200 ms. The generators will feed current into the fault and the protection relays of the power network are based on this. A couple of reasons contribute to the capability of the synchronous generators: 1) the relatively rugged diodes and thyristors used in the brushless excitation system [33], and 2) the damper windings in modern machines which to some extent screens the rotor circuit from the effect of the stator side fault current [35]. The main concern is whether the synchronous machines can maintain synchronism with the rest of the grid after the fault clearance.

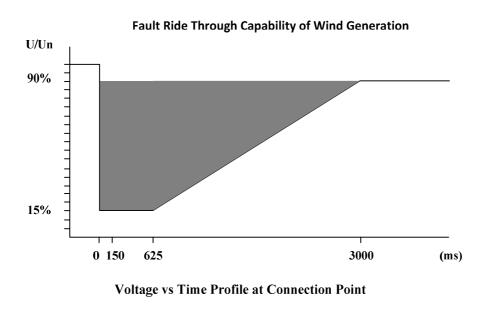

In the past when renewable power generation was treated as a negative load, there was no specific requirement to it but this situation has dramatically changed in the last 15 years. Stringent requirements are now included in the grid codes of almost all countries to ensure secure operation of the power system [36]. When renewable generation is now integrated or embedded into the transmission or distribution networks, the general expectation is that the new type of generation should behave like traditional synchronous machines. The generation units should possess the capability to ride through grid abnormalities. For instance, the UK National Grid Code requires that all wind turbine generators should remain connected to support the network and assist fault recovery if the transmission network voltage (any phase) undergoes the profile as shown in Figure 1.6 [34].

Figure 1.6 Grid code requirement for wind generation supporting the grid during grid faults, taken from [34]

A renewable power generation unit is interfaced to the grid fully [38-41] or partially (like a doubly fed induction generator [36, 42-44]) through a power electronic converter. The difficulty for a grid interfaced converter is to ride through unbalanced grid conditions including faults. Previous studies have considered control algorithms to smooth the d.c. side power [24,

45] or eliminate a.c. side negative sequence current injection [46-48]. But the algorithms proposed usually assumed that the grid pcc voltage is measured as the reference for current control, and the control transients were usually ignored.

There has been the desire to avoid grid voltage measurement in converter current and hence power control. Reliability is a major concern particularly in the case when multiple generation units are connected to the same point of common coupling. A shared voltage measurement point could then become a single weak link in the design. In [37], Parker proposed a voltage-sensor-less controller for a single phase, multilevel converter. But for a three-phase converter where the phases should not be independently treated, further studies are needed to develop the corresponding controllers.

Immediately following the occurrence of severe unbalanced grid conditions, it is important to quickly capture the grid voltage condition and control the converter current correspondingly. Many control strategies are based on the decomposition of the fundamental components into positive and negative sequences. It was shown that [24], large d.c. link voltage transients appear if the phase sequence decomposition process is slightly slowed down. Therefore it would be more challenging to achieve smooth control in the overall system with voltage-sensor-less control, and this is the main challenge to be addressed in the present study.

#### 1.3.4 Standalone mode

Standalone or microgrid mode of operation is enabled by distributed generation. Many units indeed possess a power electronic interface stage. Control for grid voltage stability is a topic that is currently under intensive study [49]. There has not been attempt to achieve robust voltage control in the voltage-sensor-less mode because the duty of voltage stability control is usually assigned to a single master voltage source converter in the system with voltage sensors

[50]. Sensor-less control is still a desired feature for both the master and more distributed converters in the microgrid.

Although the grid voltage in the mains-connected mode is usually balanced with less than 1% of negative sequence [51], voltage unbalance is likely to occur in microgrid due to the reduced effect of load or generation aggregation [52]. Therefore three-phase converters may be required to operate with sustained voltage unbalance.

#### 1.3.5 Cost effectiveness and reliability issue of distributed generation

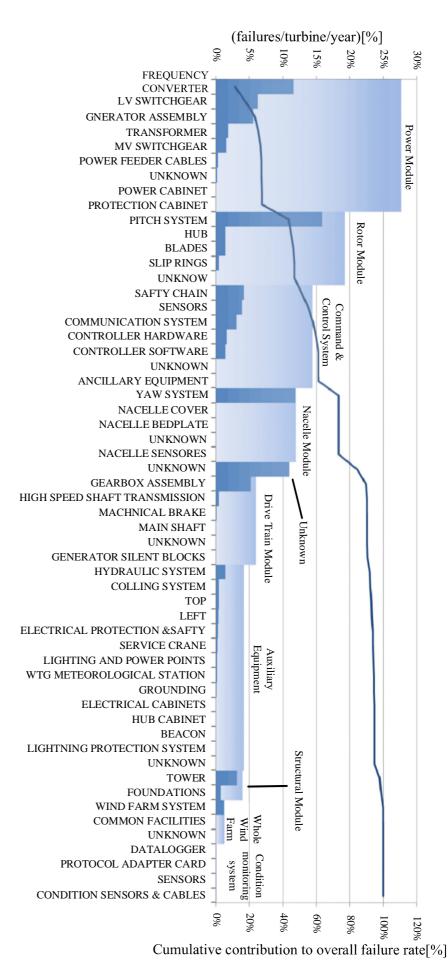

The distributed generator are predominantly provided by small business owners with locally installed units such as small wind turbines with permanent magnet generators and domestic users of solar PV. Many of such applications require a grid interfacing inverter at the output terminals. The reliability of the grid interfacing inverter contributes a great proportion of the overall reliability of the generation. Driven by desire of reducing the loss both from energy and economic points of view, the methods to improve the reliability of the grid connected inverter were investigated in [53]. Figure 1.7 shows the failure rate of the components of a wind-turbine and it can be seen that the grid interfacing VSI and its sensors contribute a great potion of the total failures.

15

Apart from the reliability issue, the owners of these generators are surely concerned about the cost effectiveness of their facilities. A competitive product in this market should be cheap enough to provide a reasonably short pay-back time.

To satisfy both interests illustrated above, an idea of reducing the sensors used in the grid connected inverter would be attractive. On one hand, the grid interfacing inverter is less likely to be affected by the failure of the sensors. On the other hand, the manufacturing cost is reduced through less sensors used. Among many sensor reduction methods, the voltage-sensor-less control is especially attractive for that it enables the system to eliminate the use of the a.c.-line voltage sensors, which reduces not only the number of sensor components, but also the number of types of the components. This shortens the supply chain behind the manufacturing and facilitate the modular design of such equipment, both reducing the cost.

# 1.4 Project Objectives

The previous discussion showed a clear future picture that an unbalanced three-phase voltage will becoming a more frequent situation at the interface between the renewable power generation and the main grid. The capability of dealing with the unbalanced grid-side voltage is an important aspect for those small scaled renewable power generators e.g. wind and solar power generators rated at 5 to 10KW, which are connected to the three-phase grid to optimise their performance. The three phase a.c. side or grid in this research refers to a three-phase three-wire configuration and as will be shown in the following chapters unless specified.

The previous research has shown discussed several different methods to achieve a.c. voltagesensor-less current control, some of them have the ability to ride-through an unbalanced grid fault. These details will be discussed in the later chapters. However, firstly, none of them has achieved unbalanced fault-ride-through based on a dq reference frame control scheme without using a.c. side voltage sensors. Secondly, the transient response of the control system should be further improved due to large delay introduced by conventional symmetrical component decomposition method. Thirdly, steady state operation of the a.c. voltage-sensor-less control system were the main focus of these previous researches. But how the system is going to synchronise to the grid voltage when start-up is not made clear.

This research aims at the development of a dq reference frame based a.c. voltage-sensor-less control algorithm which is able to reduce the cost of the generation equipment either by improving its reliability or reducing the manufacturing cost. The proposed a.c. voltage-sensor-less control system will be able to ride through the unbalanced grid side voltage. This requires the output power of the inverter can be controlled during unbalanced grid fault:

- to provide support to the grid under unbalanced grid side voltage;

- to compensate the unbalanced three-phase power output.

To overcome the potential threat of over-current when the inverter is not synchronised to the grid voltage, a start-up process is proposed in this research with direct current controllability. The power during this period should also be controlled for protecting other components on the circuit board.

The delay introduced by the symmetrical component decomposition system will deteriorat the performance of the current control. A faster symmetrical component decomposition method will be proposed to improve the transient response of the control system.

It is essential to this research to make understanding on the stability issue of a grid connected inverter system. The knowledge of a general design approach of an observer based voltage-sensor-less control system is proposed based on the analysis of the control parameters which affect the system stability against different source of the disturbances.

The following aspects will be clarified in the rest of the thesis:

- the structure of a voltage-sensor-less controller;

- the parameters and their effect on the system performance;

- the disturbances with respect to the system stability margin;

- the design objective and its physical necessities;

- the general design approach of the parameters for tuning the controller.

#### 1.5 Main Contributions of the Thesis

Initial synchronisation without a.c. voltage sensors: Several previous research studies have discussed the voltage-sensor-less control of a grid connected VSC for normal operation as well as the system performance under distorted grid voltage conditions [54-57]. However one important step for operation of the grid connected inverter, , the initial grid synchronisation, has been largely ignored. In this research, the initial synchronisation to the grid voltage before start-up is proposed. This is achieved from estimation/calculations based on the system response to the switch control commands without voltage sensors. An initial synchronisation method is developed to ensure the safety of both the power modules and the d.c. link capacitor. This provided a safe method to synchronise to the grid voltage without using voltage sensors. This also provides an alternative way to achieve grid synchronisation for 2 level grid connected inverters with a.c. voltage sensors, improving the reliability of the conventional system through redundancy.

Faster PLL system design for unbalanced utility voltage: As an important part of the control objective, the unbalanced operation of the grid connected VSCs is a focus of this study. A new PLL system is proposed and tested to solve the problem of oscillation and slow transient response of conventional PLL systems for decomposing the fundamental frequency

components of the positive and negative sequence from the total. The proposed PLL system enhanced the transient response of the proposed voltage-sensor-less VSC against utility voltage disturbances.

A generalized control method for the grid connected inverter for wind and solar power generation where a grid interfacing inverter is needed is presented by this research. As the rated power of the model being developed in this research is between 5-10 Kw, the inverter will be obliged to connect to the distribution network. The three-phase four-wire topology is typically used for modelling the grid side. But this generalized control method is also expandable to be of higher rated power. By adopting inverter with its topology suitable for high power applications, the control method can also be used in the applications connecting to the transmission network but it requires more research. By summarizing the design procedure of the proposed voltage-sensor-less system, stability analysis was carefully carried out and is presented in the thesis.

# **Chapter 2 Current Control of Voltage Source Converter**

#### 2.1 Introduction

The current controller of a grid connected inverter is responsible for determining the switching duty of the power modules to produce the desired current waveform. A well designed current controller should be able to track the reference current without any steady state error. And the response of the controller should be swift when the command changes and the controller should also be robust in different network conditions so that the system is protected from being tripped out or damaged by the utility voltage variations. As required by various grid codes [34], the low order harmonic output is restricted and the controller should be designed without any oscillation modes with any residual harmonics in the output. The current controllers can be roughly categorised into linear and none-linear current control methods.

The select of the current control technique varies with the aims of applications. For instance, the current control of a shunt connected active filter requires a high band width tracking ability to compensate the harmonic current injected into the grid by other none-linear loads, while others such as the current control for a grid connected inverter for renewable power generation requires minimum harmonic injection. In this chapter, different current control techniques are introduced and compared. The select of the current control of the voltage-sensor-less control system are made based on this comparison.

Differing from linear current control method, a distinct characteristic of the none-linear current control method is that the switching duty is directly generated by the controller to drive the power modules. On one hand, this characteristic often comes with none constant switching frequency which could result in the low order harmonic injection which is not desirable. On the other hand, the none-linear current control methods are often free from controller

bandwidth restriction as the switching duty is directly controllable which lead to a faster response and robustness. As the linear current control method has the output of the current error compensation algorithm feeding into a separate gate signal generator, which is often a PWM signal generator, a constant switch frequency can be achieved to prevent the low order harmonic injection. In this research, the full control scheme proposed benefits from both the linear and none-linear current control. A summary of different types of current controllers is provided in this chapter for overviewing the existing techniques and explaining the selection for the current controller in this research.

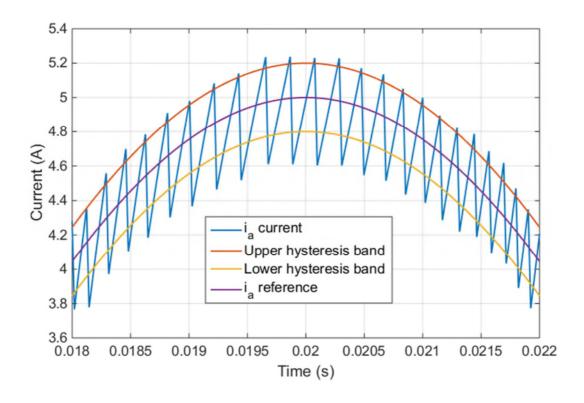

### 2.2 None-linear current control: hysteresis control

Hysteresis current control is classified as a none-linear current control method. It directly controls the switching duty of the power electronic modules to force the current output to track a desired value or waveform. Several advantages such as a higher stability margin and the better tracking ability over other current control methods have been reported in [58, 59]. Moreover, fixed-band hysteresis current control has a very simple controller algorithm and small computational burden yet it has another advantage. This control method does not introduce any voltage feed-forward to minimise the transient response. During normal operation, the grid voltage is only sampled for generating correct current reference to achieve a desired power. Therefore, it is potentially very useful in cases when the grid voltage is not available while the current should be limited in order to protect the power electronic devices e.g. start-up of the a.c. voltage-sensor-less control of the VSI.

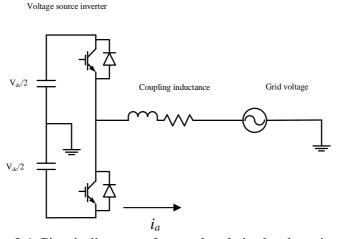

The principle of hysteresis current control is simple, applying the assumption that the d.c. link voltage are sufficiently higher than the peak to peak value of the utility a.c. voltage (line-line) so that the switching action always achieves its desired effect. This is shown in Figure 2.1. The

sampled current values are compared with the current reference. When the sampled current is shown to be smaller than the current reference, a signal to turn on the upper switch (after turning off the lower switch) of the phase-leg is given to raise the current. Similarly a signal to turn on the lower switch of the phase-leg (after turning off the upper switch) is given for bringing down the current when it is above the current reference. It is obvious that the update of the switching state is synchronised to the sampling process. Ideally, with an infinite sampling and switching rate, this mechanism is able to control the current to track its reference value without error. However, in practical applications this is hardly achievable. Firstly, the state of conduction or blocking of power electronics devices will not change instantly due to the physical nature of the devices. Secondly a dead-band is introduced to protect the upper and lower arms from shorting-through the d.c. link. Therefore a delay of turning on the in-coming device is introduced. Thirdly, the switching frequency of the power modules cannot be infinitely high by considering the switching losses. For analogue controllers, the noise problem would degrade their performance and hence they are not considered. Due to these reasons, the current reference usually sits within a tolerance range for finite switching rate [60]. This is known as the hysteresis band, and the control strategy is illustrated in Figure 2.2.

Figure 2.1 Circuit diagram of a two-level single-phase inverter

Figure 2.2 Illustration of current hysteresis control

The draw-back of fixed-band hysteresis current control is well known as the production of a wide range of harmonic frequency components, which makes the filter design difficult. For the fixed band hysteresis control, due to change of the grid voltage within a fundamental cycle, the voltage drop across the coupling impedance is not constant and this makes the current rise/drop to have different rates at different time points. The sample will not be naturally locked to the event that the current value passes the hysteresis band. During the time that the current value is between the upper and lower hysteresis band, the states of the switching devices are held. The hysteresis band should be designed taking the coupling impedance, the sampling rate on the control board and the d.c. as well as a.c. side voltage into consideration to minimise the difference of the number of samples among the switch duty updates so that the switching frequency is approximately constant.

Given the 2-level converter topology, the output voltage at the input terminal of the filter should be either  $+V_{dc}/2$  or  $-V_{dc}/2$ , with respect to the d.c. neutral. As the switching frequency of the

hysteresis control is not constant but dependent on the operating conditions, the terminal voltage cannot be ensured to be zero sequence free. This results in the interference between phases. The current flow through each phase is no longer decided by the load and the phase voltage in this phase but is also subjective to the effect of the line voltage. In [61], the effect of the phase interference is evaluated and improvement to the hysteresis switching aiming at constant switching frequency is made. However, for many control systems, the load or grid parameters could be essential but are usually hard to be obtained; the methods increase the complexity of the control system configuration.

The well-known drawback of the fixed-band hysteresis current control, i.e. the unpredictable harmonic content which makes the filter design difficult, is due to the unequal duration of each switching duty update and this is caused by voltage drop variation as illustrated above. Ideally, switching duty updates should be made on a regular basis. Although many methods were proposed to provide some the harmonic rejection features for current hysteresis control [58, 62, 63], these methods are mostly trying to adjust the hysteresis band by a.c. source voltage or prediction from the VSI output. By adjusting the hysteresis band, a more constant switching frequency can be achieved. The methods rely on the voltage measured at the PCC which is not desired in this research because the use of the voltage sensors will be eliminated. Some of the methods above aim at working out a predictive scheme to minimise the switching frequency variation at a cost of increasing the sampling frequency instantaneously to as high as 300 kHz [58], which is not realistic in many high power applications. Such controllers may increase the cost of building the power control system hardware and therefore they are not considered any further.

### 2.3 Linear current control methods

The linear current control methods have been widely used for better performance in terms of reduced low order harmonic injection as compared to the non-linear current control methods, such as the current hysteresis control described above. The current control algorithms to generate the voltage command signals have been developed based on many different models. The performance of the current control algorithm directly affects the control quality of the VSI system and thus needs to be examined. In this chapter, the current control algorithms are compared and discussed in terms of their stability, speed and accuracy.

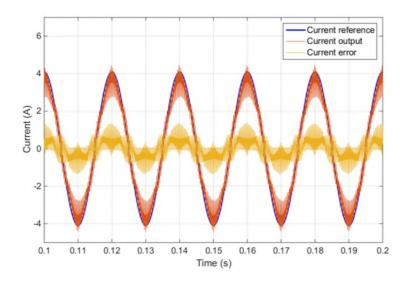

### 2.3.1 Ramp comparison current control

The PI controllers are widely used in many control tasks and the simplest way to use such a controller for VSI current control purpose is the method known as ramp comparison current control. The error between the phase current and its reference is directly feed into the PI controller to generate the voltage command signals, aiming at driving the error towards zero. A voltage feed-forward term is often applied to the command signals in order to minimise the transients in response. Then the gate signals are generated depending on the method selected such as SVPWM and SPWM. However, this technique is usually insufficient due to the inherent tracking error associated with the PI regulator tracking a sinusoidal signal, unless a controller structure of a higher rank is designed [64]. The structure of a PI controller for current control, in the phase or *abc* reference frame, is shown in Figure 2.3.

As the error between the current reference and the phase current feedback can be sinusoidal in the natural *abc* reference frame, the output of the PI controller has a phase delay compareing to the original error. The output of the PI controller as a voltage compensation will result in the current compensation further being delayed due to the coupling inductance. In the steady state,

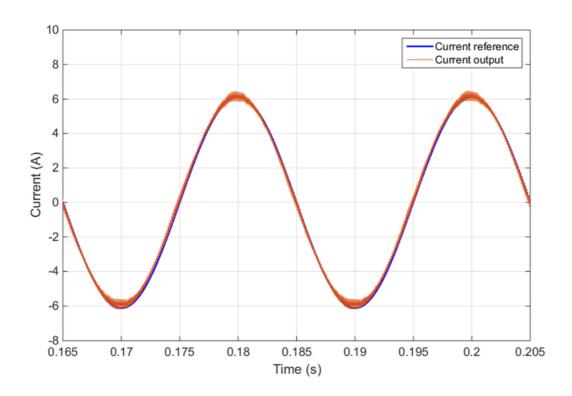

an inherent tracking error will be clearly visible in the ramp comparison current control. Furthermore, the ramp comparison current control is seemingly simple but comparing to the dq-decoupled control (to be explained next) and the proportional-resonance (PR) current controller on the alpha-beta reference frame, more control actions are needed. Thus the cost effectiveness of such a simple PI controller in term of the computational power is not attractive. This conclusion has been verified by several different studies. Figure 2.4 shows the simulation results of a PI based ramp comparison current control, with significant tacking errors.

Figure 2.3 System diagram of ramp comparison current control

Figure 2.4 Tracking error of the ramp comparison current control

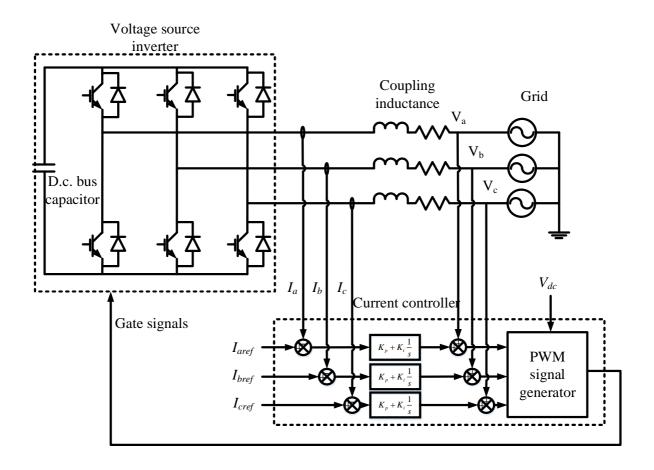

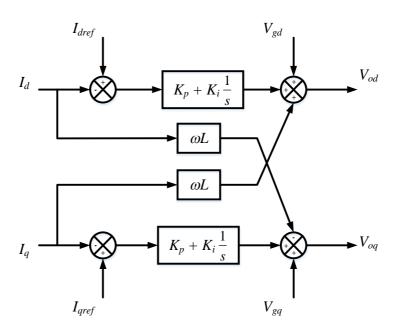

## 2.3.2 Dq-decoupled current control

The dq-decoupled control is the most widely used current controller structure. It also utilizes the PI algorithm in the control scheme but it has several advantages over the ramp comparison current control. Conventionally, the balanced three phase voltage signals are transformed into the direct and quadrature axes using the dq transformation. Through this transformation, all three phase sinusoidal signals are represented by the corresponding direct and quadrature axes components. For an ideally balanced three-phase utility grid voltage, the direct and quadrature components are constant or d.c. values, while the dq reference frame rotates at the synchronous speed with respect to the abc reference frame. A synchronous reference frame based phase locked loop (SRF-PLL) [65-67] can be utilized to track the necessary phase angle and amplitude as well as the frequency for the downstream control stages. By applying the SRF-PLL, the dq rotating reference frame is defined according to the grid voltage vector. The dq transformation is also applied to the current signals. The direct and quadrature components of the current are the vector projections to the dq reference frame defined by the reference grid

voltage vector. The controller stricture is shown in Figure 2.5. In the steady state, the current signals  $i_d$  and  $i_q$  are also d.c. values. As the control signals (commands) for the PI controller in the dq-decoupled current control scheme are d.c. values, the current control can be done accurately using a PI algorithm without steady state error. The current references for  $i_d$  and  $i_q$  could be generated from the desired real and reactive power by the power control algorithm based on the input condition and the utility voltage [68-71]. By changing the  $i_d$  and  $i_q$  references, the real and reactive power at the receiving end can be controlled independently.

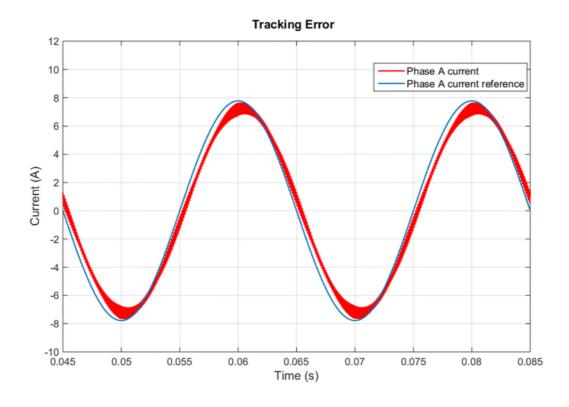

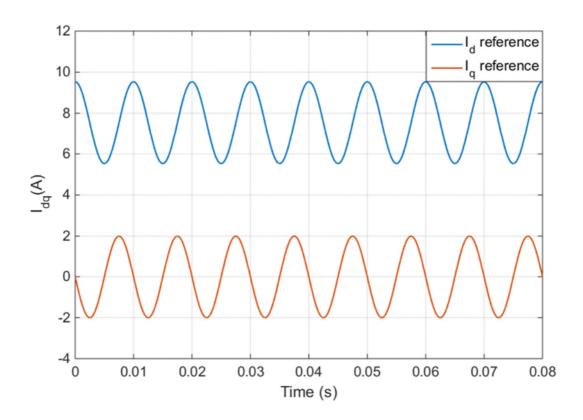

In this way, the VSI system can be usually regarded as a second order system and the optimisation of such a system is well established in control theory [64]. The optimum response can be achieved by adjusting the proportional and integral control gains. The detailed discussion of the tuning procedure of the current controller, as applied in this study, will be provided in Chapter 5. Figures 2.6 and 2.7 show the simulation results of the dq-decoupled current control tracking different reference. Figure 2.8 shows the sinusoidal reference under which, the current response is shown as in Figure 2.7.

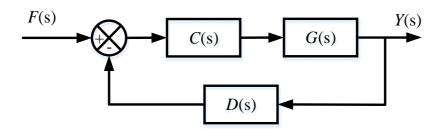

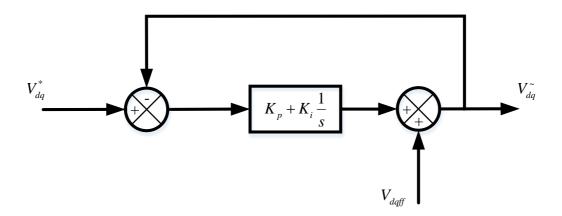

Figure 2.5 Dq-decoupled current controller structure