## **Durham E-Theses**

# Reasoning about Locks and Transactions in Concurrent Programs

BARNETT, GRANVILLE

#### How to cite:

BARNETT, GRANVILLE (2014) Reasoning about Locks and Transactions in Concurrent Programs, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/10573/

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- $\bullet \;$  the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

# Reasoning about Locks and Transactions in Concurrent Programs

### Granville Barnett

School of Engineering and Computing Sciences

**Durham University**

A thesis submitted for the degree of

$Doctor\ of\ Philosophy$

2013

# Contents

| C  | onter              | ats                            | i |

|----|--------------------|--------------------------------|---|

| Li | st of              | Figures                        | V |

| N  | omer               | nclature xvii                  | i |

| 1  | Intr               | oduction                       | 1 |

|    | 1.1                | Background                     | 1 |

|    | 1.2                | Motivation                     | 2 |

|    | 1.3                | Objectives                     | 4 |

|    | 1.4                | Challenges                     | 5 |

|    | 1.5                | Contributions                  | 7 |

| 2  | ${ m Lit}\epsilon$ | erature Review 29              | 9 |

|    | 2.1                | Programming Languages          | O |

|    | 2.2                | Locks and Transactional Memory | 7 |

|    | 2.3                | Memory Consistency Models      | 0 |

|    | 2.4                | Summary                        | 4 |

| Ι | Dy                   | ynamic Reasoning                  | 66         |

|---|----------------------|-----------------------------------|------------|

| 3 | Inti                 | roduction                         | 69         |

|   | 3.1                  | Actions                           | 69         |

|   | 3.2                  | Action Indivisibility             | 70         |

|   | 3.3                  | Locks or Transactions             | 73         |

|   | 3.4                  | Locks and Transactions            | 76         |

|   | 3.5                  | Summary                           | 80         |

| 4 | $\operatorname{Pro}$ | gramming Model                    | 81         |

|   | 4.1                  | Programming Language              | 81         |

|   | 4.2                  | Operational Semantics             | 83         |

|   | 4.3                  | Summary                           | 121        |

| 5 | Mo                   | verness of Locks and Transactions | 130        |

|   | 5.1                  | Overview                          | 130        |

|   | 5.2                  | Linearisation Points              | 132        |

|   | 5.3                  | Moverness                         | 139        |

|   | 5.4                  | Summary                           | 149        |

| 6 | Gua                  | aranteed Transactions             | <b>151</b> |

|   | 6.1                  | Overview                          | 151        |

|   | 6.2                  | Rules                             | 164        |

|   | 6.3                  | Moverness                         | 169        |

|   | 6.4                  | Applying Guaranteed Transactions  | 172        |

|   | 6.5                  | Summary                           | 178        |

| II | St   | tatic Reasoning                             | 180        |

|----|------|---------------------------------------------|------------|

| 7  | Intr | oduction                                    | 183        |

|    | 7.1  | Isolation                                   | 183        |

|    | 7.2  | Isolation of Concurrently Issued Accesses   | 184        |

|    | 7.3  | Example                                     | 186        |

|    | 7.4  | Summary                                     | 188        |

| 8  | Pro  | gramming Model                              | 190        |

|    | 8.1  | Programming Language                        | 190        |

|    | 8.2  | Summary                                     | 193        |

| 9  | Mer  | nory and Memory Accesses                    | <b>194</b> |

|    | 9.1  | Memory                                      | 194        |

|    | 9.2  | Memory Accesses                             | 200        |

|    | 9.3  | Summary                                     | 204        |

| 10 | Stat | cic Execution Rules and Isolation Algorithm | <b>205</b> |

|    | 10.1 | Static Execution Rules                      | 205        |

|    | 10.2 | Isolation Algorithm                         | 220        |

|    | 10.3 | Summary                                     | 226        |

| 11 | Sun  | nmary & Conclusions                         | <b>228</b> |

|    | 11.1 | Summary                                     | 228        |

|    |      | Conclusions                                 |            |

| A  | Algo | orithm Definitions                          | <b>232</b> |

|    | A.1  | Types                                       | 232        |

#### CONTENTS

|    | A.Z   | Algorithm Definitions for Operational Semantics  | 230         |

|----|-------|--------------------------------------------------|-------------|

|    | A.3   | Algorithm Definitions for Static Execution Rules | 248         |

|    | A.4   | Algorithm Definitions for Isolated?              | 260         |

| В  | Exa   | mple Applications of Part II's Static Framework  | <b>27</b> 3 |

| Re | efere | nces                                             | 295         |

# List of Figures

| 1.1 | A vertically scaled program describes its computation as a linear               |   |

|-----|---------------------------------------------------------------------------------|---|

|     | sequence of commands. This linear sequence can only utilise a                   |   |

|     | single PE, irrespective of whether the other PEs of the CMP are                 |   |

|     | being utilised                                                                  | 3 |

| 1.2 | A horizontally scaled program describes its computation as a series             |   |

|     | of partitioned tasks. A task is defined by a linear sequence of                 |   |

|     | commands. Tasks can be executed by the available PEs of the CMP.                | 3 |

| 1.3 | Three threads contend utilisation of the CMP's two PEs. Threads                 |   |

|     | $1\ \mathrm{and}\ 2$ are scheduled to utilise the CMP by the operating system's |   |

|     | thread scheduler; Thread 3 is placed in the wait queue                          | 6 |

| 1.4 | Incrementing x's value: load x pushes x's current value onto the                |   |

|     | evaluation stack; push_int 1 pushes the integer literal 1; add pops             |   |

|     | the two values on the stack and pushes the result of its addition;              |   |

|     | store pops the value off the stack and stores it in x                           | 7 |

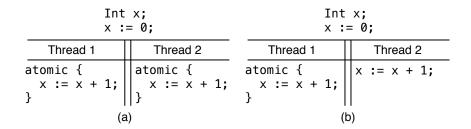

| 1.5  | (a) Threads 1 and 2 increment the shared variable ${\tt x}$ . The double           |    |

|------|------------------------------------------------------------------------------------|----|

|      | bars    denote the commands are executed concurrently. (b) Is                      |    |

|      | the instruction representation of (a). Instructions are executed as                |    |

|      | described in Figure 1.4. Each thread has its own evaluation stack.                 | 8  |

| 1.6  | Scheduling of Figure 1.5 (b) that leads to a data race on $x$ . Thread             |    |

|      | 1 reads 0 as the value of $x$ , then is preempted; Thread 2 reads 0                |    |

|      | as the value of ${\tt x}$ and subsequently increments and writes 1 to ${\tt x}$ in |    |

|      | shared memory; Thread 1 resumes execution and writes 1 to $\mathbf{x}$             | 8  |

| 1.7  | Using locks to remove the data race in Figure 1.5 (a)                              | 10 |

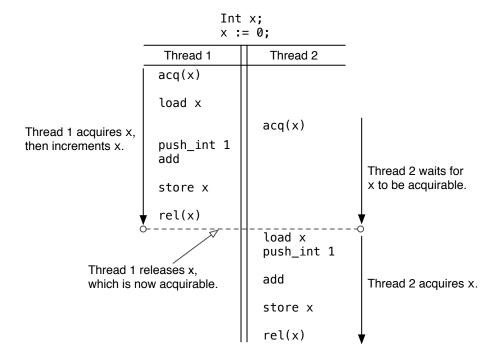

| 1.8  | A scheduling of the instructions that represent Figure 1.7. Acqui-                 |    |

|      | sition (acq) and release (rel) of x results in its increments being                |    |

|      | serialised. The final value observed for $\mathbf{x}$ is $2.$                      | 10 |

| 1.9  | The increments of $\mathbf{x}$ are not isolated. Thread 1 issues its write of      |    |

|      | x while protected on x; thread 2 writes x irrespectively                           | 12 |

| 1.10 | The increments of ${\tt x}$ are not serialised as each thread uses a differ-       |    |

|      | ent mutex to isolate its write of $x$                                              | 12 |

| 1.11 | (a) The locks of threads 1 and 2 acquire <b>x</b> and <b>y</b> in reverse orders.  |    |

|      | (b) A possible scheduling of (a): thread 1 acquires x; thread 2                    |    |

|      | acquires y; thread 1 tries to acquire y but fails as thread 2 has it               |    |

|      | acquired; thread 2 tries to acquire <b>x</b> but fails as thread 1 has it          |    |

|      | acquired. Consequently, threads 1 and 2 block indefinitely. That                   |    |

|      | is, neither thread proceeds in its execution                                       | 13 |

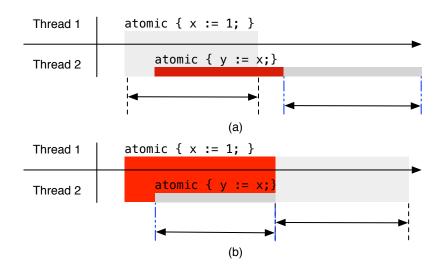

| 1.12 | (a) Transactions are used to isolate the increments of ${\tt x}$ by threads        |    |

|      | 1 and 2. (b) Transactional accesses are only isolated with other                   |    |

|      | transactional accesses                                                             | 15 |

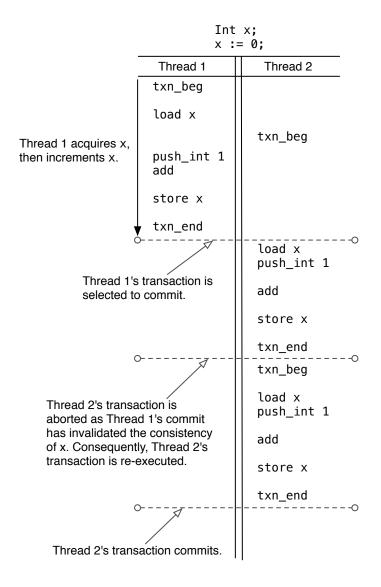

| 1.13 | A possible scheduling of Figure 1.12 (a). txn_beg and txn_end are                 |    |

|------|-----------------------------------------------------------------------------------|----|

|      | instructions that delimit transactional regions of program text                   | 16 |

| 1.14 | (a) Reads of ${\tt x}$ are always serialised due to the pessimism of locks.       |    |

|      | (b) Reads of ${\tt x}$ are not serialised should they be scheduled concur-        |    |

|      | rently                                                                            | 18 |

| 1.15 | Threads 1, 2 and 3 access ${\tt x}$ . Threads 1 and 2 only read ${\tt x}$ so they |    |

|      | acquire a read lock. By contrast, thread 1 writes ${\tt x}$ so it acquires        |    |

|      | a write lock. Threads 1 and 2 can execute concurrently; if thread                 |    |

|      | 1 has acquired the write lock then only it can execute – threads $2$              |    |

|      | and 3 will block until thread 1 releases the write lock                           | 19 |

| 1.16 | (a) Fine-grained: mutexes associated with ${\tt v}$ and ${\tt x}$ are acquired    |    |

|      | to perform the assignment. (b) Coarse-grained: a single mutex is                  |    |

|      | used to protect accesses on $v$ and $x.\ .\ .\ .\ .$                              | 19 |

| 1.17 | (a) Composes the add and pop operations of the LinkedLists 11                     |    |

|      | and 12. (b) Attempts to compose the operations in a thread-safe                   |    |

|      | manner. (c) Uses transactions to safely compose the operations                    | 20 |

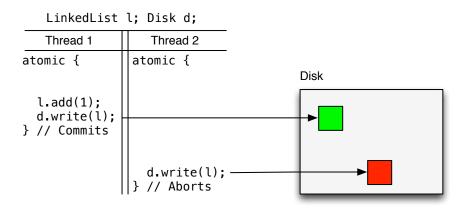

| 1.18 | Using locks to safely execute an irreversible I/O operation                       | 21 |

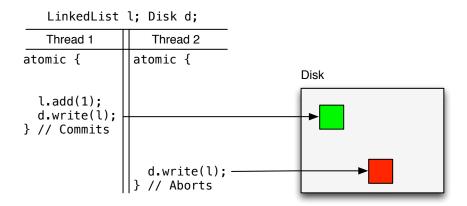

| 1.19 | Using transactions to execute an irreversible I/O operation. Thread               |    |

|      | 2's transaction aborts but its write to disk remains. Thread 2's                  |    |

|      | transaction has invalidated the atomicity and consistency guaran-                 |    |

|      | tees                                                                              | 22 |

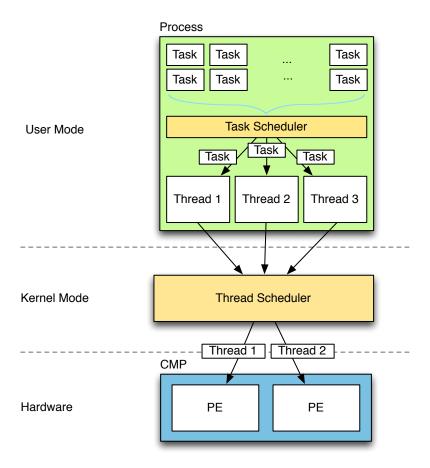

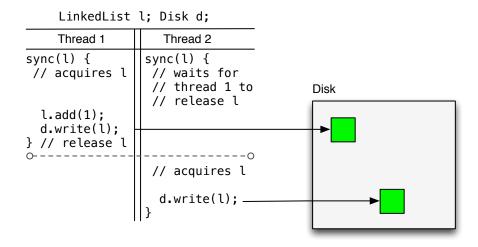

| 2.1  | High-level architecture of a process that uses tasks                              | 34 |

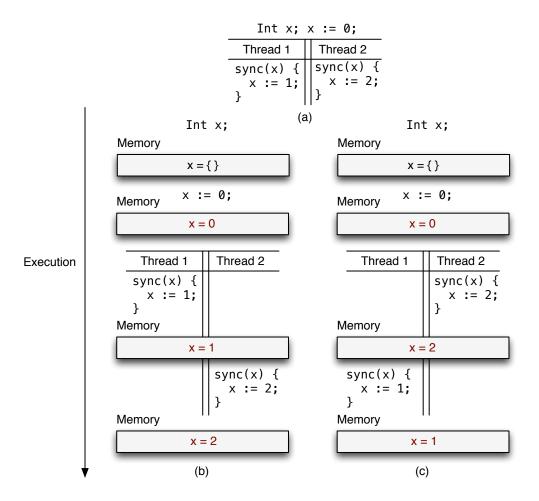

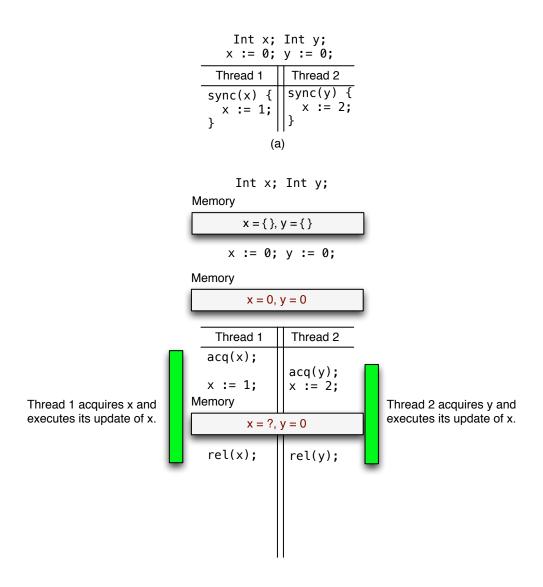

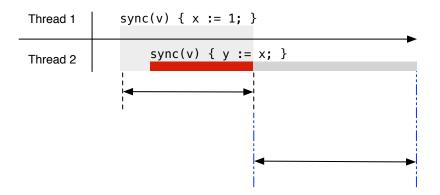

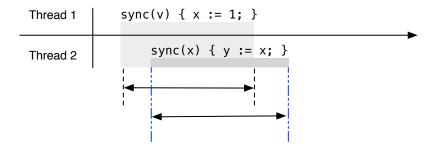

| 2.2 | (a) sync(x) { } denotes an explicit lock protected on x. Two                    |    |

|-----|---------------------------------------------------------------------------------|----|

|     | threads update the value of $\mathbf{x}$ ; each update is protected on the      |    |

|     | mutex associated with $\mathbf{x}$ . (b) and (c) show the possible thread       |    |

|     | schedules                                                                       | 39 |

| 2.3 | A possible scheduling that leads to the ordering in Figure 2.2 (b).             |    |

|     | We use the pseudo instructions acq and rel to denote acquire and                |    |

|     | respectively release operations of the mutex associated with ${\tt x.}$         | 41 |

| 2.4 | (a) The writes of <b>x</b> are protected on different mutexes. (b) A            |    |

|     | possible scheduling of (a). Each thread's write of ${\tt x}$ can occur          |    |

|     | concurrently, leading to a data race on $\mathbf{x}.$                           | 42 |

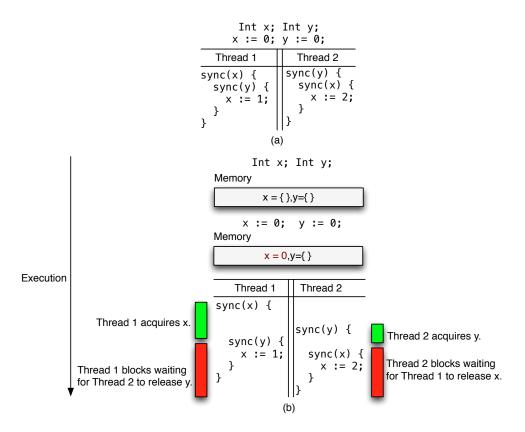

| 2.5 | (a) Each thread acquires the mutexes associated with ${\tt x}$ and ${\tt y}$ in |    |

|     | the opposite order to the other thread. (b) A possible schedule                 |    |

|     | that leads to deadlock. Here, thread 1 acquires ${\tt x}$ then thread 2         |    |

|     | acquires y. Neither thread can make any progress as each thread                 |    |

|     | is waiting on the other thread to release their mutex. For this                 |    |

|     | scheduling the value of $\boldsymbol{x}$ will remain 0                          | 43 |

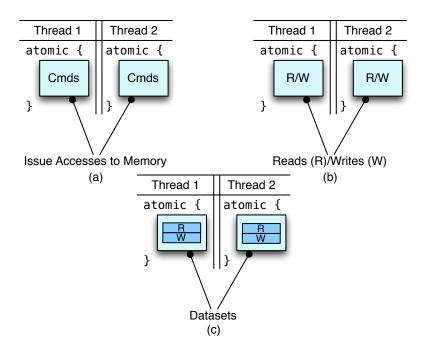

| 2.6 | Abstract view of transactional accesses to memory. (a) A transac-               |    |

|     | tion entails a number of commands to execute. (b) Each command                  |    |

|     | to be executed by a transaction issues a sequence of reads and                  |    |

|     | writes to memory. (c) The set of memory locations a transaction                 |    |

|     | accesses is known as its dataset                                                | 48 |

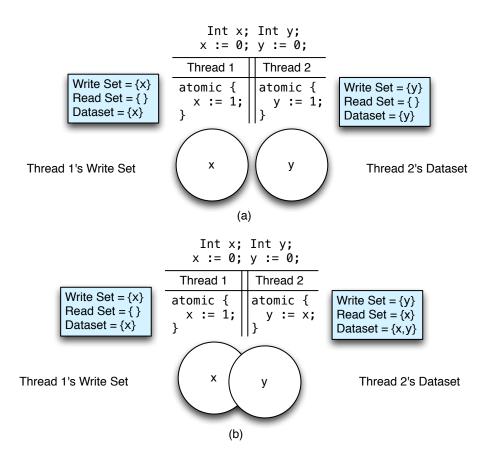

| 2.7 | (a) The write set of thread 1's transaction does not intersect with             |    |

|     | the dataset of thread 2's transaction. (b) The write set of thread              |    |

|     | 1's transaction intersects: only one of the two transactions may                |    |

|     | commit                                                                          | 49 |

| 2.8  | (a) Thread 1's transactional write of ${\tt x}$ is selected to commit.               |    |

|------|--------------------------------------------------------------------------------------|----|

|      | Thread 2's transactional read of x is aborted and subsequently                       |    |

|      | re-executed, upon which it observes 1 for the value of x. (b) Is                     |    |

|      | the reverse of (a). Thread 2's transactional read of ${\tt x}$ observes 0            |    |

|      | as its value. Thread 1's transactional write of $\mathbf{x}$ is aborted and          |    |

|      | subsequently re-executed                                                             | 50 |

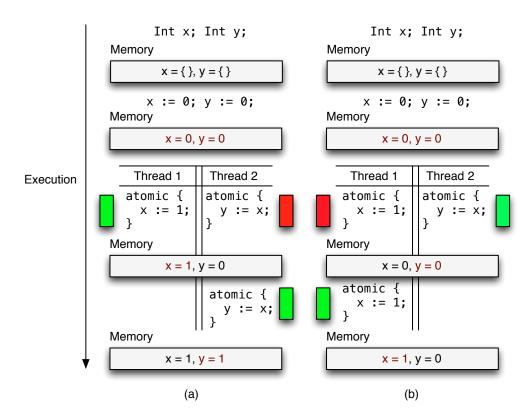

| 2.9  | (a) Upon execution of the program the following assertion holds for                  |    |

|      | the final values for $x$ and $y$ : $x = 1 \land (y = 0 \lor y = 1)$ . The assertion  |    |

|      | that models the final values for (b) is $x = 1 \land (y = 0 \lor y = 1 \lor y =?)$ . | 51 |

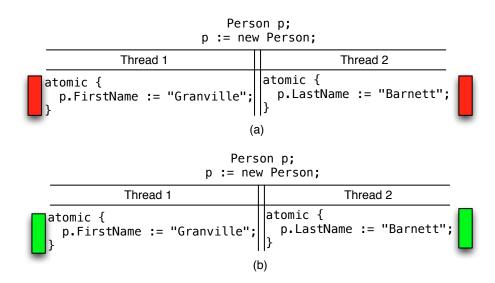

| 2.10 | (a) Under an object STM the accesses to FirstName and LastName                       |    |

|      | result in a conflict as they are both fields of the same object.                     |    |

|      | (b) An address-based STM treats the accesses to FirstName and                        |    |

|      | ${\tt LastName}$ distinctly as they occupy distinct regions of memory                | 52 |

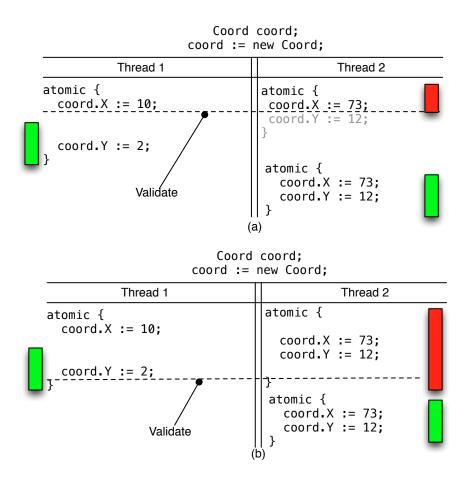

| 2.11 | (a) Employs incremental validation at per-transactional command                      |    |

|      | granularity. Thread 2's transaction is selected to abort. Here,                      |    |

|      | thread 2's transaction does not execute the doomed write of Y. (b)                   |    |

|      | Uses pre-commit validation. The conflict during the transactional                    |    |

|      | execution of the accesses to coord are only observed upon pre-                       |    |

|      | commit                                                                               | 54 |

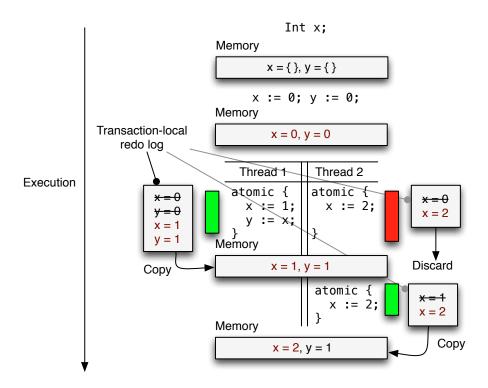

| 2.12 | Out-of-place update. Each transaction maintains a private $redo$                     |    |

|      | $\log$ . The redo log encapsulates the effect of a transaction. A trans-             |    |

|      | action that commits replays its redo log to main memory. After                       |    |

|      | this so-called replay the effect of a committed transaction is observ-               |    |

|      | able by the other threads of the program. Aborting transactions                      |    |

|      | discard their redo logs                                                              | 55 |

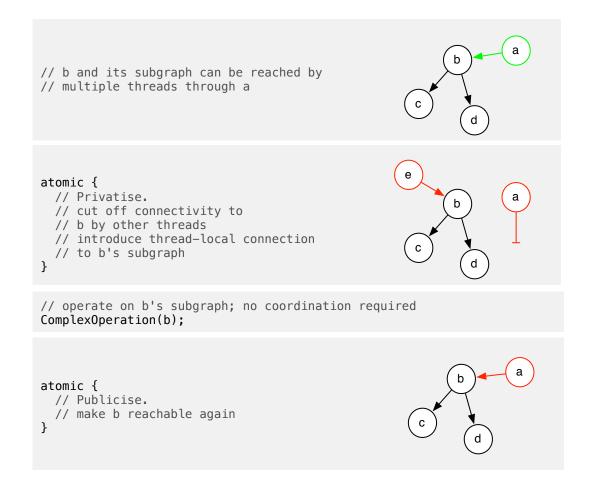

| 2.13 | Privatising and publicising <b>b</b> and its subgraph using transactions.                                           | 58 |

|------|---------------------------------------------------------------------------------------------------------------------|----|

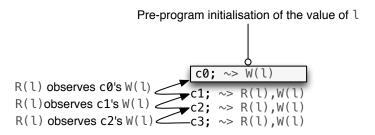

| 2.14 | Program Order. R and W are used to denote read and respectively                                                     |    |

|      | write. For example, R(1) indicates a read of 1. Each command                                                        |    |

|      | issues a sequence of reads and writes upon its execution. c1's read                                                 |    |

|      | observes the write of $1$ by $c0$ , $c2$ 's read observes the write by $c1$ ,                                       |    |

|      | and so on                                                                                                           | 62 |

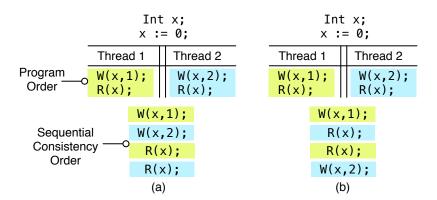

| 2.15 | Thread 1's instructions are coloured green; thread 2's blue. $\mathtt{W(x,1)}$                                      |    |

|      | writes 1 to x. For thread 1 we have $W(x,1) \xrightarrow{po} R(x)$ and for thread                                   |    |

|      | 2 W(x,2) $\xrightarrow{po}$ R(x). (a) is valid under SC as W(x,1) $\xrightarrow{sc}$ R(x) $\xrightarrow{sc}$        |    |

|      | $\mathbb{W}(x,2) \xrightarrow{sc} \mathbb{R}(x)$ preserves each thread's $\xrightarrow{po}$ . By contrast, (b) does |    |

|      | not as thread 2's read of ${\tt x}$ occurs before its write of ${\tt x}$ , which goes                               |    |

|      | against the ordering of these two instructions in thread 2's PO                                                     | 63 |

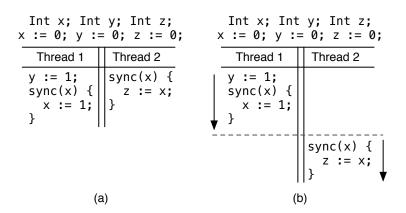

| 2.16 | (a) Thread 1 writes ${\tt x}$ and thread 2 reads ${\tt x}$ . (b) a DRF scheduling                                   |    |

|      | of (a) according to the JMM. Here, thread 1 and 2's accesses of ${\tt x}$                                           |    |

|      | are ordered by happens-before                                                                                       | 65 |

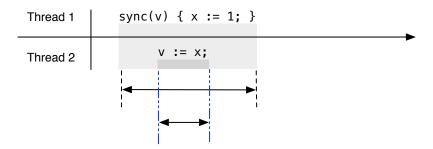

| 3.1  | Threads 1 and 2 write y but their writes may overlap in time,                                                       |    |

|      | resulting in a data race                                                                                            | 70 |

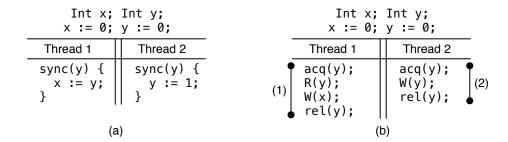

| 3.2  | (a) Each thread's access of y is protected by the same mutex.                                                       |    |

|      | Consequently, each thread's access of y is isolated. (b) Shows the                                                  |    |

|      | coversion of (a) to its synchronisation and read/write action form.                                                 |    |

|      | Due to each thread's access of t being isolated the acquire/release                                                 |    |

|      | delimited sequence of actions collapses into a single indivisible ac-                                               |    |

|      | tion. For example, if we label (1) as action $a_1$ and (2) as action $a_2$ ,                                        |    |

|      | the possible execution sequences are $a_1a_2$ or $a_2a_1$                                                           | 71 |

| 3.3 | (a) Each thread uses a different mutex to protect its access of y.         |            |

|-----|----------------------------------------------------------------------------|------------|

|     | Consequently, each thread's access of y is not isolated. (b) Due           |            |

|     | to the locks not agreeing on a mutex each thread's acquire/release         |            |

|     | delimited sequence of actions is not treated as an indivisible action.     |            |

|     | Therefore, the possible action sequence is any permutation of the          |            |

|     | four actions issued by thread 1 and the three actions issued by            |            |

|     | thread 2                                                                   | 71         |

| 3.4 | (a) Each thread's access of y is isolated as their respective accesses     |            |

|     | are issued transactionally. (b) Each transaction begin/end delim-          |            |

|     | ited sequence of actions can be treated as an indivisible action. For      |            |

|     | example, if we label (1) as the action $a_1$ and (2) as the action $a_2$ , |            |

|     | the sequences $a_1a_2$ or $a_2a_1$ are possible                            | 73         |

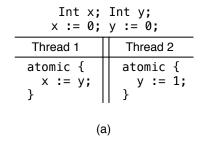

| 3.5 | Accesses of y are not isolated. The uncoordinated access of y by           |            |

|     | thread 2 results in thread 1's transactional sequence of actions not       |            |

|     | being viewed as taking effect indivisibly                                  | <b>7</b> 3 |

| 3.6 | Threads 1 and 2 access y. However, each thread's access of y is            |            |

|     | protected by a different mutex. Therefore, thread 1's read and             |            |

|     | thread 2's write of y may take place concurrently and result in a          |            |

|     | data race.                                                                 | 74         |

| 3.7  | Threads 1 and 2 compose the components a and b. Because a                |    |

|------|--------------------------------------------------------------------------|----|

|      | and <b>b</b> can be accessed by multiple threads we pessimistically com- |    |

|      | pose them with locks. The programmer working on the program              |    |

|      | text executed by thread 1 composes the isolation invariants in the       |    |

|      | sequence of acquiring a then b; the programmer who coded the pro-        |    |

|      | gram text being executed by thread 2 took the opposite approach.         |    |

|      | The result is deadlock should thread 1 acquire ${\tt a}$ and thread 2    |    |

|      | acquire <b>b</b>                                                         | 75 |

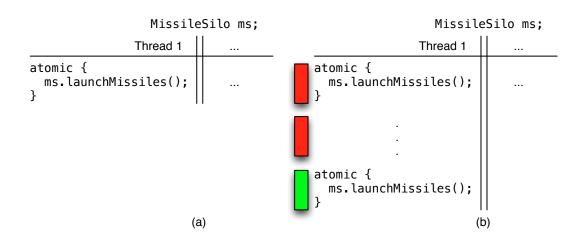

| 3.8  | (a) Thread 1 launches some missiles. Once the missiles are launched      |    |

|      | it may not be possible to have them aborted, e.g. the missles may        |    |

|      | be out of control range. This problem is exemplified in (b) where        |    |

|      | the transaction executing launchMissiles is aborted several times        |    |

|      | before it finally commits                                                | 76 |

| 3.9  | (a) Shows a program that performs the CPU bound operation of             |    |

|      | multiplying two complex matrices. In (b) the transaction executing       |    |

|      | the matrix operation is aborted several times before committing.         |    |

|      | Here, an operation which may have taken at most 100 milliseconds         |    |

|      | of CPU time ends up taking several seconds, introducing artificial       |    |

|      | contention on system resources                                           | 77 |

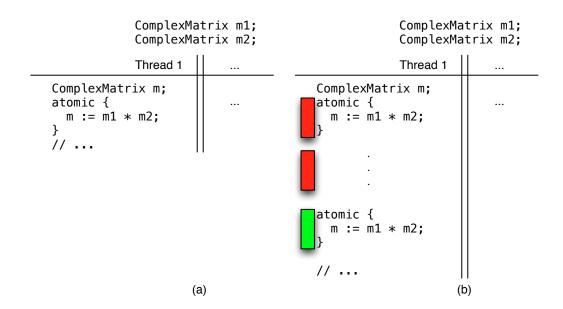

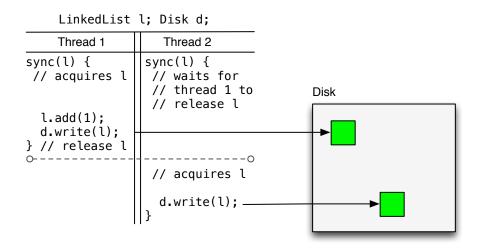

| 3.10 | Using transactions to execute an irreversible I/O operation. Thread      |    |

|      | 2's transaction aborts but its write to disk remains                     | 77 |

| 3.11 | Using locks to safely execute an irreversible I/O operation              | 78 |

| 3.12 | Locks are used to execute a CPU bound operation                          | 78 |

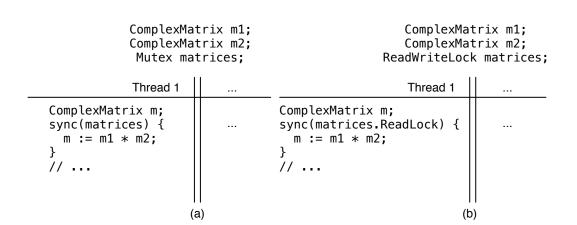

| 3.13 | (a) The programmer defines the object matrices which is to be                    |     |

|------|----------------------------------------------------------------------------------|-----|

|      | used each time an operation accesses the matrices ${\tt m1}$ and ${\tt m2}.$ The |     |

|      | lock invariant is simplified at the cost of increasing the granularity           |     |

|      | of the isolation invariant. (b) A Read/Write lock is used to opti-               |     |

|      | mise for cases when m1 and m2 are only read. Threads that only                   |     |

|      | read $m1$ and $m2$ need only acquire the read lock                               | 79  |

| 3.14 | Transactions are used to simplify component composition                          | 79  |

| 4.1  | Programming Language Abstract Syntax                                             | 82  |

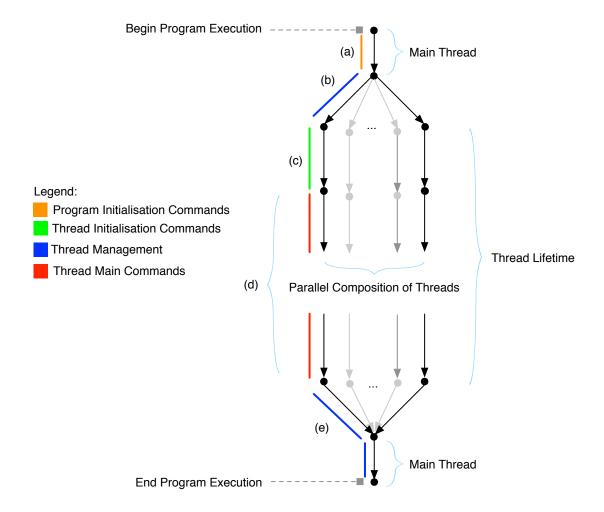

| 4.2  | Annotated program execution lifetime                                             | 84  |

| 4.3  | Abstract Syntax for Actions                                                      | 91  |

| 4.4  | Program Command Rules                                                            | 95  |

| 4.5  | The object model used by our semantics                                           | 97  |

| 4.6  | Thread Command Rules (Part I)                                                    | 100 |

| 4.7  | Thread Command Rules (Part II)                                                   | 101 |

| 4.8  | Thread Command Rules (Part III)                                                  | 102 |

| 4.9  | Thread Command Rules (Part IV)                                                   | 103 |

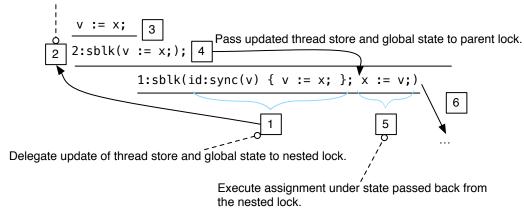

| 4.10 | The parent lock contains two commands: a write of $\mathbf{x}$ and a lock.       |     |

|      | The nested lock contains a write of v. The most nested active lock               |     |

|      | is in charge of persisting the effect of its commands. For example,              |     |

|      | the parent lock persists the write of $x$ , while the nested lock is in          |     |

|      | charge of persisting the write of $v$                                            | 110 |

| 4.11 | Unified Command Rules (Part I)                                                   | 123 |

| 4.12 | Unified Command Rules (Part II)                                                  | 124 |

| A 13 | Unified Command Rules (Part IV)                                                  | 195 |

#### LIST OF FIGURES

| 4.14 | Unified Command Rules (Part V)                                                | 126 |

|------|-------------------------------------------------------------------------------|-----|

| 4.15 | Unified Command Rules (Part VI)                                               | 127 |

| 4.16 | Abstract derivation for the delegation of state persistence for nested        |     |

|      | locks. The responsibility of state persistence is delegated to the            |     |

|      | most nested lock when executing a lock which is a child of another            |     |

|      | lock                                                                          | 128 |

| 4.17 | Parallel Composition Rule                                                     | 129 |

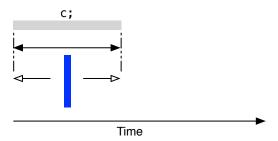

| 5.1  | The shaded box is the execution interval of c. The blue bar (the              |     |

|      | linearisation point) can be placed at any point within the bounds             |     |

|      | of c's execution interval                                                     | 133 |

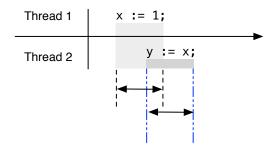

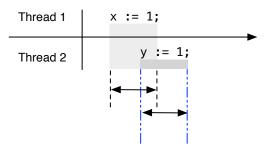

| 5.2  | The linearisation points of the commands executed by threads 1                |     |

|      | and 2 may take place concurrently, resulting in a data race on $\mathbf{x}$ . |     |

|      | This is possible because there does not exist a total ordering over           |     |

|      | the commands. $\hdots$                                                        | 133 |

| 5.3  | The linearisation points of each command can take effect concur-              |     |

|      | rently and not yield erroneous data                                           | 134 |

| 5.4  | Thread 1's lock acquires v. Consequently, the linearisation point             |     |

|      | of thread 2's lock takes place after thread 1's lock                          | 135 |

| 5.5  | Each lock protects its access of ${\tt x}$ on a distinct mutex, consequently  |     |

|      | a total ordering does not exist over the linearisation points of the          |     |

|      | locks                                                                         | 135 |

| 5.6  | The linearisation points may overlap as a total ordering does not             |     |

|      | exist over the uncoordinated and lock commands                                | 135 |

#### LIST OF FIGURES

| 5.7  | The linearisation points of the transactional commands are totally                              |     |  |  |  |

|------|-------------------------------------------------------------------------------------------------|-----|--|--|--|

|      | ordered as they conflict. Thread 2's transactional read of ${\tt x}$ will                       |     |  |  |  |

|      | observe 1                                                                                       | 136 |  |  |  |

| 5.8  | A total order does not exist over the linearisation points of trans-                            |     |  |  |  |

|      | actions which do not conflict.                                                                  | 137 |  |  |  |

| 5.9  | The linearisation points of threads 1 and 2 may overlap, resulting                              |     |  |  |  |

|      | in thread 2's read of $\boldsymbol{x}$ not observing thread 1's write of $\boldsymbol{x}.$      | 137 |  |  |  |

| 5.10 | The linearisation point of the transaction occurs after that of the                             |     |  |  |  |

|      | lock due to the stronger semantics of locks                                                     | 138 |  |  |  |

| 5.11 | The linearisation point of the lock and transaction may occur con-                              |     |  |  |  |

|      | currently due to the transaction not accessing the lock's mutex. $\ .$                          | 138 |  |  |  |

| 5.12 | (a) The linearisation point of thread 1's transaction appears to the                            |     |  |  |  |

|      | left of the linearisation point of thread 2' transaction. (b) The                               |     |  |  |  |

|      | order of linearisation points is reversed. The order of linearisation                           |     |  |  |  |

|      | points for conflicting transactions is dependent on the contention                              |     |  |  |  |

|      | manager                                                                                         | 143 |  |  |  |

| 6.1  | (a) A single mutex is used to protect accesses to x, y and z. (b)                               |     |  |  |  |

|      | The individual mutexes associated with $\mathbf{x}$ , $\mathbf{y}$ and $\mathbf{z}$ are used to |     |  |  |  |

|      | protect their respective accesses                                                               | 154 |  |  |  |

| 6.2  | Each variable has an associated read/write lock                                                 | 155 |  |  |  |

| 6.3  | Using locks and transactions                                                                    | 157 |  |  |  |

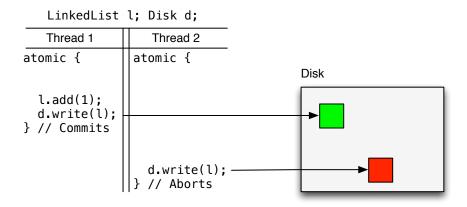

| 6.4  | Using transactions to execute an irreversible I/O operation. Thread       |     |

|------|---------------------------------------------------------------------------|-----|

|      | 2's transaction aborts but its write to disk remains. Thread 2's          |     |

|      | transaction has invalidated the atomicity and consistency guaran-         |     |

|      | tees                                                                      | 157 |

| 6.5  | Using locks to safely execute an irreversible I/O operation               | 158 |

| 6.6  | General principle of the privatisation and publication idioms. Trans-     |     |

|      | actions are used to close off and open up the reachability of a           |     |

|      | program's object graph.                                                   | 159 |

| 6.7  | Simplified application of the privatisation/publication idioms to         |     |

|      | write a linked list's contents to disk                                    | 160 |

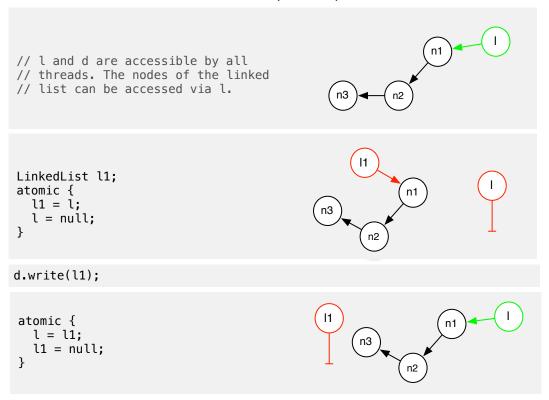

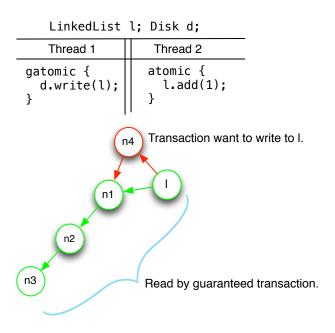

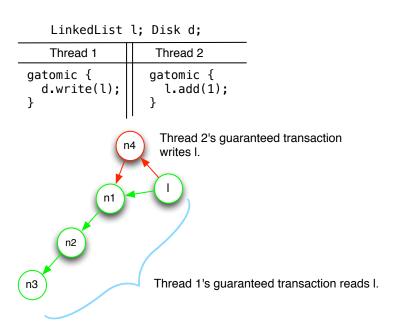

| 6.8  | The guaranteed transaction reads the memory associated with               |     |

|      | $1,n1,\ n2$ and $n3.\ 1$ is included in the transaction executed by       |     |

|      | thread 2's write set. The guaranteed transaction will force the           |     |

|      | transaction to abort should they be scheduled concurrently                | 163 |

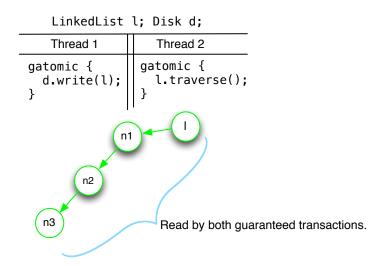

| 6.9  | The guaranteed transactions can execute concurrently as neither           |     |

|      | guaranteed transaction writes data the other guaranteed transac-          |     |

|      | tion accesses                                                             | 164 |

| 6.10 | Conflicting guaranteed transactions are totally ordered should they       |     |

|      | be scheduled concurrently                                                 | 165 |

| 6.11 | Guaranteed Transaction Command Rules                                      | 166 |

| 6.12 | Parallel Composition Rule for Transactions and Guaranteed Trans-          |     |

|      | actions                                                                   | 170 |

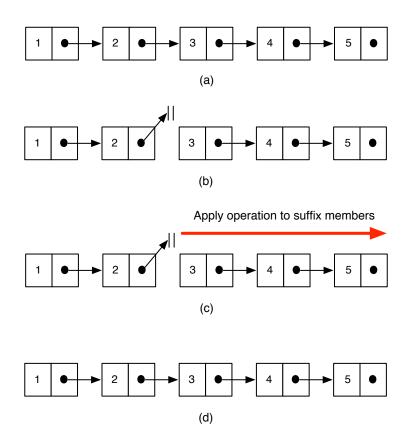

| 6.13 | (a) Instance of a singly linked list; (b) privatise list suffix at 2; (c) |     |

|      | apply an operation upon the suffix members; (d) publicise the list        |     |

|      | suffix                                                                    | 174 |

| 6.14 | Pseudo steps for attaining the semantics required for Figure 6.13                                                        |     |

|------|--------------------------------------------------------------------------------------------------------------------------|-----|

|      | using the privatisation and publication idioms                                                                           | 174 |

| 6.15 | Singly linked list entailing a privatising/publicising operation on                                                      |     |

|      | the members of a user-defined suffix. serialise_suffix mutates                                                           |     |

|      | the members of a suffix in addition to applying an irreversible                                                          |     |

|      | operation on those members via writing them to disk courtesy of                                                          |     |

|      | of Disk.Write                                                                                                            | 175 |

| 6.16 | Transactional addition of a value to an instance of LinkedList                                                           | 177 |

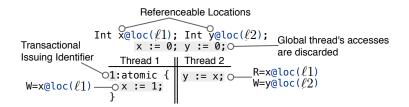

| 7.1  | A simple program annotated with the inferred memory locations                                                            |     |

|      | $(\ell 1 \text{ and } \ell 2)$ for the global variables $\mathbf{x} @ loc(\ell 1)$ and $\mathbf{y} @ loc(\ell 2)$ . Exe- |     |

|      | cution of thread 1's assignment results in a write (W) of $\ell$ 1; Exe-                                                 |     |

|      | cuting thread 2's assignment results in a read (R) of $\ell 1$ and a write                                               |     |

|      | of $\ell 2.$                                                                                                             | 186 |

|      |                                                                                                                          | 100 |

| 8.1  | Abstract Syntax of the Core Programming Language and Memory                                                              |     |

|      | Annotations                                                                                                              | 191 |

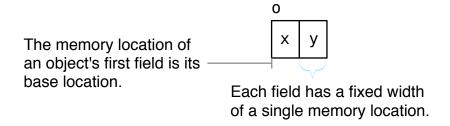

| 9.1  | A simple Point class with fields for $\mathbf{x}$ and $\mathbf{y}$ coordinates                                           | 195 |

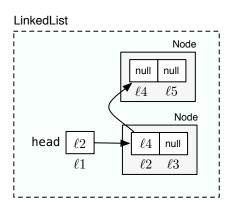

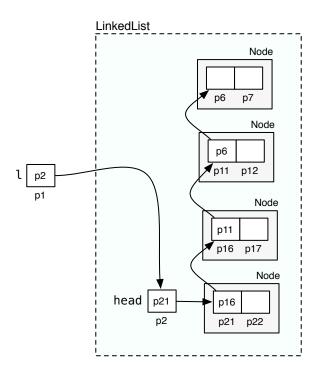

| 9.2  | An advanced application of our system. Node and LinkedList                                                               |     |

|      | classes make use of @object-space, @serialise and @iter-space an-                                                        |     |

|      | notations                                                                                                                | 197 |

| 10.1 | Static Execution Rules (Part I)                                                                                          | 210 |

| 10.2 | Static Execution Rules (Part II)                                                                                         | 211 |

| 10.3 | Static Execution Rules (Part III)                                                                                        | 212 |

| 10 4 | Static Execution Rules (Part IV)                                                                                         | 213 |

#### LIST OF FIGURES

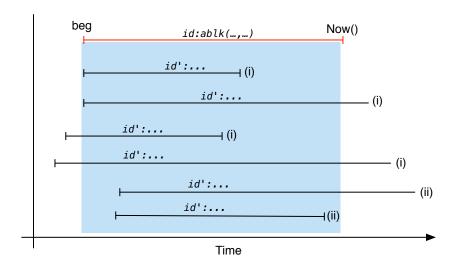

| 10.5 | Isolation Algorithm                                                  | 22  |

|------|----------------------------------------------------------------------|-----|

| B.1  | Structure of the anonymous LinkedList object. The LinkedList         |     |

|      | object is anonymous due to all literal values being discarded – only |     |

|      | the shape of the LinkedList that 1 points-to is of relevance 2       | 288 |

The research presented in this thesis is the original work of the author, unless stated otherwise. The copyright of this thesis rests with the author. No quotation from it should be published without the author's prior written consent and information derived from it should be acknowledged.

## Acknowledgements

I thank my supervisor Professor Shengchao Qin for his tutilige and support over the years. My thanks also to Professor Iain Stewart and an EPSRC Doctoral Training Award from Durham University, without which this PhD would not have been possible. I also wish to thank: Ryuta Arisaka, Professor Paul Roe, Dr Wayne Kelly, Professor John Gough, Dr Keshav Dahal, Professor Peter Cowling, Professor Chin Wei Ngan, Professor Huibiao Zhu, Dr Steven Hand, Andrew Craik, Richard Mason, Darryl Cain, Joao Ferreira, Guanhua He, Chenguang Luo, Le Duy Khanh and Mengda He.

Wariya – thank you for your love, support and patience.

$\mathit{Mum}$  – thank you for always believing in me.

#### Abstract

The aim of this thesis is to present novel techniques for reasoning about the dynamic and static semantics of concurrent programs that use locks and transactions to isolate accesses to shared memory. We use moverness to characterise the observational semantics of reads issued by locks and transactions under the simpler semantics of free, left, right and both movers. The second contribution is guaranteed transactions which are a safer alternative to locks and the privatisation/publication idioms for specific scenarios. Guaranteed transactions facilitate a simpler pessimistic coordination semantics than locks, but offer most of the conveniences that have made transactions appealing. Finally, we present a static analysis for reasoning about the isolation of a program that uses locks and transactions. If our isolation algorithm determines that all the accesses issued by a program are isolated, then the program is declared data-race-free.

# Chapter 1

# Introduction

# 1.1 Background

#### 1.1.1 Chip Multiprocessors

Failure to economically address heat dissipation in uniprocessors has resulted in industry adoption of *chip multi-processors* (CMP) [Olukotun et al., 1996]. Each CMP comprises a number of homogeneous *processing elements* (PE). By contrast to the PE found in a uniprocessor, the PEs in CMPs consume less power and dissipate less heat. Desktop PCs, laptops and most recent tablets and smart phones comprise CMPs. The transition to CMPs has a large impact on software. Designing software for the uniprocessor was relatively simple: solutions were described as a sequence of linear commands, and every other year or so the solution would receive a significant speedup [Schaller, 1997]. This sort of design under present-day hardware gains little to no speedup [Sutter and Larus, 2005]. Exploiting CMPs requires a fundamental shift in software design: instead

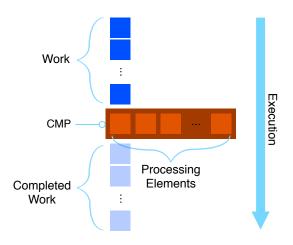

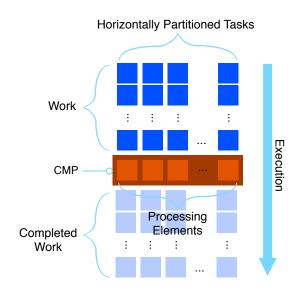

of focusing on linear execution (vertical scaling), we now focus our efforts on partitioning work into tasks which can be distributed across the PEs of a CMP (horizontal scaling). Figures 1.1 and 1.2 show vertical and respectively horizontal scaling under CMPs. The goal of horizontal scaling is relatively simple: we would like to design software in such a way that it can take advantage of all the PEs of a CMP, irrespective of whether the CMP comprises four or four hundred PEs. Software designs that embrace horizontal scaling can expect favourable speedups as CMPs with larger quantities of PEs are released. For example, an algorithm that scales horizontally can potentially run twice as fast on a CMP with four PEs than it did on a CMP with two PEs, and so on. Linear speedups such as the previous example are the gold standard for software targeting CMPs. In theory CMPs are spawning an exciting era in computing: problems that were previously the domain of supercomputing are now computationally tractable on consumer grade hardware. However, as will shortly be illustrated, the correct design of such programs using the current tools is steeped in technical idiosyncrasies, making the task of exploiting CMPs in practice a difficult and error-prone task.

#### 1.1.2 Threads

Horizontal scaling requires the use of threads [Butenhof, 1997]. Before the importance of threads can be understood we need to describe their role in modern operating systems. Let us assume we have a valid C program defined in the file program.c which has the single method main. At the moment program.c is just a text file. To create something the machine can understand we need to compile and link program.c using the command CC program.c, where CC is a C compiler.

Figure 1.1: A vertically scaled program describes its computation as a linear sequence of commands. This linear sequence can only utilise a single PE, irrespective of whether the other PEs of the CMP are being utilised.

Figure 1.2: A horizontally scaled program describes its computation as a series of partitioned tasks. A task is defined by a linear sequence of commands. Tasks can be executed by the available PEs of the CMP.

The result of the previous step is the binary image a.out. We do not need to know the detailed contents of a.out, just that it contains the machine instructions that model the high-level commands defined in program.c. To execute our program we issue a command such as ./a.out from a UNIX terminal. When we issue this command the operating system performs a number of steps: creation of a new process; assigning virtual memory to the newly created process; loading the binary image a.out into the process's memory; and creation of a main thread, so-called because it executes the user defined method labelled main. The main method is often known as being the entry point due to it being the earliest point where user defined commands are executed. Each thread entails a stack and possibly some private memory known as thread local storage. The thread's stack facilitates method calls. A process has at least one thread, otherwise it can perform no meaningful work.

#### 1.1.3 Tasks

Each PE of a CMP can execute one thread at a time. The PEs of some CMPs, such as those manufactured by Intel with Hyper-Threading [Intel, 2013a], can execute two threads at a time. Utilising the PEs of a CMP requires a program to partition its work into tasks. A task is described as a method and can be passed to a thread to execute. A process that creates multiple threads during its lifetime is said to be multi-threaded. The process that models the execution of program.c is not multi-threaded as it comprises only the main thread. That is, the process will only utilise one PE, even if several PEs of the CMP are available, just like Figure 1.1. To better utilise a CMP our process needs to create additional threads

and map tasks to those threads. The tasks delegated to these additional threads may execute *concurrently* like in Figure 1.2. That is, each PE of the CMP may execute a distinct thread of the process at the same time.

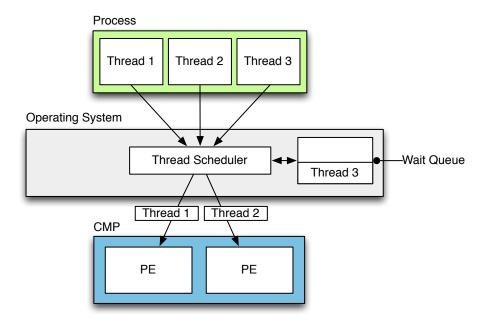

#### 1.1.4 Thread Scheduling

Typically more threads than PEs exist. The job of an operating system's thread scheduler is to map threads to PEs. There are two types of scheduling approaches: non-preemptive and preemptive. Under non-preemptive scheduling the threads of a process utilise the CMP for as long as they need to execute; however, a thread can voluntarily yield control of a PE if it wishes, e.g. it may yield while waiting for some I/O to complete. Non-preemptive scheduling is a simple model of cooperative computing but an unfair one. For example, a thread may infrequently or never yield, starving other threads from utilising the CMP. In response, most modern operating systems, including Linux, OSX and Windows, use preemptive scheduling. A preemptive scheduler generally uses time quantums and domainspecific heuristics to ensure that the PEs of a CMP are fairly shared between the threads of processes. Under preemptive scheduling each thread is given a time quantum, the maximum amount of contiguous time it may utilise a PE, and a priority. A thread implicitly yields if it terminates within its allotted time quantum. A preemptive scheduler is free at any time during a thread's utilisation of a PE to context switch it out in favour of a waiting thread. A context switch generally entails: (1) saving the state of the thread currently utilising the PE; (2) placing that thread in the waiting queue; and (3) mapping a thread from the waiting queue to the now vacant PE. The heuristics used to select the next thread

Figure 1.3: Three threads contend utilisation of the CMP's two PEs. Threads 1 and 2 are scheduled to utilise the CMP by the operating system's thread scheduler; Thread 3 is placed in the wait queue.

to run and the technical details of context switching are irrelevant. However, the fact that a thread can be usurped from utilising a PE at any time is very important. Figure 1.3 describes a scheduling scenario with three threads from the same process contending utilisation of a CMP with two PEs.

#### 1.1.5 Accessing Shared Memory

The threads created during the lifetime of a process share the process's virtual memory. We will refer to this memory as *shared memory*. Executing a thread's task results in the thread issuing a sequence of low-level instructions. These instructions are taken from the binary image a.out. For example, a thread that increments the integer value of a variable x by one, described by the high-level

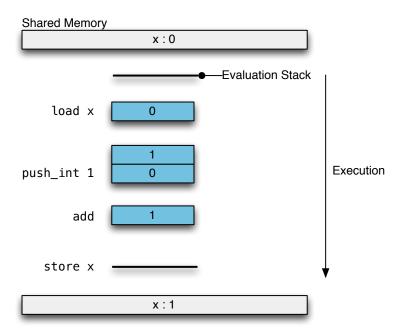

command x := x + 1, is modelled by a sequence of low-level instructions, such as the pseudo-instructions load x; push\_int 1; add; store x. Figure 1.4 shows the operation of these instructions. There are two important concepts on display here: (1) a high-level command is implemented as a sequence of instructions; and (2) these instructions may issue accesses (reads and writes) to a process's shared memory, e.g. load x reads x and store x writes x. The low-level representation of a high-level program's commands, in conjunction with the operating system's preemptive scheduling, can result in a number of program defects exclusive to multi-threaded programs.

Figure 1.4: Incrementing x's value: load x pushes x's current value onto the evaluation stack; push\_int 1 pushes the integer literal 1; add pops the two values on the stack and pushes the result of its addition; store pops the value off the stack and stores it in x.

Figure 1.5 (a) gives a program where two threads increment the value of the shared variable x. We say a variable is shared if it resides in a process's shared

| <pre>Int x; x := 0;</pre> |            | <pre>Int x; x := 0;</pre>              |                                        |

|---------------------------|------------|----------------------------------------|----------------------------------------|

| Thread 1                  | Thread 2   | Thread 1                               | Thread 2                               |

| x := x + 1                | x := x + 1 | load x<br>push_int 1<br>add<br>store x | load x<br>push_int 1<br>add<br>store x |

| (a)                       |            | (I                                     | p)                                     |

Figure 1.5: (a) Threads 1 and 2 increment the shared variable x. The double bars | | denote the commands are executed concurrently. (b) Is the instruction representation of (a). Instructions are executed as described in Figure 1.4. Each thread has its own evaluation stack.

| Int x;<br>x := 0; |                             |  |  |

|-------------------|-----------------------------|--|--|

| Thread 1          | Thread 2                    |  |  |

| load x            | load x<br>push_int 1<br>add |  |  |

| push_int 1<br>add | store x                     |  |  |

| store x           |                             |  |  |

Figure 1.6: Scheduling of Figure 1.5 (b) that leads to a data race on  $\mathbf{x}$ . Thread 1 reads 0 as the value of  $\mathbf{x}$ , then is preempted; Thread 2 reads 0 as the value of  $\mathbf{x}$  and subsequently increments and writes 1 to  $\mathbf{x}$  in shared memory; Thread 1 resumes execution and writes 1 to  $\mathbf{x}$ .

memory. Recall that each thread of a process may access the data stored in its shared memory. Figure 1.5 (b) shows the low-level representation of Figure 1.5 (a). Each instruction takes place as an indivisible step: a preemptive scheduler cannot context switch a thread while it is executing an instruction; however, it can context switch a thread that is *between* executing instructions. Figure 1.6 shows a possible concurrent scheduling of Figure 1.5 (b). Here, the scheduler tries

to fairly share the uniprocessor's single PE between two threads. The initial value of x is 0, and each thread increments x by 1, so we expect to observe 2 for x's final value. However, we observe 1. Our program has been subject to a data race [Unger, 1995]: the final value observed for x depends on the relative ordering of the instructions issued by each thread. The order that instructions are issued is dependent upon the operating system's thread scheduler. It is possible we could execute Figure 1.5 (a) several times on the same hardware and never observe 1 for x's final value. If our process comprised more threads, each incrementing x, then the set of observable final values for x increases, and the schedules that reproduce the set of incorrect values of x grows. Data races are often hard to detect, e.g. in Figure 1.6 we observed 1 for the final value of x: logically this value is incorrect, despite 1 being an integer. Data races become harder to detect when advanced data types are used, e.g. user defined classes and data types which span multiple words in size. A programmer, suspecting the presence of a data race, may seek assistance from his language's compiler and debugger. A compiler for Java and C++ will provide no help. Success may be had with a debugger but only if he has an idea of where the data race originated. Let us suppose our programmer knows where to begin his search during a debugger session: he must still deal with the preemptive scheduling of the operating system; moreover, it is possible that use of the debugger affects access contention within the attached process due to the overhead of the debugger's instrumentation code.

| <pre>Int x; x := 0;</pre>     |                               |

|-------------------------------|-------------------------------|

| Thread 1                      | Thread 2                      |

| sync(x) {<br>x := x + 1;<br>} | sync(x) {<br>x := x + 1;<br>} |

Figure 1.7: Using locks to remove the data race in Figure 1.5 (a).

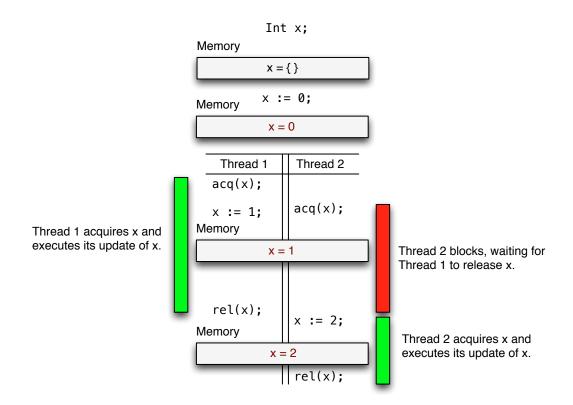

Figure 1.8: A scheduling of the instructions that represent Figure 1.7. Acquisition (acq) and release (rel) of x results in its increments being serialised. The final value observed for x is 2.

#### 1.1.6 Coordination

Preventing data races requires the use of *coordination*. When employed correctly coordination facilitates thread exclusion.

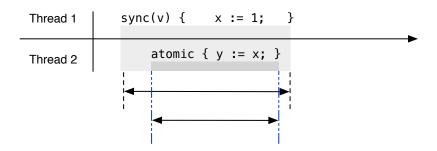

#### 1.1.6.1 Locks

Mutual exclusion is facilitated by a binary semaphore [Dijkstra, 1968]. A binary semaphore is known as a *mutex*. Let us use sync(v) { c } to mean that in order to execute the program commands c we must have acquired the mutex v; when c has completed executing v is released. A thread can acquire v if and only if another thread has not already acquired it; v becomes acquirable upon its release by the thread that currently has it acquired. Conceptually we can think of v as being released before any user defined program commands are run. That is, v is initially acquirable when the user's program text is executed. Figure 1.7 shows a version of Figure 1.5 (a) that uses the sync construct to remove the data race on x. We say that Figure 1.7 is data-race-free (DRF). Figure 1.8 shows how sync works at the instruction-level. We will refer to sync(v) { c } as a lock and permit any variable v to be used as a lock's mutex. The accesses issued by locks in distinct threads are *isolated* if and only if the locks use the same mutex. Figure 1.7 showed how easy it was to remove the data race on x; by contrast, Figures 1.9 and 1.10 show how simple it is to get locking wrong. Figure 1.9 (a) has a data race on x as thread 1 acquires x and then increments x; however, thread 2 issues its increment of x without having acquired x. Figure 1.10 (a) comprises a data race on x as each thread's lock uses a different mutex. Both Figures 1.9 (a) and 1.10 (a) are semantically equivalent to the accesses issued by Figure 1.5. A compiler will not warn the programmer of his failure to mutually exclude accesses to x, despite being obvious that was his intention.

The problem with locks is that in most languages they are a library facility [Butenhof, 1997; Oaks and Wong, 2004]. That is, a programming language does

| <pre>Int x; x := 0;</pre> |             | <pre>Int x; x := 0;</pre> |                      |

|---------------------------|-------------|---------------------------|----------------------|

| Thread 1                  | Thread 2    | Thread 1                  | Thread 2             |

| sync(x) {                 | x := x + 1; | acq(x)                    |                      |

| x := x + 1;               |             | load x                    |                      |

|                           |             | push_int 1<br>add         | load x<br>push_int 1 |

|                           |             | store x                   | add                  |

|                           |             | rel(x)                    |                      |

|                           |             |                           | store x              |

| (a                        | )           | (b                        | )                    |

Figure 1.9: The increments of x are not isolated. Thread 1 issues its write of x while protected on x; thread 2 writes x irrespectively.

| <pre>Int x; Int y;     x := 0;</pre> |             | Int x; Int y;<br>x := 0; |            |  |

|--------------------------------------|-------------|--------------------------|------------|--|

| Thread 1                             | Thread 2    | Thread 1                 | Thread 2   |  |

| sync(x) {                            | sync(y) {   | acq(x)                   |            |  |

| x := x + 1;<br>}                     | x := x + 1; | load x                   |            |  |

|                                      |             |                          | acq(y)     |  |

|                                      |             | push_int 1<br>add        | load x     |  |

|                                      |             | store x                  | push_int 1 |  |

|                                      |             | rel(x)                   | add        |  |

|                                      |             |                          | store x    |  |

|                                      |             |                          | rel(y)     |  |

| (a                                   | 1)          | (t                       | p)         |  |

Figure 1.10: The increments of x are not serialised as each thread uses a different mutex to isolate its write of x.

not semantically treat an access issued within a lock any different to one issued outside of a lock. A programmer who works on a codebase that uses locks often

relies on program comments to determine what lock or locks should be acquired before accessing a particular bit of shared memory. These comments also often describe the *order* mutexes are to be acquired in. Acquisition and release orders are very important for mutexes. Figure 1.11 (a) shows a program where each thread acquires the mutexes **x** and **y** in opposing orders. Here, the opposing acquisition orders results in a program defect known as *deadlock* [Zöbel, 1983]. For example, consider the scheduling of acquire/release's given in Figure 1.11 (b) for the program in Figure 1.11 (a). Thread 1 acquires **x** then thread 2 acquires **y**. Neither thread can make any subsequent progress until the other thread releases their respective mutex. Unfortunately, neither thread can release their mutex until the other thread releases theirs. Both thread's will never make any further progress. Deadlock can be considered a simpler defect to diagnose than a data race. For example, in a debugger session we can observe that threads 1 and 2 are making no progress.

### 1.1.6.2 Software Transactional Memory

Software transactional memory (STM) [Shavit and Touitou, 1995] is another form of coordination. Under STM we issue accesses to shared memory using a transaction. A transaction in STM is similar to a transaction under a relational database management system (RDBMS). A transaction under a RDBMS exhibits the following properties: Atomicity – the effect of a transaction appears to take effect as a single step or not at all; Consistancy – only committed transactions contribute their effect to the underlying store; Isolation – transactional accesses are isolated with respect to other transactional accesses; and Durability – the underlying store persists, irrespective of whether the program executing the transaction

| <pre>Int x; Int y;</pre>                              |                                                       | <pre>Int x; Int y;</pre> |                   |  |

|-------------------------------------------------------|-------------------------------------------------------|--------------------------|-------------------|--|

| Thread 1                                              | Thread 2                                              | Thread 1                 | Thread 2          |  |

| <pre>sync(x) {     sync(y) {         //     } }</pre> | <pre>sync(y) {     sync(x) {         //     } }</pre> | acq(x)<br><br>acq(y)     | acq(y)            |  |

| (ε                                                    | a)                                                    |                          | acq(x)<br><br>(b) |  |

Figure 1.11: (a) The locks of threads 1 and 2 acquire x and y in reverse orders. (b) A possible scheduling of (a): thread 1 acquires x; thread 2 acquires y; thread 1 tries to acquire y but fails as thread 2 has it acquired; thread 2 tries to acquire x but fails as thread 1 has it acquired. Consequently, threads 1 and 2 block indefinitely. That is, neither thread proceeds in its execution.

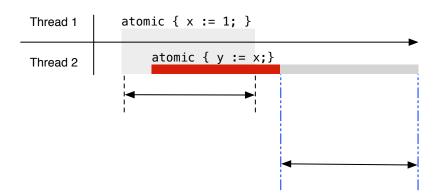

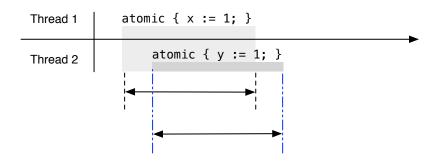

Goodman, 1983]. The *store* is the abstract term we give to the physical storage the transactional system interfaces with: transactions in RDBMSs interface with a store that is designed exclusively for relational data (e.g., to optimise query execution plans); by contrast, the store used by transactions in STM is shared memory. At the moment we will discard technical details and simply state that shared memory always resides in a machine's *random access memory* (RAM). The RAM of a machine is *volatile* – when a machine is turned off the contents of RAM are cleared. STM, due to the volatility of RAM, does not support durability. We will focus on STM. Under STM, if transactions issued by distinct threads access the same shared memory, and one of those accesses is a write, then one transaction will *abort* and the other will *commit*. Figure 1.12 (a) shows a DRF version of Figure 1.5. Where, atomic { c } executes the program commands c

Figure 1.12: (a) Transactions are used to isolate the increments of  $\mathbf{x}$  by threads 1 and 2. (b) Transactional accesses are only isolated with other transactional accesses.

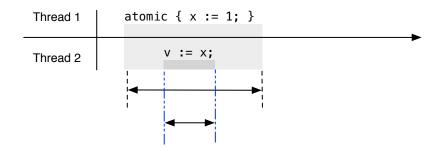

under a transactional semantics. Transactions typically perform their operations on a local copy of the data they reference. This is known as *out-of-place* updates. Figure 1.13 shows a scheduling for Figure 1.12 (a). Here, each thread's respective load and store of x reads and writes a thread-local copy of x. The updates made to x by a transaction are only persisted to shared memory if the transaction commits. STM in many cases is also a library, so they are as prone to an error like Figure 1.9, as shown in Figure 1.12 (b). Transactional accesses are isolated only with other transactional accesses. This property is known as *weak isolation* [Harris et al., 2010].

### 1.1.7 Locks or Transactions?

We have presented two types of coordination so far: locks and transactions. The reader may ask why we need two types of coordination rather than just locks or transactions. Observing Figures 1.7 and 1.12 we note that the only difference between the program texts is the way they issue their accesses to x: Figure 1.7 (a) uses sync parameterised on a mutex; and Figure 1.12 (a) uses atomic. The accesses issued by a lock are isolated with respect to those issued by locks that use

Figure 1.13: A possible scheduling of Figure 1.12 (a). txn\_beg and txn\_end are instructions that delimit transactional regions of program text.

the same mutex; transactional accesses are isolated with respect to those issued by other transactions. The key difference is that using a lock to coordinate accesses requires the programmer specify a mutex. In lock programming we can consider the mutex as encapsulating an *isolation invariant*. For example, we can interpret the isolation invariant of thread 1's lock in Figure 1.11 (a) as

"acquire(v) \( \text{ acquire(w)}"\). The value yielded from such an expression must be casually true. However, the expression cannot always be casually evaluated as shown in Figure 1.11 (b). In STM isolation invariants are maintained by the STM system rather than the programmer. Consequently, STM is a lot less errorprone than locks. Furthermore, the learning curve for correctly applying locks is steep. For example, if one wishes to use locks effectively in Java, for instance, then ideally the programmer should have digested and understood the three main texts on the subject [Herlihy and Shavit, 2008; Lea, 2006; Peierls et al., 2005]. By contrast, a programmer can correctly apply STM in minutes.

We will now describe the advantages of locks and transactions, and importantly show that locks and transactions complement one another.

#### 1.1.7.1 Pessimism and Optimism

Locks are an effective tool in the hands of an expert: they facilitate a pessimistic, low-overhead and fine-grained coordination semantics. By contrast, transactions are optimistic and simplify error-free component composition. Pessimistic means that for every code fragment sync(v) { c } the mutex v will always have been acquired before executing c, irrespective of whether or not v needed to be acquired for a given scheduling to isolate the accesses issued to c. For example, consider Figure 1.14 (a) where two threads read x. Intuitively both threads can execute their assignment concurrently without introducing a data race. However, the use of locks in this fashion always serialises their reads of x. The pessimism of locks in this case unnecessarily reduces the amount of concurrency that can take place. By contrast, Figure 1.14 (b) is the same as Figure 1.14 (a) but uses transactions. Here, both threads will execute concurrently because transactions

are optimistic. Conceptually one can think of the code fragment atomic { c } as meaning "execute c first and then determine if the accesses issued by c invalidate memory consistency." The consistency of a transaction is invalidated if it *conflicts* with another transaction. That is, two or more transactions access the same data and at least one of those transactions issues a write to that data. Optimistic coordination is more suitable than pessimistic coordination for CMPs. Furthermore, pessimistic coordination may introduce a high level of artificial contention as in Figure 1.14 (a).

| <pre>Int x; Int y; Int x;</pre>   |                                   | <pre>Int x; Int y; Int x;</pre> |                        |                       |

|-----------------------------------|-----------------------------------|---------------------------------|------------------------|-----------------------|

| Thread 1                          | Thread 2                          |                                 | Thread 1               | Thread 2              |

| <pre>sync(x) {    v := x; }</pre> | <pre>sync(x) {    y := x; }</pre> | •                               | atomic {     v := x; } | atomic {    y := x; } |

| (a)                               |                                   |                                 | (b)                    |                       |

Figure 1.14: (a) Reads of x are always serialised due to the pessimism of locks. (b) Reads of x are not serialised should they be scheduled concurrently.

#### 1.1.7.2 Overhead

The magic performed by STM does not come for free: the cost of transactionally executing commands can be great. For example, in Figure 1.13 the work performed by thread 2's transaction was thrown away due to it being aborted. The possibility of abortion is a key factor when using transactions, particularly when a transaction is accessing highly contended memory. By contrast, the cost of using a lock is generally very low and can be further reduced by using locks optimised for a particular scenario as shown in Figure 1.15. Here, three threads access  $\mathbf{x}$ ; thread 1 writes  $\mathbf{x}$  and threads 2 and 3 read  $\mathbf{x}$ . We want to isolate each

Int x; Int v; Int y; ReadWriteLock l;

x := 0; v := 0; y := 0;

| . , , ,                                         |                                           |                                           |  |  |  |

|-------------------------------------------------|-------------------------------------------|-------------------------------------------|--|--|--|

| Thread 1                                        | Thread 2                                  | Thread 3                                  |  |  |  |

| <pre>sync(l.WriteLock) {    x := x + 1; }</pre> | <pre>sync(l.ReadLock) {   v := x; }</pre> | <pre>sync(l.ReadLock) {   y := x; }</pre> |  |  |  |

Figure 1.15: Threads 1, 2 and 3 access x. Threads 1 and 2 only read x so they acquire a read lock. By contrast, thread 1 writes x so it acquires a write lock. Threads 1 and 2 can execute concurrently; if thread 1 has acquired the write lock then only it can execute – threads 2 and 3 will block until thread 1 releases the write lock.

access of x but without restricting concurrency for reads as in Figure 1.14 (a). To accomplish this we coordinate all accesses to x with a ReadWriteLock 1. Thread 1 writes x so it acquires the write lock, 1.WriteLock; by contrast, threads 2 and 3 acquire the read lock, 1.ReadLock. Threads 2 and 3 can execute concurrently; however, if thread 1 has acquired the write lock then only it can execute. Another optimisation is fine-grained locking: several mutexes are used to protect possibly different regions of shared memory. Because of this greater partitioning contention is reduced, but avoiding defects such as deadlock and data races becomes harder. Figure 1.16 compares fine-grained and coarse-grained locking strategies. As a final optimisation we may combine read/write locks with fine-grained locking: this is the gold standard of applying locks; correct application of this approach is often referred to as an art rather than a science.

#### 1.1.7.3 Composition

Designing modern systems requires composing libraries. For example, consider Figure 1.17 (a) where an item is removed from one linked list and added to another linked list. Using locks we may model a version of Figure 1.17 (a) that can

```

Int v; Int x;

sync(v) {

sync(x) {

v := x;

}

}

(a)

Int v; Int x;

Object compositeMutex;

sync(compositeMutex) {

v := x;

}

(b)

```

Figure 1.16: (a) Fine-grained: mutexes associated with  $\mathbf{v}$  and  $\mathbf{x}$  are acquired to perform the assignment. (b) Coarse-grained: a single mutex is used to protect accesses on  $\mathbf{v}$  and  $\mathbf{x}$ .

be performed by multiple threads as Figure 1.17 (b). The pitfall of Figure 1.17 (b) is that it is very easy to introduce deadlock and data races. Furthermore, the complexity of composing components increases as more components are composed. By contrast, transactions eliminate most of the complexity as shown in Figure 1.17 (c). Here, the STM system manages the isolation invariants to ensure that the composition is deadlock-free. Composition is the biggest advantage of STM. For example, let us consider a scenario where a programmer is asked to create a correct thread-safe version of Figure 1.17 (a). He may apply locks in several fashions and think that the solution is correct – only to observe a scheduling that invalidates his belief. Realistically the programmer would need to read and understand the locking semantics of his platform. For Java this would require him to understand Java threads [Oaks and Wong, 2004], techniques on how to correctly use locks and their auxiliary data structures [Lea, 2006; Peierls et al., 2005 and the Java memory model [Manson et al., 2005]. Often one also needs to understand the details of their host operating system's process, memory and thread scheduling internals, and in some cases the details of the underlying hardware. This is not a small undertaking. By contrast, a programmer needs only a basic familiarity with threads, concurrency and transactions to arrive at Figure

```

LinkedList l1;

LinkedList l1;

LinkedList 11;

LinkedList 12;

LinkedList 12;

LinkedList 12;

sync(l1) {

atomic {

l1.add(l2.pop());

l1.add(l2.pop());

sync(l2) {

l1.add(l2.pop());

}

(a)

(b)

(c)

```

Figure 1.17: (a) Composes the add and pop operations of the LinkedLists 11 and 12. (b) Attempts to compose the operations in a thread-safe manner. (c) Uses transactions to safely compose the operations.

1.17 (c).

#### 1.1.7.4 Strong and Weak Semantics

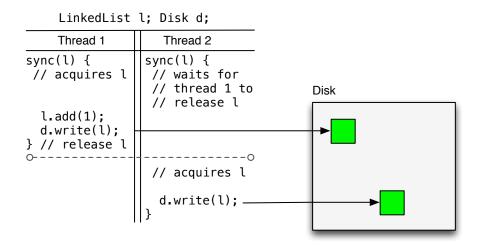

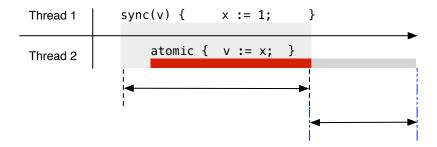

One final point of difference between locks and transactions is that locks offer a strong semantics, by contrast to transactions which are said to be weak. A lock is pessimistic which means that its protected command will always succeed: that is, in sync(v) { c } once v is acquired c will execute. By contrast, transactions are said to afford a weak semantics. For example, in atomic { c } it is possible that c will be executed multiple times should its transaction abort. This means that transactions are not generally safe for executing irreversible operations. Figure 1.18 shows the use of locks for writing to disk; Figure 1.19 shows a transactional version. The transactional program will guarantee shared memory consistency but not the consistency of peripheral components. It is possible, as shown in Figure 1.19, that a transaction may abort and leave some data that may be observed by subsequent reads of disk. Here, thread 2's transaction has not been atomic or consistent.

Figure 1.18: Using locks to safely execute an irreversible I/O operation.

Figure 1.19: Using transactions to execute an irreversible I/O operation. Thread 2's transaction aborts but its write to disk remains. Thread 2's transaction has invalidated the atomicity and consistency guarantees.

### 1.2 Motivation

Correct application of locks [Dijkstra, 1968] requires a high level of programmer skill; otherwise, data races and deadlocks may be introduced. Researchers are looking into alternative methods, e.g. STM [Shavit and Touitou, 1995], to lower the barrier of entry for correctly coordinating accesses to shared memory in multithreaded programs. Adoption of STM is limited [Harris et al., 2005; Hickey, 2008] and in many cases cannot simply supplant locks (see Section 1.1.7.4). There are two key issues that are blocking the uptake of STM by mainstream imperative programming languages: (1) performance; and (2) understanding how it co-exists with existing coordination facilities such as locks. The aim of this thesis is to contribute to the literature regarding (2).

A relatively sizeable amount of literature exists on implementing transactions in systems that already expose locks, such as [Dice et al., 2006; Lev et al., 2009; Menon et al., 2008; Saha et al., 2006; Usui et al., 2009] but remarkably little exists on understanding the semantics of such systems, which is required to develop further research into the area. There are two key advantages to defining a semantic model that is based on a common implementation strategy: (1) runtime semantics; and (2) static semantics. The latter is influenced by the former: to understand what should be statically deemed correct we must understand what we wish to observe during a program's execution, e.g. [Grossman et al., 2006; Spear et al., 2008]. Most of the current literature focuses on verification of the STM system [Cohen, 2008; Guerraoui and Kapaka, 2007; Hu, 2012] or gives a semantics which focuses on a specific use case of STM [Lev and Maessen, 2005; Smaragdakis et al., 2007; Welc et al., 2008; Ziarek et al., 2008]. Moreover, the se-

mantics presented typically do not encompass several forms of coordination tools. That is, they focus on STM but omit usages of other coordination tools in the same program.

Construction of a dynamic and static semantics for programs using locks and transactions has the following concrete advantages:

- Dynamic Semantics. A general notion of co-existence of locks and transactions can be defined on the basis of fundamental properties such as memory locations accessed. Properties can be constructed for conflict detection and resolution between the two semantics, as well as the observational properties of reads [Adve and Gharachorloo, 1996]. With this understanding we can apply the derived knowledge to the static analysis of programs which use locks and/or transactions to coordinate accesses to shared memory. At present a clear gap in the literature exists in understanding the semantics of programs which use locks and/or transactions to coordinate accesses to shared memory.