# **Durham E-Theses**

# The design and construction of the control and arithmetic units of a demonstration electronic digital computer

Brunskill, Raymond H.

#### How to cite:

Brunskill, Raymond H. (1969) The design and construction of the control and arithmetic units of a demonstration electronic digital computer, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/10010/

#### Use policy

$The full-text\ may\ be\ used\ and/or\ reproduced,\ and\ given\ to\ third\ parties\ in\ any\ format\ or\ medium,\ without\ prior\ permission\ or\ charge,\ for\ personal\ research\ or\ study,\ educational,\ or\ not-for-profit\ purposes\ provided\ that:$

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

- The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

Academic Support Office, The Palatine Centre, Durham University, Stockton Road, Durham, DH1 3LE e-mail: e-theses.admin@durham.ac.uk Tel: +44 0191 334 6107 http://etheses.dur.ac.uk The Design and Construction of the Control and Arithmetic units of a Demonstration

Electronic Digital Computer.

Thesis submitted for the

## Degree

of

Master of Science, in the University of Durham.

Raymond H Brunskill, C.Eng., M.I.E.E., M.Inst.M.C.

January 1969.

ß

#### ACKNOWLEDGMENTS.

The author wishes to thank Professor D.A. Wright for his approval of the project and his co-operation in making available the facilities which have enabled its completion. It is pleasing to acknowledge the valuable assistance and guidance of Dr. M.J. Morant who, in addition to supervising this work, has always given encouragement and constructive criticism. Thanks are also due to Dr. B.J. Stanier for his generous counsel and practical aid, especially during the commissioning period.

The author is grateful to the Darlington Education Authority, and the Chairman and Members of the Governing Body of the Darlington College of Technology for their permission to undertake this work; to his Principal, Mr. C.E. Beynon, for his encouragement and active support; to Dr. H. Williams for his initial advice and subsequent co-operation; and to Mr. W.S. Wood for numerous mentorial services.

He is appreciative of the assistance given by: Mr. T. Nancarrow, Mr. L. Erskine and Mr. E.S. Collin in the construction of the machine; and Mrs. E. Brunskill, Mr. R.G. Smith and Mr. A. Lowcock in the production of the typescript.

This list of acknowledgments would be incomplete without mention of my wife, Mary, whose understanding and forbearance proved to be invaluable.

• •

CONTENTS.

4

| Chap | ter.                                          |                                                                         | Page |

|------|-----------------------------------------------|-------------------------------------------------------------------------|------|

| I    | INTRODUCTION.                                 |                                                                         |      |

| II   | I THE TEACHING COMPUTER - PRESENT AND FUTURE. |                                                                         |      |

| ١    | 2.1                                           | Practical Training in Computer Electronics.                             | 6    |

| •    | 2.2                                           | Review of Present Commercial Equipment.                                 | 7    |

|      |                                               | 2.2.1 Simple Logic Tutors.                                              | 8    |

|      |                                               | 2.2.2 Digital Equipment to Demonstrate<br>Arithmetic Processes.         | 14   |

|      |                                               | 2.2.3 Conclusions on Commercially Produced<br>Teaching Computers.       | 19   |

|      | 2.3                                           | Review of Literature on Computing<br>Electronics Teaching Equipment.    | 20   |

|      | 2.4                                           | General Requirements of a Machine for<br>Teaching Computer Electronics. | 23   |

| III  |                                               | BASIC COMPUTING TECHNIQUES                                              | 26   |

|      | 3.1                                           | Logic Functions.                                                        | 26   |

|      | 3.2                                           | Minimal Design Procedure,                                               | 30   |

|      | 3.3                                           | Combinational Logic Circuits                                            | 31   |

|      |                                               | 3.3.1 EXCLUSIVE-OR Gate.                                                | 31   |

| •    |                                               | 3.3.2 The Binary Adder.                                                 | 32   |

|      |                                               | 3.3.3 The Bistable Element.                                             | 33   |

|      |                                               | 3.3.4 Shifting and Counting.                                            | 34   |

|      | 3.4                                           | Realisation of Arithmetic Processes.                                    | 37   |

|      |                                               | 3.4.1 Binary Subtraction.                                               | 37   |

|      |                                               | 3.4.2 Binary Multiplication.                                            | 39   |

|      |                                               | 3.4.3 Binary Division.                                                  | 41   |

| IV   |                                               | FACTORS AFFECTING DESIGN.                                               | 43   |

|      | 4.1                                           | Primary Considerations.                                                 | 43   |

|      | 4.2                                           | Some Aspects of General Purpose Computers.                              | 45   |

|      | 4.3                                           | Machine Instructions.                                                   | 46   |

|      | 4.4                                           | Parallel or Serial Operation.                                           | 48   |

|      | 4.5                                           | Number Representation.                                                  | 49   |

# CONTENTS.

|    | 4.6 0                                       | Operand Address Modification.                | 49  |  |  |  |

|----|---------------------------------------------|----------------------------------------------|-----|--|--|--|

|    | 4.7 V                                       | 50                                           |     |  |  |  |

|    | 4.8 Micro-programming.                      |                                              |     |  |  |  |

|    | Method of Demonstration.                    | 52                                           |     |  |  |  |

| v  | GENERAL FEATURES OF THE DESIGN.             |                                              |     |  |  |  |

|    | 5.1 \$                                      | Statement of Specification.                  | 54  |  |  |  |

|    | 5.2 (                                       | Overall Operation of the Computer.           |     |  |  |  |

|    | 5.3 Final Outline Design of the Control Uni |                                              |     |  |  |  |

|    | 5.4 I                                       | Final Outline Design of the Arithmetic Unit. | 59  |  |  |  |

|    | 5.5 1                                       | The Machine Instructions.                    | 63  |  |  |  |

|    | 5.6 1                                       | The Order Code.                              | 65  |  |  |  |

| VI |                                             | DETAILED CIRCUIT DESIGN.                     | 78  |  |  |  |

|    | 6.1 (                                       | Choice of Integrated Circuits.               | 78  |  |  |  |

|    | 6.1                                         | .l Practical Considerations.                 | 78  |  |  |  |

|    | 6.1                                         | .2 Texas Instruments 74N Series.             | 81  |  |  |  |

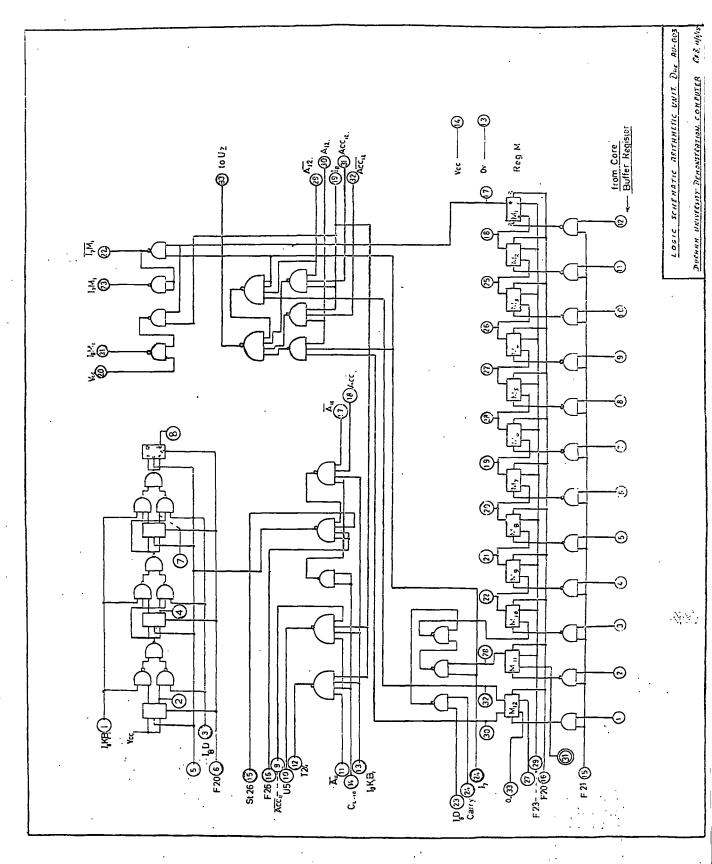

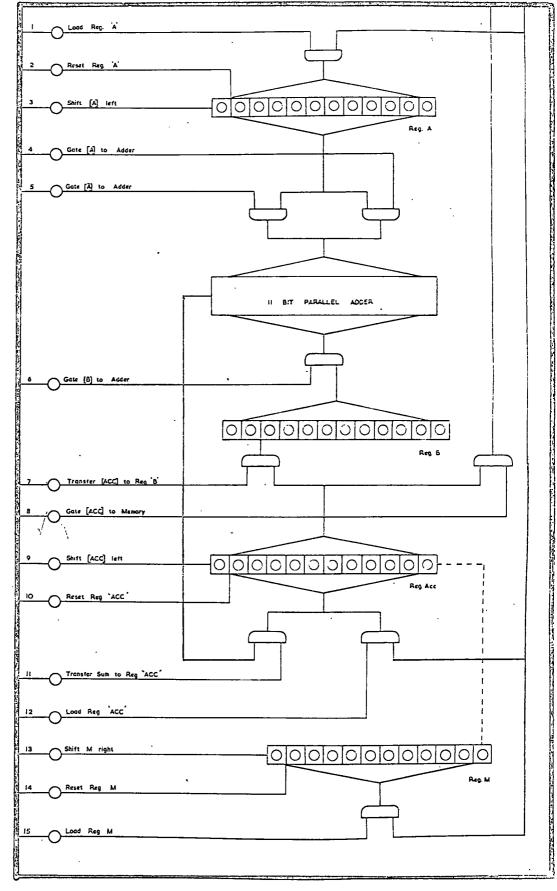

|    | 6.2                                         | Detailed Design of the Arithmetic Unit.      | 82  |  |  |  |

|    | 6.2                                         | .1 The Accumulator Register.                 | 82  |  |  |  |

|    | 6.2                                         | .2 Register B.                               | 85  |  |  |  |

|    | 6.2                                         | .3 Register A.                               | 86  |  |  |  |

|    | 6.2                                         | .4 Register M.                               | 89  |  |  |  |

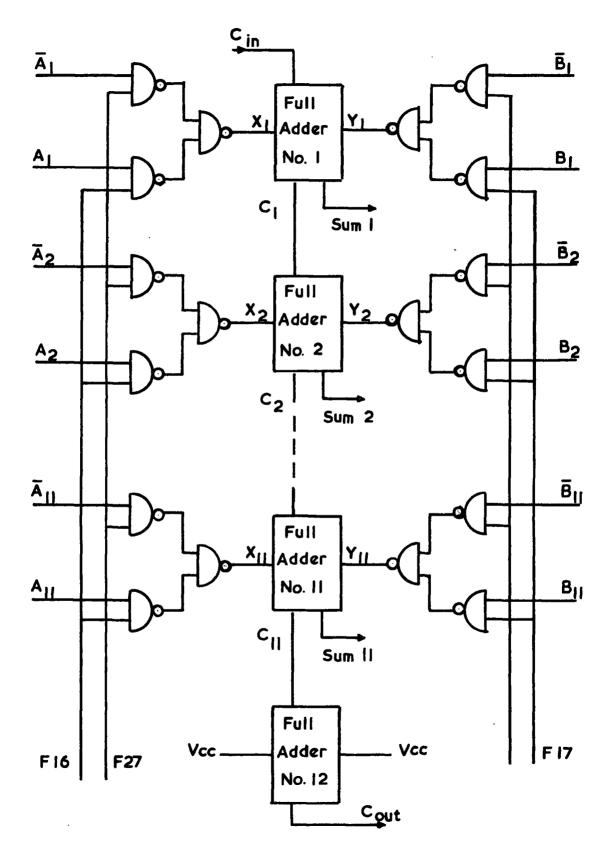

|    | 6.2                                         | .5 The Parallel Adder.                       | 91  |  |  |  |

|    | 6.2                                         | .6 Miscellaneous Special Circuits.           | 93  |  |  |  |

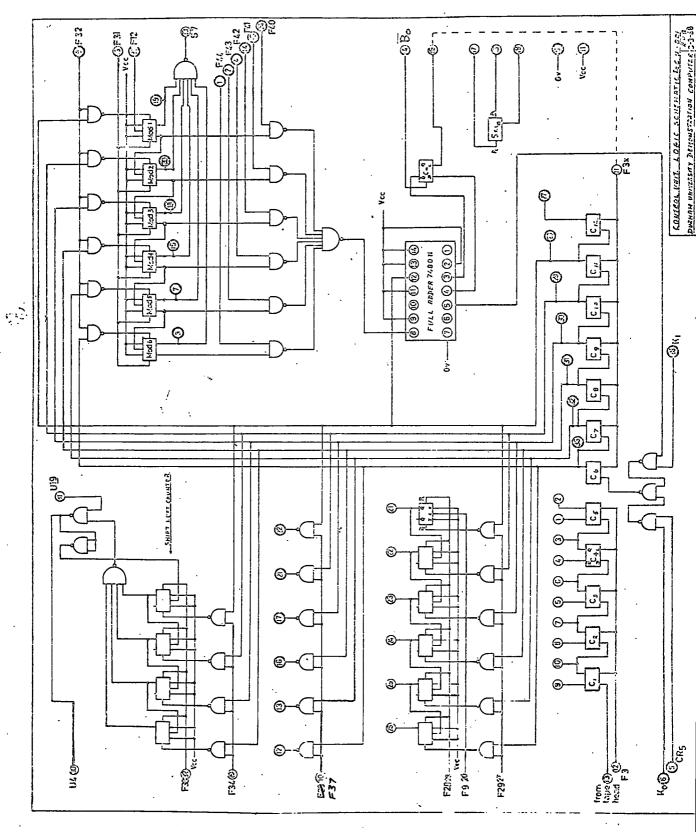

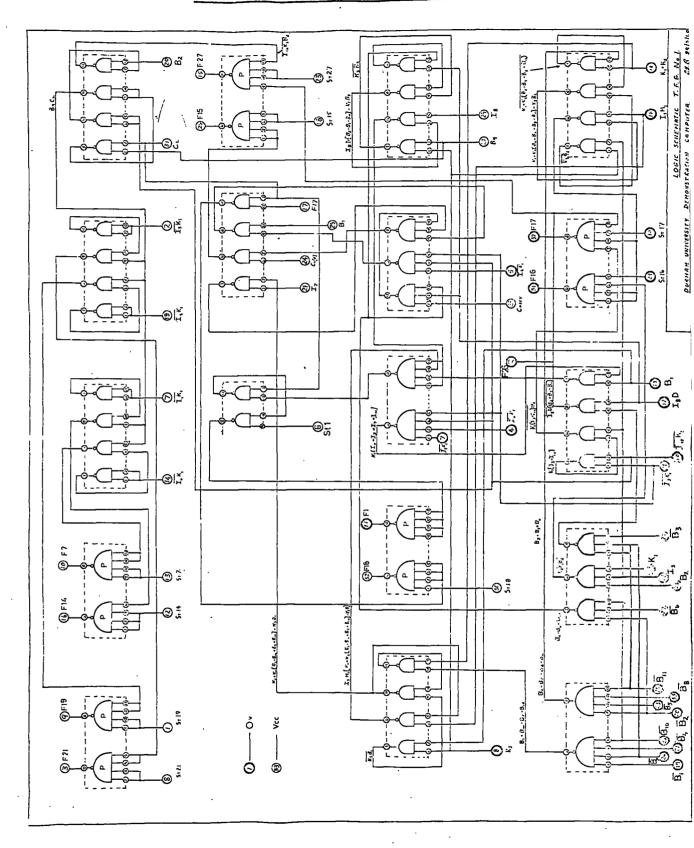

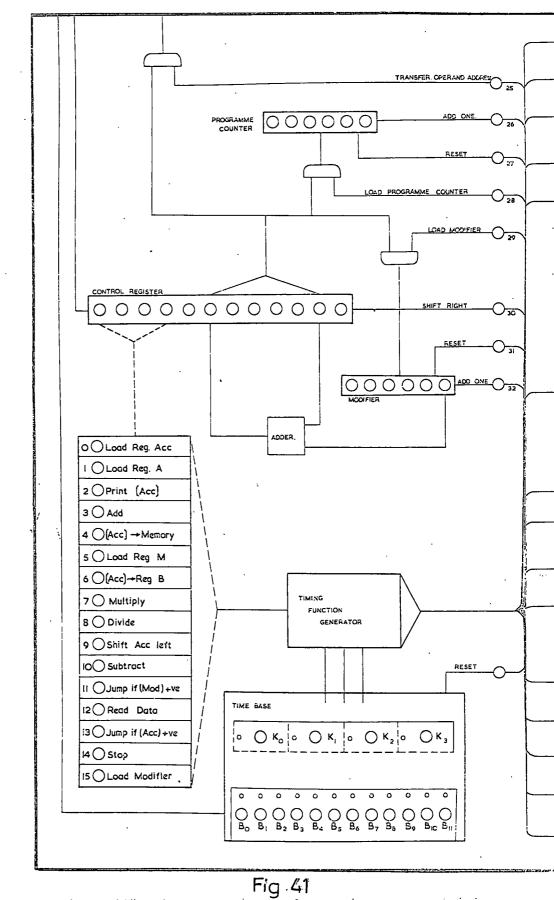

|    | 6.3 I                                       | Detailed Design of the Control Unit.         | 94  |  |  |  |

|    | 6.3                                         | .1 The Control Register.                     | 94  |  |  |  |

|    | 6.3                                         | •2 The Modifier Register.                    | 95  |  |  |  |

|    | 6.3                                         | .3 The Programme Counter.                    | 98  |  |  |  |

|    | 6.3                                         | .4 Miscellaneous Control Circuits.           | 99  |  |  |  |

|    | 6.4 Detailed Design of the Timebase and     |                                              |     |  |  |  |

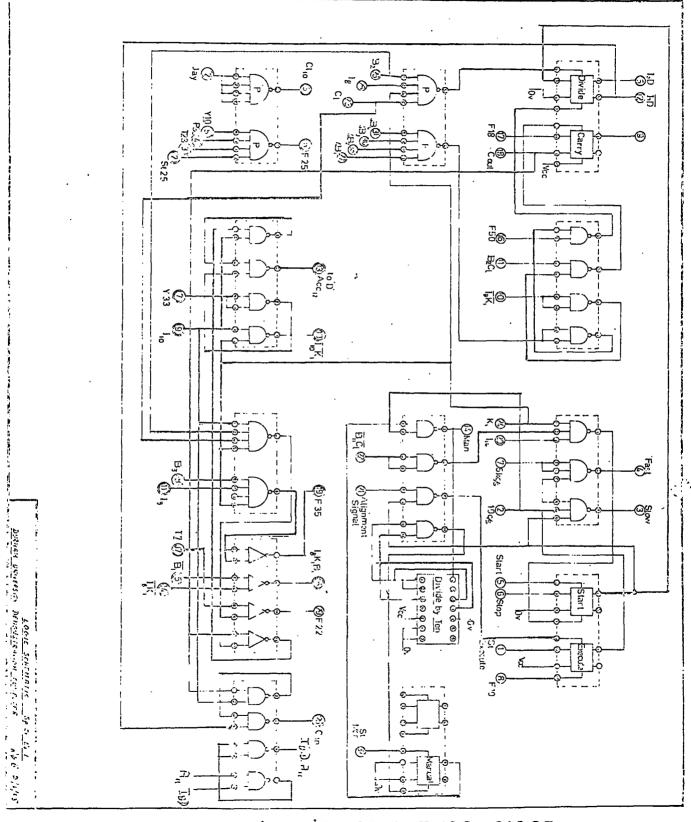

|    |                                             | Instruction Decode Section.                  | 101 |  |  |  |

|    |                                             | .1 The Instruction Decoder.                  | 101 |  |  |  |

|    |                                             | .2 The Timebase.                             | 102 |  |  |  |

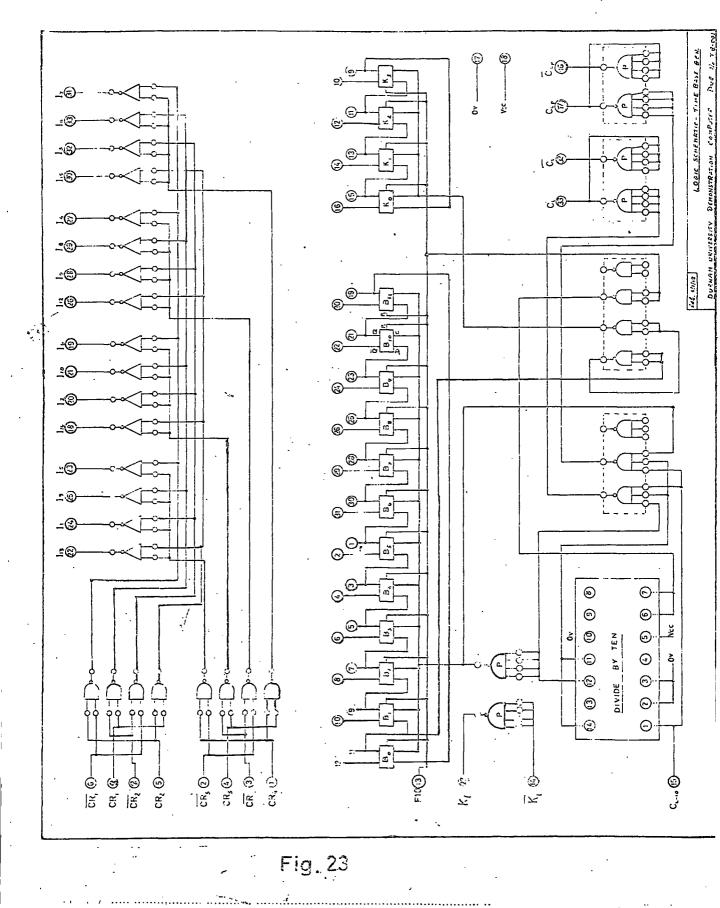

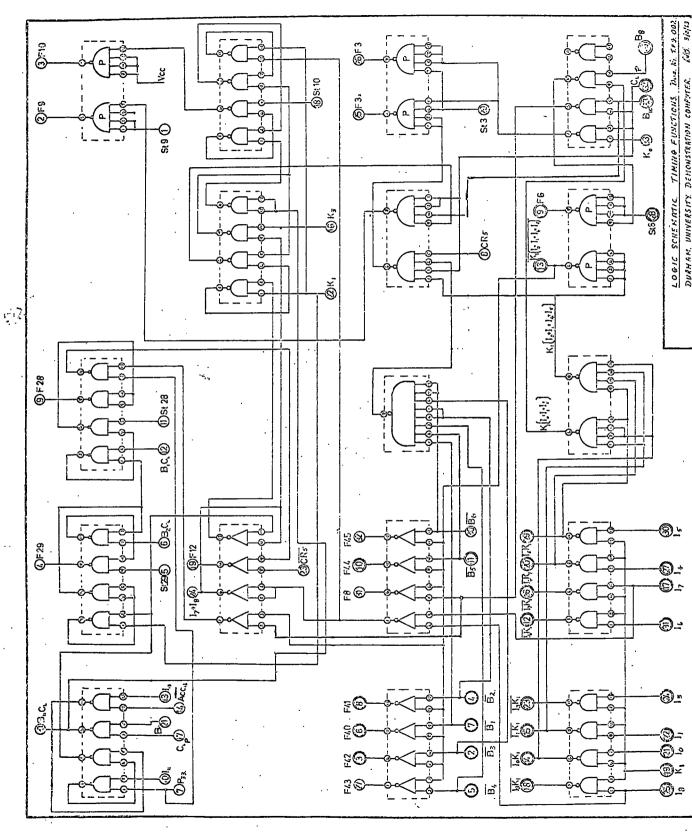

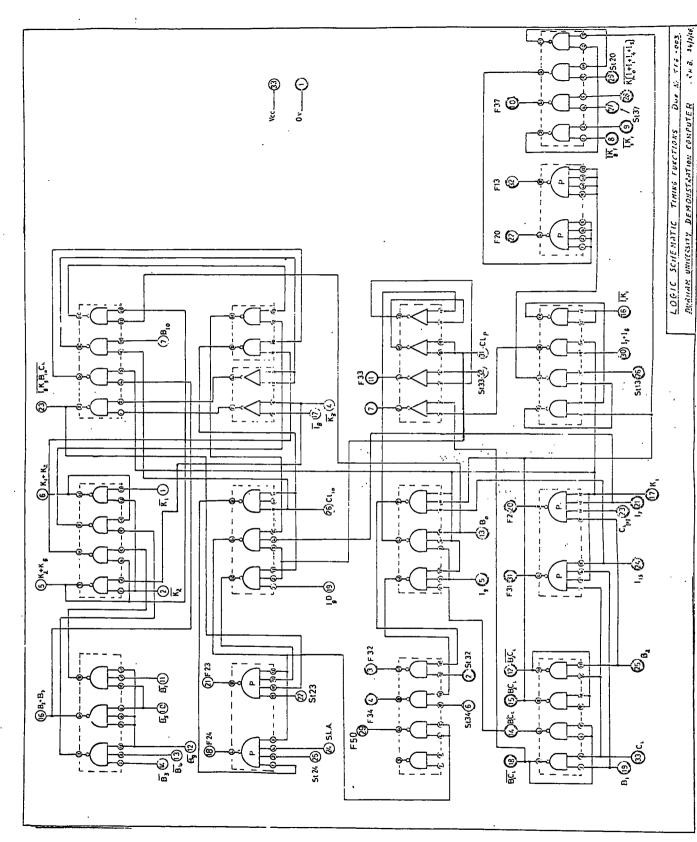

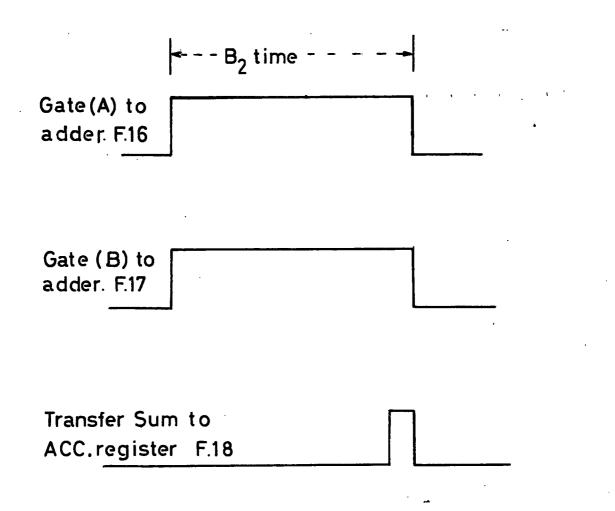

|    | 6.5                                         | The Timing Function Generators.              | 106 |  |  |  |

# CONTENTS.

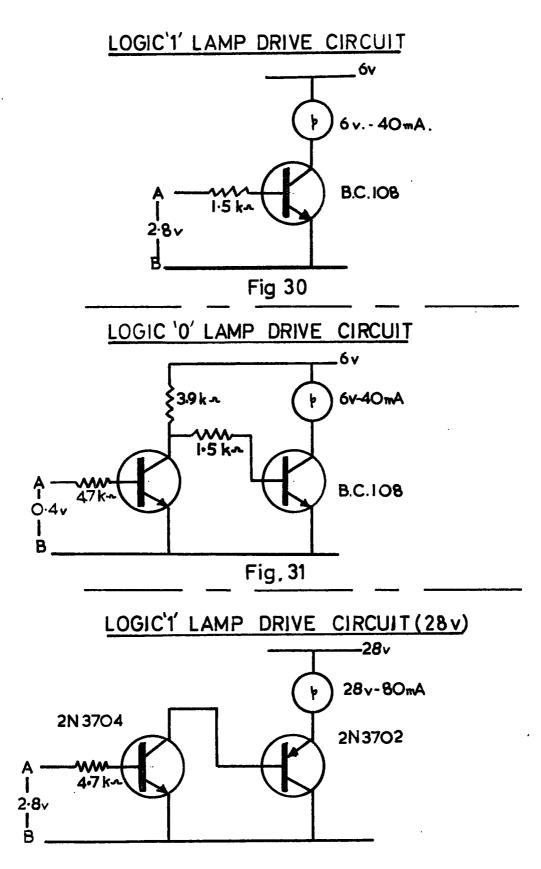

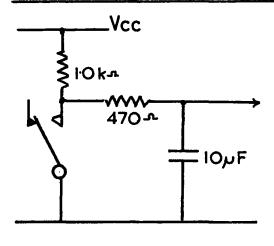

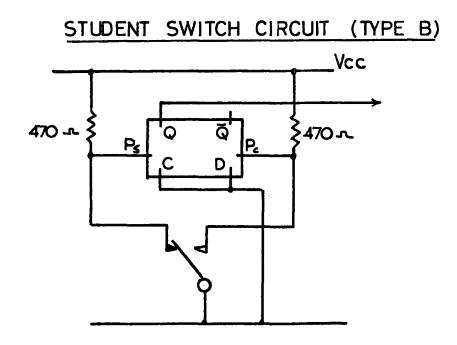

|      | 6.6 The             | Display and Manual Control Circuits          | 107    |  |  |  |  |  |

|------|---------------------|----------------------------------------------|--------|--|--|--|--|--|

|      | 6.7 The             | Power Supplies.                              | 108    |  |  |  |  |  |

| VII  |                     | MAIN ASSEMBLY.                               | 110    |  |  |  |  |  |

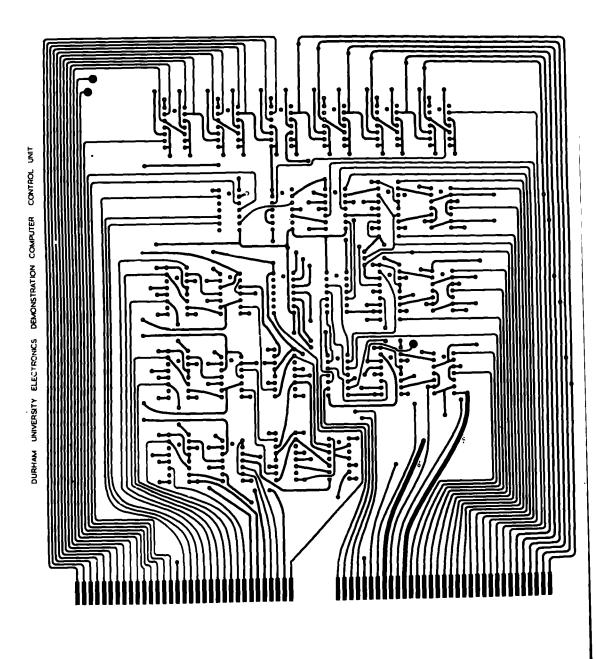

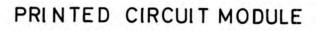

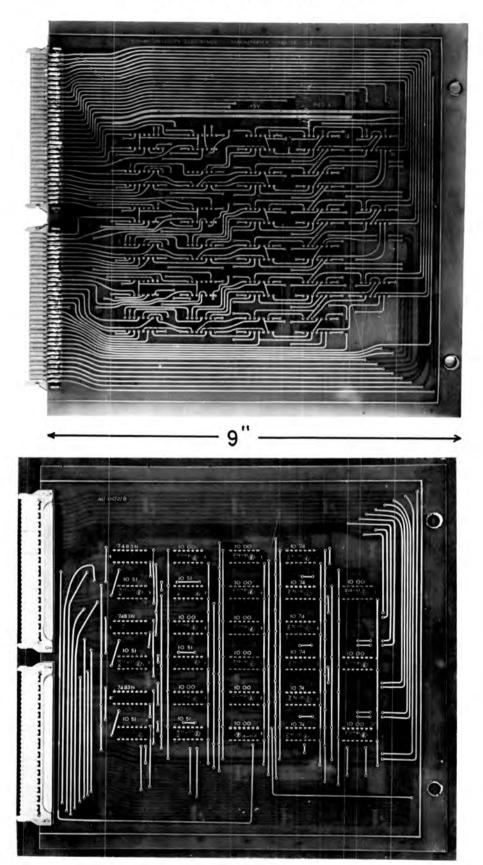

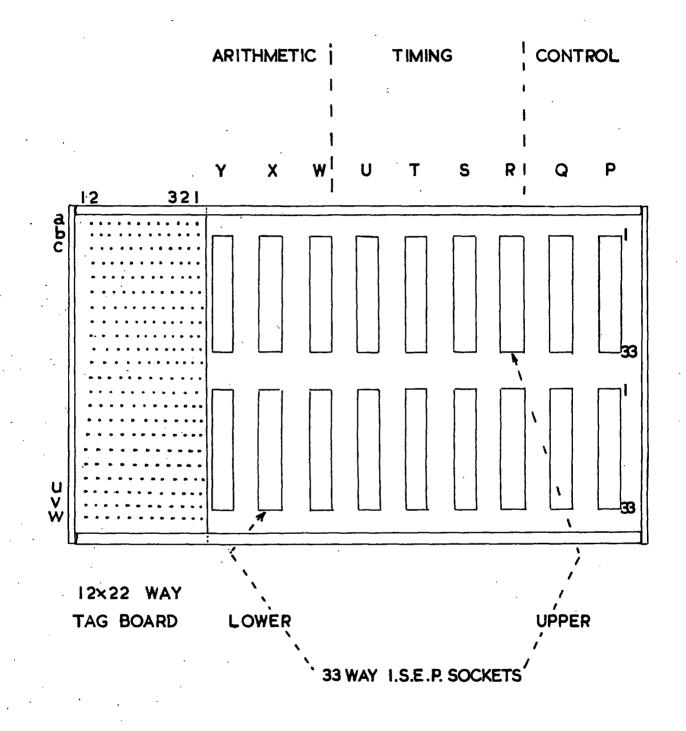

|      | 7.1 Pri             | nted Circuit Boards.                         | 110    |  |  |  |  |  |

|      | 7.2 Wir             | ing Schedule.                                | 112    |  |  |  |  |  |

|      | 7.3 Pan             | el Layout.                                   | 112    |  |  |  |  |  |

|      | 7.4 Mec.            | hanical Construction.                        | 115    |  |  |  |  |  |

| VIII |                     | COMMISSIONING.                               | 116    |  |  |  |  |  |

|      | 8.1 Cir             | cuit Testing.                                | 116    |  |  |  |  |  |

|      | 8.2 Cir             | cuit Modifications.                          | 116    |  |  |  |  |  |

| IX   | SUGG                | ESTED TEACHING PROGRAMME.                    | 120    |  |  |  |  |  |

|      | 9.1 Ins             | truction Manual.                             | 120    |  |  |  |  |  |

|      | 9.2 Not             | es on Laboratory Exercises.                  | 122    |  |  |  |  |  |

|      | 9.2.1               | Revision of Simple Logic Circuits.           | 122    |  |  |  |  |  |

|      | 9.2.2               | Central Processor Organisation.              | 124    |  |  |  |  |  |

|      | 9.2.3               | Manual Operation of Arithmetic Process       | es 125 |  |  |  |  |  |

|      | 9.2.4               | Manual Operation of Machine<br>Instructions. | 127    |  |  |  |  |  |

|      | 9.2.5               | The Timebase.                                | 127    |  |  |  |  |  |

|      | 9.2.6               | Sequencing of Minor Commands.                | 128    |  |  |  |  |  |

|      | 9.2.7               | Execution of a Series of Instructions.       | 129    |  |  |  |  |  |

|      | 9.2.8               | Assembling a Programme.                      | 129    |  |  |  |  |  |

| X    |                     | CONCLUSIONS.                                 | 130    |  |  |  |  |  |

| APPE | NDIX 1.             | Timing Functions.                            | A.1.1  |  |  |  |  |  |

| APPE | ENDIX 2.            | Wiring Schedule.                             | A.2.1  |  |  |  |  |  |

| LIST | LIST OF REFERENCES. |                                              |        |  |  |  |  |  |

. . . . .

. . .

### CHAPTER I

#### INTRODUCTION

This thesis is concerned with the design and construction of a small demonstration digital computer. This computer has been built to assist in the teaching of computer electronics. It is not intended to be employed for teaching programming, for which full size computers are more suitable. The Department of Applied Physics has been interested in a project of this nature for some years. The digital computer is seen as an admirable machine on which to demonstrate some of the applications of modern electronic devices with which the department is so actively concerned.

It was obvious that to attempt to construct a machine of adequate specification using second generation components, (i.e. transistors etc.), was totally impractical. The physical effort involved in the assembly of a very large number of discrete circuit elements was considered to be too great for the facilities available and to give no guarantee of success. The difficulties of this form of construction were confirmed by examining the commercially available equipment for teaching computer electronics. Machines costing up to  $\pounds 2,000$  (which is considered to be a normal upper limit for most educational establishments) work only in the serial mode and are mostly limited to demonstrating basic arithmetic processes. The present project had in mind a more sophisticated computer, while still aiming at a possible commercial price limit of around £2,000.

The advent of the cheaper ranges of integrated circuits stimulated further examination of the possibility of constructing a small demonstration digital computer. The project was now much more attractive, since component requirements would be reduced by a factor of ten. The chances of success would be greatly increased owing to improved circuit reliability and the reduction in the number of actual circuit elements. Coupled with this was the confirmation that the cost of these devices was falling and that this trend was likely to continue for some time to come. The prospect of being among the first to apply integrated logic elements, to quite complex switching networks, was most exciting. The obvious enthusiasm was of course tempered by the knowledge that a fundamental error in design or construction would render the equipment virtually redundant.

It was against this background that the project started in September, 1966. The initial discussions,

-2-

involving Dr. M.J. Morant, Dr. B.J. Stanier, Mr. A. Smith and the author, were directed at establishing the general requirements of a demonstration digital computer. These are listed in section 2.4. Subsequent discussion led to the formulation of the detailed specification of section 5.1. This specification was drawn up in December, 1966 and approved during the following month. The project was divided into two parts at this stage. The control and arithmetic sections were allocated to the author and the memory section became the responsibility of Mr. A.Smith. This part of the work is the subject of a separate thesis (1).

This thesis records the events, since September, 1966, which have led to the production of the control and arithmetic sections of the demonstration computer. The design, construction and commissioning associated with these sections are, with a small amount of technical assistance, entirely the work of the author. The project has been carried out under the supervision of Dr.M.J. Morant and Dr. B.J. Stanier. The author has, of course, enjoyed the general advice and encouragement of his supervisors.

The project was completed by stages, each of which may be identified with the appropriate sections of the

-3-

thesis. The detailed planning of these stages was considered vital to the success of the project. It was felt that the work could not be allowed to proceed without clearly defined terms of reference, involving component costs and time estimates of design and construction effort. A realistic approach to component costs, delivery dates, design effort, construction time, etc. enabled the completion dates for the various stages to be approximated. With few exceptions these estimates have proved to be fairly accurate.

The background work, which involved a study of available digital teaching equipment. current techniques and design procedures, is discussed in Chapters 2, 3 and 4. A detailed analysis of the accepted design is given in Chapter 5. The description of the detailed circuit design. Chapter 6, shows how the individual requirements of each register, timing function, control gate, etc. have been met using the techniques previously established. In Chapter 7 details are given of the methods and processes used in the actual construction. The test procedures and problems associated with persuading the machine to function are recorded in Chapter 8. Chapter 9 lists some typical laboratory excercises, to show how the machine is to be employed in the teaching situation. In

-4-

the final Chapter consideration is given to modifications which, it is believed, would improve the performance of the equipment.

### CHAPTER II.

#### THE TEACHING COMPUTER - PRESENT AND FUTURE

### 2.1 Practical Training in Computer Electronics

It is necessary to examine the type of situation in which a demonstration digital computer would be of assistance. Practical training in the application of logic elements to complex switching networks is primarily the concern of applied science departments in universities and colleges of technology. The digital computer, employing all logic circuit techniques, is the ideal vehicle on which to gain practical experience. The function of such equipment is to demonstrate, clearly and in considerable detail, the various techniques likely to be encountered by prospective engineers and technicians whose later work will be associated with complex logic circuitry. It is considered that practical work, using equipment of the proposed design, could form a valuable part of courses in the following subjects.

(i) Electronics and Electronic Engineering.

It is now certain that students should have practical experience in the application of modern electronic devices to a wide range of digital techniques and in the analysis of complex switching networks. (ii) Computing Science.

A detailed study of the central processor appears to form an essential part of such courses. (iii) Measurement and Control.

It is apparent that digital methods are becoming well established in these courses.

(iv) Electronic Technician.

The construction and maintenance of industrial digital equipment forms an important part of the course.

### 2.2 <u>Review of Present Commercial Equipment</u>.

One of the first exercises undertaken in this project was to examine currently available equipment which has been designed solely for teaching purposes. The literature describing the majority of U.K. equipment was obtained from the manufacturers and, where possible, arrangements were made for actual demonstration. It was necessary to compare the relative merits and limitations in terms of effectiveness, flexibility and cost. The results of this review assisted in the determination of an acceptable specification for the proposed demonstration computer.

It was found that most of the equipments examined were described as being 'Digital Computers' whereas, in

-7-

fact, none adequately complied with the B.S. 3527 definition of a digital computer. The equipment reviewed here may be conveniently divided into two groups.

- (i) Simple Logic Tutors.

- (ii) More elaborate equipment to demonstrate arithmetic processes.

In addition, there are a number of full scale computer systems which are described as being suitable for teaching purposes, but owing to their relatively high cost, these are not considered in the present context.

### 2.2.1 <u>Simple Logic Tutors.</u>

### (i) Lan Electronics Integrated Computer Training System.

Lan Electronics, probably the most active in the development of electronic training aids, marketed one of the first logic trainers (LAN-DEC 15), and has since developed a comprehensive range of teaching aids for the electronics and computing subjects. This first logic tutor is based on the use of NOR elements. A telephone dial, in conjunction with manual push-buttons, is provided to set up the input conditions to some of the fifteen available NOR gates. Monitoring of the state of logic elements is achieved by using six panel-mounted filament lamps.

Although this equipment is described, by the manufacturer, as being suitable for the teaching and demonstration of computing techniques, it is evident from the specifications of this company's more recent equipments that its limitations have been realised. These are as follows: - a) the inability to demonstrate the fundamental AND-OR relationships; b) the degree of complexity involved in assembling astable and bistable circuits, coupled with the risk of their malfunction; c) the comparatively small number of logic elements available, compared with those required to construct any of the basic combinational logic circuits, e.g. counter, shift register. It is worth noting that this equipment was conceived at a time when most of the industrial control equipment was designed around the use of NOR elements, and in this respect it may have been useful as a design aid in industrial situations.

The cost of this equipment is approximately £100 and includes the power unit, relay unit, patch cords and handbooks.

The succeeding equipment, LAN-DEC 100, Training Computer, is much more versatile. The front patching panel connects to eight multiway sockets, each of which accepts a printed circuit card. These cards can

-9-

incorporate any type of logic element; typically a card may include 20 gates or perhaps five bistable elements. Input conditions are set up by a telephone dial and toggle switches. Output conditions may be checked using the eight panel-mounted filament lamps.

The effectiveness of this equipment is directly related to the ability of the demonstrator to troubleshoot incorrect student wiring. With so many front panel terminals available, it is necessary for each student to be thoroughly familiar with the dangers of connecting rail voltages to the output of gates and with the loading capacities of the elements. Another point worth noting is that if the student is able to employ such a large number of elements, as is implied by the number made available, he must surely have encountered counting, coding, timing circuits etc. It would doubtless be of advantage to provide two or three clock generators, and to make these permanently available on the front panel. The cost of the equipment is in excess of £320. Although its flexibility is recognised, the large number of interconnections required to assemble the circuits, the lack of continuous timing pulses and the relatively high cost, make this equipment less than ideal.

The most ambitious logic tutor advertised by this

-10-

company is the ROBTOM digital computer, which incorporates four separate panels to accommodate the logic elements. Thirtytwo filament lamps and their associated inverter amplifiers are provided on one panel, a second panel carries a 32 bit store and fast counter, while a third panel provides a number of two and four input NOR gates. Input conditions are set up on the 31 toggle switches which are assembled on the fourth panel. The equipment has the same basic limitations as the LAN DEC 100. It is therefore likely that equipment of this sort would be most useful in a digital control design laboratory where the large numbers of gates and storage facilities would be of advantage in breadboarding control schemes. It is considered that the equipment is too general and without any specific aim. Its cost is £650.

### (ii) L.K. 250 Series of Logikits Feedback Ltd.

Each of the logikits obtainable from Feedback Ltd. comprises a base board and a number of lamps and sockets to accept plug-in logic elements. One feature of the range is that both AND and OR functions are available in addition to bistables, monostables, clock generators, pulse shapers and delay units. The degree of flexibility obtained with this equipment is high. Since only those elements required for a particular exercise are included

-11-

on the base board, students may cover a considerable range of digital techniques in very simple steps, without redundant terminations or symbols appearing. The handbook, for model L.K. 253, lists some twenty exercises which may be demonstrated. The author has no actual experience in the use of this equipment and cannot therefore comment on reliability and student-proofing. The concept of using only the required logic elements would appear to simplify the 'patching up' procedure, and the symbols appearing on each element provide an acceptable mimic diagram of the system under consideration.

The model L.K. 253, which has nine indicator lamps on the 32 socket base board together with 20 logic elements is listed at £325, whereas the model L.K. 255 with slightly inferior specifications (20 sockets, 6 Lamps, 15 elements) costs £133.

### (iii) Logic Tutor - Systems Computers Ltd.

One feature of the Systems Computers Logic Tutor which distinguishes it from other logic tutors is in the method of interconnecting the logic elements. A detachable 336 way patch board may be pre-wired and checked before insertion in the tutor panel. There are 30 NAND gates available, four bistables and two buffer amplifiers. Six toggle switches may be used to set up the

-12-

input conditions and eight filament lamps are included to monitor the output conditions of the logic elements. The elaborate 336-way patch panel obviously accounts for much of the cost of £345.

# (iv) <u>Digital Logic Instrumentation Kit.</u> Farnell <u>Instruments Ltd</u>.

Priced at £125, the Farnell Logic Kit comprises a base board and 26 plug-in units. Included are 6 NOR gates, 5 AND gates and 5 Binary units. It is aimed at introducing the student to the principles of digital control systems. The chief advantage is its simplicity of assembly, because only those elements required for a particular experiment need be assembled. There are no redundant switches, lamps and free terminations to interfere with the appreciation of the circuit under consideration. Additional units may be obtained to permit the study of larger combinational logic systems. It is possible to demonstrate the basic laws of Boolean algebra as both AND and OR elements may be incorporated. Multiple gating with these basic elements is not possible, unless the coupling between each pair of units is done with a buffer amplifier. It is considered that, apart from this limitation, the equipment is quite effective, easy to demonstrate and flexible, and that the chief aim of

demonstrating simple digital techniques has been achieved.

(v) <u>Other Logic Breadboard Systems</u>.

There are a number of other plug-in logic systems commercially available. These are primarily intended for use in development laboratories, and as they have not been designed solely for educational purposes they are not considered relevant to this discussion.

### 2.2.2. <u>Digital Equipment to Demonstrate Arithmetic</u> <u>Processes.</u>

### (i) Educational Computer, Type B.T.1 - Elliott Bros. Ltd.

The Elliott Bros. computer type B.T.l, designed in . conjunction with the Battersea College of Advanced Technology, performs routing, control and arithmetic operations on binary numbers. Input of data is achieved by push-button and information monitoring is done using filament lamps. A multiway rotary switch is used to select any of the seven machine instructions. Timing pulses are available at the rate of 5kHz, 1Hz or by manual push-button. The machine operates in the serial mode, on pure binary numbers, with a 16 bit word. The main combinational logic circuits incorporated are three 16 bit shift registers, a single bit full adder and a 4 bit binary counter, which is used to generate the shift pulses. The instructions are executed in the serial mode requiring

16 of the available 20 pulses allocated to each word time. Subtraction is performed by the complement method, multiplication by addition and right shifting, but there is no instruction for division.

In February, 1968 it was announced that this equipment was to be part of a complete computer to be manufactured by Feedback Ltd. The specification of this new equipment, ABACUS Educational Computer Ec360/370, indicates that it is now in two sections, an Arithmetic unit, very similar to the type B.T.l. and a Control and Store unit which incorporates a 256 word ferrite core store. The normal operating speed is quoted at 2,500 p.p.s., although an unspecified slow speed is included. The control unit, when operating at slow speed, can show the arithmetic and control processes associated with serial operation. It appears from photographs, that the circuitry is built up using discrete components which obviously accounts for much of the cost of £2,950.

### (ii) <u>Teaching Computer.</u> <u>Telefunken Ltd</u>.

Although the Telefunken equipment is manufactured outside the U.K., it is considered here because it demonstrates clearly the link between arithmetic and memory functions. The equipment incorporates a control

-15-

unit, an arithmetic unit and a store. The control unit consists of 11 push-button switches to select the required machine instruction and a telephone dial to generate the timing pulses. There are six storage cells, each storing one 8-bit word. Examination of the interrogated storage location is achieved using a relay driven lamp matrix.

The arithmetic operations, add and subtract, are performed using 2 eight-bit shift registers and a single bit full adder, together with suitable gating circuitry. The display panel carries a mimic diagram with lamps to illustrate the operation of all registers and control gates.

Although this equipment appears to be good, from the demonstration point of view, there is no facility for slow automatic operation. If this were available, the student could then become familiar with the machine cycle before assuming the role of the control unit. There is no attempt to demonstrate those instructions dealing with 'jumps' in the programme. The demonstration of binary multiplication and division is difficult, owing to the large number of timing pulses required for serial operation.

This equipment is priced at approximately £800. It is somewhat expensive, considering its component parts; but the layout, which gives a very clear appreciation of

-16-

the demonstration, to some extent off-sets this cost.

### (iii) <u>Teaching Computer</u>. <u>Mullard Educational Services Ltd</u>.

The Mullard Educational Computer is a suggested design which can be built in five stages. The first stage provides for the addition and subtraction of 2 eight-bit binary numbers in the serial mode, either under manual control or at a clock rate of 20 kHz. A slow automatic speed of 1 Hz is also provided. The succeeding stage carries out multiplication and division by the inclusion of extra switches and logic circuitry. The stage three computer incorporates two additional eight-bit storage registers to replace the manual switches of the stage two equipment. The modifications required to progress to stages four and five are still under development. Preliminary information suggests that a 16-bit word will be used, together with data and programme-storage facilities using one or more 160 bit delay lines. The equipment which is currently available does not include display or control panels, which must be designed and constructed by the purchaser. All logic circuits are built on plug-in printed circuit cards using M.E.L. series two elements.

It is considered that this equipment has evolved as a side-issue from development exercises in the application of this company's range of series two logic elements. Due consideration has not been given to those primary requirements, a clear display, a comprehensive mimic diagram and manual operating facilities. The cost of the stage one unit is approximately £200.

### (iv) <u>Cedus 201</u>. <u>Computer Engineering Ltd</u>.

The Cedus computer training system is based on unit construction and built to the user's specification. Each unit is capable of manual operation without reference to any other unit. The machine operates in the serial mode using a 16-bit word. Arithmetic operations are performed using three 16-bit shift registers in conjunction with the single-bit adder unit. The pulse generator unit incorporates a five stage counter and decoding gates to produce the 16 discrete timing pulses associated with each word. The counter operates at any frequency up to 100kHz and a sinewave of this frequency is generated internally. Clock pulses are generated either internally from the oscillator at this frequency, or by manual pushbutton. It is also possible to couple a separate pulse generator to the equipment. A plugboard unit is provided to 'patch up' any of the 16 machine instructions. in any order, to form a programme. The memory unit comprises a 1,024 word drum store with associated timing

pulse amplifiers. Interface units permit the use of tape readers and line printers. The average price of the 15 units. not including the £1,500 drum store, is £240.

It is possible to assemble these units to demonstrate most of the salient features of a digital computer system The manual operating facilities allow each step in the programme to be examined before proceeding to the next instruction. Filament lamps are used to indicate the flow of data through the machine. It is expected that equipment of this nature would provide the basis of a good demonstration computer, although it is extremely expensive and it operates serially, which is not in accordance with current practice on full scale computers.

# 2.2.3 <u>Conclusions on Commercially Produced Teaching</u> <u>Computers.</u>

It is evident from this review of equipment that there are two stages involved in the teaching of computer electronics. Units similar to those described in Section 2.2.1 are both necessary and appropriate to give the initial training in logic applications. The range of this equipment and the relatively small costs involved make it unnecessary for university and college departments to undertake special development to build their own equipment of this type. In the case of the more sophisticated

-19-

computer trainers it is seen that a considerable outlay, approximately £3,000, is required to obtain even a modest system which is suitable for demonstration work. The most modern of these equipments, ABACUS EC360/370, still employs second generation components and operates in the serial mode.

With reference to the equipment reviewed, it is apparent that the trend has been to adopt a 16 bit word and to provide a minimum of 120 words of storage. Manual. control is provided in most cases and facilities are normally made available for interfacing peripheral equipment.

# 2.3 <u>Review of Literature on Computer Electronics</u> <u>Teaching Equipment</u>

It is the intention, in this section, to establish the stages that appear to be currently adopted in the practical teaching of computing techniques. There have been a number of papers, notably in the Journal of Electrical Engineering Education, describing digital computing teaching aids which have been constructed in Schools, Colleges of Technology and Universities.

In the case of school projects (e.g. 2,3) it is apparent that the limitations of available time, finance and experience have resulted in equipment which is generally unsuitable for wider use. The tendency has been to produce equipment which will perform arithmetic operations, without prior reference to any teaching aids related to the basic logic functions. It was decided that reports of school projects were of little assistance in the determination of an acceptable specification for a demonstration computer for higher education.

There appear to be only a few references to more advanced machines. One practical aid has been described by Green (4). This incorporates the basic logic functions AND, OR and NOT. The display panel permits access to the terminals of six bistable elements and to the basic gating functions. Filament lamps are used to monitor the state of some of the logic elements, and toggle switches are are used to set up the input conditions. Pre-wired plug-in boards are included, as a special feature, to eliminate the need for extensive re-wiring of the front panel between demonstrations. It is reported that equipment of this sort is a useful aid in the teaching of undergraduate courses, and is seen to prepare students for the design of the complex circuits associated with arithmetic and control operations.

A paper by Hurst (5) describes a logic tutor which utilizes ten identical logic display panels and one master

-21-

panel, within the framework of a single unit. Each of the logic display panels provides access to: one of each of the four gating elements AND, OR, NOR and NAND, a bistable element, a buffer amplifier and a filament lamp. The master panel incorporates a telephone dial, a voltmeter and three clock generators. In order to reduce front panel wiring, six of the more complex circuits, e.g. shifting and B.C.D. counting, are pre-wired and selected by means of a rotary switch.

The Low Cost Digital Computer for Teaching described by Abrahams (6) has already been dealt with in Section 2.2.1 and is therefore not given further consideration here.

The main conclusions to be drawn from these articles are:

- (i) The initial use of the basic AND and OR functions.

- (ii) That teaching aids of this sort are "stage one" in preparing students to deal with the more complex operations of a full computer.

(iii) That front panel wiring should be minimised as it

is time-consuming and detracts from the main objective

Most of the textbooks dealing with computer fundamentals

provide a good indication of the various stages involved in

the understanding of computing techniques. It is not the

intention to discuss these books here, although it should be

.-

noted that they all show the same sort of pattern in developing the subject. This appears to be as follows:

- (i) Arithmetic / algebra of the binary system.

- (ii) Application of electronic devices to switching circuits.

- (iii) A detailed treatment of each of the major units, arithmetic, control and memory.

- (iv) A description of the design features of either a hypothetical machine (e.g. 7,8) or an actual general purpose computer.

- (v) The applications of digital computers, including notes on programming.

It is therefore considered that the logic tutors, referred to in Section 2.2.1, support the teaching and appreciation of topics i and ii. The more complex equipment, similar to that described in Section 2.2.2, is required when dealing with topics iii and iv.

# 2.4 <u>General Requirements of a Machine for Teaching</u> <u>Computer Electronics</u>

The review of the commercial equipment and of the literature seems to show considerable deficiencies in previous thought on the production of equipment for teaching computer electronics. It has, however, enabled the general requirements to be specified in a rather more precise form and, at this stage, it is desirable to list these since they are the basis of the design described in the remainder of this thesis.

(i) The requirement appears to be for a computer (9) as distinct from a complex logic trainer. This implies automatic operation of machine instructions and the ability to modify the sequence of instructions.

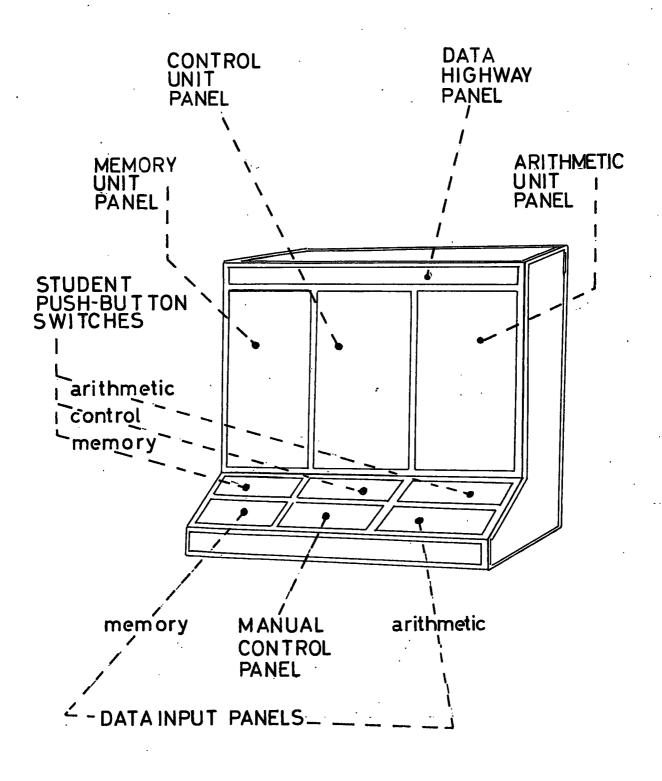

(ii) It should be able to demonstrate the operations of the machine in much more detail than is possible with a full-size computer. To this end a large display panel is essential with lamps to indicate the flow of information and the state of all major control gates. It should be possible to gain access to the entire logic circuitry for more detailed examination. Pushbutton switches should enable the machine to be operated manually.

(iii) To enable the operation of the machine to be followed it should be capable of very slow, IHbit/sec, and manual operation as well as automatic operation at moderate speed.

(iv) It should incorporate up-to-date, preferred techniques and components in order to be of use for as many years as possible. This implies parallel operation using integrated circuits and printed wiring. The machine should be capable of extension in the future.

-24-

(v) It should be cheap enough for purchase by university and college departments. This probably means an upper price limit of between £1,500 and £2,000.

(vi) The educational aspect should be held in mind throughout the project and the various student instruction manuals produced at the end.

These basic requirements will be built into a technical specification in Section 5.1 by which time the fundamental decisions on the machine will have been taken.

#### CHAPTER III

#### BASIC COMPUTING TECHNIQUES

The basic requirements of the proposed teaching computer were listed in Section 2.4. Before working out a more detailed specification, it is necessary to discuss some of the basic techniques used in digital computation. This is done in the present chapter to prepare the way for the more detailed discussions of chapters 4, 5 and 6.

3.1 Logic Functions

It is necessary to define the basic logic states, connectives and graphical symbols used in this thesis. Many of these are standard notation as may be found in any books on computing electronics, such as 'Digital Computer Design' by Edward L. Braun (10) or 'Fundamentals of Digital Machine Computing' by Guenther Hintze (11).

The following rules are used to define the logic states and notation which exist in digital switching systems.

(i) Two discrete states are considered; any two obviously different from each other may be employed, e.g.

0 - 1, on - off, black - white. In this equipment the logic 1 state is represented by +5 volts and the logic 0 state by 0 volts.

(ii) Every logic quantity must exist in one of these two states.

(iii) Every logic quantity may exist in only one of these states at any one time.

(iv) A quantity representing the logic 1 state is equal to any other quantity which represents the logic 1 state.

(v) Every logic quantity has an opposite. If a quantity is equal to logic 1, then its opposite is equal to logic 0.

(vi) A logic quantity may be constant or variable.

If constant it remains in one of the two logic states:

if variable it is continuously switched between the two logic states.

(vii) Alpha characters are normally used to identify the various logic functions which exist within a digital switching system. Thus the letter A may represent a logic function, and the letter B used to denote a second logic function. A may therefore be equal to logic 1 or logic 0, but not both at the same time. The notation for the opposite of A, called NOT A, is  $\overline{A}$ . Thus if A = 1,

then  $\overline{A} = 0$ , and if  $\overline{A} = 1$ , then A = 0.

There are three fundamental logic connectives, and, although they are not used in the equipment, it is necessary to define these functions, as the equations specifying the operation of the machine were originally deduced using these basic connectives.

Ą

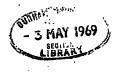

#### The AND Function

The AND function, or 'gate', is represented by a dot, ', or brackets associated with two or more variables. The graphical symbol used to denote this function is shown in Fig. 1. If A, B and C represent the input variables, then the equation defining the output of the function F is given by,

$$\mathbf{F} = \mathbf{A} \cdot \mathbf{B} \cdot \mathbf{C}$$

Thus the function F is 1, when all input variables are 1, and F is 0, if any one of the input variables is 0.

### The OR Function

The OR function, or 'gate', is represented by a plus sign, +, associated with two or more variables. The graphical symbol used to denote this function is shown in Fig 2. If A, B and C are input variables, then the equation defining the operation of the function F is given by

$\mathbf{F} = \mathbf{A} + \mathbf{B} + \mathbf{C}$

Thus the function F is 1, if any one of the input variables is 1, and F is 0, when all input variables are 0.

### The NOT Function

The NOT function is represented by a bar above the variable, e.g.  $\overline{A}$ . The graphical symbol used to denote this function is shown in Fig. 3. If A represents the input variable, then the output of the function F is given by

$$\mathbf{F} = \overline{\mathbf{A}}$$

Thus the function F is 1, when the input variable is 0 and F is 0, when the input variable is 1.

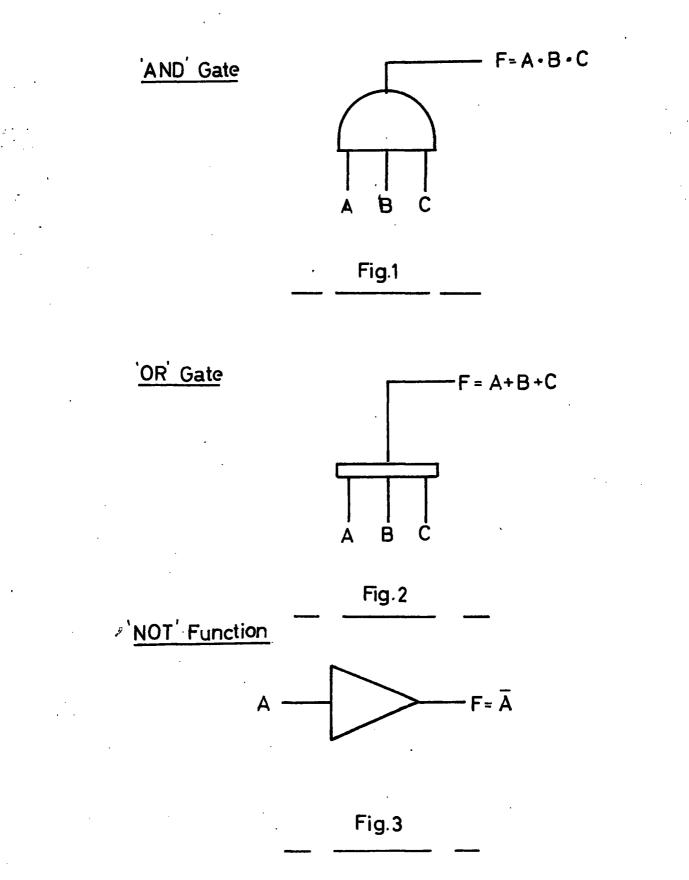

The NOR and NAND functions are developments of these three basic gates. It is possible to construct large combinational switching systems using only NOR or NAND elements

The NOR Function

The NOR function is represented by a combination of the symbols used for the OR and NOT functions. The graphical symbol for the NOR function is shown in Fig. 4. If A, B and C represent input variables, the output of the function, F, is defined by the equation

$$F = \overline{A + B + C}$$

Thus the function F is 0, if any one of the input variables is 1, and F is 1, when all input variables are 0.

The NAND Function.

The NAND function is represented by a combination of the symbols used for the basic AND and NOT functions. The graphical symbol for the NAND function is shown in Fig. 5. If A, B and C represent input variables, the output of the function, F, is defined by the equation,

# $\mathbf{F} = \overline{\mathbf{A} \cdot \mathbf{B} \cdot \mathbf{C}}$

Thus the function F is 0, when all input variables are 1, and  $\mathbf{F}$  is 0, if any one of the input variables is 0.

,

ļ,

### 3.2 Minimal Design Procedure.

It is sometimes convenient, when designing complex switching circuitry, to specify the design in terms of Boolean equations using the basic connectives AND, OR and NOT. It then becomes necessary to rearrange the equations, in order that the specification be presented in terms of the more versatile NOR or NAND elements. Also it is necessary to eliminate any redundant terms which were not initially apparent. The detection of such redundant terms may not be easily seen using the principie laws of Boolean algebra; it may, therefore, be necessary to introduce special techniques (12) which are summarised as follows:

- (i) Trial and error.

- (ii) Conversion of a sum of products to a product of sums.

- (iii) Introduction of dummy factors.

- (iv) Chart methods.

- (v) Map methods.

It is important to note that, in expressions containing a large number of variables, it may be convenient to break the expression into sections and apply the most appropriate of the above methods to each section. As most of the design specification was required in terms of NAND functions, a simple example is given.

-30-

-31-

| F | Ξ | $\mathbf{A} \cdot \mathbf{B} + \overline{\mathbf{A}} \cdot \overline{\mathbf{B}}$            |

|---|---|----------------------------------------------------------------------------------------------|

| F | = | $\overline{\mathbf{A} \cdot \mathbf{B} + \overline{\mathbf{A}} \cdot \overline{\mathbf{B}}}$ |

| F | = | $(\mathbf{A} \cdot \mathbf{B})  (\overline{\mathbf{A}} \cdot \overline{\mathbf{B}})$         |

| F | = | $\overline{(\overline{A} \cdot B)} \ \overline{(\overline{A} \cdot \overline{B})}$           |

It is seen that the function F may be realised using three NAND elements.

#### 3.3 Combinational Logic Circuits

When it becomes evident that a number of basic logic elements, connected so as to satisfy a complex expression, are being employed on a number of occassions, it is customary to simplify the specification by considering the complex function as a single unit which has straightforward relationships defining its operation. The combinational logic elements used in this equipment are therefore listed and defined.

#### 3.3.1 <u>EXCLUSIVE-OR Gate</u>

The EXCLUSIVE-OR gate is used fairly commonly when a function F is to be in the logic 1 state with only one of two input variables, A + B, in the logic 1 state. Thus  $F = \overline{A} \cdot B + \overline{A} \cdot \overline{B}$ ,

which may be rearranged to give,

$$F = A \cdot B + A \cdot B$$

.

The use of two AND gates and one NOR gate is required to satisfy this equation. The general arrangement for the EXCLUSIVE-OR function is shown in Fig. 6.

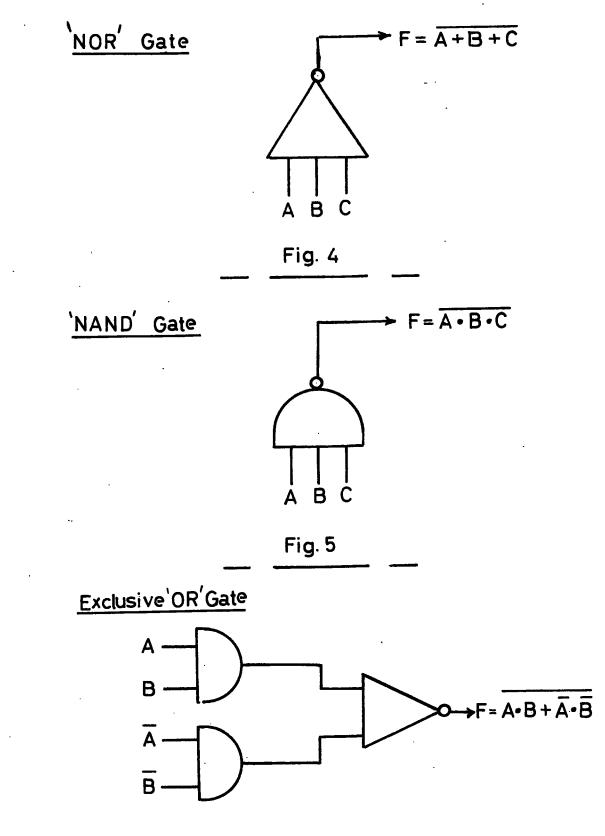

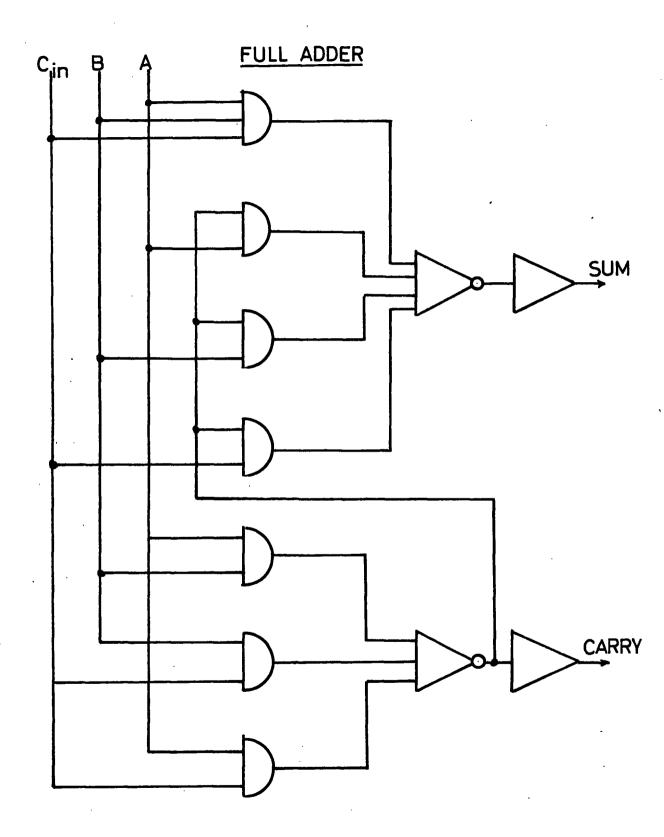

# 3.3.2 The Binary Adder

The combinational logic circuit required to add together two binary digits, A and B, with a carry digit C from a previous stage, is obviously used extensively in computing electronics. An examination of the following truth table shows how the Boolean expressions are derived to satisfy the requirements of a full binary adder.

| A                |                                                                               | B                                                                       | C       | Cout    | Cout      | Sum |  |

|------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------|---------|-----------|-----|--|

| 0                |                                                                               | 0                                                                       | 0       | 0       | 1         | 0   |  |

| 0                |                                                                               | 0                                                                       | 1       | 0       | 1         | 1   |  |

| 0                |                                                                               | 1                                                                       | 0       | 0       | 1         | 1   |  |

| 0                |                                                                               | l                                                                       | 1       | 1       | 0         | 0   |  |

| 1                |                                                                               | 0                                                                       | 0       | 0       | 1         | 1   |  |

| 1                |                                                                               | 0.                                                                      | 1       | 1       | 0         | 0   |  |

| 1                |                                                                               | 1                                                                       | 0       | 1       | 0         | 0   |  |

| 1                |                                                                               | 1                                                                       | l       | l       | 0         | 1   |  |

| C <sub>out</sub> | =                                                                             | <b></b>                                                                 | - A.B.C | + A.B.C | F + A.B.C | !   |  |

|                  | $= C(\overline{A}.B + A.\overline{B} + A.B + A.B) + A.B.\overline{C} + A.B.C$ |                                                                         |         |         |           |     |  |

|                  | ł                                                                             | $C\left[A(\overline{B}+B)+B(\overline{A}+A)\right]+A.B(\overline{C}+C)$ |         |         |           |     |  |

|                  | =                                                                             | $A \cdot C + B \cdot C + A \cdot B$                                     |         |         |           |     |  |

| Sum              | =                                                                             | A.Cout                                                                  | + B.Cou | t + C.0 | out + A.  | B.C |  |

### \* Dummy factors

The logic circuit required to satisfy these two equations is shown in Fig. 7. and is the circuit of the Texas 7483N I.C. which was used in this computer.

Fig. 7

### 3.3.3 The Bistable Element

The bistable element is widely used in digital equipment. It is appropriate, therefore, to describe the operation of the simplest form of such elements and to give the characteristic equations and symbols associated with the two types used in this equipment.

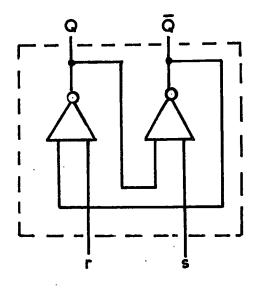

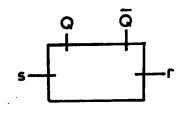

This logic circuit is arranged to have two outputs, Q and  $\overline{Q}$ , only one of which may exist in the logic 1 state at any one time. The state of these two outputs is controlled by the previous application of a logic 1 state to either of the two inputs which are called the set, s, and reset, r, inputs. If a logic 1 is applied to s, then the output Q assumes the logic 1 state and will remain in that state even after the logic 1 mhas been removed from the set input. Similarly a logic 1 applied to r will cause the output  $\overline{Q}$ to assume the logic 1 state and remain in that state after the logic 1 has been removed from the reset input. The logic schematic of Fig. 8 illustrates the mechanism of a very simple R-S bistable element.

The characteristic equation, defining the operation of the bistable element, relates the state of the outputs Q and  $\overline{Q}$  at a time (t+1) to the state of the inputs at a previous time (t). Thus the characteristic equations for the R-S bistable element shown in Fig. 8 is simply,

$Q_{t+1} = s_t$  and  $\overline{Q}_{t+1} = r_t$ .

-33-

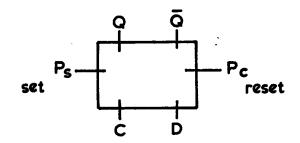

$Q_{t+i} = \overline{P}_{c} \cdot Q_{t} + P_{s} + C \left( J\overline{K} + \overline{J}\overline{K}Q_{t} + J\overline{K}\overline{Q}_{t} \right)$  $\overline{Q_{t+i}} = \overline{P}_{s} \cdot \overline{Q}_{t} + P_{c} + C \left( \overline{J}K + \overline{J}\overline{K}\overline{Q}_{t} + J\overline{K}Q_{t} \right)$ Type J K Bistable

$\overline{Q}_{t+1} = \overline{P}_s \cdot \overline{Q}_t + P_c + C \cdot \overline{D}$

Type D Bistable

Fig. 9.

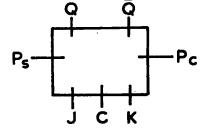

The type D and J-K bistables, which are used in this equipment are more complex than the R-S type. They have more input terminals from which the state of the outputs Q and  $\overline{Q}$  may be controlled. A detailed analysis of the operation of these elements is given in Ref. 13. The graphical symbol and characteristic equations for each type are shown in Fig. 9.

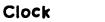

It is customary to give a title to each bistable, and this is normally done by using the initial letters of the particular function with appropriate numerical subscripts. The schematic of Fig. 10 illustrates the accepted method of designating a series of bistable elements associated with the common function B.

## 3.3.4 Shifting and Counting

Since the shifting and counting operations are used extensively in digital equipment, it is appropriate to show how they may be realised using both basic logic and bistable elements. An 'n' stage shift register may be constructed from n bistable units, so interconnected by gating elements, that on the application of a shift pulse the contents of each stage,  $B_x$ , is transferred to stage  $B_{x\pm 1}$ . Fig. 10 indicates how a shift left register may be constructed using R-S bistable elements. The gates R and S are used to steer the clock pulses from the control line to either the

-34-

Clock pulses

Fig. 11

•

CI

reset (r) or set (s) input of each bistable element. This steering action is controlled by the state of each preceding element, or in the case of stage  $B_0$ , by the state of the input function A. Assuming that element  $B_0$  is 'set' and A is equal to 0, then on the application of the first clock pulse,  $C_T$ , gates  $R_0$  and  $S_1$  will operate, causing elements Bo and B1 to be 'reset' and 'set' respectively. This steering action applies to all stages of the register, causing the contents of each stage to be shifted one place left each time a clock pulse  $C_{T_{t}}$  is applied to the control line. The switching time of the binary element usually provides sufficient delay, so that intermediate storage elements are not required. Shift registers are used for temporary storage of binary numbers, serial to parallel conversion and in the more complex arithmetic processes. The characteristic equations for each bistable element Bn in a shift left register are given by:

$B_{n_{t+1}} = B_{n-1_t} \cdot C_L$  and  $\overline{B_{n_{t+1}}} = \overline{B_{n-1_t}} \cdot C_L$ Similarly for a shift right register these equations are:

$B_{n_{t+1}} = B_{n+1_t} \cdot C_L$  and  $\overline{B_{n_{t+1}}} = \overline{B_{n+1}} \cdot C_L$

The second of the more complex operations, binary counting, may be realised using similar techniques to those described for the shift register. In this case the steering of the <u>clock pulses</u> is controlled by the state of the

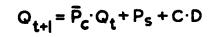

bistable element to which the pulses are applied. The logic schematic, Fig. 11, shows a simple 'divide-by-two' circuit in which the pulses appearing at the output occur at half the rate of those applied to the input. With the bistable initially reset, gate S steers the first and subsequent oddnumbered clock pulses to the set input s. causing the bistable element to change state. The second and subsequent even-numbered pulses are applied to the reset input r. causing the bistable element to switch back to its original reset state. The signal appearing at the  $\overline{Q}$  output may be used as a clock signal to a second identical 'divide-by-two' circuit. By cascading n stages in this fashion, a system is produced which will accept and store as a binary number up to 2<sup>n</sup>-1 clock pulses. When constructing counters of this sort, it is important to establish whether the bistable elements change state on the leading or trailing edge of the clock pulse. The effect of propagation delay in fast counters may be overcome by gating the clock pulses to each stage of the counter. This ensures that all stages change state at the same time. The characteristic equations for a 'divide-bytwo' circuit are:

$B_{n_{t+1}} = \overline{B_{n_t}} C_L$  and  $\overline{B_{n_{t+1}}} = B_{n_t} C_L$

-36-

### 3.4 Realisation of Arithmetic Processes

The basic processes involved in arithmetic are addition, subtraction, multiplication and division. It is expected that sub-routines will be programmed for the determination of the more complex arithmetic operations e.g. square roots, trignometric functions etc. These subroutines will also assist in demonstrating the operation of the equipment. Some of the logic methods available for the realisation of the basic processes are described here. Addition has already been dealt with in Section 3.3.2

## 3.4.1 Binary Subtraction.

It is possible to produce a set of equations to satisfy the laws of binary subtraction, and hence construct a binary subtractor by methods similar to to those described for the full adder in Section 3.3.2. It is common practice to employ the method of complementing the subtrahend and adding, thus eliminating the need for both an adder and a subtractor to be incorporated in the same machine. The logical decisions required to complete a subtraction are given for the types of complement possible in binary algebra. Both methods have certain merits and limitations, the most serious limitation being the complexity of the methods necessary to establish the sign of the remainder. A number of rules may be applied (14) which provide the equations necessary

-37-

to determine the sign of the remainder. The two methods are as follows:

(i) Subtraction using Two's Complement.

The two's or radix complement of a binary number is obtained by replacing all 1's by 0's and all 0's by 1's and adding 1 in the least significant position. The difference is formed by adding the two's complement of the subtrahend to the minuend.

e.g. 1001 - 0101 = 0100 i.e. 9-5 = 4Two's complement of subtrahend = 1010  $= \frac{1}{1011}$ adding minuend = 1) 0100

The l in the overflow column indicates a positive difference.

(ii) <u>Subtraction using One's Complement.</u>

The one's complement of a binary number is obtained simply by replacing all 1's by 0's and all 0's by 1's. The one's complement of the subtrahend is added to the minuend to give the difference. With this method the carry produced in the most significant stage must be added together with the least significant digits to complete the subtraction. Using the previous example:

| One's complement of subtrahend,       | 1010      |

|---------------------------------------|-----------|

| adding minuend                        | 1001      |

|                                       | 1 0011    |

| The overflow digit is then            | <b></b> 1 |

| added in the least significant stage. |           |

| Difference. =                         | . 0100    |

## 3.4.2 Binary multiplication.

As in the case of subtraction it is not economical to construct a multiplier which will generate the product digits simultaneously with the inputs. It is usual to find that the methods adopted are based on 'long multiplication'. The method described here is based on the repeated addition of the multiplicand to correct orders of a sub-product, the final sub-product being the required product. It will be appreciated that if each of the two operands have n digits, then the product will have a maximum of 2n+1 digits. It is customary to allow the product to develop in an accumulator and in the register which is used to store the multiplier. This is possible since the multiplier is successively shifted out of its initial storage register during the operation. It then becomes necessary to round off the product to n digits so that it is again compatible with the data already stored.

This operation may be realised in the following way. It is assumed that the sub-products are to be developed in an accumulator register which has right shifting facilities and that the multiplier is initially stored in an auxilliary storage register M, which allows right shifting. The first sub-product is formed by examining the least significant digit of the multiplier. If this is a l. the multiplicand is added to the zero contents of the accumulator. If the least significant digit of the multiplier is 0, the addition is not performed and the contents of the accumulator remain at zero. The contents of both the accumulator and register M are then shifted one place right, with the least significant digit in the accumulator being routed to the most significant position in register M. The process of examining the least significant digit of the multiplier, adding and then shifting is repeated until all the digits of the multiplier have been tested.

The following example is intended to illustrate this method of binary multiplication. Multiply 10011 x 1101 i.e Multiplicand is 10011 and the multiplier 1101.

|                                  | Accumulator. | Register M |

|----------------------------------|--------------|------------|

| The L.S.D of multiplier is 1,    | 00000        |            |

| therefore sub-product is 10011   |              | •          |

| Shift (ACC) and (Reg.M) right    | 01001        | 1          |

| L.S.D of multiplier is 0, sub-pr | oduct=01001  | 1          |

| Shift (ACC) and (Reg.M) right    | 00100        | 11         |

| L.S.D of multiplier is 1, add    | <u>10011</u> |            |

| Sub-product 10111                |              | 11         |

| Shift (ACC) and (Reg.M) right    | 01011        | 111        |

| L.S.D of multiplier is 1, add    | 10011        |            |

| Final product is therefore       | 11110        | 111        |

-40-

# 3.4.3 Binary Division.

The method involving counting the number of repeated subtractions of the divisor from the dividend and resulting remainders is considered to be uncharacteristic of a modern computer. The commonly used method requiring trial subtractions, restoring and shifting is considered suitable for the proposed demonstration equipment and is therefore described here.

This method requires that the two operands be initially aligned such that the most significant 1 digits are in identical positions in their respective registers. The difference in the number of digits contained in the dividend. compared with those contained in the divisor, is used to determine the number of digits in the quotient. A trial subtraction of the aligned divisor is performed; if the remainder is positive a 1 is placed in the most significant position of the register in which the quotient is to be developed. If, however, the remainder is negative a 0 is placed in the quotient and the original dividend restored. The divisor is then shifted one place right and a further trial subtraction is performed. The tests on the remainder are repeated to determine the value of the digit to be entered into the quotient register. The process of trial subtraction is repeated until either the required accuracy is obtained or the capacity of the register storing the

-41-

the quotient has been exceeded. An example is given to illustrate this method of binary division.

Divide 1100100 by 10100 i.e. 100 by 20. The difference in the number of digits between the two operands is (7 - 5) = 2; therefore the number of digits in the quotient is (7 - 5 + 1) = 3.

| Step 1. | Align both operands                                                    | 1100100<br>1010000        |

|---------|------------------------------------------------------------------------|---------------------------|

| Step 2. | Subtract                                                               | 0010100                   |

| Step 3. | Remainder is positive                                                  |                           |

|         | therefore quotient is l                                                |                           |

| Step 4. | Shift divisor one place right                                          |                           |

|         | Positive remainder<br>Shifted divisor                                  | 0010100<br><u>0101000</u> |

| Step 5. | Subtract 1                                                             | 0001100                   |

| Step 6. | Remainder is negative                                                  |                           |

|         | therefore quotient is 10                                               |                           |

| Step 7. | Shift divisor one place right<br>Restored remainder<br>Shifted divisor | 0010100<br>0010100        |

| Step 8. | Subtract                                                               | 0000000                   |

| Step 9. | Remainder is positive                                                  |                           |

|         | therefore quotient is 101.                                             |                           |

|         |                                                                        |                           |

The quotient now contains the required three digits and at this stage the operation is terminated.

### CHAPTER 1V.

#### FACTORS AFFECTING DESIGN.

#### 4.1 Primary Considerations.

The general requirements for the demonstration computer have already been established from the literature and in Section 2.4 as follows:

(i) The machine must be a computer in the full sense of the word and not an electronic calculator. This implies that it must work to a programme, which will be fed to the machine, to-gether with the data, and that the programme may be modified during its execution.

(ii) Large display panels are essential for the teaching function.

(iii) Three speed operation is required, manual, slow speed and fast speed.

(iv) The machine must incorporate modern circuit and constructional techniques.

(v) The cost of the equipment should be as low as possible. (vi) The educational requirements must be borne in mind at every stage. This implies that the circuit must be capable of being broken down into the basic units for individual study, and that each part must be based on straight forward, easily understood electronic circuits.

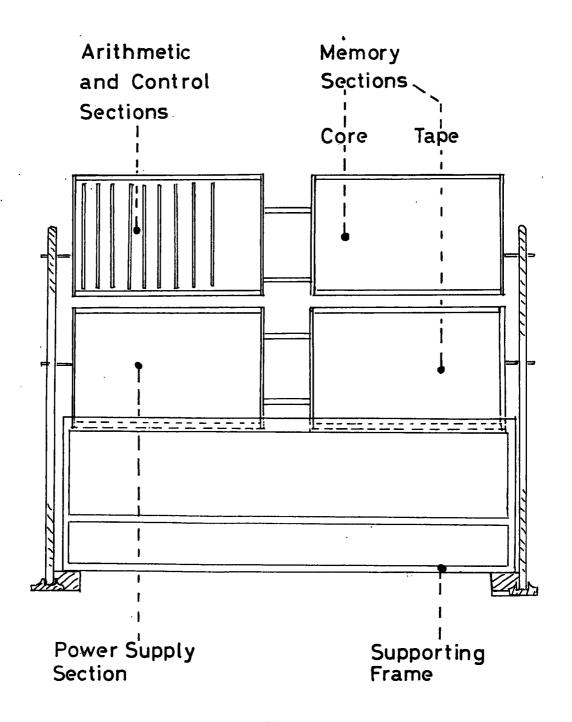

It is appropriate at this stage to state the nontechnical factors which have affected the design. It was obviously necessary to balance the estimated available manhours with the requirements of design and construction It was important to ensure that the programme did effort. not become so large that there would not be time to consider it in sufficient detail. Also it was necessary to 'foresee' the state of the art techniques so that components would be available at reasonable cost. In considering these and other aspects, the senior members of the department decided to split the project into three sections. The Memory Unit is described by Smith (1), the Control and Arithmetic Units are the subject of this thesis, while the design and construction of the Input / Output equipment was held in abeyance until after the completion of the other two parts. This arrangement is compatible with the initial proposals, that the three sections should be physically separable so that, in the event of some major malfunction, all would not be lost.

Against this background, there are the following main features of the machine, which should be listed but which obviously warrent no further discussion in this thesis. It was decided that the computer would have:

(i) A ferrite core store.

(ii) A magnetic drum store.

(iii) An adaquate instruction repetoire.

(iv) That it would use integrated circuits and plug-in printed circuit modules.

-44-

The following secondary features were also examined:

- (i) Aspects of general purpose computers.

- (ii) Type and number of machine instructions.

- (iii) Serial or parallel operation.

- (iv) Number representation.

- (v) Address modification.

- (vi) Word length.

- (vii) Micro-programming.

(viii) Method of demonstration.

These features are discussed in detail in the present Chapter. Decisions on these features enabled a detailed specification of the machine to be drawn up and this will be given in Section 5.1.

## 4.2 Some Aspects of General Purpose Computers.

In an effort to establish those main characteristics, which are common to the majority of general purpose machines, an examination of the recent survey on British computers(15) was undertaken. The results of this examination assisted in determining a specification which is characteristic of a modern general purpose machine. Those aspects relating to central processor operation are summarised here.

(i) There is no definite preference for pure binary or binary coded decimal number systems. There is a suggestion, that, where the machine is intended for business or accounting purposes, the latter system is preferred.

(ii) All machines operate with fixed point arithmetic, floating point operation being included in those machines used for scientific applications.

(iii) The word length appears to be governed by accuracy and the expected range of numbers as wellcas the address format. Variations from 12 to 60 bits are evident.

(iv) With few exceptions, arithmetic operations are carried out in the parallel mode, the execution time for such operat--ions being dependent on the switching speed of the logic elements, the access time of the memory and the complexity of the timing circuits. Times for addition vary from 3µS to 1.3mS, with multiplication and division taking in general 4 to 5 times as long.

(v) Current trends indicate a complete lack of uniformity in respect of the number of instructions offered, the range being from 14 to 170, with the majority of machines having between 50 and 80 instructions.

## 4.3 <u>Machine Instructions.</u>

A machine instruction comprises a pre-determined sequence of minor commands whichbare established by the design of arithmetic, control and memory units. The number and type of machine instructions may be classified as those associated with:

-46-

(i) transfer of operands between the memory and arithmetic units,

(ii) elementary arithmetic operations,

(iii) transfer of control and the B line modifier,

(iv) logical manipulation of operands,

(v) input and output of data.

The number of instructions in this machine must be kept to a minimum to reduce costs and preserve clarity of demonstration. There must of course be sufficient instructions to enable the machine to operate with all the main features of a full computing system. The instructions should be as simple as possible, and it is hoped that student appreciation of the more complex instructions will be improved by demonstrating one simple step and allowing time for discussion, before proceeding to the next. In a general purpose machine a typical instruction may be, "Add the contents of location n to the contents of the accumulator placing the sum in storage location n" In the demonstration computer it is expected that three instructions may be necessary to effect this operation:

(i) Transfer (n) to the arithmetic unit,

(ii) Add,

(iii) Transfer sum to location n.

By placing a stop instruction between steps i and ii, and between ii and iii, it will be possible to demonstrate the operation more effectively.

-47-

## 4.4 Parallel or Serial Operation.

The difference between parallel and serial operation is as follows. In a parallel arithmetic unit all bits in the operands are acted upon simultaneously, requiring a single timing pulse for any one function. In a serial machine, on the other hand, each bit of an n bit word is acted upon sequentially, and this requires n timing pulses to complete each function.

Comparing the two modes of operation, the parallel type requires approximately, n times the circuitry in the arithmetic unit, 1/n times the circuitry in the timing unit and 1/nth of the time to complete a particular function. Other major factors must also be considered: e.g. compatibility with the memory system, the operating speed of the input devices and the expected load on the machine. Nearly all full-size computers operate in the parallel mode and the proposed machine should, if possible, be typical of this modern practice.

The choice of parallel or serial operation in this case is also affected by the demonstration aspects of the machine. One of the major techniques to be demonstrated is timing and sequencing of operations, and it is felt that to introduce many more timing pulses to satisfy the requirements of a serial machine would seriously impair the effectiveness of the demonstration. The parallel mode

-48-

is also compatible with the small core memory which is included in the machine. For these reasons it was decided to adopt parallel working in the arithmetic unit.

#### 4.5 Number Representation

The choice of number representation was made on the simplicity of circuitry and student appreciation. The three systems, pure binary, binary coded decimal and octal were each reviewed. The pure binary system, which requires the most simple arithmetic circuitry, was adopted. It was appreciated that the binary coded decimal system has certain advantages in the input / output sections. It was felt that the complexity of the circuitry to deal with the 'excess 6' would severely limit the effectiveness of arithmetic demonstrations.

### 4.6 Operand Address Modification.

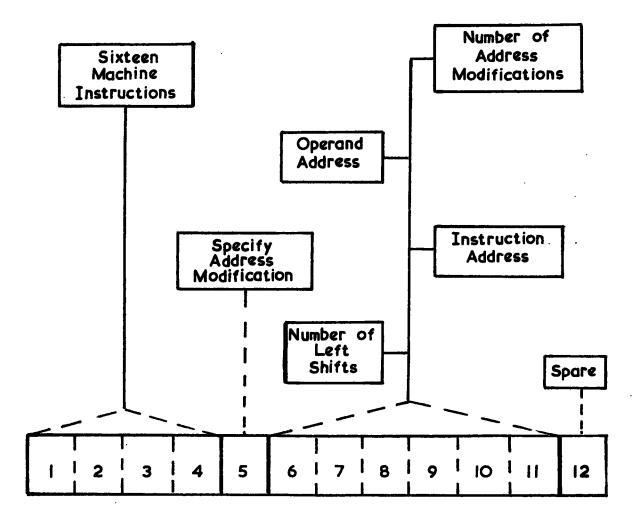

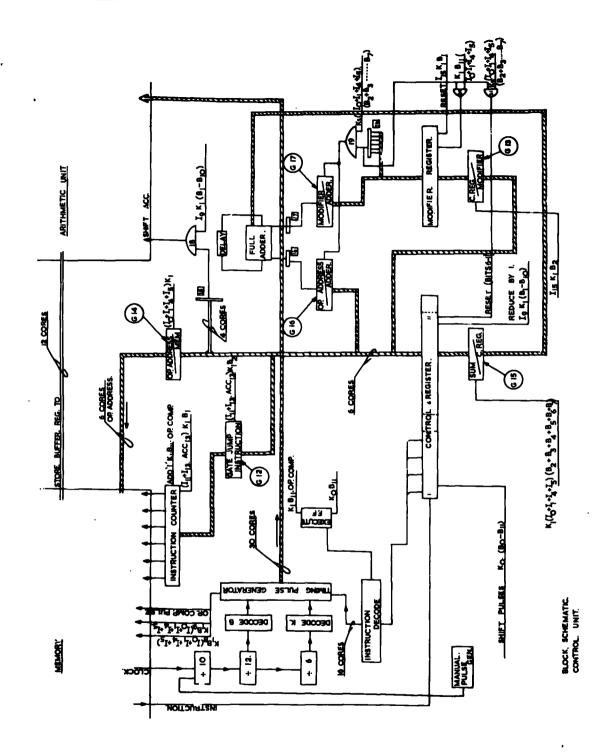

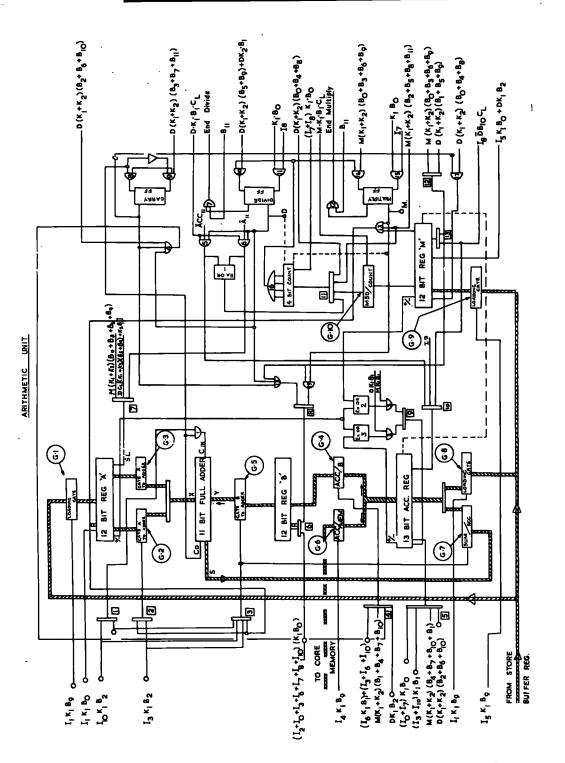

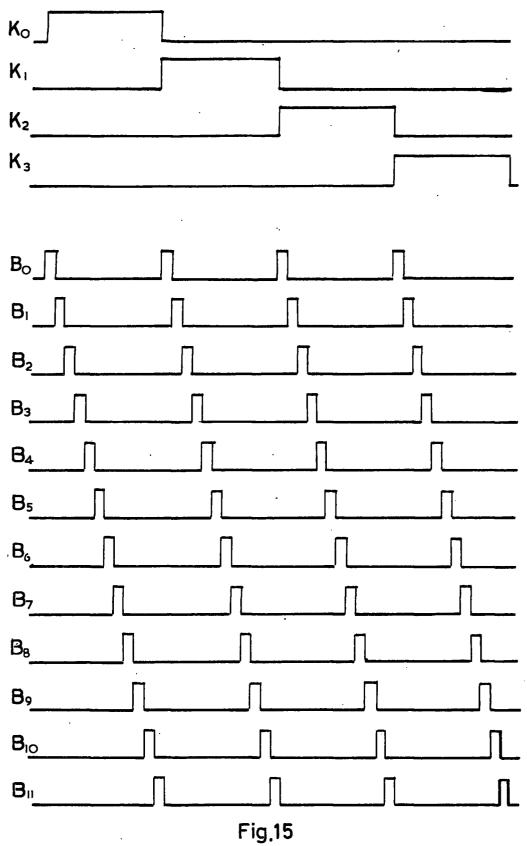

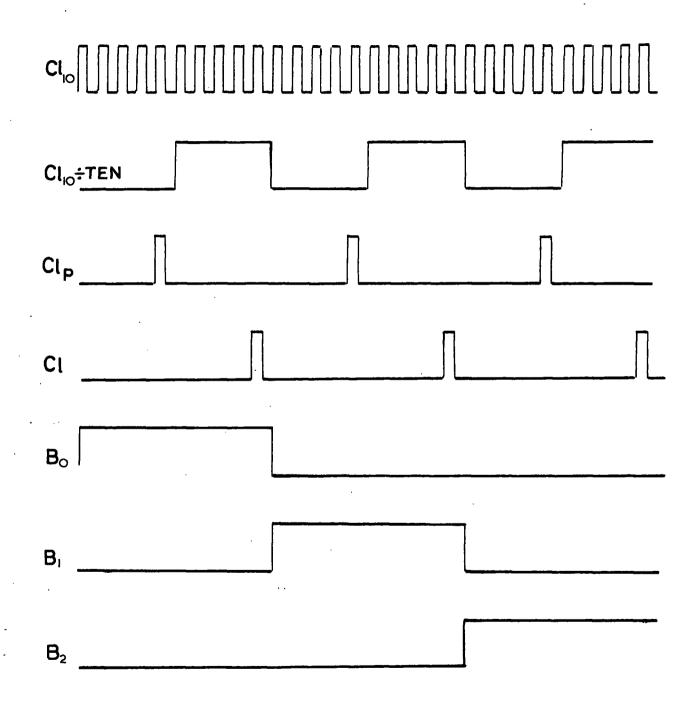

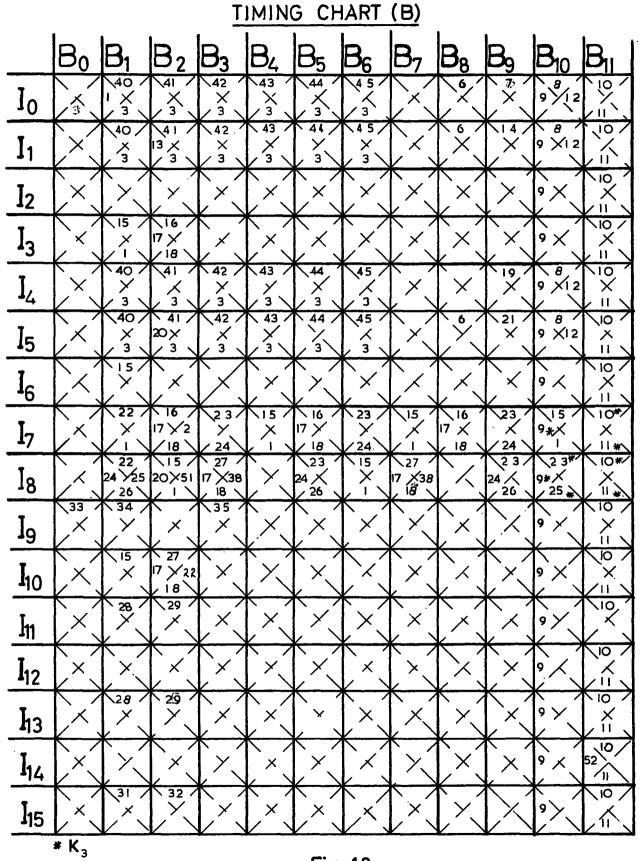

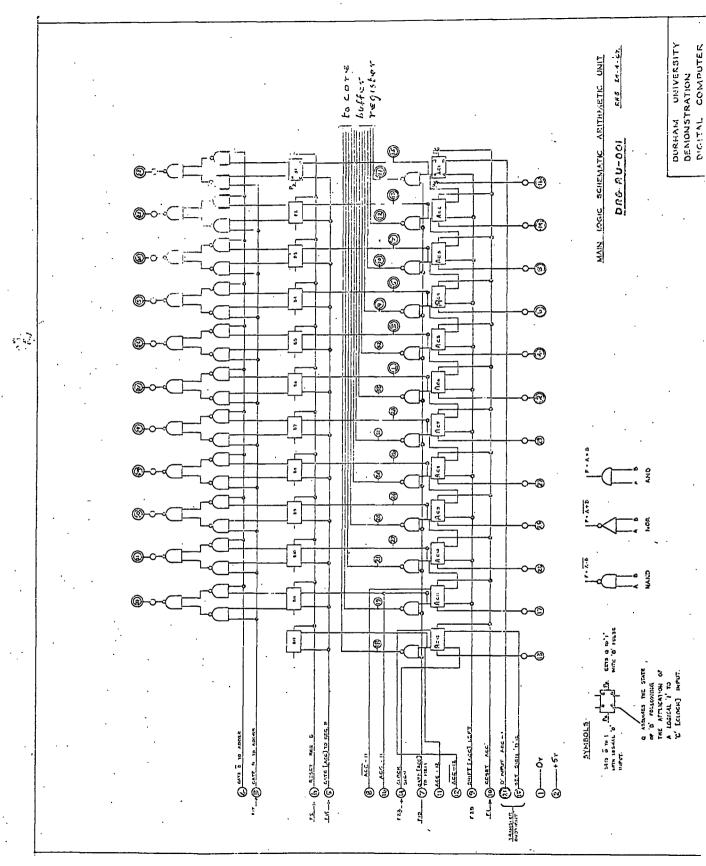

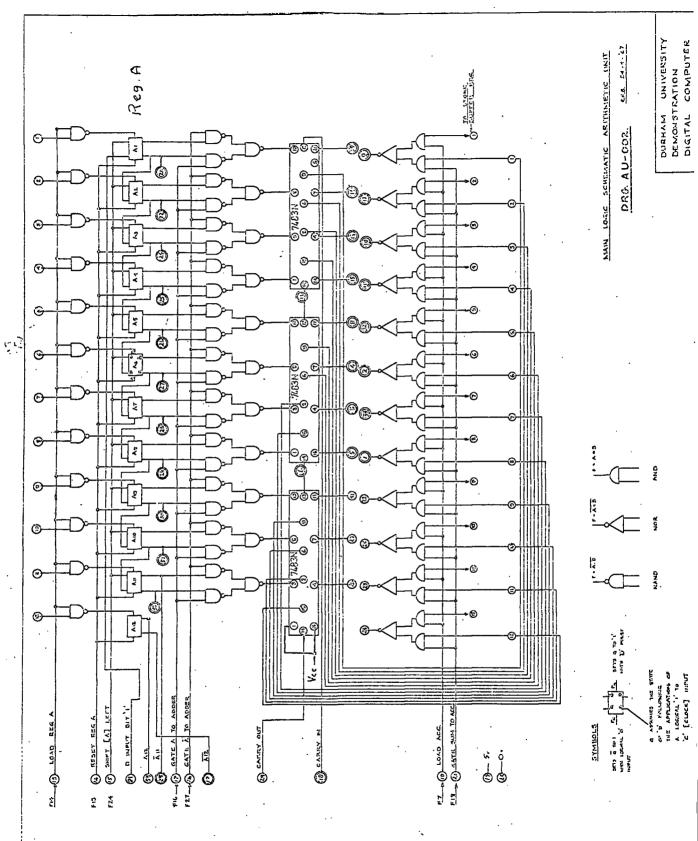

One of the most important aspects of computing is the use of the'B line modifier' or index register. When it is required to repeat an instruction n times with different operands, it is usual to employ the same instruction, modify the address field by the contents of the modifier register and use a conditional transfer instruction to maintain the loop in the programme. The number of address modifications to be applied, (n), is initially stored in the modifier register, the contents of which are reduced